1. Introduction

A smart temperature sensor is one of the most commonly desired parts in Internet of Things (IoT) devices to monitor either environment or chip conditions [

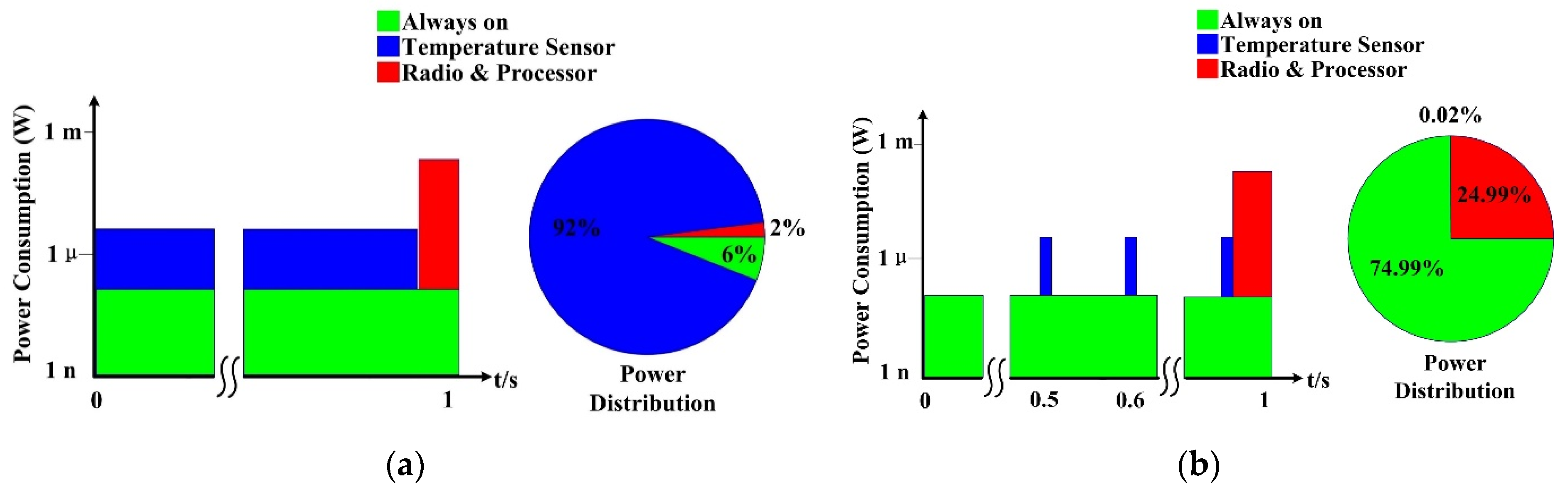

1]. The temperature sensors that have high energy efficiency and are of low cost can be used in many BIoT applications, for example, the preservation and transport of vaccines, medicines, blood samples, and other medical samples that should be placed in a certain temperature range. Duty cycling is a commonly used mode in a BIoT system, which requires the sensors switching between the on and off states to extend the batter life. As shown in

Figure 1a, the temperature sensor consumes 4.6 μW and it is always on just like other always-on modules that consume 300 nW. The processor and radio frequency module are activated to process and transmit data, which takes 1 ms at a 100 μW normalized power consumption. The temperature sensor consumes 92% of the total power consumption that is 5 μW, which is unacceptable for most BIoT applications. When the temperature sensor works on a duty-cycling mode, it is activated every 100 ms to take a measurement which takes only 1.3 μs consuming a 31 nA leakage current. The temperature sensor consumes only 0.02% of the total power consumption that is reduced to 400 nW. Thus, the conversion time of a temperature sensor should be as short as possible in order to reduce the effective power contribution on a BIoT system. According to

where

C is the equivalent capacitor,

F is the frequency and

V is the supply voltage. Reducing the supply voltage is beneficial to further reduce the power consumption. It means that a temperature sensor that works at a near-threshold-voltage supply has an advantage over the one that works at a normal-voltage supply. In addition, a temperature sensor should be compact and compatible with the CMOS process to reduce the cost.

Previous researches proposed various kinds of temperature sensors with different principles. A traditional voltage domain temperature sensor used BJT to generate proportional to absolute temperature (PTAT) voltages and then converted the voltages into a digital temperature reading with a ΔΣ-Analog-to-Digital Converter (ADC) [

2]. It is both energy and area consuming to implement a high-resolution ΔΣ-ADC. The higher working voltage (>1 V) required by BJT is not suitable for the BIoT applications. In [

3], a resistive-type temperature sensor achieved a high sensitivity up to 1.09%/°C, but it is not easy to be integrated, so it is not suitable for the BIoT applications. An alternative method is to use frequency or phase information to express temperature information. In [

4], researchers used two Voltage-Controlled Oscillators (VCOs) with different temperature-sensitive characteristics to convert the temperature change into a frequency change, and thus into a temperature reading by counter. With two oscillators operating at dozens of MHz frequency, they achieved a short conversion time of 6.5~22 μs, but this resulted in a high power consumption of about 154 μW. To solve the problem of power consumption, two MOSFETs operating in a sub-threshold region are used to sense the variation of temperature and generated two reference currents. Then, the ratio of currents are transformed into an output frequency difference between the two VCOs working in dozens of kHz frequency. The counter counts the frequency difference and outputs a temperature reading. However, this low-frequency method resulted in a longer conversion times of 59 ms [

5]. Resistance-based temperature sensors are usually implemented by RC filters [

6], which output temperature-related phase signal. This kind of temperature sensors can achieve high resolutions, but they are not quite suitable for BIoT applications due to high power consumption and long conversion time. In addition, researchers also expressed temperature information using time domain signal. In Ref. [

7], a delay line was designed to generate temperature-dependent time signal, and a cyclic time-to-digital convertor (TDC) outputs temperature reading. In [

8], a delay line was reused to sense the temperature in a sensing module and measure the PTAT pulse in a TDC. Time domain temperature sensors achieve better power consumption and smaller area.

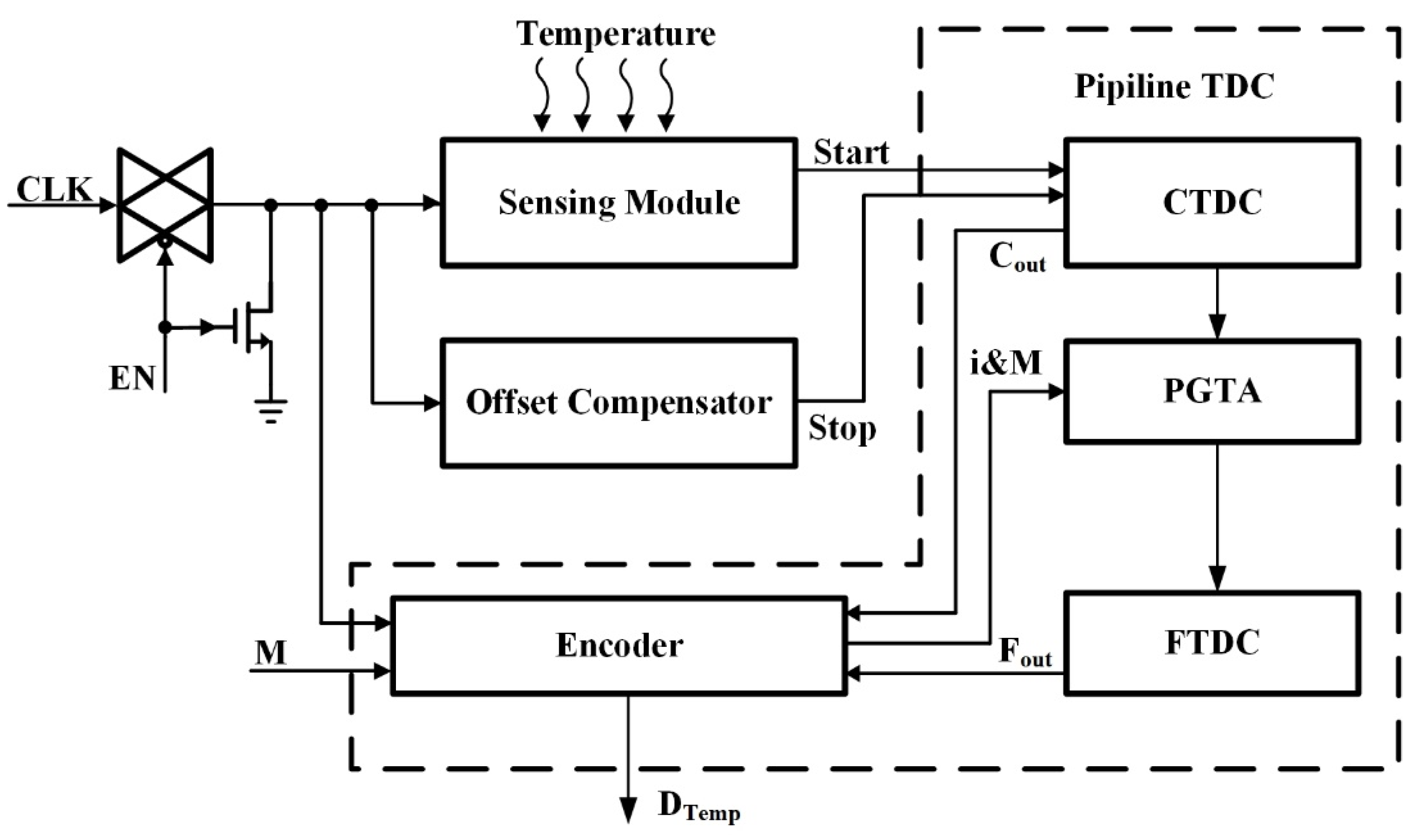

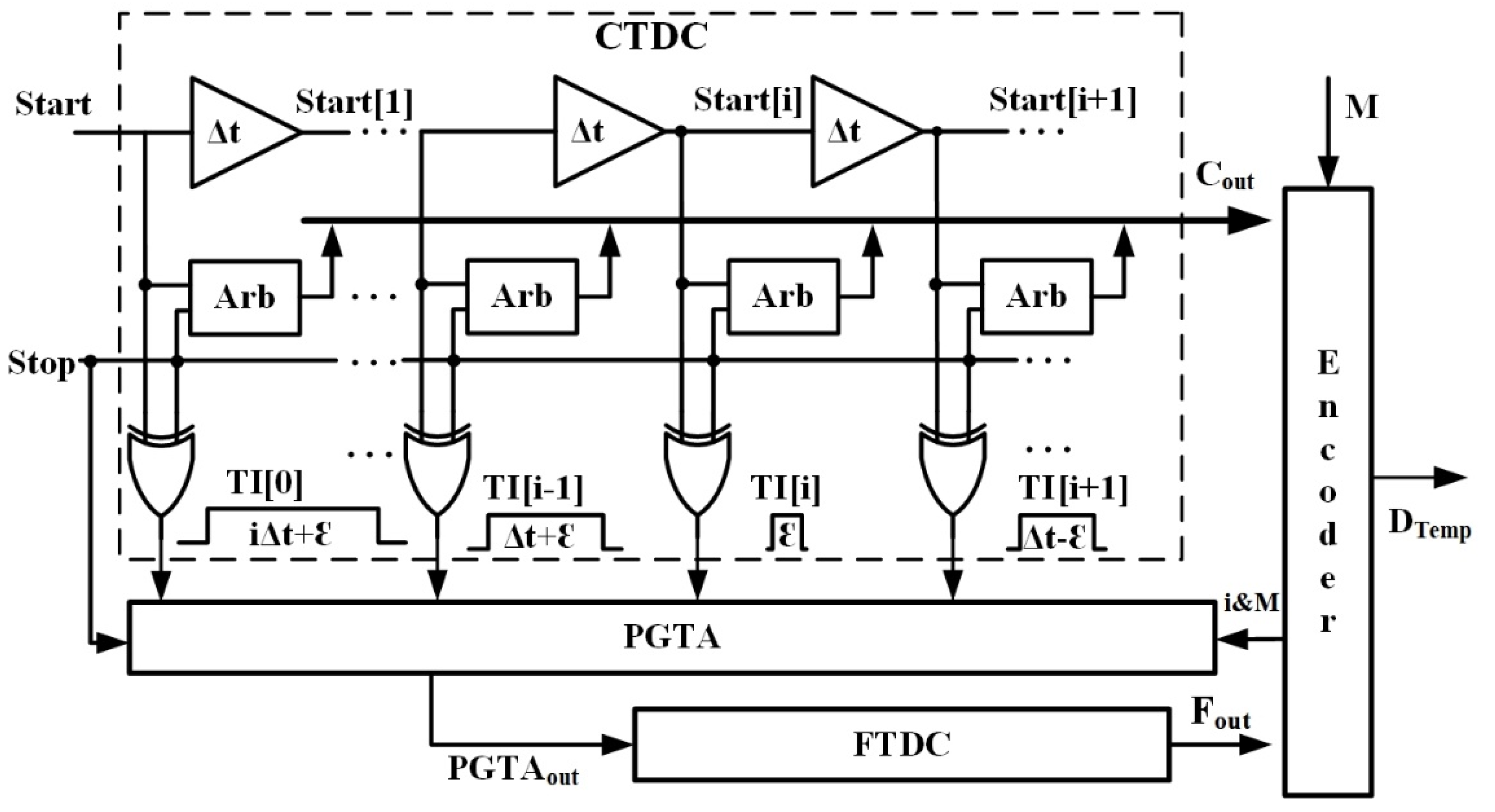

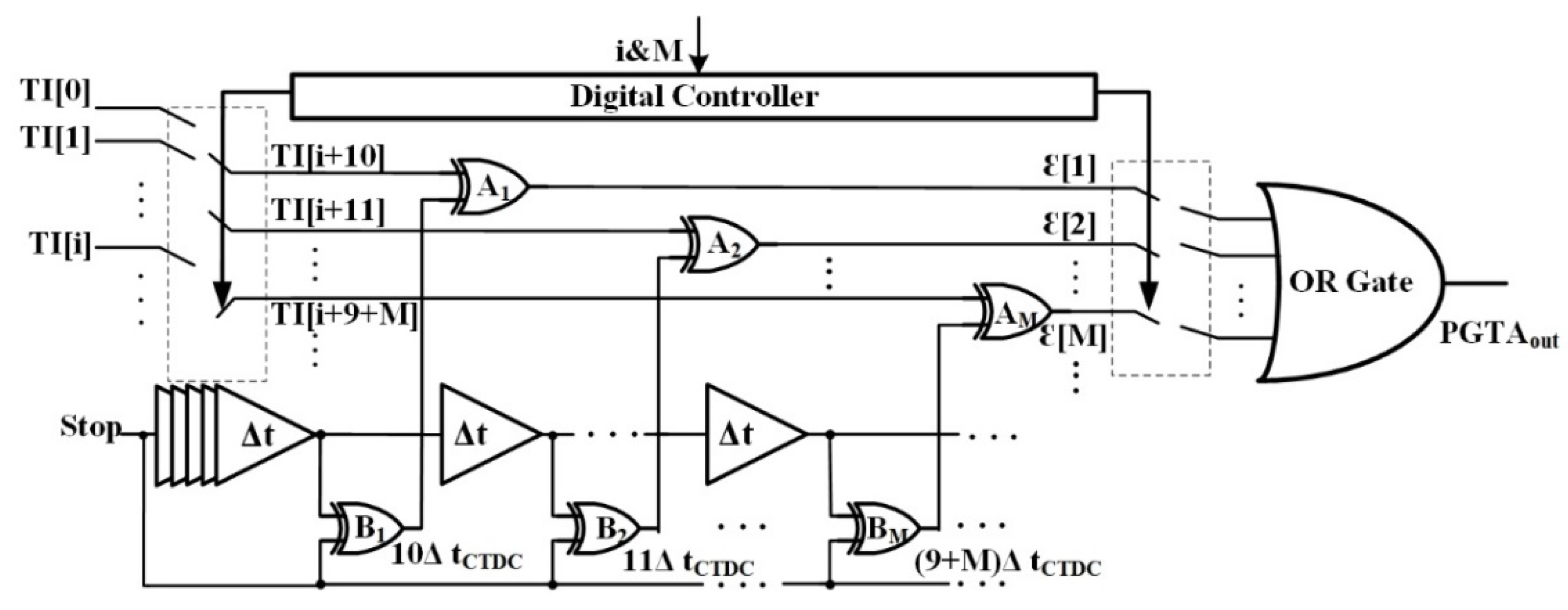

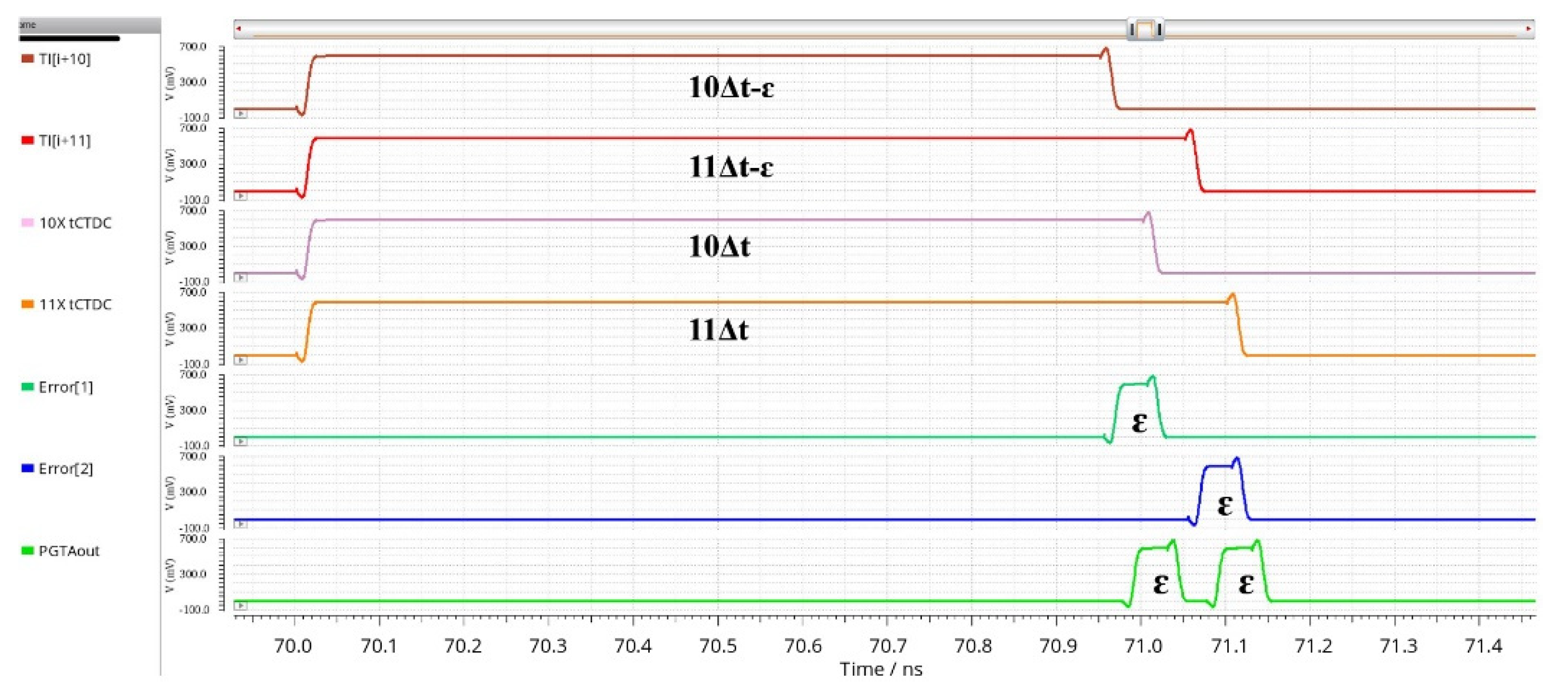

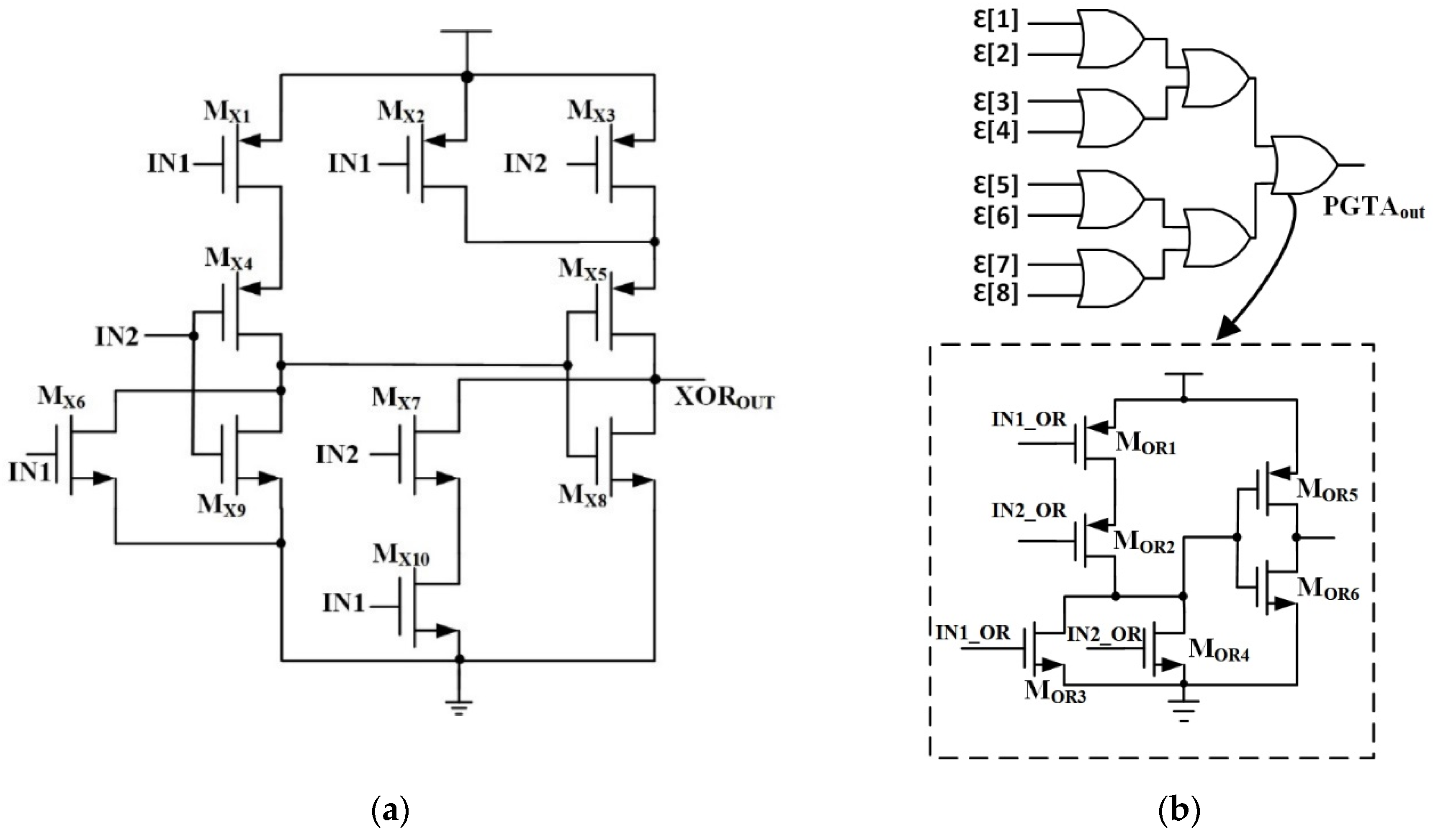

In this paper, we propose a MOSFET-based time domain temperature sensor, which is suitable for BIoT applications due to its short conversion time and high energy efficiency. The architecture diagram of this work is shown in

Figure 2. The sensing module uses a delay line to convert the temperature information into a delay time. An offset compensator generates a delay signal with low temperature sensitivity, which can compensate the offset part of the sensing module output. The output delay difference between the sensing module and the offset compensator is then translated into a corresponding digital code using a pipeline TDC. A programmable-gain time amplifier (PGTA) is proposed to achieve an integer time gain and it is low sensitive to temperature variation. The PGTA has a high linearity, a wide linear range, and a programmable time gain. Implemented in a 40 nm standard CMOS technology, the prototype sensor consumes 7.6 μA at a 0.6 V supply and achieves a 90 K resolution from –20 °C to 80 °C at a short conversion time of 1.3 μs.

The remainder of this paper is organized as follows.

Section 2 describes the operation principles and the theory analysis.

Section 3 presents circuit implementations with detail analysis.

Section 4 shows the measurement results of this work, and in

Section 5, we present the conclusions for this paper.

2. Principles of Operation and Theory Analysis

For time-domain temperature sensors, the most common method of temperature sensing is to use one or more delay lines to convert the temperature information into a time-domain signal. Therefore, it is necessary to analyze the temperature characteristics of the delay unit which is used in the sensing module and the TDC. According to [

9], the process of an inverter output transiting from high to low and from low to high can be equivalent to the process of the load capacitor charging and discharging through the equivalent resistance of MOSFET. At this point, if the output voltage is taken as half of the supply voltage as the reference point, the propagation delay can be expressed as

where

RP and

RN are the equivalent resistances of PMOS and NMOS, respectively, at the ON state.

CL is the load capacitance of the inverter, which has a low-temperature sensitivity [

7,

8]. The temperature characteristic of the delay time thereby depends on

RP and

RN that can be written by

where

VDD,

VDS,

IDS, and

λ are the supply voltage, drain-source voltage, drain-source current and channel length modulation coefficient, respectively.

Considering that the MOSFETs operates in triode region when the output voltage transits from initial value to 1/2

VDD, ignoring the influence of other non-ideal factors, the drain current can be expressed as follows:

where

µ is the carrier mobility,

COX is the gate-oxide capacitance per unit area,

W and

L are the channel width and length of MOSFET, and

VTH is the threshold voltage. According to the analysis in References [

10,

11]:

where

T0 is the reference temperature,

µ0 is the carrier mobility at reference temperature,

VTH0 is the threshold voltage at reference temperature, and

T is the temperature.

With a rise of temperature, the mobility and the threshold voltage will both decrease. The change of drain current with respect to temperature is obtained by derivation of the Equation (5) to temperature.

Since dμ/dT < 0 and dVTH/dT < 0, the temperature characteristics of the drain-source current can be determined by VDD − VTH, affected by the anti-short channel effect of MOSFET, the threshold voltage decreases with the increase of channel length. Therefore, when the channel length is long, VTH is much smaller than VDD. In this case, the temperature characteristics of the drain current will be controlled by the carrier mobility, that is, thermal coefficient of the drain current is negative. Otherwise, a shorter channel length will make the thermal coefficient of drain current positive.

By substituting Equations (3)–(5) into Equation (2), the delay time of inverter can be obtained:

The delay time of a delay unit composed of two inverters is shown in Equation (10), which is inversely proportional to the drain current. According to Equation (8), with the change of the channel length of MOSFETs, the delay unit can generate a delay time that is positively or negatively correlated with temperature.

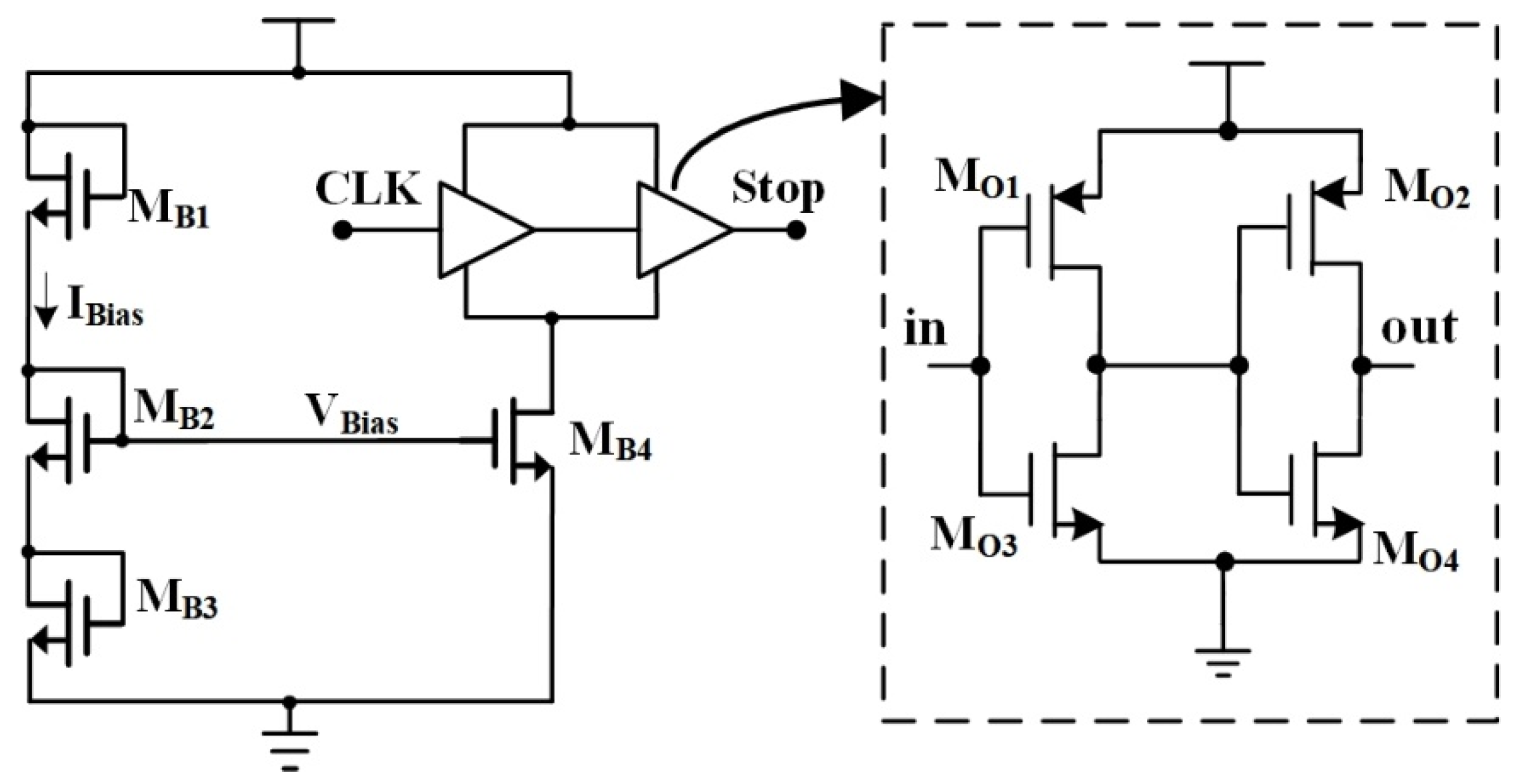

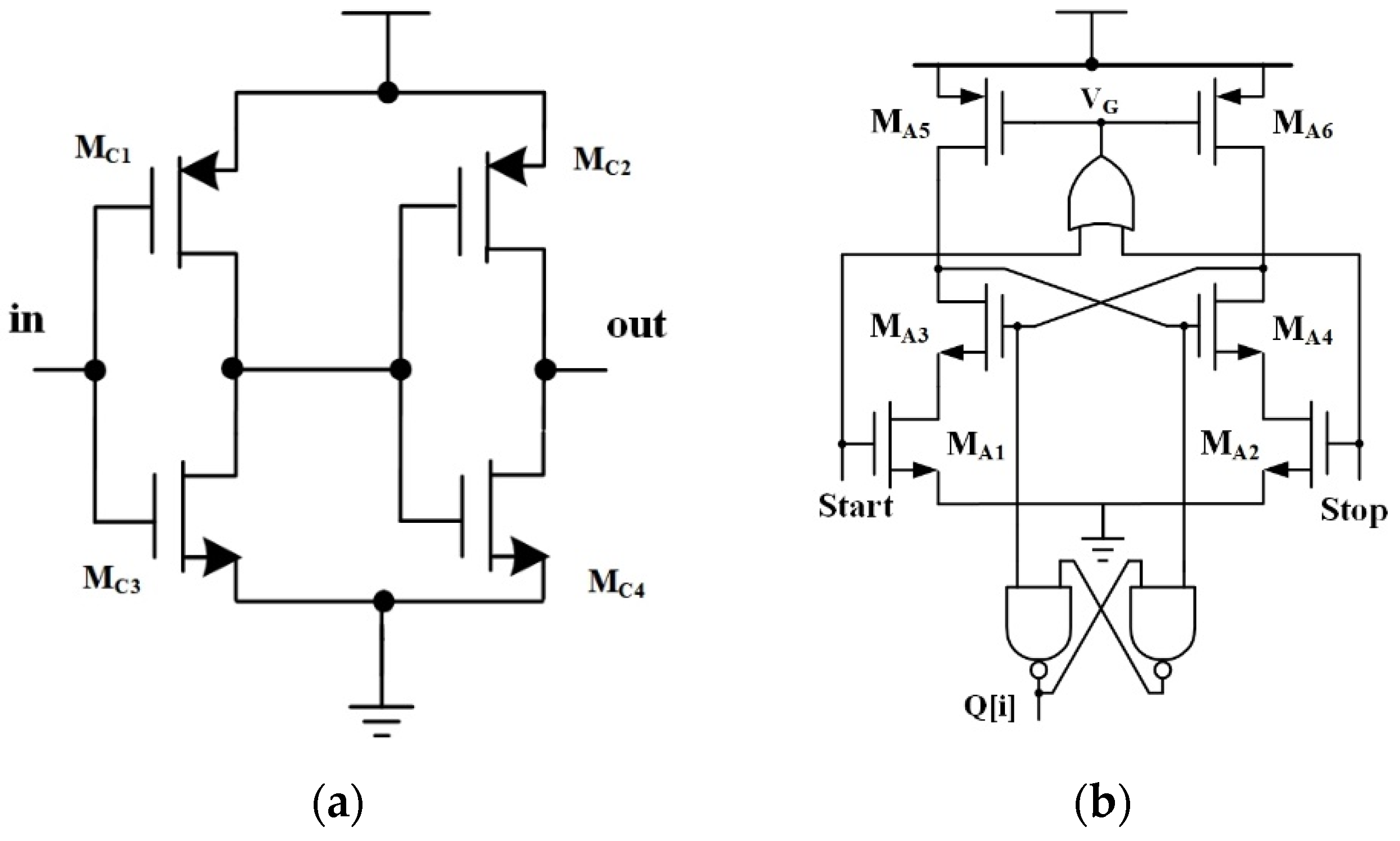

In the range of the temperature measurement, the propagation delay of the sensing module has a part of offset. If this signal is directly quantized by a TDC, it will greatly increase the number of the delay units in the TDC and furthermore lead to an additional area and a longer conversion time, which increases the effective power and the area of the sensor and is not suitable for the BIoT applications. To solve this problem, an offset compensator is used to generate a delay signal with low temperature sensitivity to compensate the offset part and the structure is shown in

Figure 3.

In order to reduce the power consumption of the bias circuit in the offset compensator, the bias circuit works in sub-threshold region. The drain current of a MOSFET operating in sub-threshold region is shown as

where

n is the sub-threshold slope and it is larger than one under the normal circumstances.

VT is the thermal voltage, and its relationship with temperature is

when

VDS ≥ 4

VT, the Equation (11) can be simplified as

As shown in

Figure 3, the offset compensator consists of four MOSFETs and delay units,

MB1,

MB2, and

MB3 are working in sub-threshold region, and

MB2 and

MB3 have the same size. According to Equation (13), the

IBias and

VBias are shown as

In the offset compensator, M2 and M3 have the same size. Therefore,

With the same CMOS process, the temperature coefficients of VTH1 and VTH2 are approximately same. Therefore, the temperature characteristics of VBias is determined by VT. By changing the size of MB1 and MB2, VBias that is proportional to temperature is generated. For delay units in the offset compensator, choosing MOSFETs with a longer channel length can increase the propagation time. According to Equation (8), this means the current of the delay units in the offset compensator is inversely proportional to temperature. With the control of VBias, the drain current of MB4 will be positively correlate with the temperature, thereby this can reduce the temperature sensitivity of propagation delay of the offset compensator. Note that the linearity of the offset compensator is more important than the temperature sensitivity of the offset compensator, because the sensitivity is not required to be exactly zero. In this work, the slope of the delay-temperature curve in the sensing module is 0.141 ns/°C, where that in the offset compensator is 0.059 ns/°C, which is translated to a 0.081 ns/°C slope of the temperature sensor.

4. Experimental Results

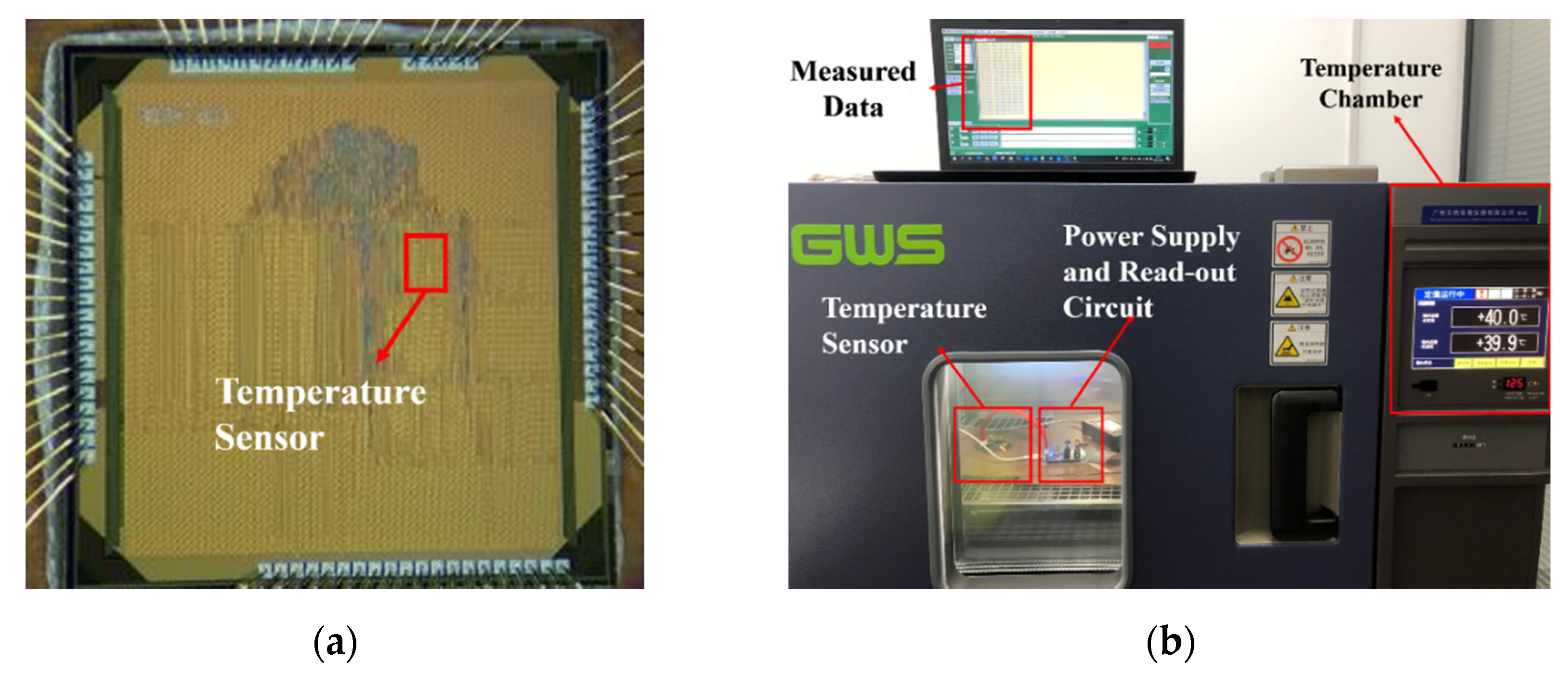

The proposed temperature sensor was fabricated in a TSMC 40-nm standard CMOS technology and worked at a 0.6 V supply voltage. The total area of this sensor is 0.05 mm

2, as shown in the die micrograph in

Figure 16a. A photograph of the testing environment is shown in

Figure 16b. The sensor was mounted on a test board and placed in a temperature chamber manufactured by GWS. The test board was connected to a power supply and read-out circuit. A computer placed outside the temperature chamber was connected to the read-out circuit, and the output code was read every 10 °C.

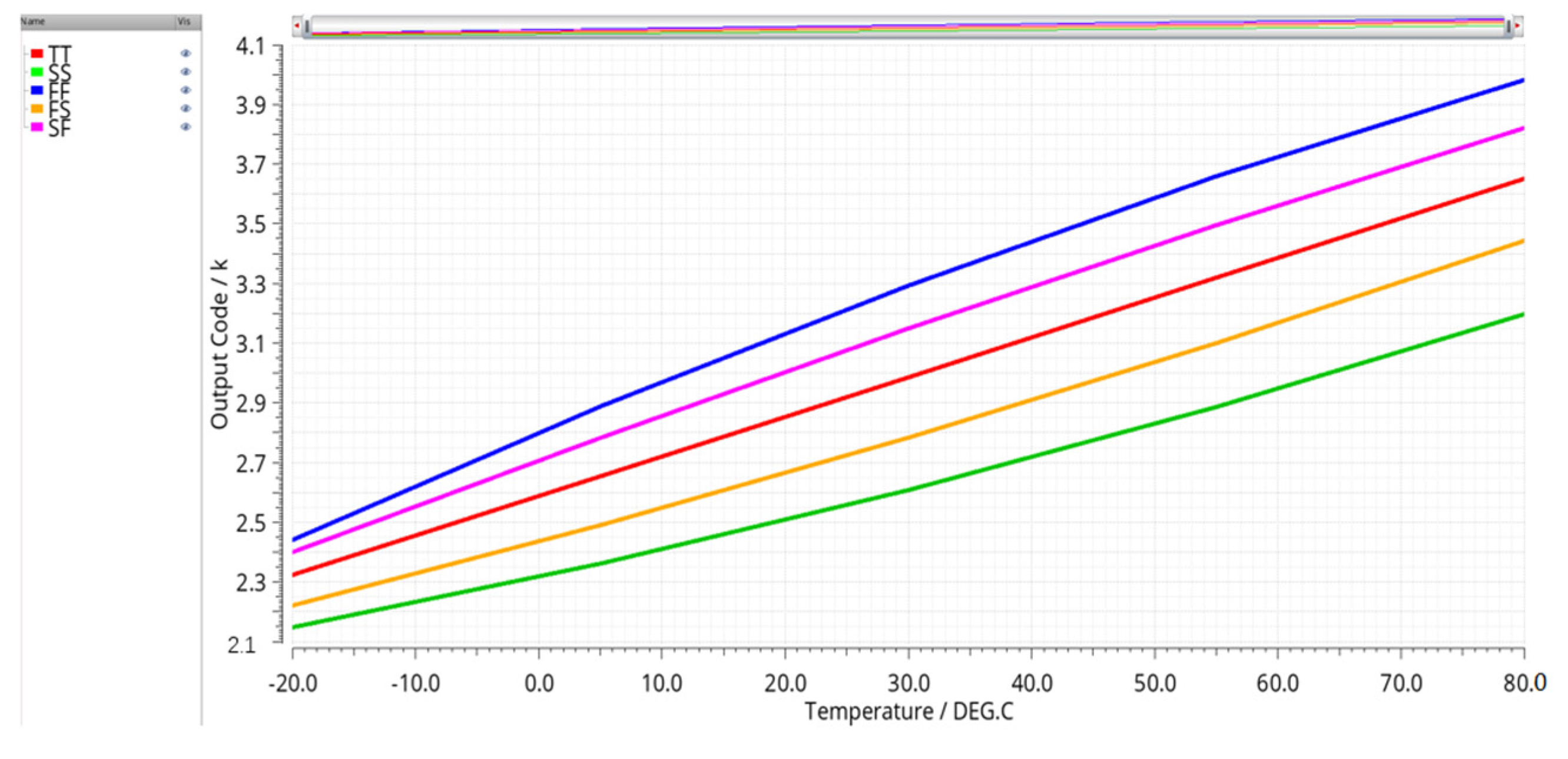

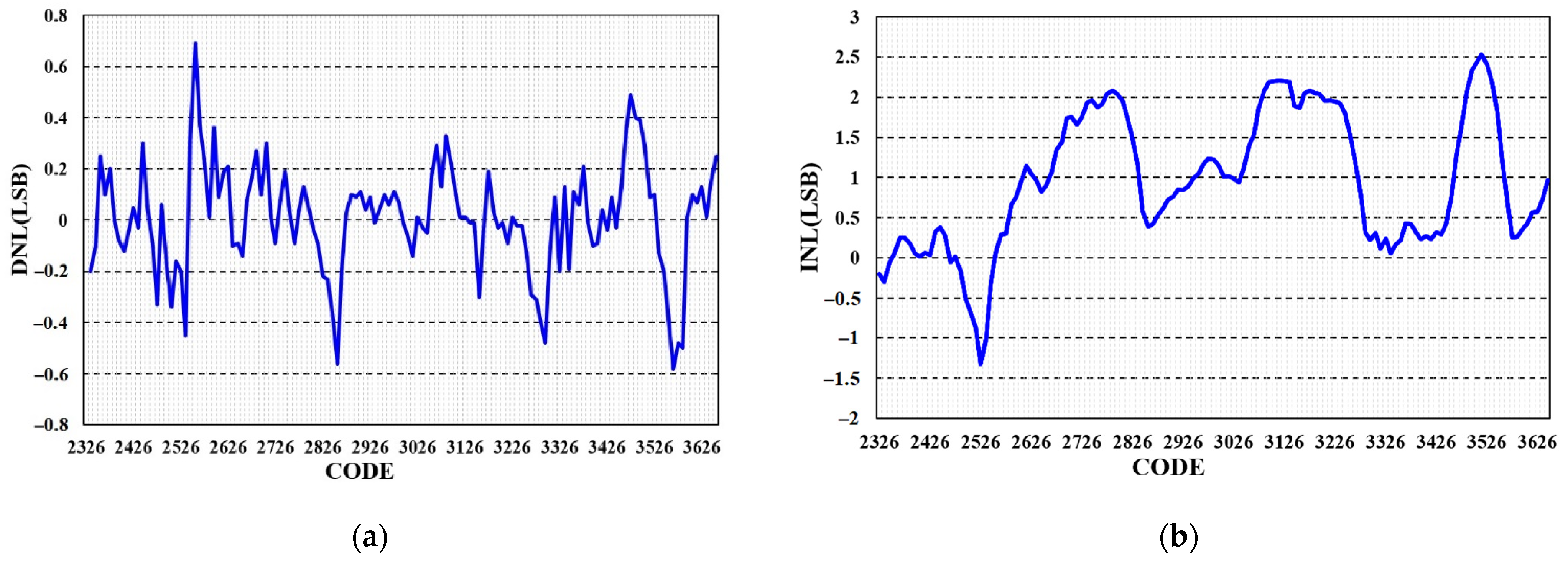

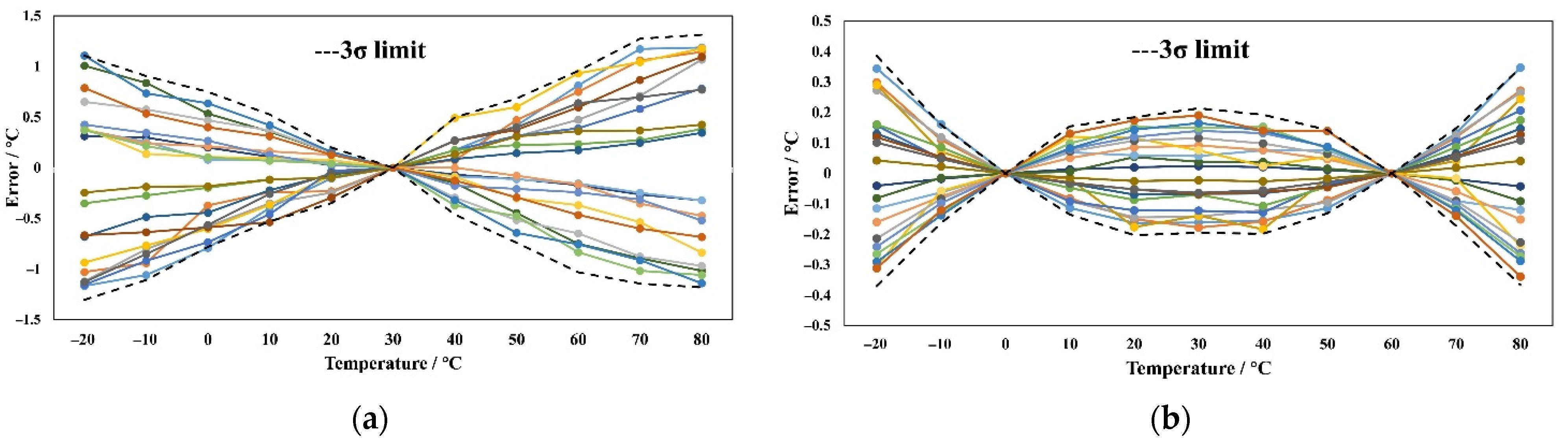

The

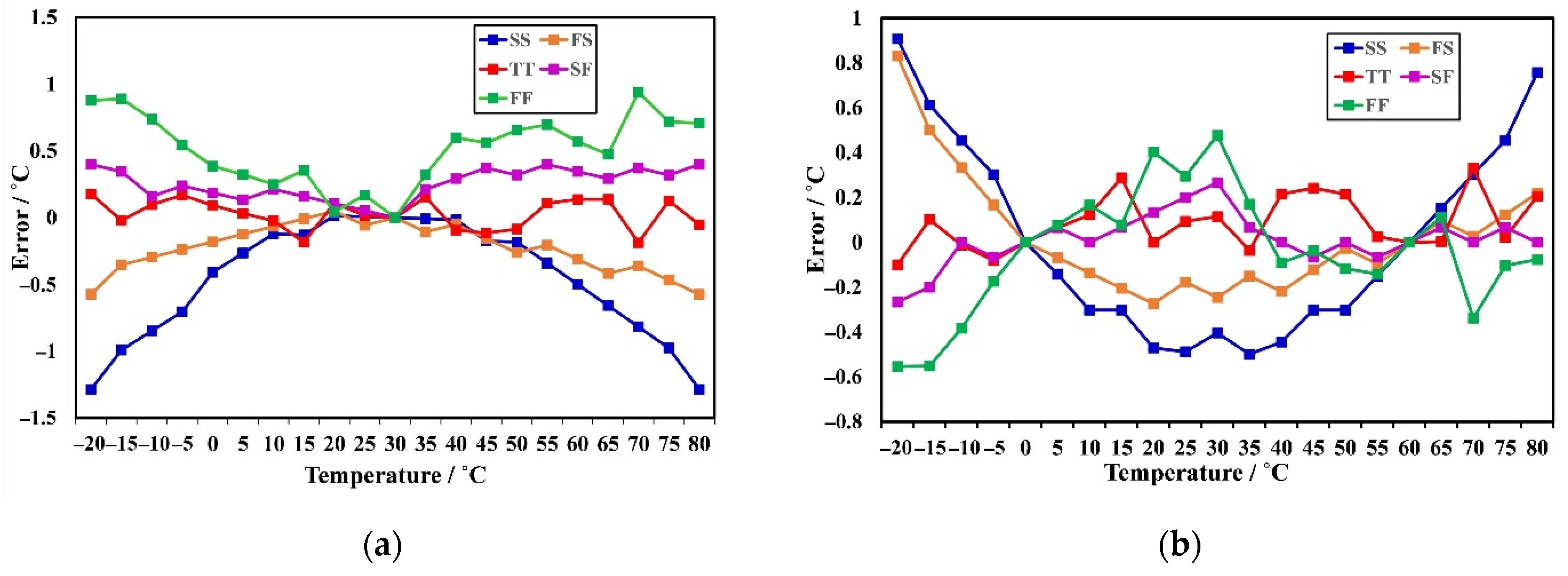

Figure 17 shows the simulated output results and the measured output results with different PGTA gains. When M = 8, 20 samples from one wafer are tested in the temperature chamber over the temperature range of −20~80 °C. The error measurements of the proposed temperature sensor with one-point and two-point calibration are shown in

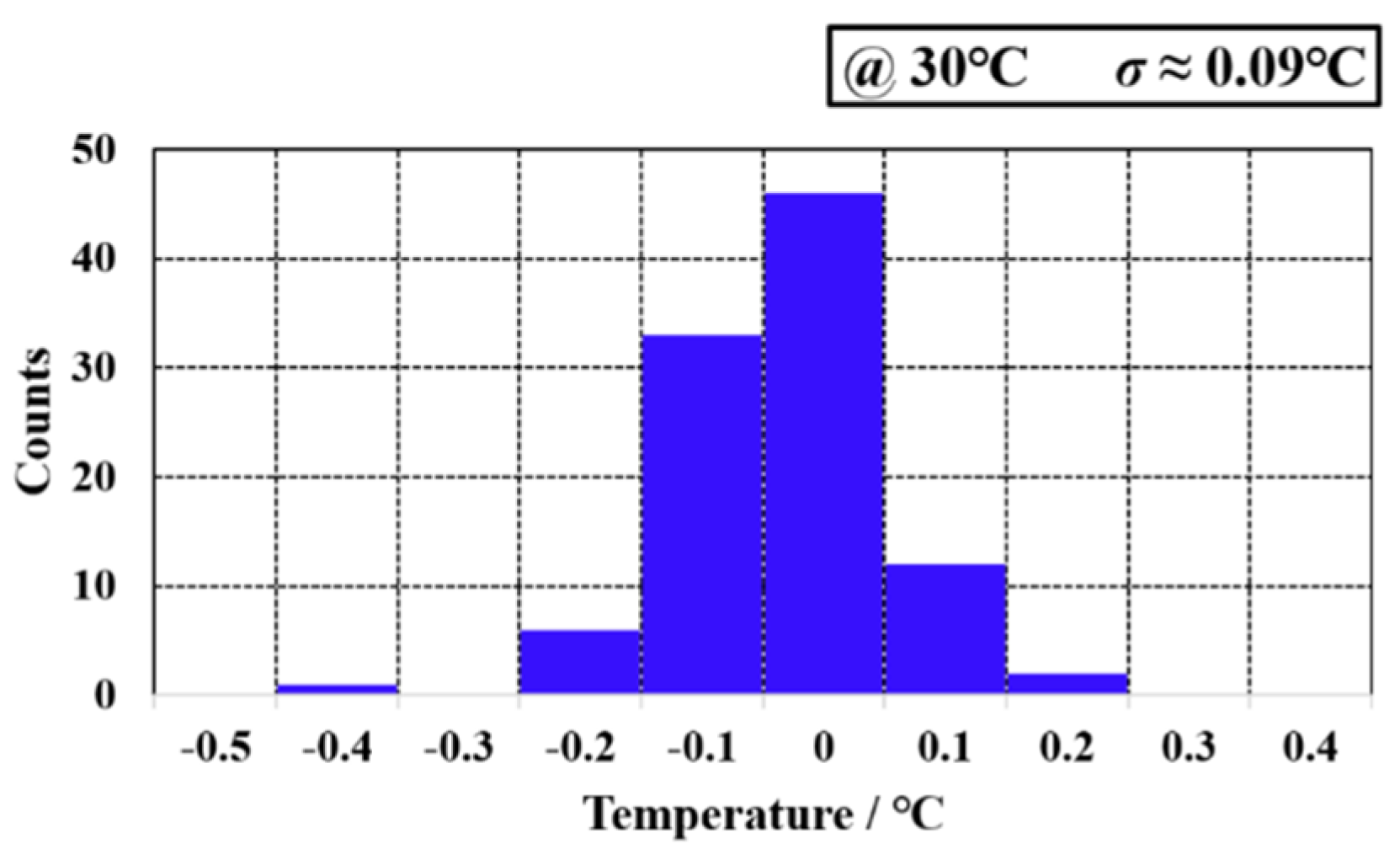

Figure 18a,b, respectively. With one-point calibration at 30 °C, the measured peak-to-peak errors is ±1.3 °C. In the case of a two-point calibration, the calibration temperatures are selected to 0 °C and 60 °C, and the measured peak-to-peak nonlinearity is ±0.39 °C. The sensor resolution is obtained by measuring the spread of sensor error at 30 °C, as shown in

Figure 19. The standard deviation of the measurement is about 0.09 °C.

Table 1 summarizes the measured temperature sensor performance and compares it with other state-of-the-art works. Reference [

16] has the highest resolution and a high FoM at the cost of long conversion time and large area. Reference [

17] has a similar high resolution with Reference [

16] and small area at the cost of high power and long conversion time. This work achieves the best FoM of 0.048 pJ·K

2 thanks to the shortest conversion time of 1.3 µs.

5. Conclusions

We proposed a CMOS time-domain temperature sensor in this paper. The relationship between the temperature characteristic of propagation delay and the size of a delay unit is analyzed. The design of the channel length of MOSFET can determine the positive or negative temperature coefficient of the propagation delay. Based on this principle, the temperature is converted into a PTAP time domain signal, and then a pipeline TDC is used to quantize the signal. A PGTA is proposed to achieve linear programmable gain. In order to avoid introducing additional errors and to improve the linearity of the TDC output, the circuits in the TDC are designed with low temperature sensitivity. Thus, this temperature sensor does not need any curvature corrections.

Based on the analysis and design, a temperature sensor had been fabricated in a 40-nm CMOS technology. A 90 mk resolution at an eight times PGTA gain was achieved. The conversion time is only 1.3 µs, and a FoM of 48 fJ·K2 is obtained.

For most BIoT applications, the temperature does not change fast, therefore, a low sampling rate of the temperature sensor can meet the demand of the system that works at a duty-cycling mode. In the sleep mode, the sensor only draw 31 nA at 40 °C. At 10 conversions/s and Tconv = 1.3 µs, the effective average power consumption is only 18.6 nW. In order to apply this sensor to different applications, a higher-stages of sensing module can be used to increase the range of propagation delay varying with temperature to achieve a higher resolution.