Study on Multiple Input Asymmetric Boost Converters with Simultaneous and Sequential Triggering

Abstract

1. Introduction

- An output voltage stability analysis for an n paralleled boost stages converter operation with MPPT control combined with other controllers.

- Formulations for the steady-state voltage gain and the output voltage ripple.

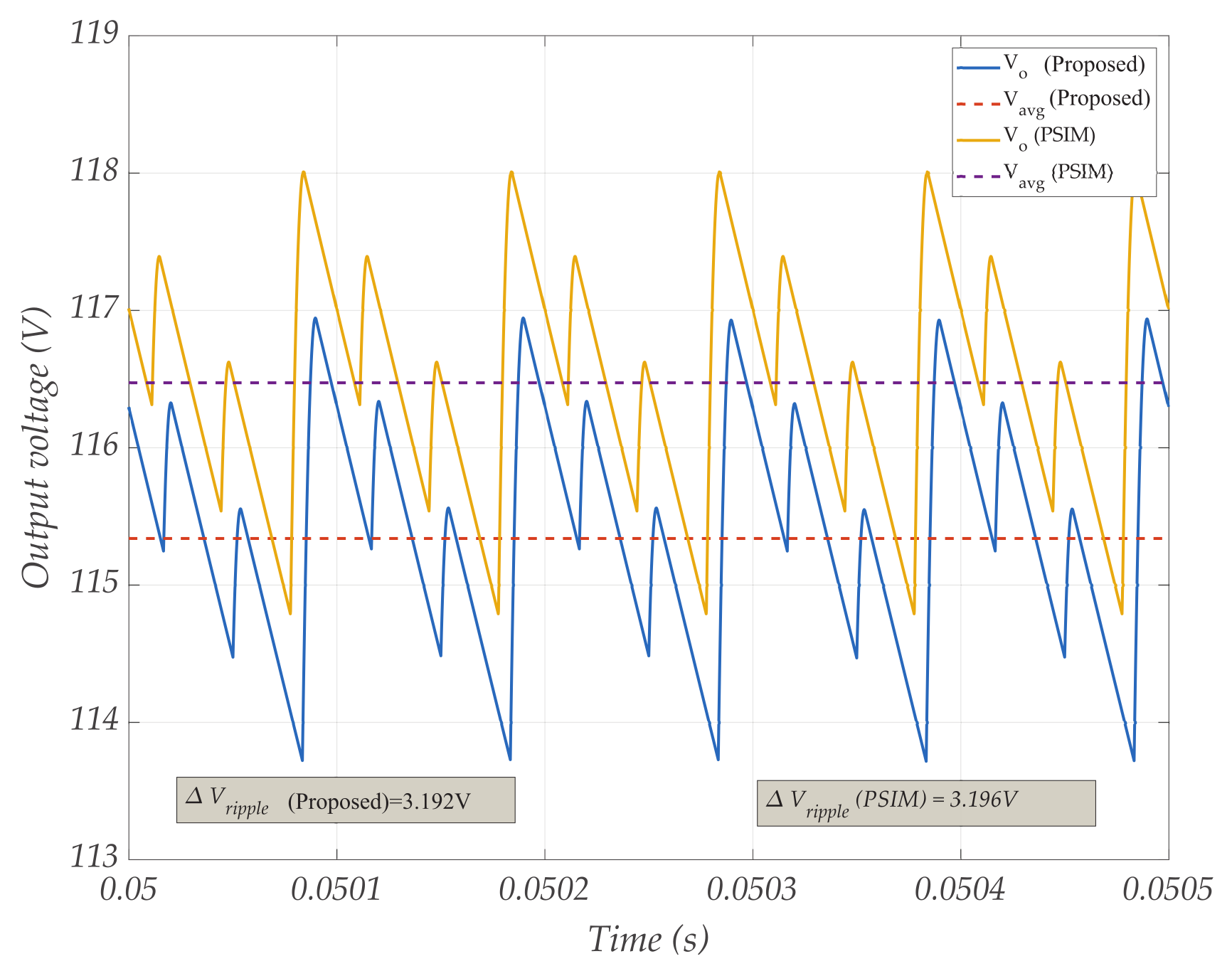

- An approach to design an easy-to-implement, versatile, and stable boost-type paralleled MIC with n unequal stages and sources and independent controllers (MPPT/other). This strategy allows different energy sources to feed a resistive load and decouple the paralleled boost stages without extra components, avoiding circulating currents with a low-cost implementation. The output voltage and current ripples are diminished in comparison with simultaneous triggering schemes; an experimental exemplification of the MIC design is provided.

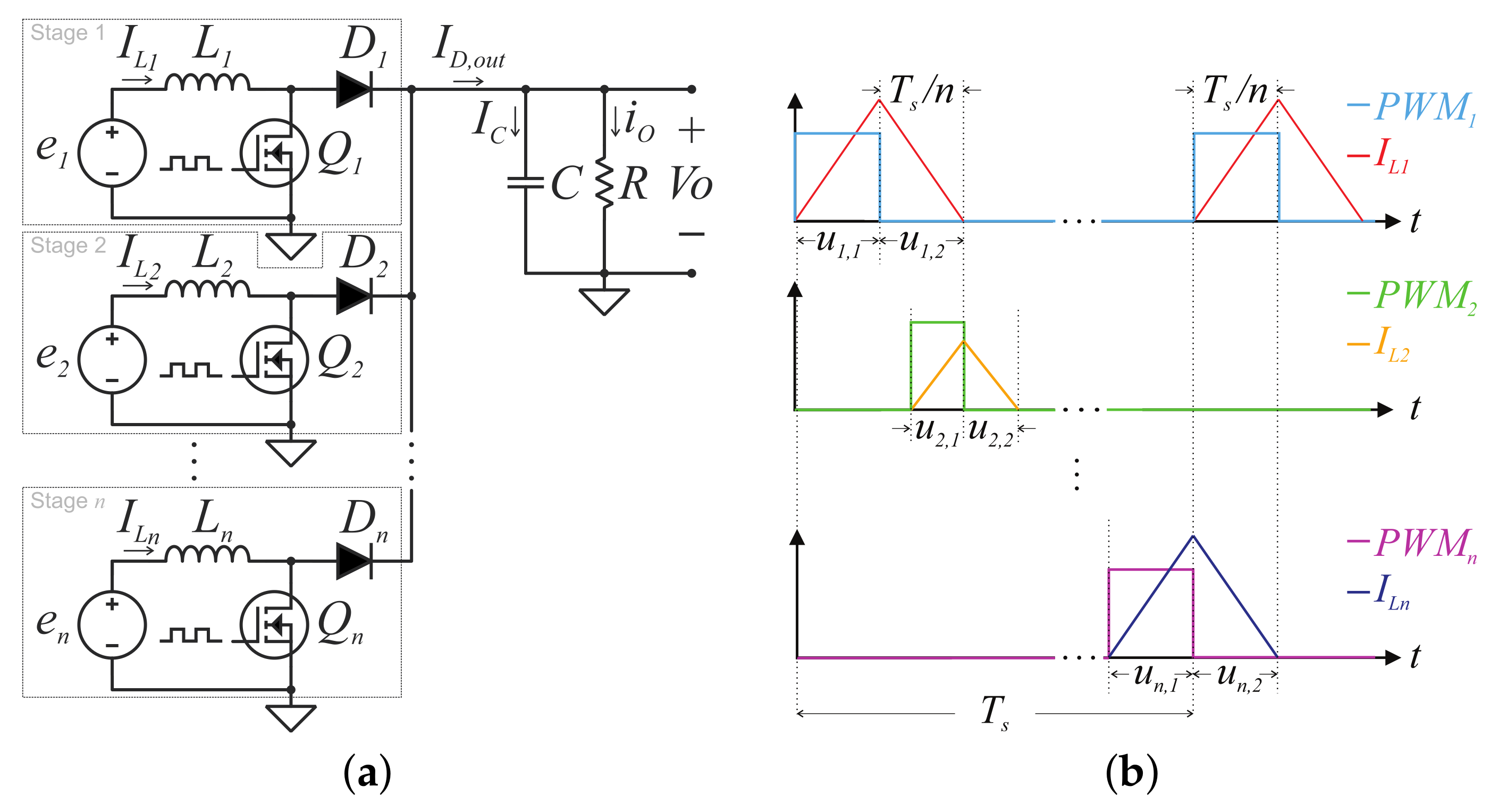

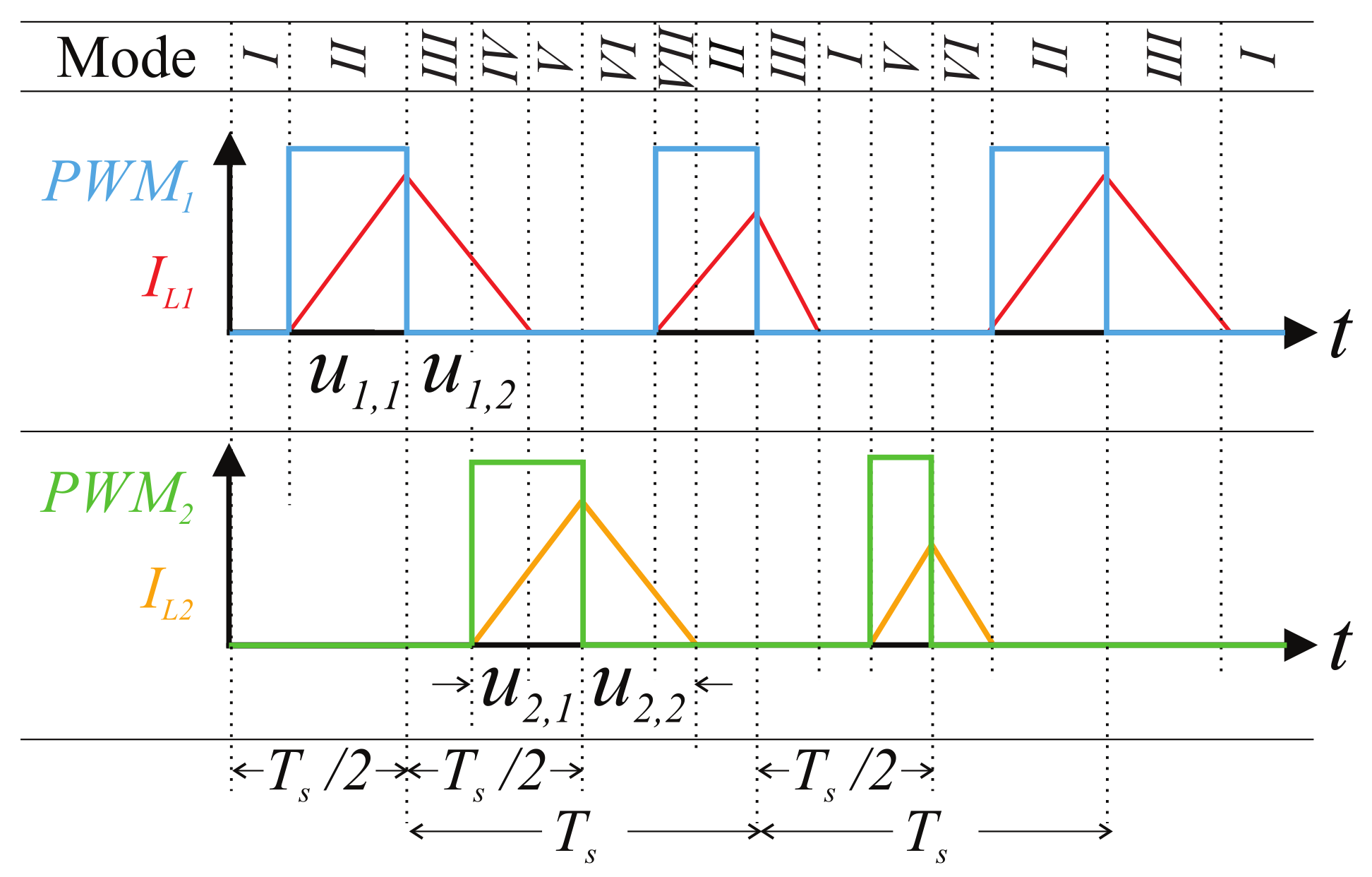

2. Paralleled-Boost-Converter, Dynamic Modeling, and Stability

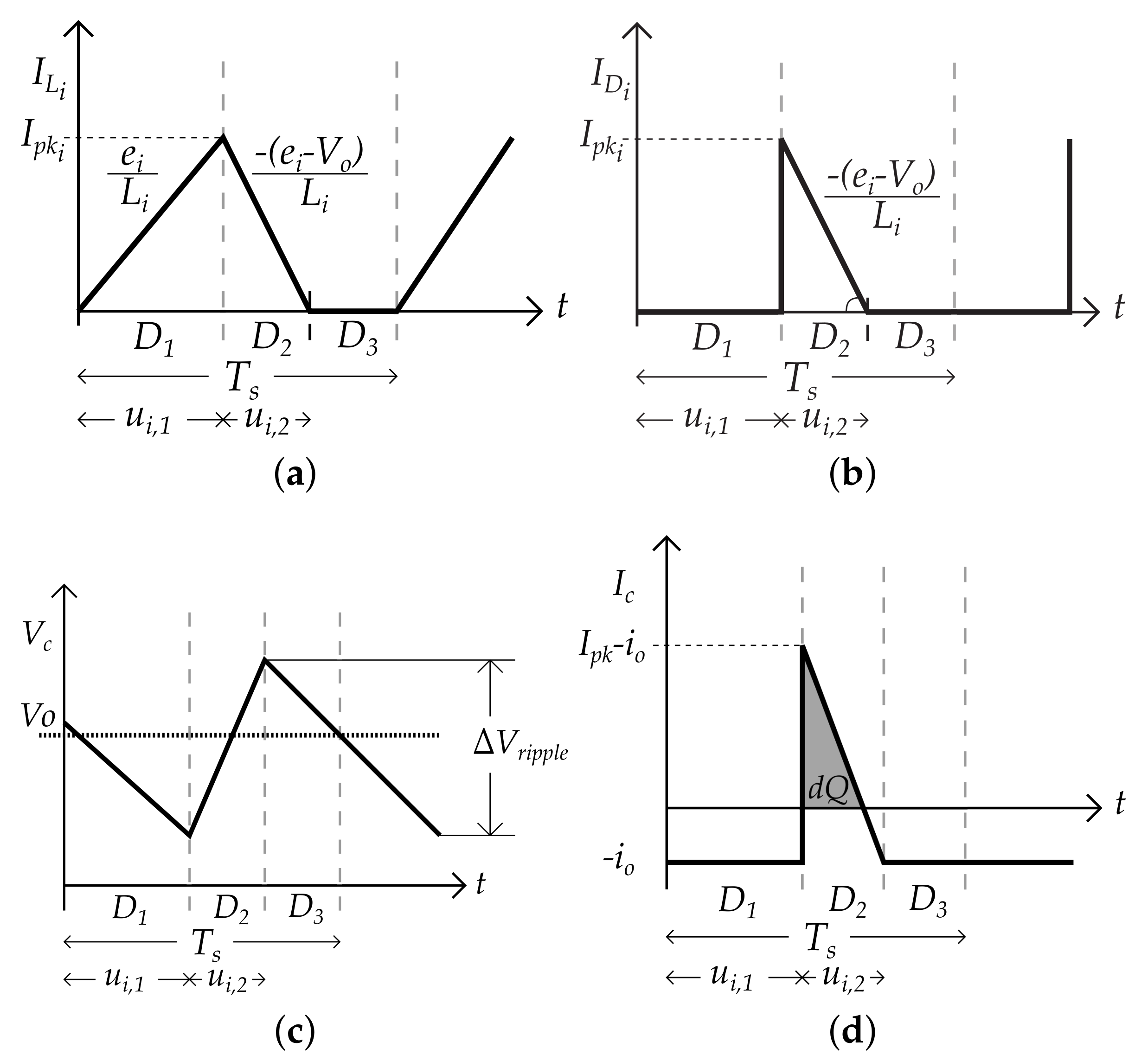

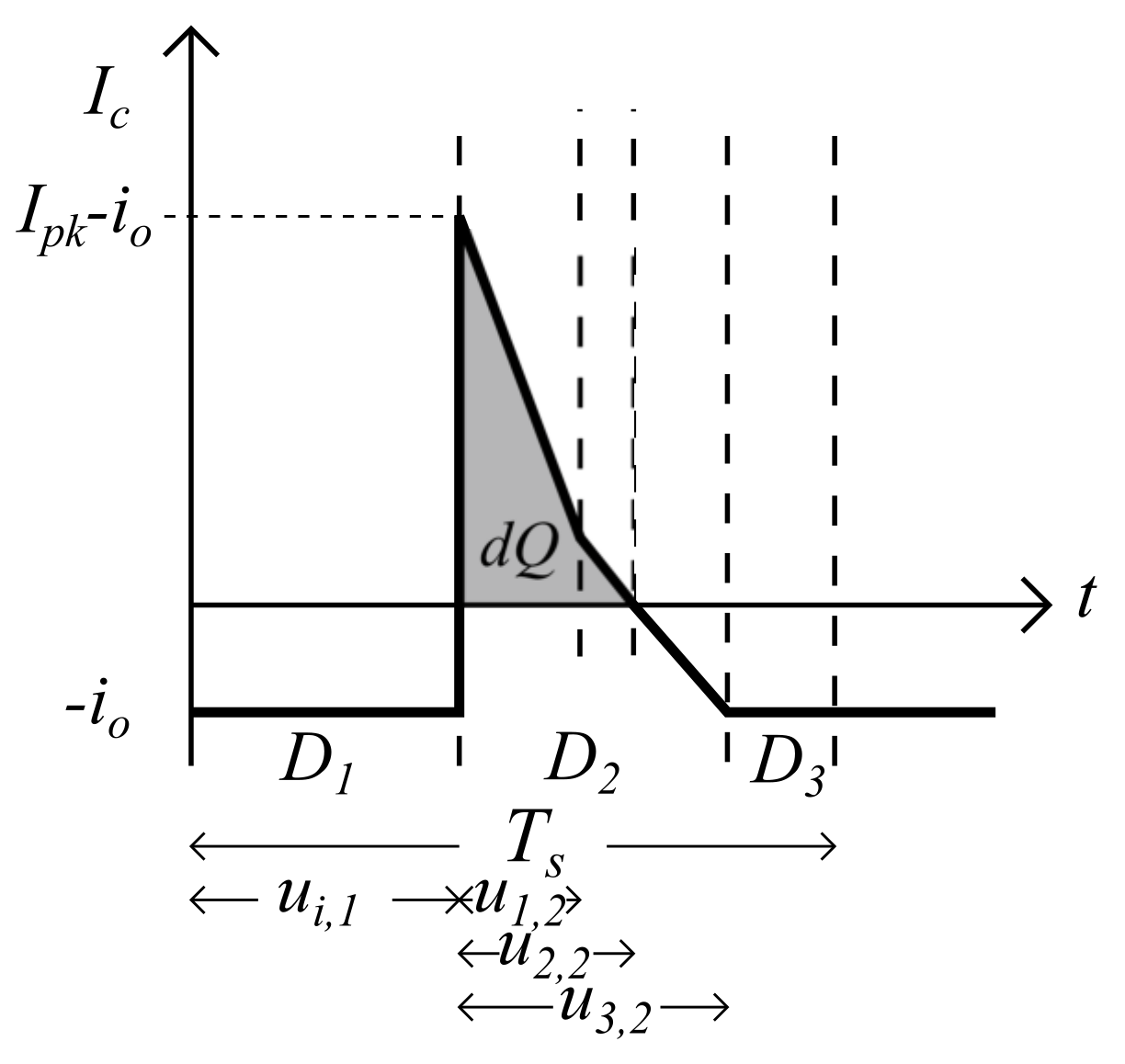

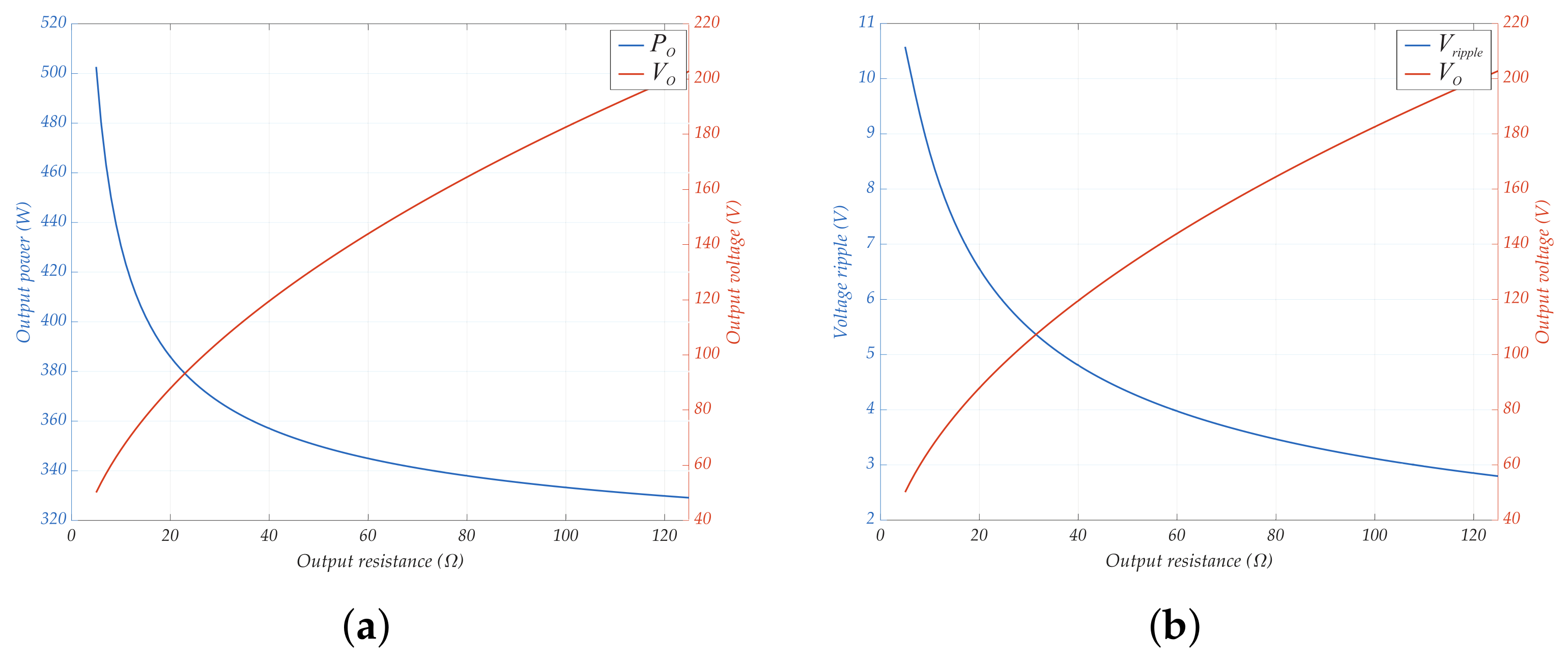

3. Steady-State Analysis

3.1. Averaged Output Voltage for the MISeC

3.2. Output Voltage Ripple for the MISeC

3.3. Average Output Voltage for the MISiC

3.4. Output Voltage Ripple for the MISiC

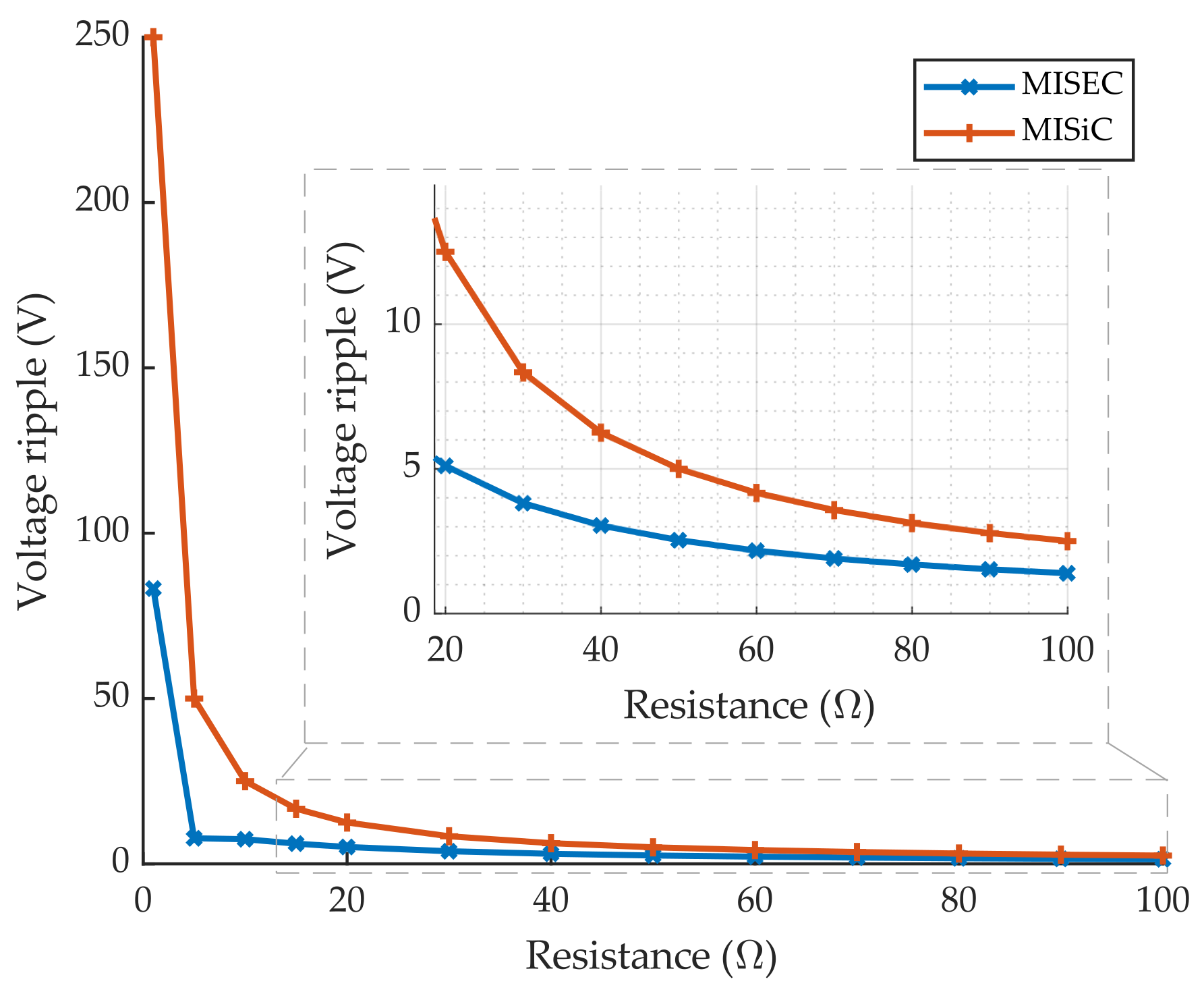

3.5. Analytic Ripple Comparison for Sequential and Simultaneous Triggering

4. Component Selection

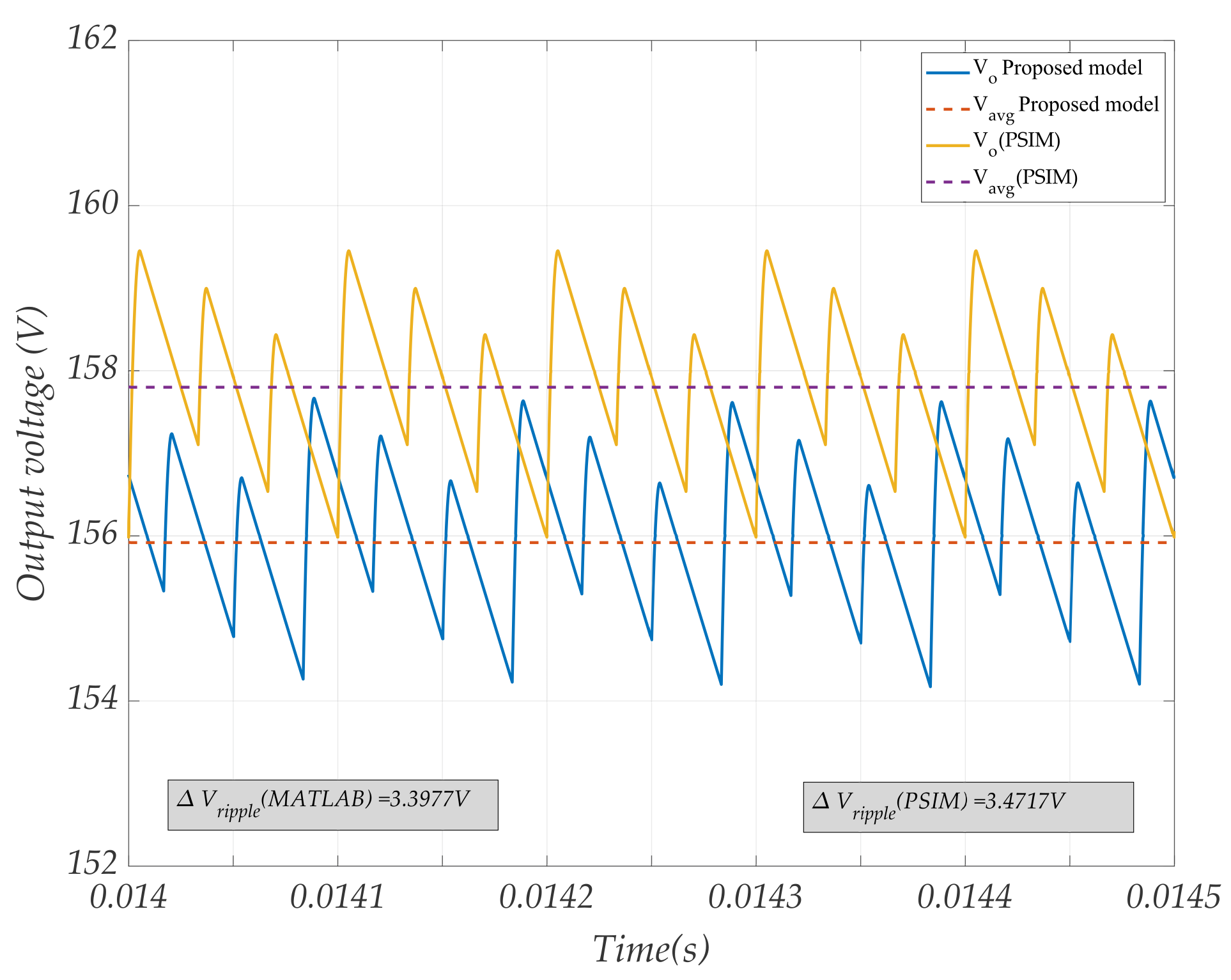

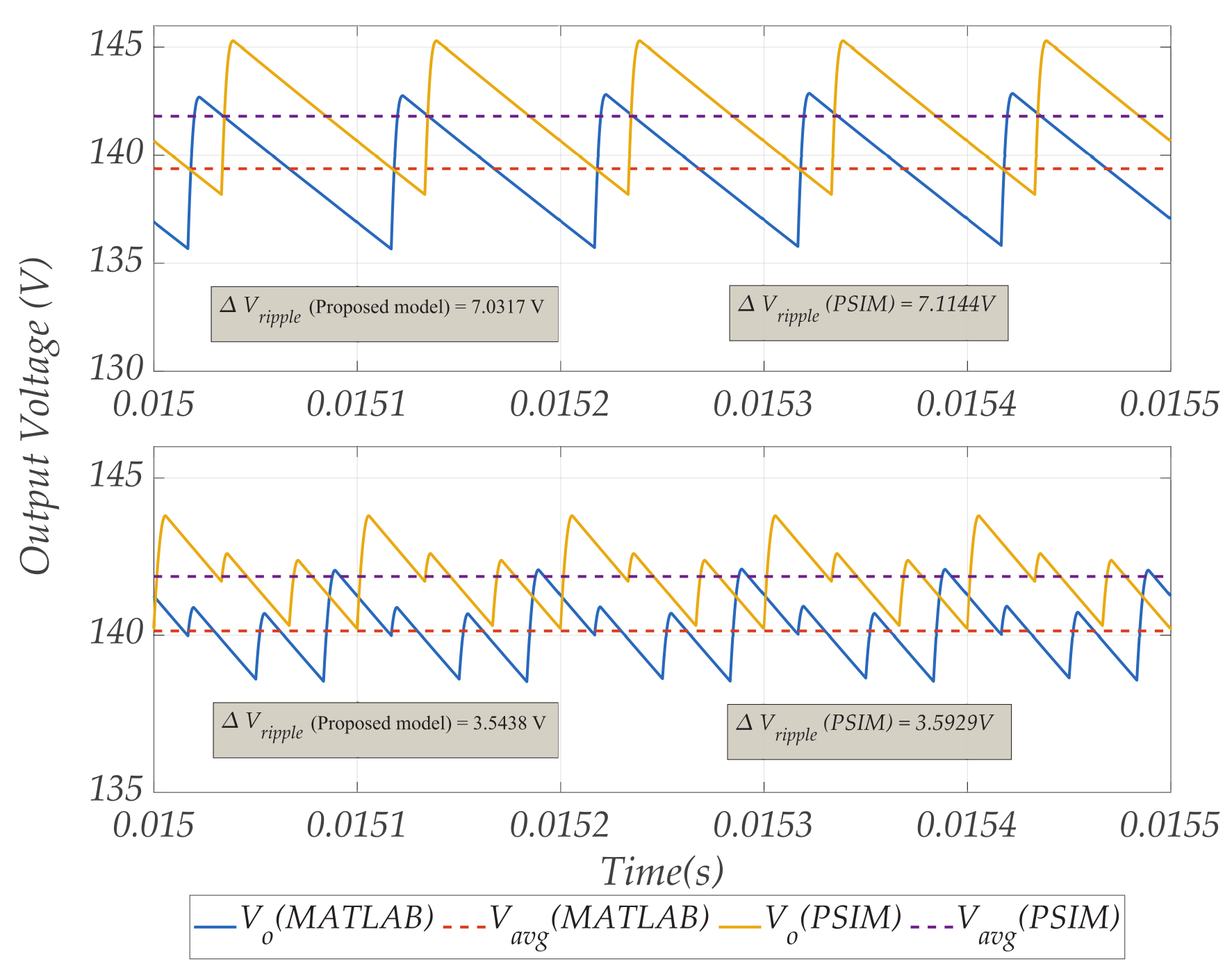

5. Numerical Validation of the Models

6. Experimental Validation

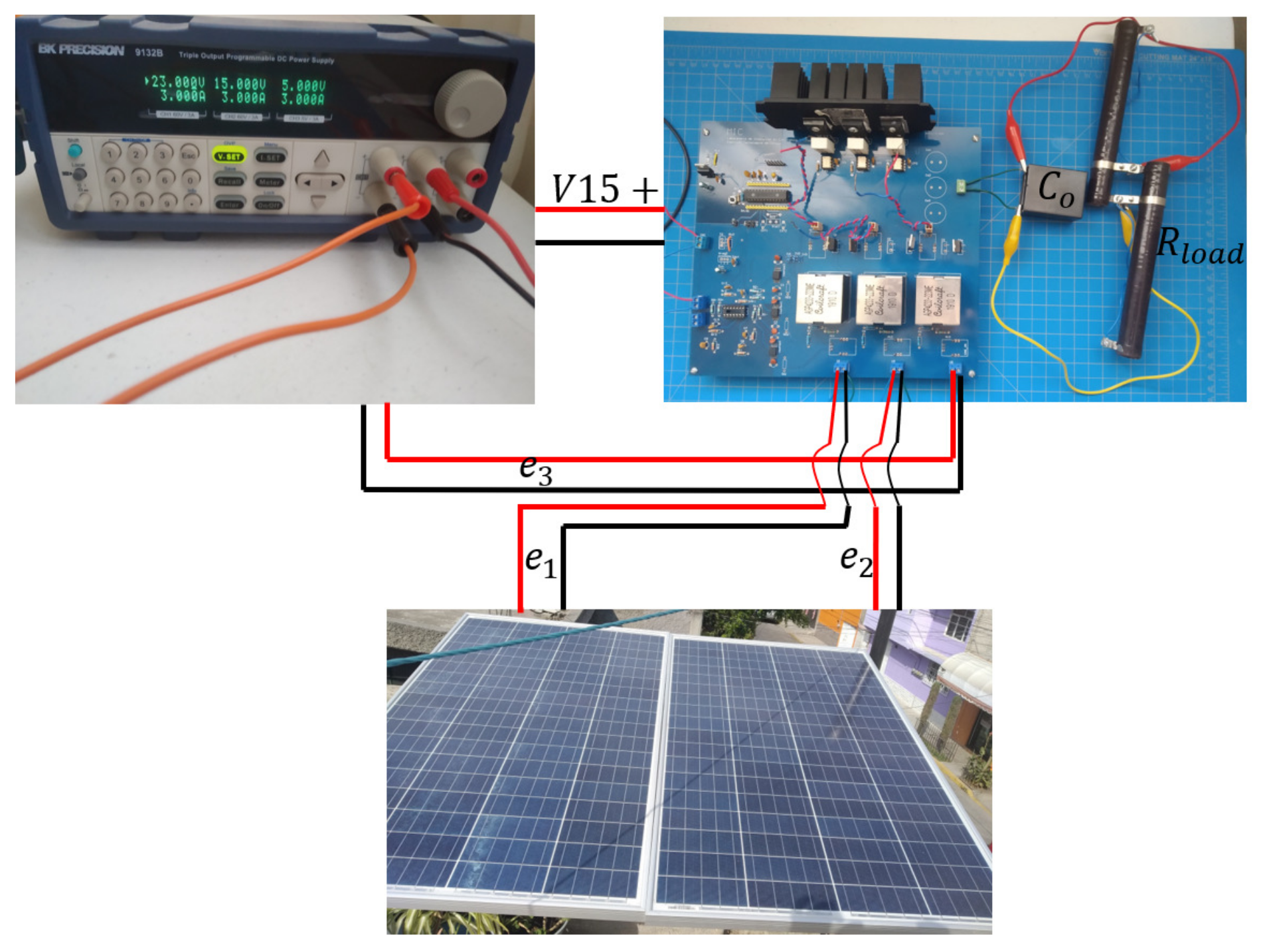

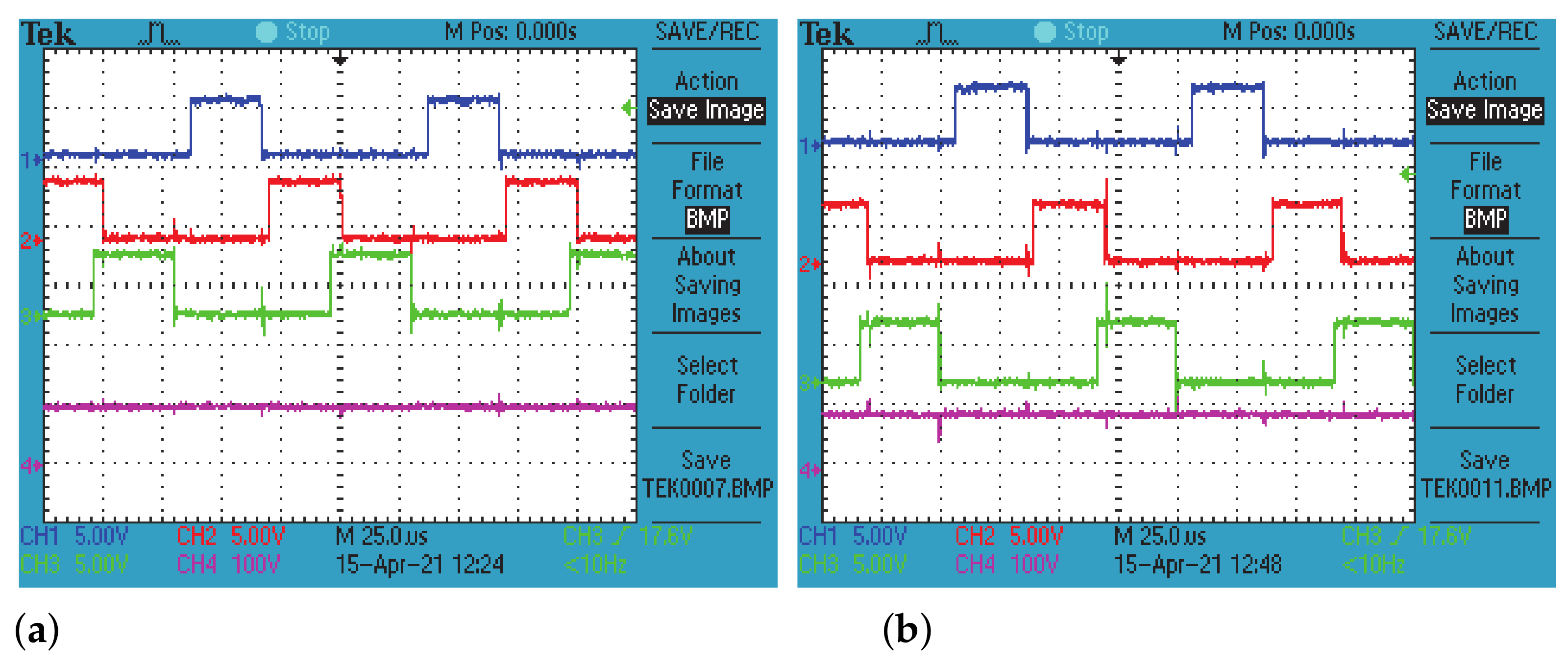

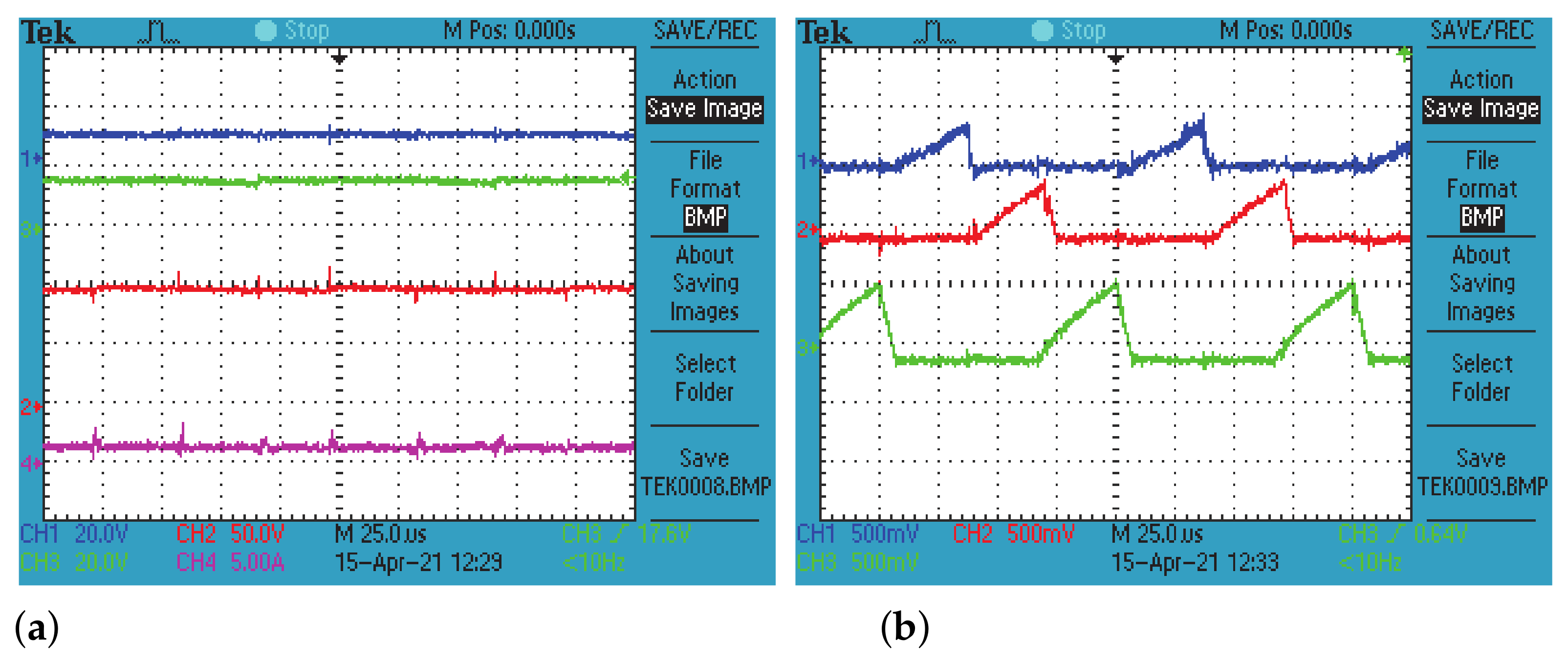

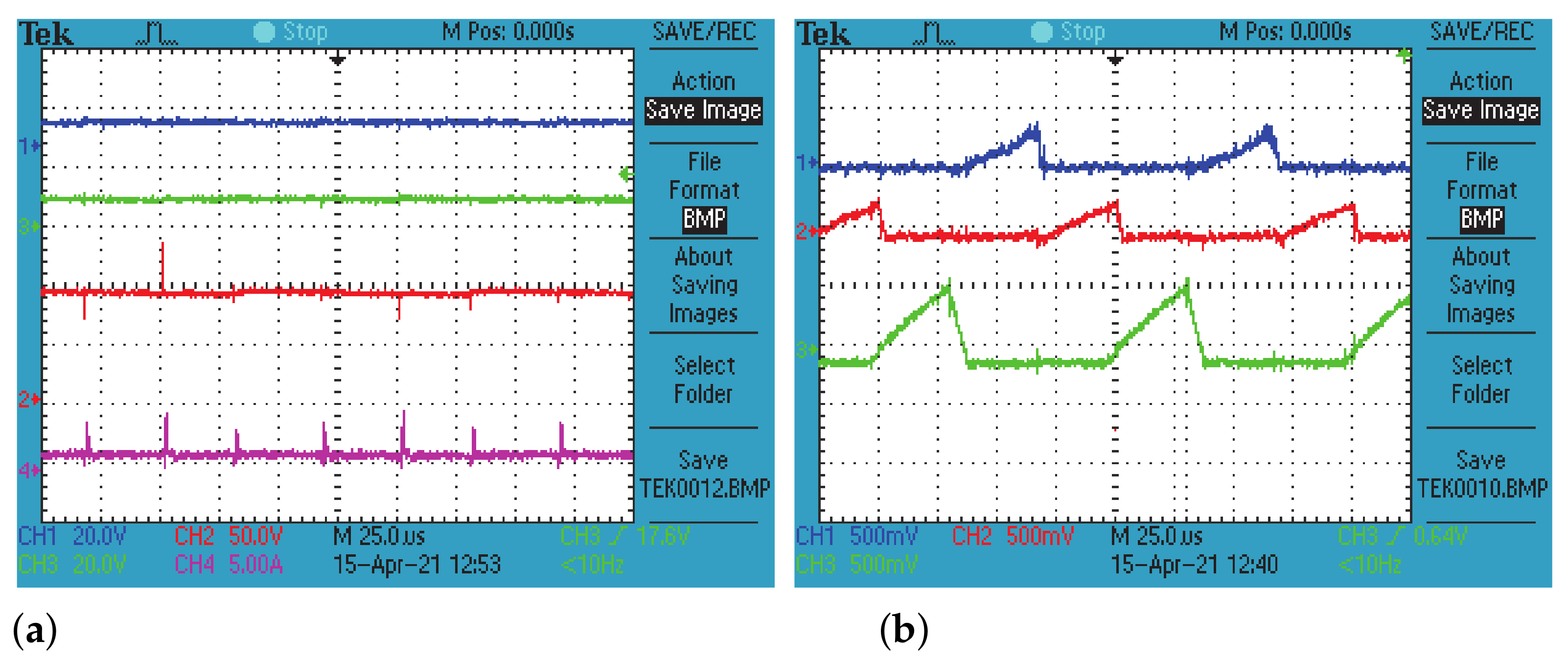

6.1. Experimental Setup

6.2. Controller Design

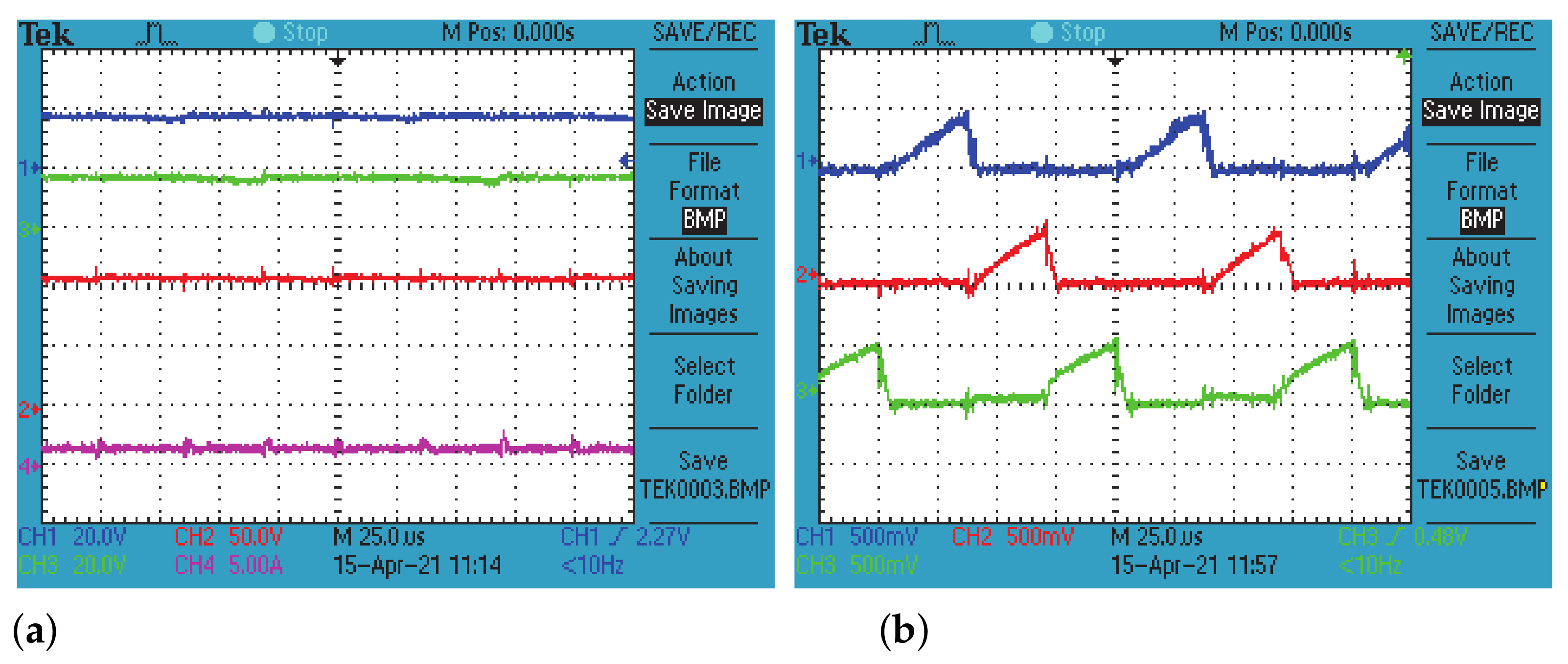

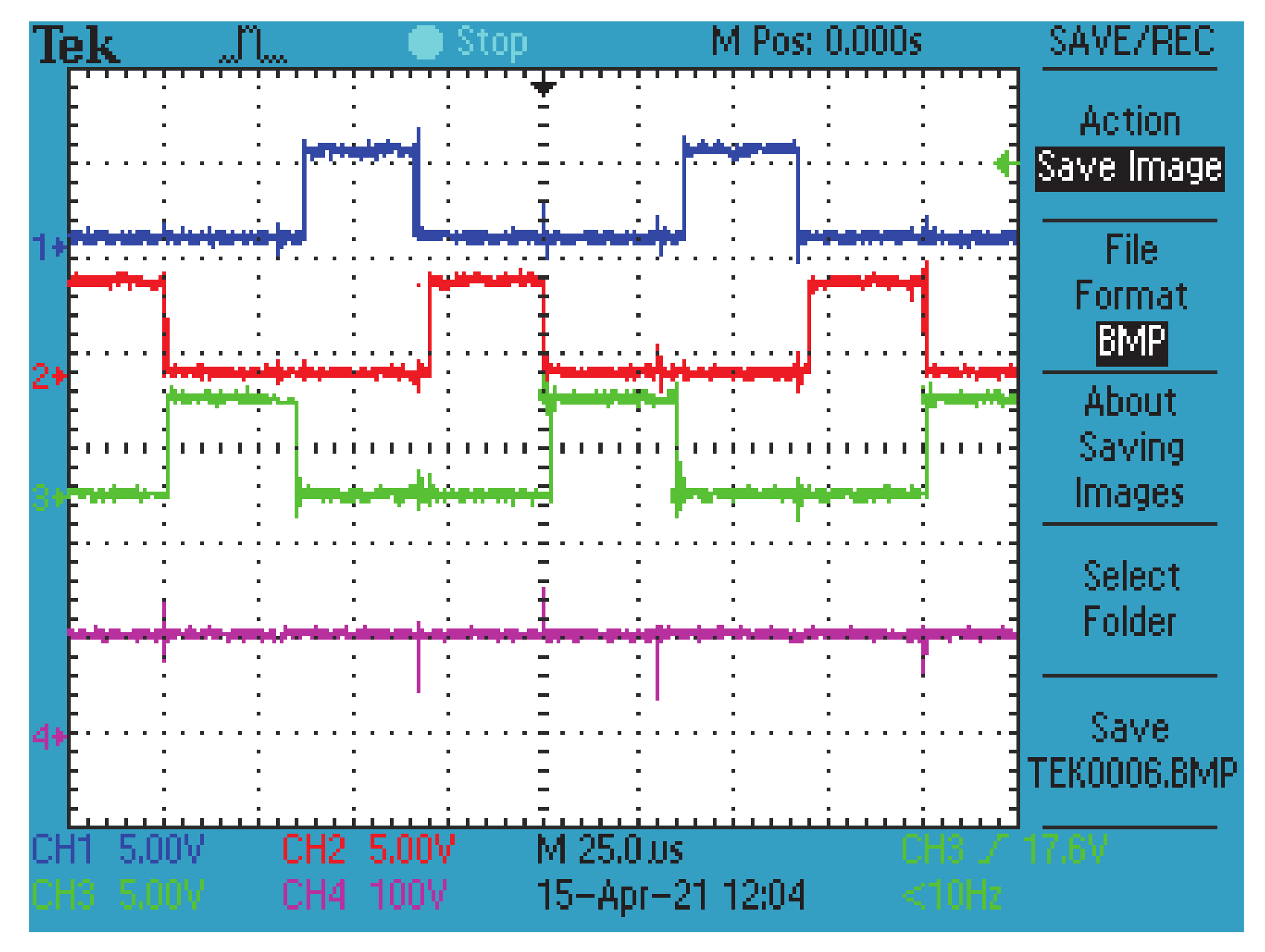

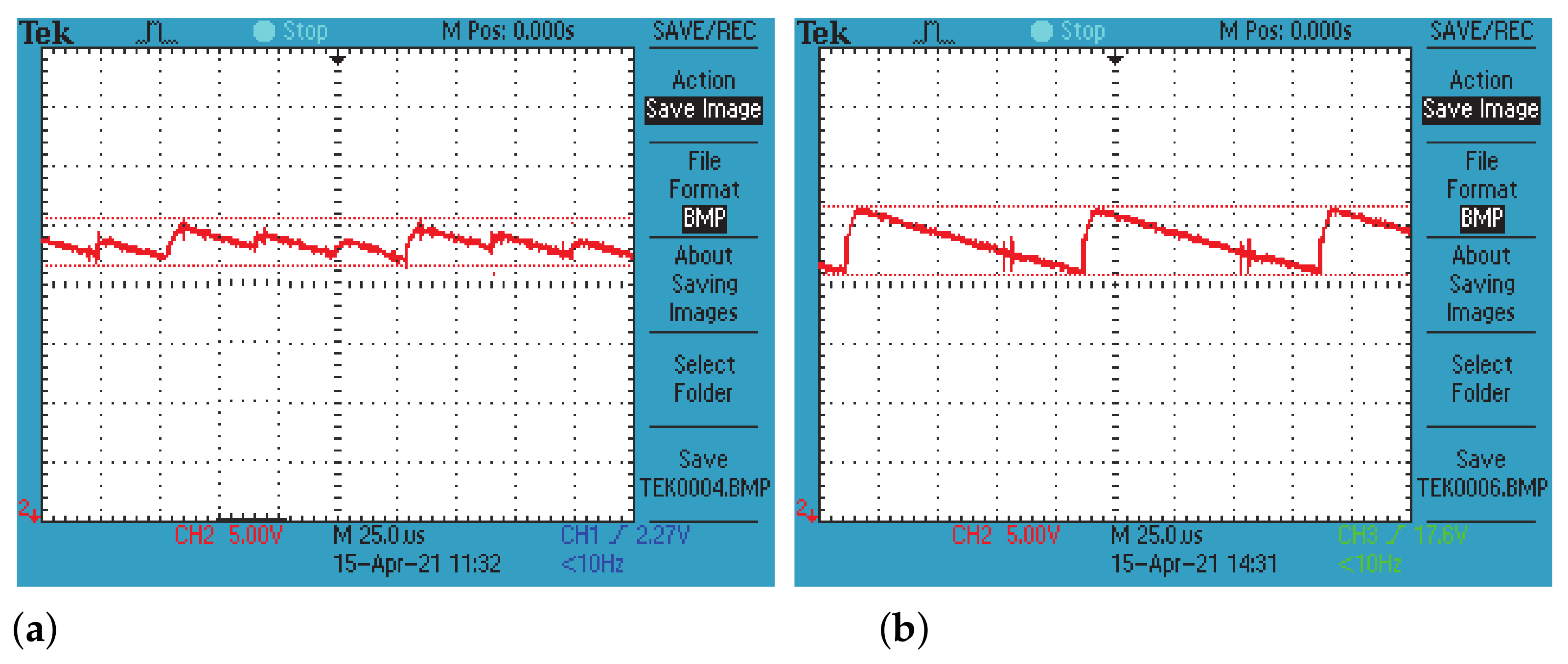

6.3. Experimental Tests

7. Discussion, Conclusions, and Future Work

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Knudsen, T.; Bak, T.; Svenstrup, M. Survey of wind farm control—Power and fatigue optimization. Wind Energy 2015, 18, 1333–1351. [Google Scholar] [CrossRef]

- de Alegría, I.M.; Andreu, J.; Martín, J.L.; Ibanez, P.; Villate, J.L.; Camblong, H. Connection requirements for wind farms: A survey on technical requierements and regulation. Renew. Sustain. Energy Rev. 2007, 11, 1858–1872. [Google Scholar] [CrossRef]

- Nugent, D.; Sovacool, B.K. Assessing the lifecycle greenhouse gas emissions from solar PV and wind energy: A critical meta-survey. Energy Policy 2014, 65, 229–244. [Google Scholar] [CrossRef]

- Cicia, G.; Cembalo, L.; Del Giudice, T.; Palladino, A. Fossil energy versus nuclear, wind, solar and agricultural biomass: Insights from an Italian national survey. Energy Policy 2012, 42, 59–66. [Google Scholar] [CrossRef]

- Chen, S.; Zhang, J.; Wang, L.; Zhang, H.; Li, L. Evaluation of Power Quality and Reliability of Distributed Generation in Smart Grid. In Proceedings of the IOP Conference Series: Earth and Environmental Science, Kamakura, Japan, 10–11 October 2020; IOP Publishing: Bristol, UK, 2020; Volume 632, pp. 1–7. [Google Scholar]

- Karthikumar, K.; Karthik, K.; Karunanithi, K.; Chandrasekar, P.; Sathyanathan, P.; Prakash, S.V.J. SSA-RBFNN strategy for optimum framework for energy management in Grid-Connected smart grid infrastructure modeling. Mater. Today Proc. 2021. [Google Scholar] [CrossRef]

- Anwar, M.; Naeem, A.; Gul, H.; Arif, A.; Fareed, S.; Javaid, N. Electricity Price and Load Forecasting Using Data Analytics in Smart Grid: A Survey. In Proceedings of the International Conference on Emerging Internet, Data & Web Technologies, Kitakyushu, Japan, 24–26 February 2020; pp. 427–439. [Google Scholar]

- Al-Badi, A.H.; Ahshan, R.; Hosseinzadeh, N.; Ghorbani, R.; Hossain, E. Survey of Smart Grid Concepts and Technological Demonstrations Worldwide Emphasizing on the Oman Perspective. Appl. Syst. Innov. 2020, 3, 5. [Google Scholar] [CrossRef]

- Alishah, R.S.; Yahya Hassani, M.; Hosseini, S.H.; Bertilsson, K.; Babalou, M. Analysis and Design of a New Extendable SEPIC Converter with High Voltage Gain and Reduced Components for Photovoltaic Applications. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 12–14 February 2019; pp. 492–497. [Google Scholar] [CrossRef]

- Babalou, M.; Dezhbord, M.; Alishah, R.S.; Hossein Hosseini, S. A Soft-Switched Ultra High Gain DC-DC Converter with Reduced Stress voltage on Semiconductors. In Proceedings of the 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), Shiraz, Iran, 12–14 February 2019; pp. 677–682. [Google Scholar] [CrossRef]

- Mazumder, S.; Nayfeh, A.H.; Borojevi, C.D. Development of integral-variable-structure control schemes for parallel-buck and parallel-boost DC-DC converters. In Proceedings of the INTELEC. Twenty-Second International Telecommunications Energy Conference (Cat. No. 00CH37131), Phoenix, AZ, USA, 10–14 September 2000; pp. 82–89. [Google Scholar]

- Cadirci, I.; Yafavi, A.; Ermiş, M. Unity power factor boost converter with phase shifted parallel IGBT operation for medium power applications. IEE Proc. Electr. Power Appl. 2002, 149, 237–244. [Google Scholar] [CrossRef]

- Lee, Y.J.; Emadi, A. Phase shift switching scheme for DC/DC boost converter with switches in parallel. In Proceedings of the 2008 IEEE Vehicle Power and Propulsion Conference, Harbin, China, 3–5 September 2008; pp. 1–6. [Google Scholar]

- Neacsu, D.O.; Bonnice, W.; Holmansky, E. On the small-signal modeling of parallel/interleaved buck/boost converters. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 2708–2713. [Google Scholar]

- El Fadil, H.; Giri, F.; Guerrero, J.M. Adaptive sliding mode control of interleaved parallel boost converter for fuel cell energy generation system. Math. Comput. Simul. 2013, 91, 193–210. [Google Scholar] [CrossRef]

- Cuoghi, S.; Mandrioli, R.; Ntogramatzidis, L.; Gabriele, G. Multileg interleaved buck converter for EV charging: Discrete-time model and direct control design. Energies 2020, 13, 466. [Google Scholar] [CrossRef]

- Zhuo, S.; Gaillard, A.; Li, Q.; Ma, R.; Paire, D.; Gao, F. Current Ripple Optimization of Four-Phase Floating Interleaved DC–DC Boost Converter Under Switch Fault. IEEE Trans. Ind. Appl. 2020, 56, 4214–4224. [Google Scholar] [CrossRef]

- Ahmed, S.; Kashif, S.A.R.; Ain, N.U.; Rasool, A.; Shahid, M.S.; Padmanaban, S.; Ozsoy, E.; Saqib, M.A. Mitigation of Complex Non-Linear Dynamic Effects in Multiple Output Cascaded DC-DC Converters. IEEE Access 2021, 9, 54602–54612. [Google Scholar] [CrossRef]

- Miranda, H.F.B.; da Costa, L.P.; Soares, S.O.; da Silva, J.V. Potential induced degradation (PID): Review. In Proceedings of the 2020 IEEE PES Transmission & Distribution Conference and Exhibition-Latin America (T&D LA), Montevideo, Uruguay, 28 September–2 October 2020; pp. 1–6. [Google Scholar]

- Erickson, R.W. Fundamentals of Power Electronics; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2013. [Google Scholar]

- Aloisi, W.; Palumbo, G. Efficiency model of boost dc–dc PWM converters. Int. J. Circuit Theory Appl. 2005, 33, 419–432. [Google Scholar] [CrossRef]

- Kebaili, S.; Betka, A. Efficiency model of DC/DC PWM converter photovoltaic applications. In Proceedings of the Global Conference on Renewables and Energy Efficiency for Desert Regions, Amman, Jordan, 3–5 April 2018. [Google Scholar]

- Hema Chander, A.; Kumar Sahu, L.; Ghosh, S.; Gupta, K.K. Comparative analysis on selection and synthesis of multiple input converters: A review. IET Power Electron. 2020, 13, 611–626. [Google Scholar] [CrossRef]

- Kumar, L.; Jain, S. Multiple-input DC/DC converter topology for hybrid energy system. IET Power Electron. 2013, 6, 1483–1501. [Google Scholar] [CrossRef]

- Babaei, E.; Abbasi, O. Structure for multi-input multi-output dc–dc boost converter. IET Power Electron. 2016, 9, 9–19. [Google Scholar] [CrossRef]

- Lindiya, S.A.; Palani, S.; Vijayarekha, K. Modelling and Simulation of Photovoltaic System Fed Two Input Two Output DC-DC Boost Converter Interfaced with Asymmetric Cascaded H-Bridge Multilevel Inverter. Indian J. Sci. Technol. 2017, 10, 5. [Google Scholar] [CrossRef]

- Yuan-mao, Y.; Cheng, K.W.E. Multi-input voltage-summation converter based on switched-capacitor. IET Power Electron. 2013, 6, 1909–1916. [Google Scholar] [CrossRef]

- Hou, S.; Chen, J.; Sun, T.; Bi, X. Multi-input step-up converters based on the switched-diode-capacitor voltage accumulator. IEEE Trans. Power Electron. 2015, 31, 381–393. [Google Scholar] [CrossRef]

- Varesi, K.; Hosseini, S.H.; Sabahi, M.; Babaei, E. A high-voltage gain nonisolated noncoupled inductor based multi-input DC-DC topology with reduced number of components for renewable energy systems. Int. J. Circuit Theory Appl. 2018, 46, 505–518. [Google Scholar] [CrossRef]

- Amaleswari, R.; Prabhakar, M. Non-isolated multi-input DC-DC converter with current sharing mechanism. Int. J. Electron. 2020, 108, 237–263. [Google Scholar] [CrossRef]

- Bahravar, S.; Abbaszadeh, K.; Olamaei, J. High Step-Up Non-isolated DC–DC Converter Using Diode–Capacitor Cells. Iran. J. Sci. Technol. Trans. Electr. Eng. 2020, 45, 81–96. [Google Scholar] [CrossRef]

- Chander, A.H.; Sahu, L.K.; Ghosh, S. Stand-alone multiple input photovoltaic inverter for maximum power extraction and voltage regulation under mismatched atmospheric conditions. IET Renew. Power Gener. 2020, 14, 1584–1595. [Google Scholar] [CrossRef]

- Zamanzad Ghavidel, B.; Maalandish, M.; Hosseini, S.H.; Sabahi, M.; Mohammadi-Ivatloo, B. Design and implementation of an improved power-electronic system for feeding loads of smart homes in remote areas using renewable energy sources. IET Renew. Power Gener. 2021, 15, 1–16. [Google Scholar] [CrossRef]

- Apoorva, G.; Savyasachi, G.; Shashikala, M. DC-DC Converter Integrated with Asymmetrical Multi-Level Inverter for Solar PV Application. In Proceedings of the 2017 International Conference on Current Trends in Computer, Electrical, Electronics and Communication (CTCEEC), Mysore, India, 8–9 September 2017; pp. 725–732. [Google Scholar]

- Smith, N.; McCann, R. Analysis and simulation of a multiple input interleaved boost converter for renewable energy applications. In Proceedings of the 2014 IEEE 36th International Telecommunications Energy Conference (INTELEC), Vancouver, BC, Canada, 28 September–2 October 2014; pp. 1–7. [Google Scholar]

- Colalongo, L.; Dotti, D.; Richelli, A.; Kovács-Vajna, Z.M. Non-isolated multiple-input boost converter for energy harvesting. Electron. Lett. 2017, 53, 1132–1134. [Google Scholar] [CrossRef]

- Kumar, G.K.; Arunkumar, G.; Elangovan, D. Multiple Input Interleaved Boost Converter for Non-Conventional Energy Applications. In Proceedings of the 2019 Innovations in Power and Advanced Computing Technologies (i-PACT), Vellore, India, 22–23 March 2019; Volume 1, pp. 1–5. [Google Scholar]

- Yang, F.; Ge, H.; Yang, J.; Dang, R.; Wu, H. An asymmetrical multi-level dual-input dual-buck inverter for multi-source interface applications. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2228–2233. [Google Scholar]

- Kardan, F.; Alizadeh, R.; Banaei, M.R. A new three input DC/DC converter for hybrid PV/FC/battery applications. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1771–1778. [Google Scholar] [CrossRef]

- Varesi, K.; Hosseini, S.H.; Sabahi, M.; Babaei, E.; Vosoughi, N. Performance and design analysis of an improved non-isolated multiple input buck DC–DC converter. IET Power Electron. 2017, 10, 1034–1045. [Google Scholar] [CrossRef]

- Saeed, L.; Khan, M.Y.A.; Arif, M.; Majid, A.; Saleem, J. A multiple-input multiple-output non-inverting non-isolated bidirectional buck/boost converter for storage application. In Proceedings of the 2018 International Conference on Computing, Mathematics and Engineering Technologies (iCoMET), Sukkur, Pakistan, 3–4 March 2018; pp. 1–6. [Google Scholar]

- Zhu, B.; Zeng, Q.; Chen, Y.; Zhao, Y.; Liu, S. A dual-input high step-up DC/DC converter with ZVT auxiliary circuit. IEEE Trans. Energy Convers. 2018, 34, 161–169. [Google Scholar] [CrossRef]

- Khan, S.H.; Saeed, L.; Khan, M.Y.A.; Saleem, J.; Majid, A. A multiple-input multiple-output bipolar DC-DC voltage gain converter with backup battery port. In Proceedings of the 2019 International Conference on Engineering and Emerging Technologies (ICEET), Lahore, Pakistan, 21–22 February 2019; pp. 1–6. [Google Scholar]

- Faraji, R.; Ding, L.; Rahimi, T.; Kheshti, M.; Islam, M.R. Soft-Switched Three-Port DC-DC Converter with Simple Auxiliary Circuit. IEEE Access 2021, 9, 66738–66750. [Google Scholar] [CrossRef]

- Taufik, T.; Muchtar, R.; Taufik, M. Performance analysis of multiple input boost converter with inherent OR diode configuration. In Proceedings of the 2017 International Seminar on Intelligent Technology and Its Applications (ISITIA), Surabaya, Indonesia, 28–29 August 2017; pp. 175–180. [Google Scholar]

- Chang, C.; Knights, M.A. Interleaving technique in distributed power conversion systems. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 1995, 42, 245–251. [Google Scholar] [CrossRef]

- Goad, S.D. Power Conversion Array Applying Small Sequentially Switched Converters in Parallel. US Patent 5,563,780, 8 October 1996. [Google Scholar]

- Hart, D.W. Power Electronics; Mc. Graw Hill: New York, NY, USA, 2011. [Google Scholar]

- Ned Mohan, T.M.U.; Robbins, W.P. Power Electronics Converters, Applications and Design; Jhon Wiley and Sons, Inc.: Hoboken, NJ, USA, 1995. [Google Scholar]

- Khalil, H.K.; Grizzle, J.W. Nonlinear Systems; Prentice Hall: Upper Saddle River, NJ, USA; Boca Raton, FL, USA, 2002; Volume 3. [Google Scholar]

- Zhao, X.; Kao, Y.; Niu, B.; Wu, T. Control Synthesis of Switched Systems; Springer: Cham, Switzerland, 2017. [Google Scholar]

- da Silva, E.R.; Elbuluk, M.E. Fundamentals of power electronics. In Power Electronics for Renewable and Distributed Energy Systems; Springer: Cham, Switzerland, 2013; pp. 7–59. [Google Scholar]

- Rogers, E. Understanding Buck-Boost power stages in switch mode power supplies. In Mixed Signal Products; Texas Instruments Incorporated: Dallas, TX, USA, 1999. [Google Scholar]

- Barbosa, P.M.; Lee, F.C. Design aspects of paralleled three-phase DCM boost rectifiers. In Proceedings of the 30th Annual IEEE Power Electronics Specialists Conference Record (Cat. No. 99CH36321), Charleston, SC, USA, 1 July 1999; Volume 1, pp. 331–336. [Google Scholar]

- Kabalci, E. Maximum Power Point Tracking (MPPT) Algorithms for Photovoltaic Systems. In Energy Harvesting and Energy Efficiency: Technology, Methods, and Applications; Springer International Publishing: Cham, Switzerland, 2017; pp. 205–234. [Google Scholar]

- Khaligh, A.; Onar, O.C. Solar energy harvesting. In Energy Harvesting Solar, Wind, and Ocean Energy Conversion Systems; CRC Press: Boca Raton, FL, USA, 2010; pp. 21–33. [Google Scholar]

- Durusu, A.; Nakir, I.; Tanrioven, M. Photovoltaic System: Case Studies. In Energy Harvesting and Energy Efficiency: Technology, Methods, and Applications; Springer International Publishing: Cham, Switzerland, 2017; pp. 235–260. [Google Scholar]

- Gomathy, S.; Saravanan, S.; Thangavel, S. Design and implementation of maximum power point tracking (MPPT) algorithm for a standalone PV system. Int. J. Sci. Eng. Res. 2012, 3, 1–7. [Google Scholar]

- Killi, M.; Samanta, S. Modified perturb and observe MPPT algorithm for drift avoidance in photovoltaic systems. IEEE Trans. Ind. Electron. 2015, 62, 5549–5559. [Google Scholar] [CrossRef]

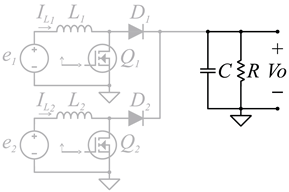

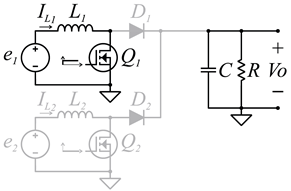

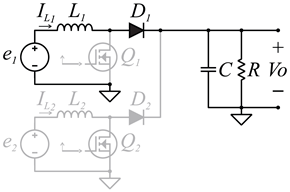

| Mode | Current Flow Schematic | Inductors Currents | Output Voltage |

|---|---|---|---|

| I |  | ||

| |||

| |||

| |||

| V |  | ||

| |||

|

| Photovoltaic Panel SE-156*104-100P-72 | |

|---|---|

| Power (nominal-real) | 100–70 W |

| Maximum open circuit voltage | V |

| Short circuit current @ 1000 W/m | A |

| Voltage at maximum power (nominal-real) | 17.70–17.50 V |

| Current at maximum power (nominal-real) | 5.65–4.00 A |

| Inductor AGP4233-223 | |

| Peak current (nominal) | A |

| (real @ 10 kHz) | µH |

| (real @ 10 kHz) | µH |

| (real @ 10 kHz) | µH |

| resistance (real @ 10 kHz) | |

| resistance (real @ 10 kHz) | |

| resistance (real @ 10 kHz) | |

| MOSFET FDP | |

| 94 m | |

| Diode MUR1520 | |

| V | |

| Capacitor | |

| Value | 25 µF |

| Series resistance | m |

| Output load | |

| Value | 75 |

| Power supply BKPrecision 9132B | |

| Stage | [A] | [V] | [W] | [V] | [A] | [W] | Efficiency |

|---|---|---|---|---|---|---|---|

| Maximum Irradiation (MISeC) | |||||||

| 1 | |||||||

| 2 | 80.3 | 1.27 | 101.981 | 82.27 | |||

| 3 | 10 | ||||||

| Single PV Module Shaded (MISeC) | |||||||

| 1 | 8 | ||||||

| 2 | 68.3 | 1.05 | 71.715 | 80.62 | |||

| 3 | 10 | ||||||

| Both Shaded PV Modules (MISeC) | |||||||

| 1 | 10 | 21 | |||||

| 2 | 57.3 | 0.82 | 46.986 | 79.74 | |||

| 3 | 10 | ||||||

| Maximum Irradiation (MISiC) | |||||||

| 1 | |||||||

| 2 | 78.7 | 1.23 | 96.801 | 78.47 | |||

| 3 | 10 | ||||||

| Values | Error | ||||

|---|---|---|---|---|---|

| PSIM | Model | Experimental | PSIM | Model | |

| V | V | 114 V | % | % | |

| W | W | W | % | % | |

| V | V | V | % | % | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Parada-Salado, J.-G.; Rodríguez-Licea, M.-A.; Soriano-Sanchez, A.-G.; Ruíz-Martínez, O.-F.; Espinosa-Calderon, A.; Pérez-Pinal, F.-J. Study on Multiple Input Asymmetric Boost Converters with Simultaneous and Sequential Triggering. Electronics 2021, 10, 1421. https://doi.org/10.3390/electronics10121421

Parada-Salado J-G, Rodríguez-Licea M-A, Soriano-Sanchez A-G, Ruíz-Martínez O-F, Espinosa-Calderon A, Pérez-Pinal F-J. Study on Multiple Input Asymmetric Boost Converters with Simultaneous and Sequential Triggering. Electronics. 2021; 10(12):1421. https://doi.org/10.3390/electronics10121421

Chicago/Turabian StyleParada-Salado, Juan-Gerardo, Martín-Antonio Rodríguez-Licea, Allan-Giovanni Soriano-Sanchez, Omar-Fernando Ruíz-Martínez, Alejandro Espinosa-Calderon, and Francisco-Javier Pérez-Pinal. 2021. "Study on Multiple Input Asymmetric Boost Converters with Simultaneous and Sequential Triggering" Electronics 10, no. 12: 1421. https://doi.org/10.3390/electronics10121421

APA StyleParada-Salado, J.-G., Rodríguez-Licea, M.-A., Soriano-Sanchez, A.-G., Ruíz-Martínez, O.-F., Espinosa-Calderon, A., & Pérez-Pinal, F.-J. (2021). Study on Multiple Input Asymmetric Boost Converters with Simultaneous and Sequential Triggering. Electronics, 10(12), 1421. https://doi.org/10.3390/electronics10121421