Design of a Real-Time Breakdown Voltage and On-Chip Temperature Monitoring System for Single Photon Avalanche Diodes

Abstract

1. Introduction

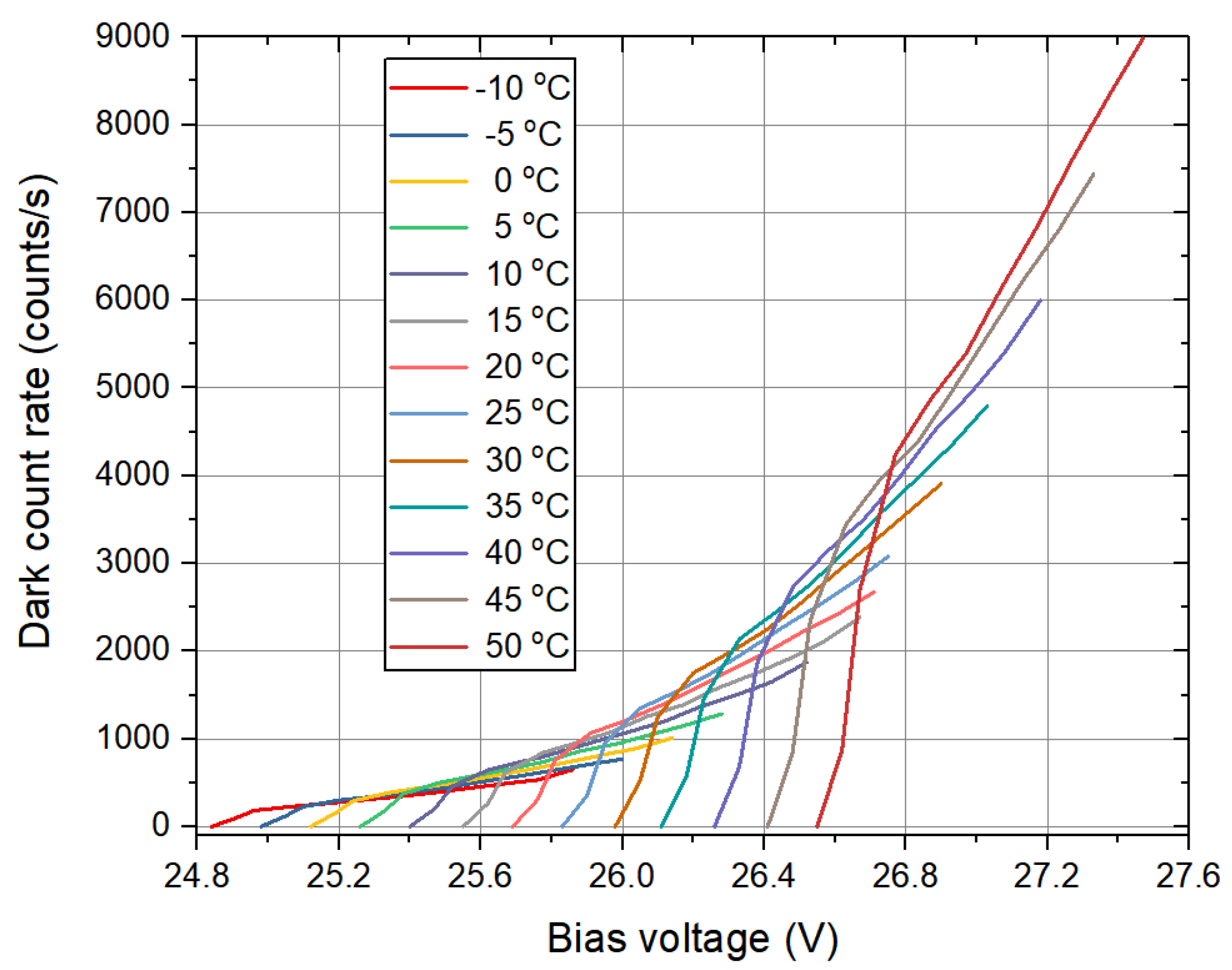

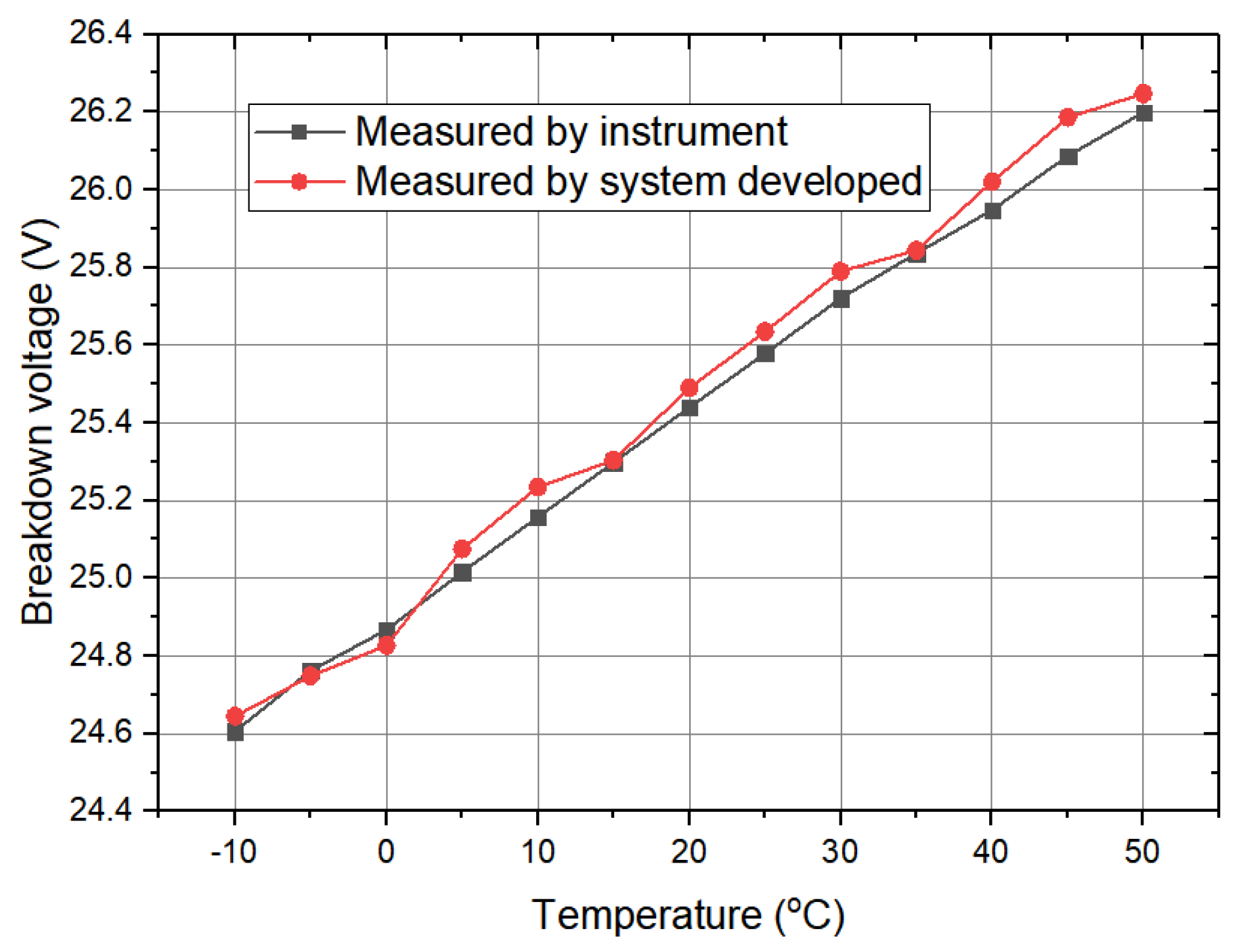

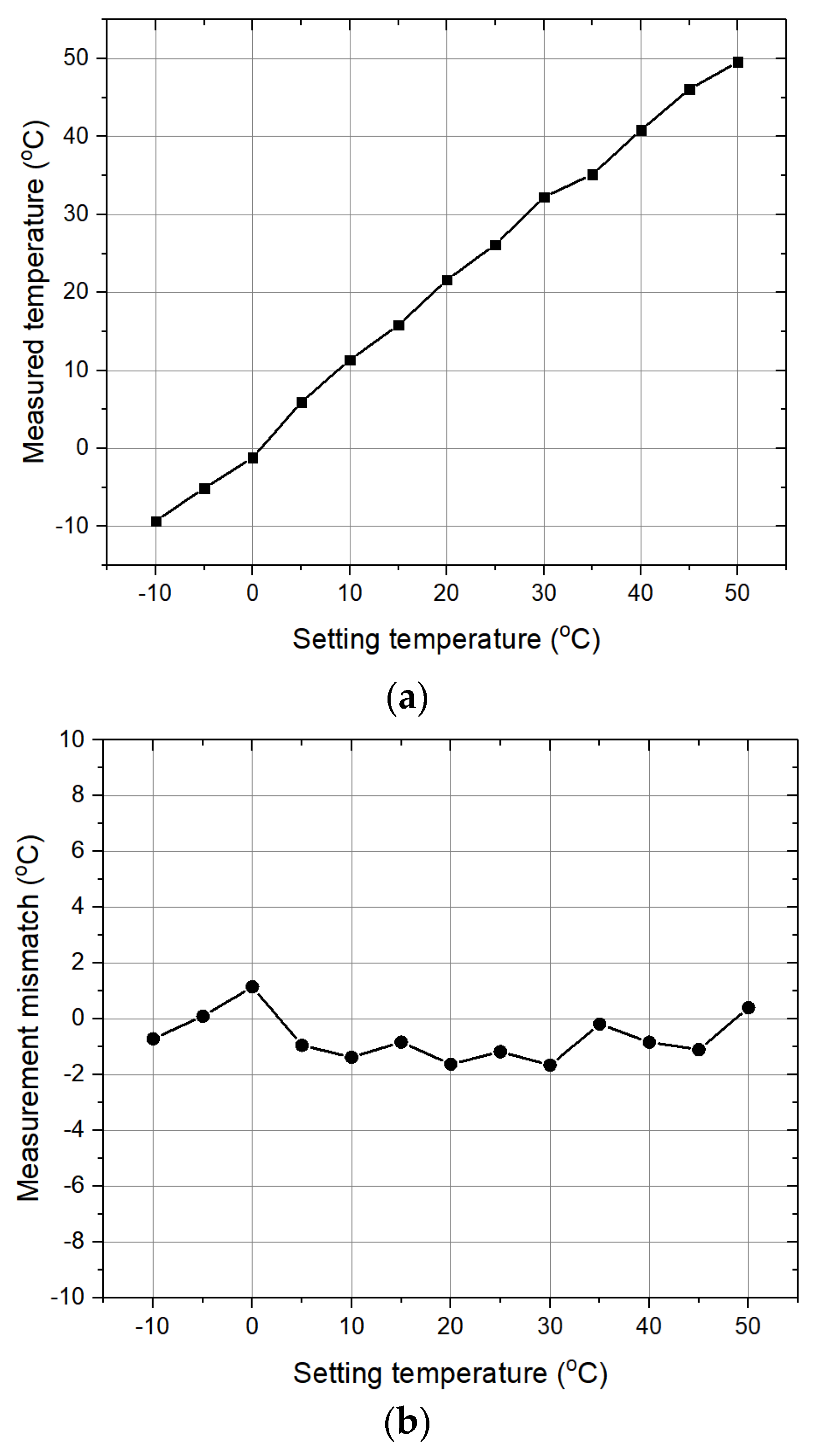

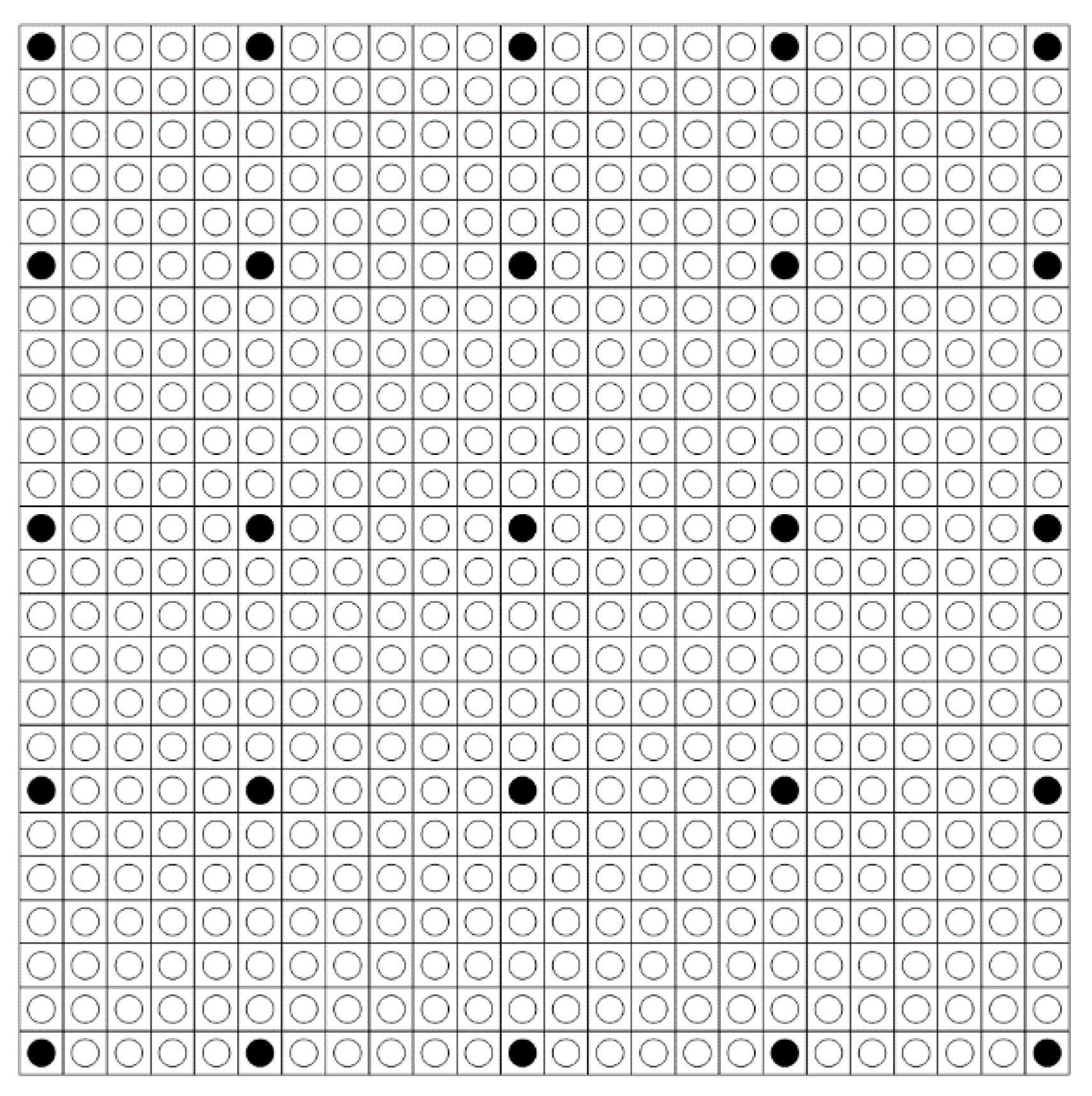

2. System Description

2.1. Power Management and Bias Voltage Setting Circuitry

2.2. Breakdown Voltage and Temperature Calculation

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Pasquinelli, K.; Lussana, R.; Tisa, S.; Villa, F.; Zappa, F. Single-Photon Detectors Modeling and Selection Criteria for High-Background LiDAR. IEEE Sens. J. 2020, 20, 7021–7032. [Google Scholar] [CrossRef]

- Hutchings, S.W.; Johnston, N.; Gyongy, I.; Al Abbas, T.; Dutton, N.A.; Tyler, M.; Chan, S.; Leach, J.; Henderson, R.K. A Reconfigurable 3-D-Stacked SPAD Imager with In-Pixel Histogramming for Flash LIDAR or High-Speed Time-of-Flight Imaging. IEEE J. Solid-State Circuits 2019, 54, 2947–2956. [Google Scholar] [CrossRef]

- Ken, H.; Schiedt, B.; Morrison, A.P. Solid-state nanopore technologies for nanopore-based DNA analysis. Nanomedicine 2007, 2, 875–897. [Google Scholar]

- Restelli, A.; Bienfang, J.C.; Clark, C.W.; Rech, I.; Labanca, I.; Ghioni, M.; Cova, S. Improved timing resolution single-photon detectors in daytime free-space quantum key distribution with 1.25 GHz transmission rate. IEEE J. Sel. Top. Quantum Electron. 2010, 16, 1084–1090. [Google Scholar] [CrossRef]

- Chockalingam, V.; Bruschini, C.; Charbon, E. Sensor network architecture for a fully digital and scalable SPAD based PET system. In Proceedings of the IEEE Nuclear Science Symposium and Medical Imaging Conference Record (NSS/MIC), Anaheim, CA, USA, 27 October–3 November 2012; pp. 1115–1118. [Google Scholar]

- Kufcsák, A.; Erdogan, A.; Walker, R.; Ehrlich, K.; Tanner, M.; Megia-Fernandez, A.; Scholefield, E.; Emanuel, P.; Dhaliwal, K.; Bradley, M.; et al. Time-resolved spectroscopy at 19,000 lines per second using a CMOS SPAD line array enables advanced biophotonics applications. Opt. Express 2017, 25, 11103–11123. [Google Scholar] [CrossRef] [PubMed]

- Iwata, T.; Takasu, T.; Araki, T. Simple Photomultiplier Tube Internal-Gating Method for Use in Subnanosecond Time-Resolved Spectroscopy. Appl. Spectrosc. 2003, 57, 1145–1150. [Google Scholar] [CrossRef] [PubMed]

- Inadama, N.; Murayama, H.; Watanabe, M.; Omura, T.; Yamashita, T.; Kawai, H.; Umehara, T.; Kasahara, T.; Orita, N.; Tsuda, T. Performance of a PET detector with a 256ch flat panel PS-PMT. IEEE Trans. Nucl. Sci. 2004, 51, 58–62. [Google Scholar] [CrossRef]

- Wang, Y.; Wong, W.H.; Aykac, M.; Uribe, J.; Li, H.; Baghaei, H.; Liu, Y.; Xing, T. An iterative energy-centroid method for recalibration of PMT gain in PET or gamma camera. IEEE Trans. Nucl. Sci. 2002, 49, 2047–2050. [Google Scholar] [CrossRef]

- Renker, D. Geiger-mode avalanche photodiodes, history, properties and problems. Nucl. Instrum. Methods Phys. Res. Sect. A 2006, 567, 48–56. [Google Scholar] [CrossRef]

- Akita, H.; Takai, I.; Azuma, K.; Hata, T.; Ozaki, N. An imager using 2-D single-photon avalanche diode array in 0.18-μm CMOS for automotive LIDAR application. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. C290–C291. [Google Scholar]

- Della Rocca, F.M.; Nedbal, J.; Tyndall, D.; Krstajić, N.; Li, D.D.U.; Ameer-Beg, S.M.; Henderson, R.K. Real-time fluorescence lifetime actuation for cell sorting using a CMOS SPAD silicon photomultiplier. Opt. Lett. 2016, 41, 673–676. [Google Scholar] [CrossRef] [PubMed]

- Ehrlich, K.; Kufcsák, A.; McAughtrie, S.; Fleming, H.; Krstajic, N.; Campbell, C.J.; Henderson, R.K.; Dhaliwal, K.; Thomson, R.R.; Tanner, M.G. pH sensing through a single optical fibre using SERS and CMOS SPAD line arrays. Opt. Express 2017, 25, 30976–30986. [Google Scholar] [CrossRef] [PubMed]

- Borg, J. Performance and Spatial Sensitivity Variations of Single-Photon Avalanche Diodes Manufactured in an Image Sensor CMOS Process. IEEE Electron Device Lett. 2015, 36, 1118–1120. [Google Scholar] [CrossRef]

- Xu, H.; Pancheri, L.; Dalla Betta, G.F.; Stoppa, D. Design and characterization of a p+/n-well SPAD array in 150nm CMOS process. Opt. Express 2017, 25, 12765–12778. [Google Scholar] [CrossRef] [PubMed]

- Lee, M.-J.; Ximenes, A.R.; Padmanabhan, P.; Wang, T.-J.; Huang, K.-C.; Yamashita, Y.; Yaung, D.-N.; Charbon, E. High-Performance Back-Illuminated Three-Dimensional Stacked Single-Photon Avalanche Diode Implemented in 45-nm CMOS Technology. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–9, Art no. 3801809. [Google Scholar] [CrossRef]

- Ratti, L.; Brogi, P.; Collazuol, G.; Dalla Betta, G.F.; Ficorella, A.; Lodola, L.; Marrocchesi, P.S.; Mattiazzo, S.; Morsani, F.; Musacci, M.; et al. Dark Count Rate Degradation in CMOS SPADs Exposed to X-Rays and Neutrons. IEEE Trans. Nucl. Sci. 2019, 66, 567–574. [Google Scholar] [CrossRef]

- Jackson, J.C.; Morrison, A.P.; Phelan, D.; Mathewson, A. A novel silicon Geiger-mode avalanche photodiode. In Proceedings of the IEEE International Electron Devices Meeting (IEDM’02), San Francisco, CA, USA, 8–11 December 2002; pp. 797–800. [Google Scholar]

- Phelan, D.; Jackson, C.; Redfern, R.M.; Morrison, A.P.; Mathewson, A. Geiger mode avalanche photodiodes for microarray systems. Proc. SPIE 2002, 4626, 89–97. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Deng, S.; Morrison, A.P.; Guo, Y.; Teng, C.; Chen, M.; Cheng, Y.; Liu, H.; Xiong, X.; Yuan, L. Design of a Real-Time Breakdown Voltage and On-Chip Temperature Monitoring System for Single Photon Avalanche Diodes. Electronics 2021, 10, 25. https://doi.org/10.3390/electronics10010025

Deng S, Morrison AP, Guo Y, Teng C, Chen M, Cheng Y, Liu H, Xiong X, Yuan L. Design of a Real-Time Breakdown Voltage and On-Chip Temperature Monitoring System for Single Photon Avalanche Diodes. Electronics. 2021; 10(1):25. https://doi.org/10.3390/electronics10010025

Chicago/Turabian StyleDeng, Shijie, Alan P. Morrison, Yong Guo, Chuanxin Teng, Ming Chen, Yu Cheng, Houquan Liu, Xianming Xiong, and Libo Yuan. 2021. "Design of a Real-Time Breakdown Voltage and On-Chip Temperature Monitoring System for Single Photon Avalanche Diodes" Electronics 10, no. 1: 25. https://doi.org/10.3390/electronics10010025

APA StyleDeng, S., Morrison, A. P., Guo, Y., Teng, C., Chen, M., Cheng, Y., Liu, H., Xiong, X., & Yuan, L. (2021). Design of a Real-Time Breakdown Voltage and On-Chip Temperature Monitoring System for Single Photon Avalanche Diodes. Electronics, 10(1), 25. https://doi.org/10.3390/electronics10010025