CMOS Inverter as Analog Circuit: An Overview

Abstract

:1. Introduction

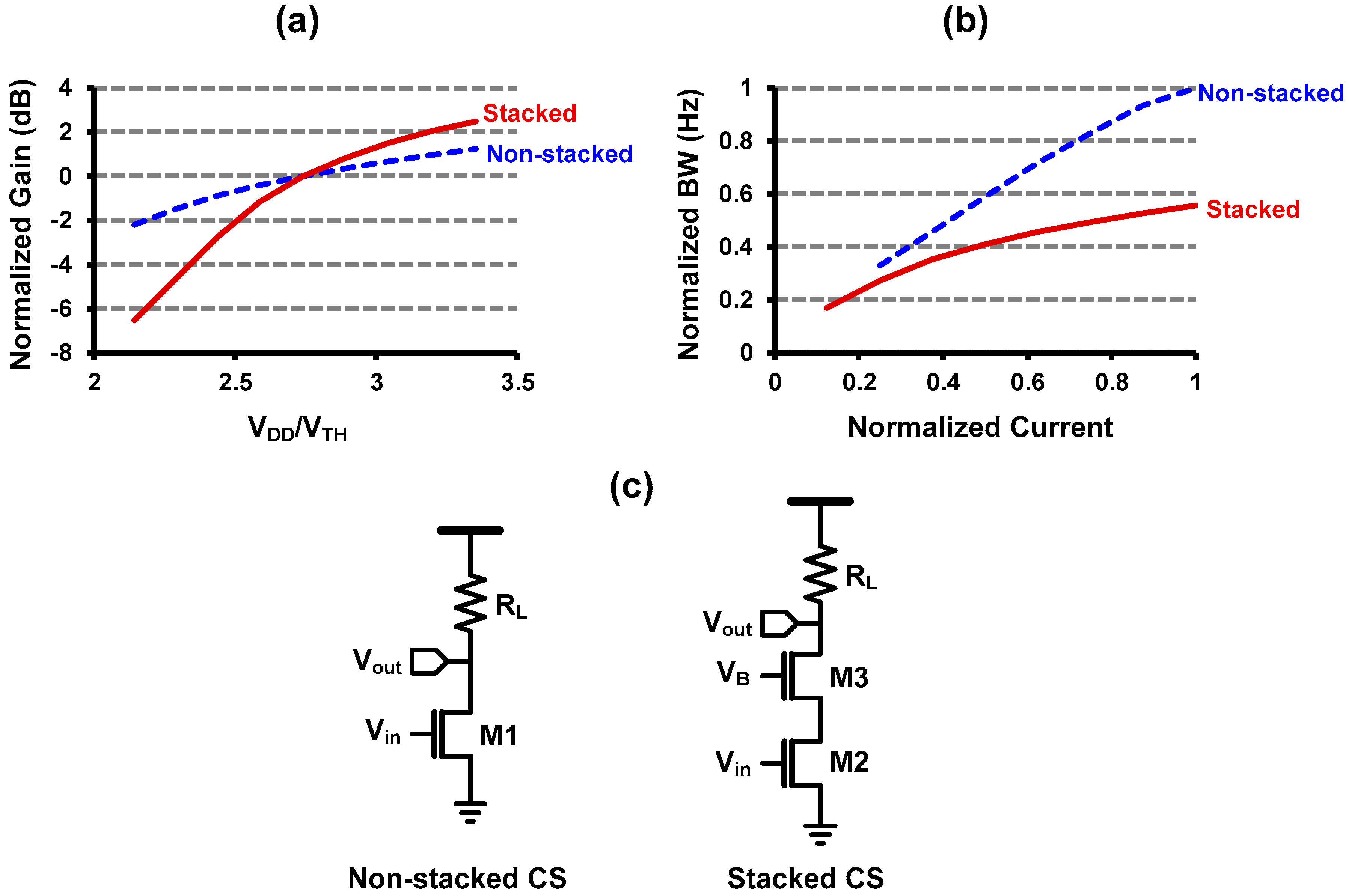

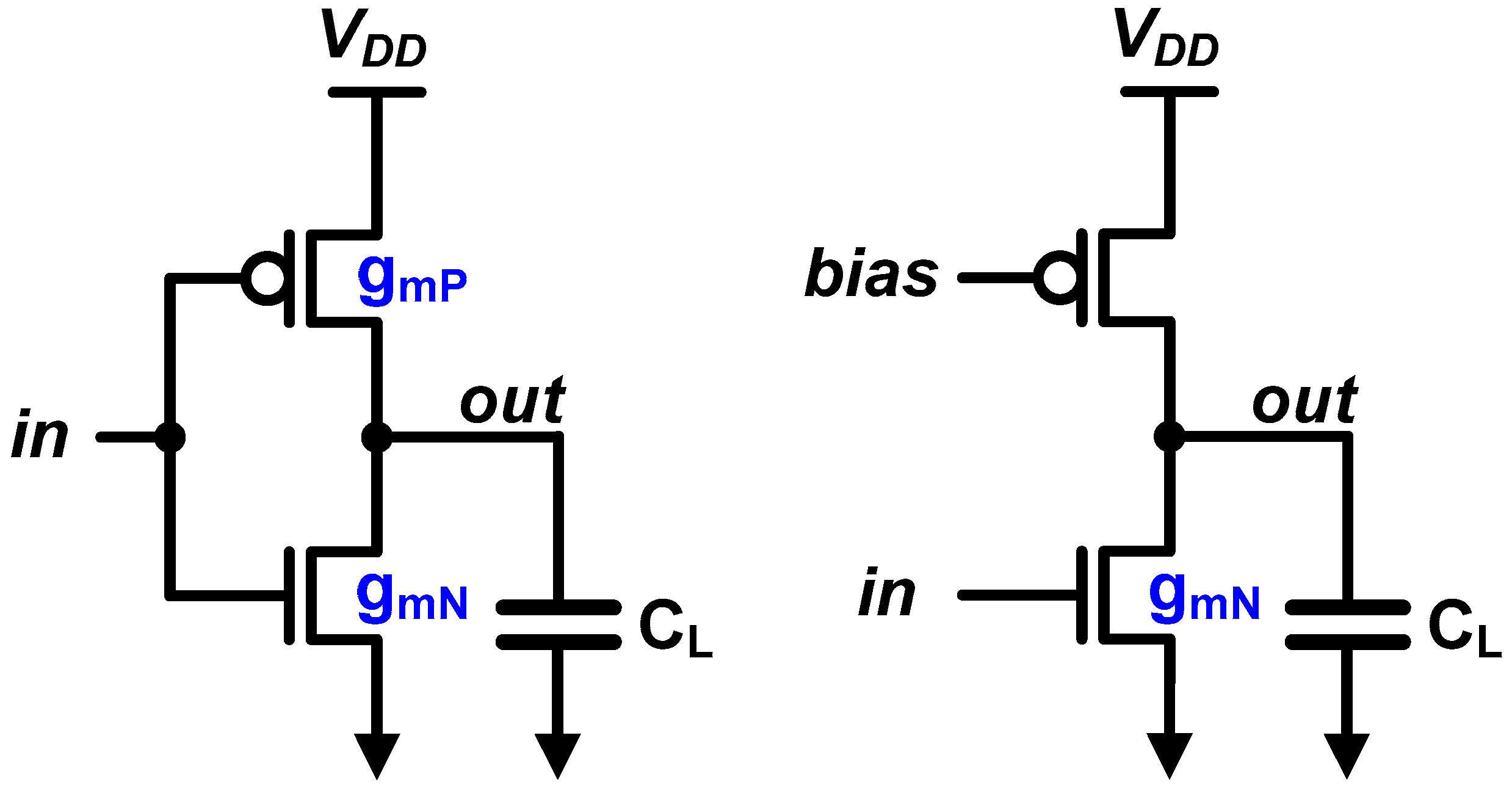

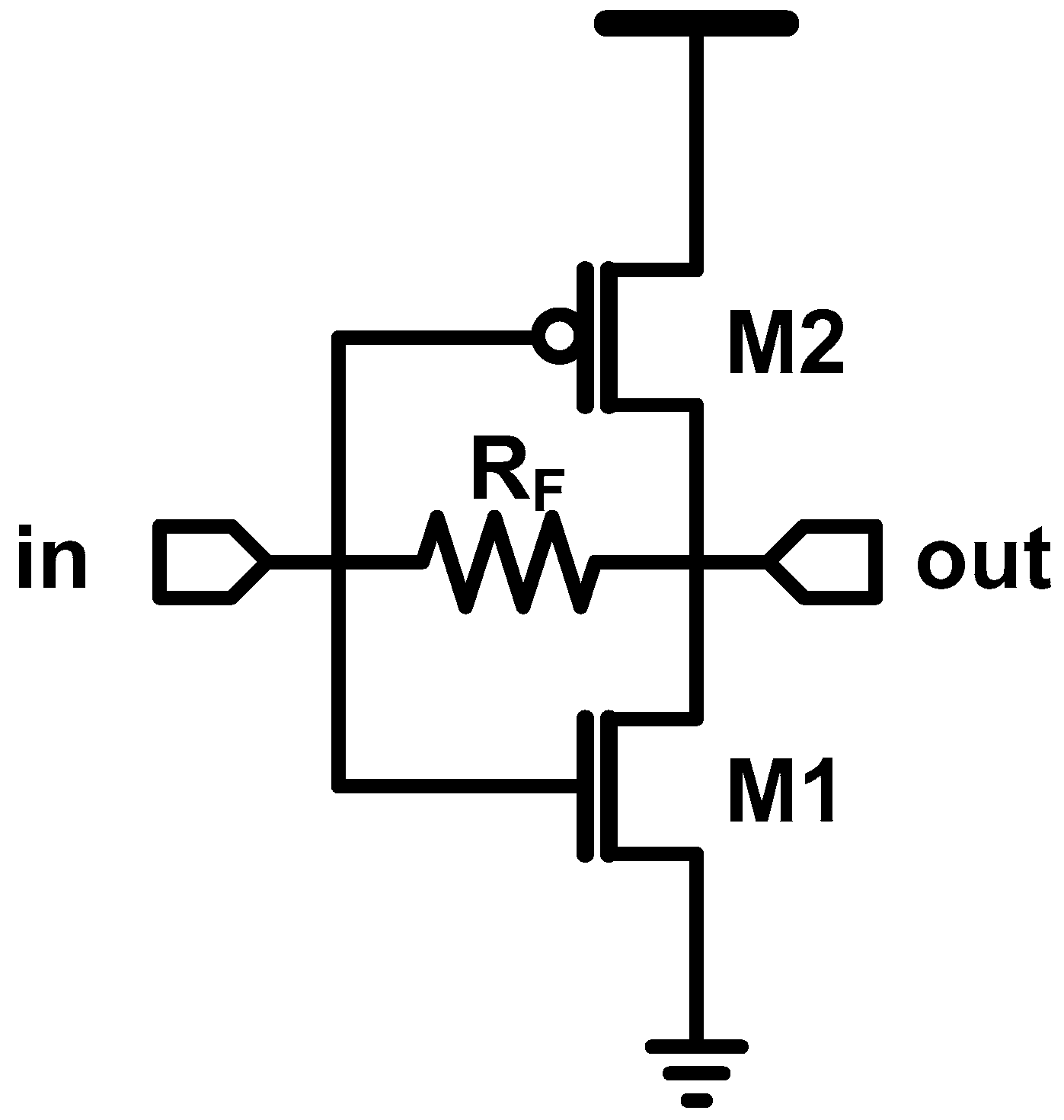

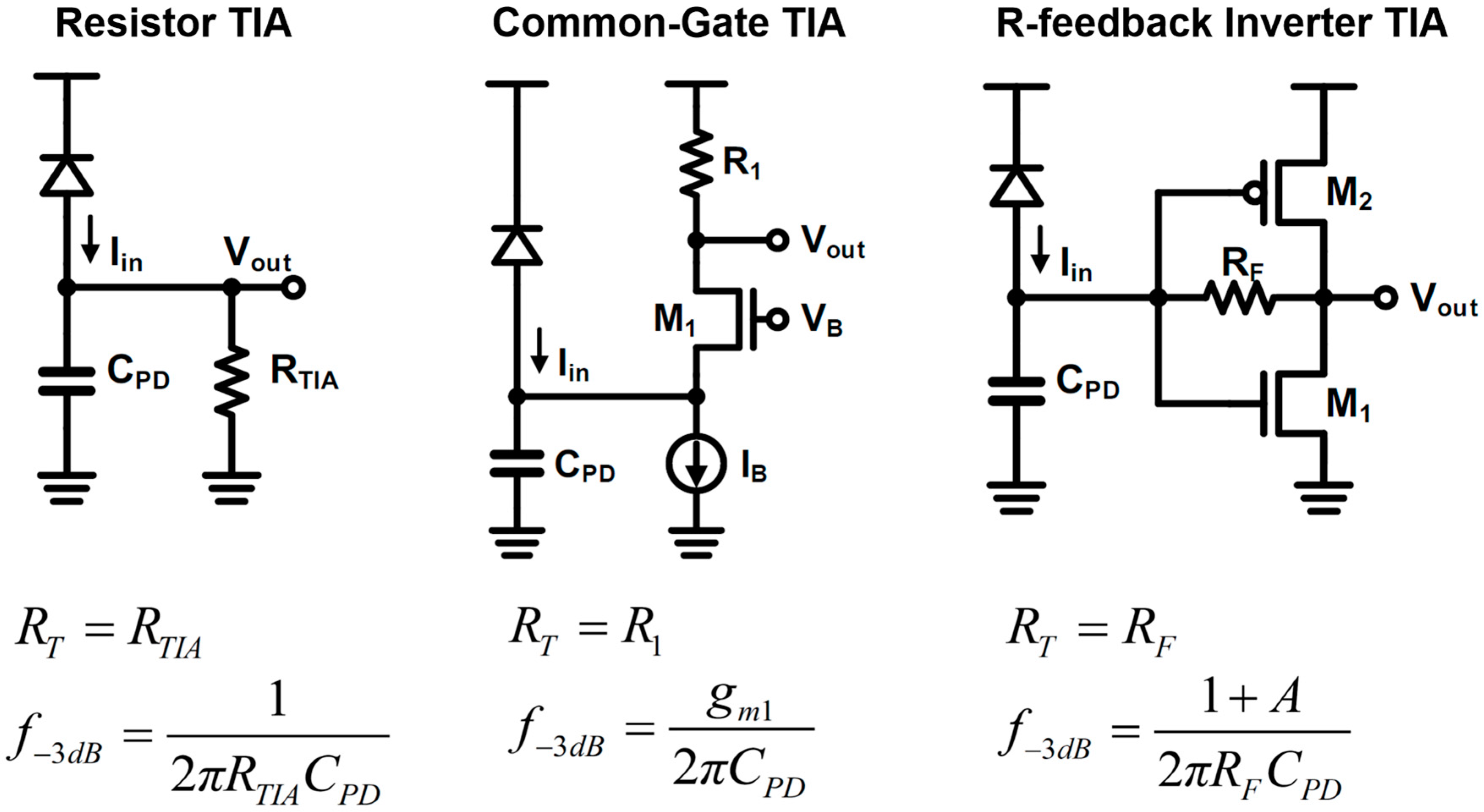

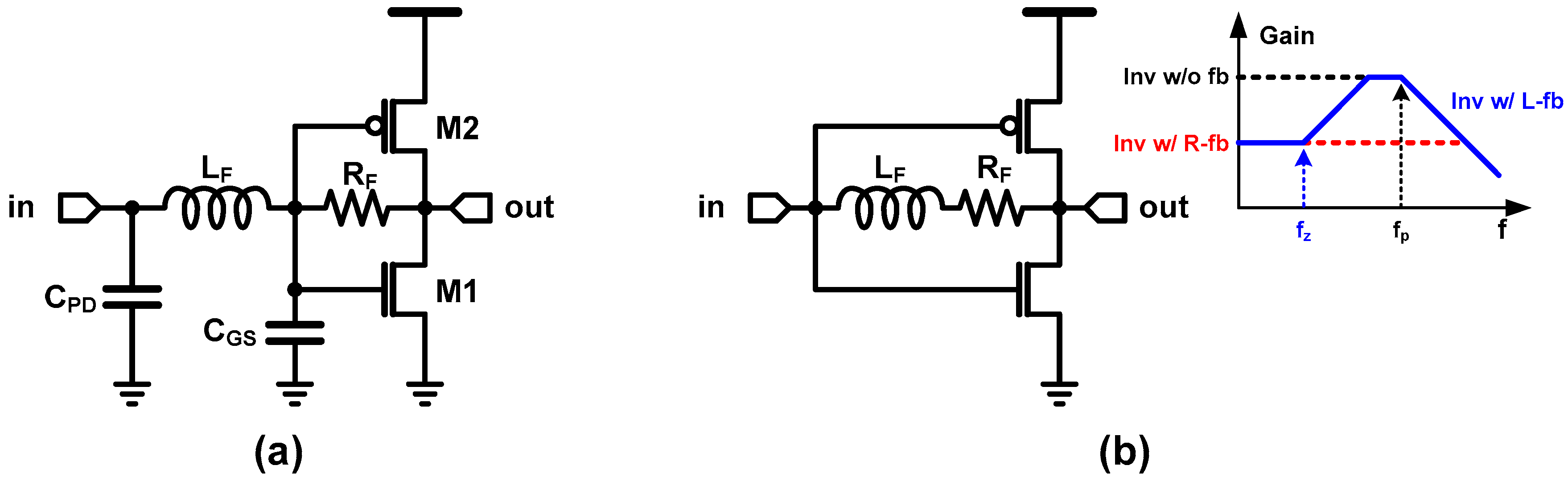

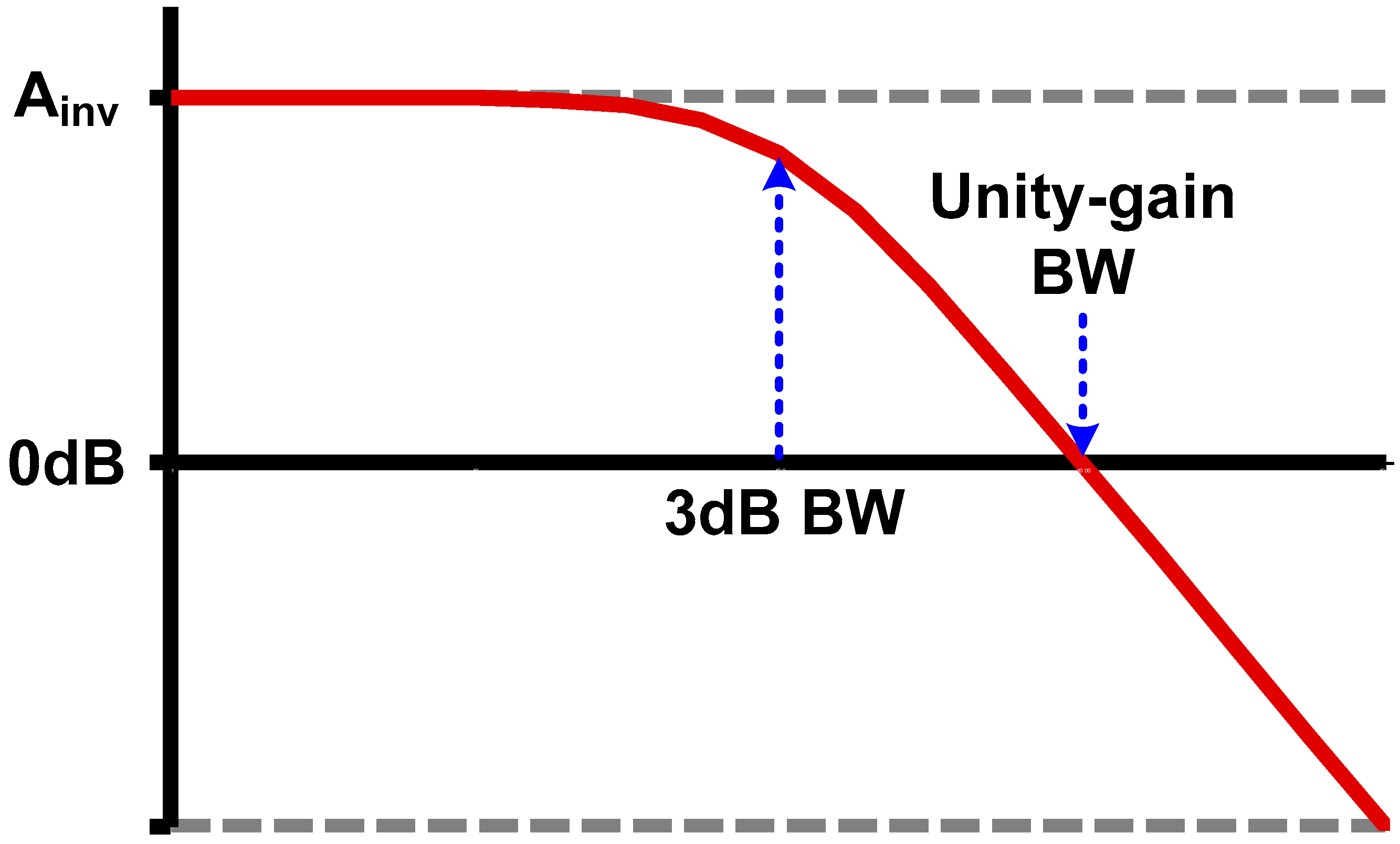

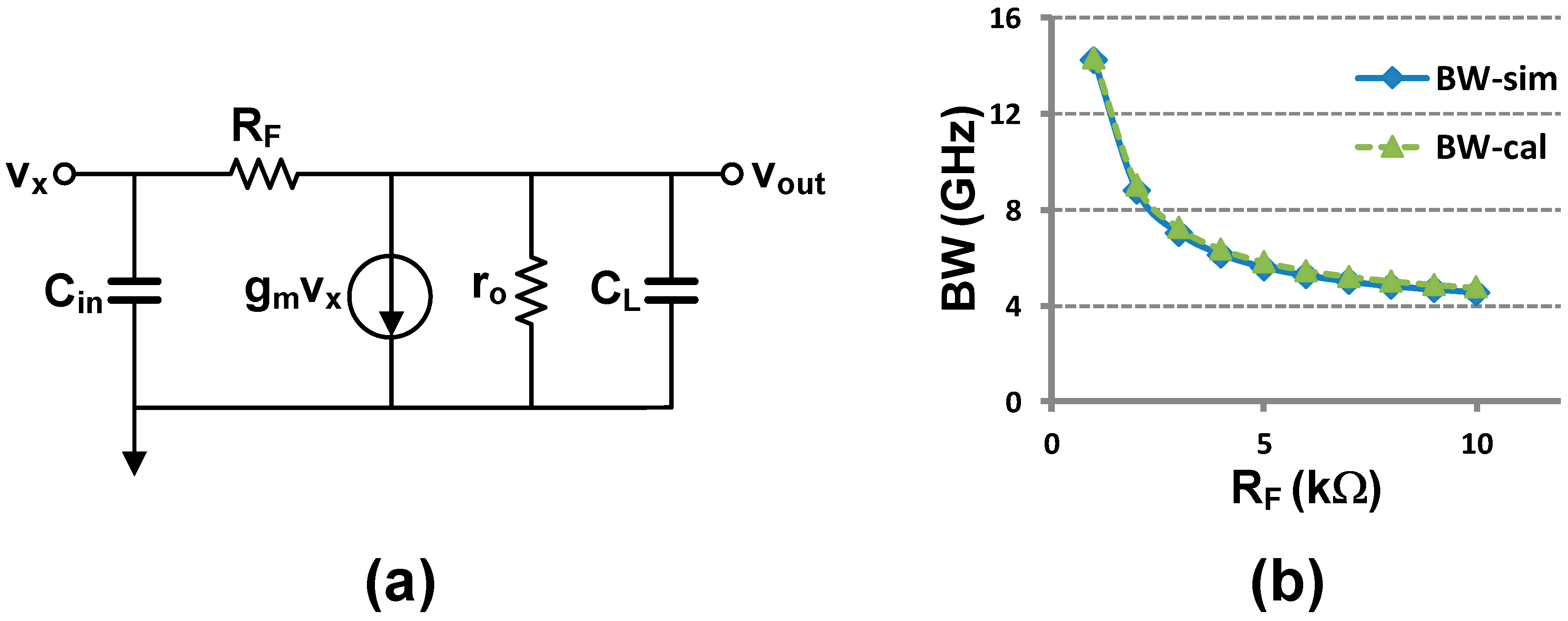

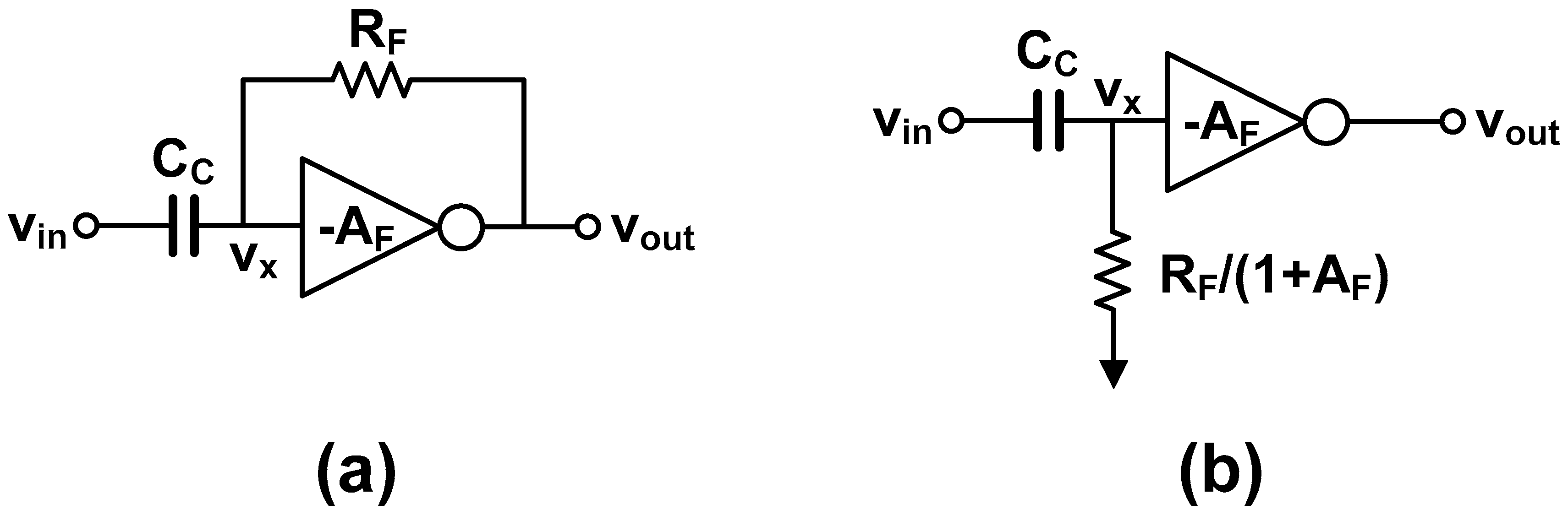

2. CMOS Inverter as an Amplifier

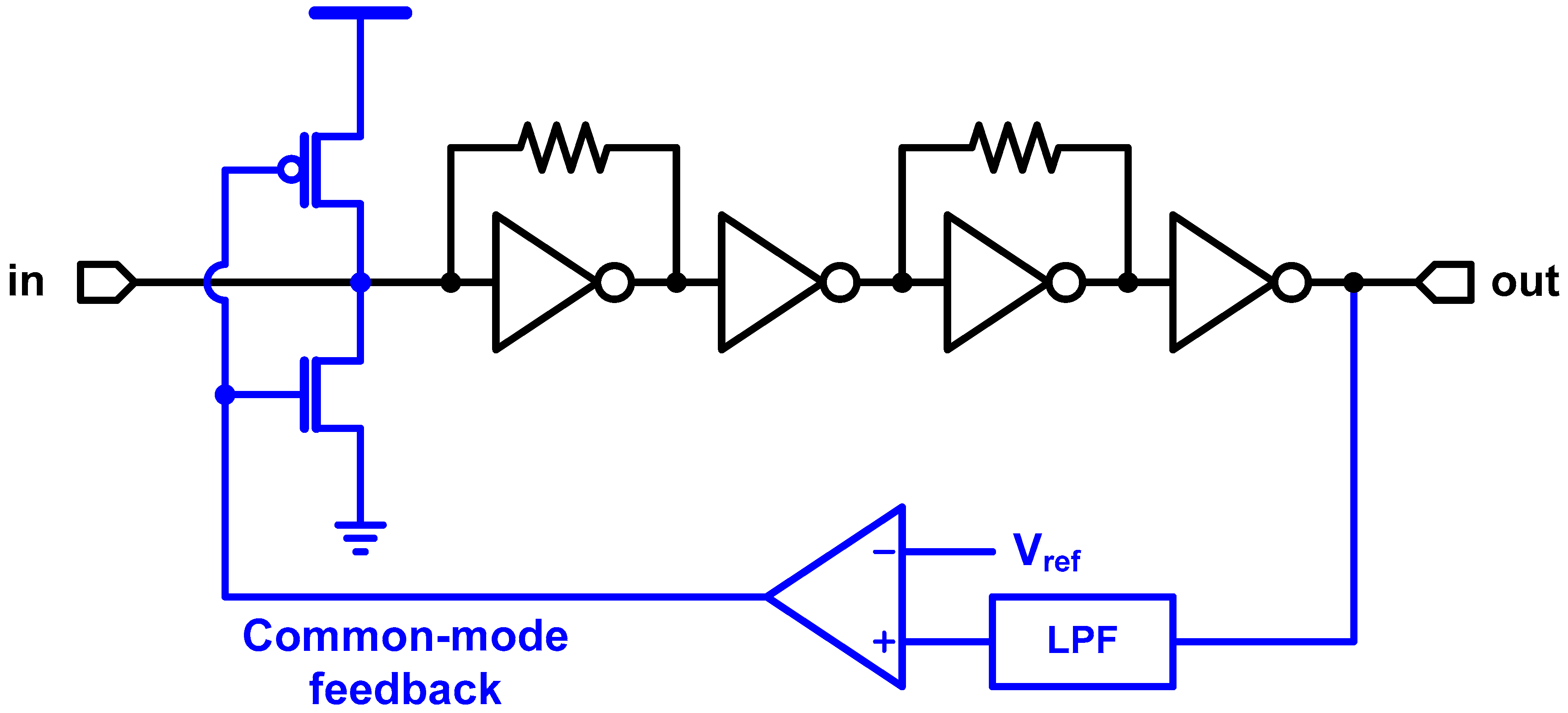

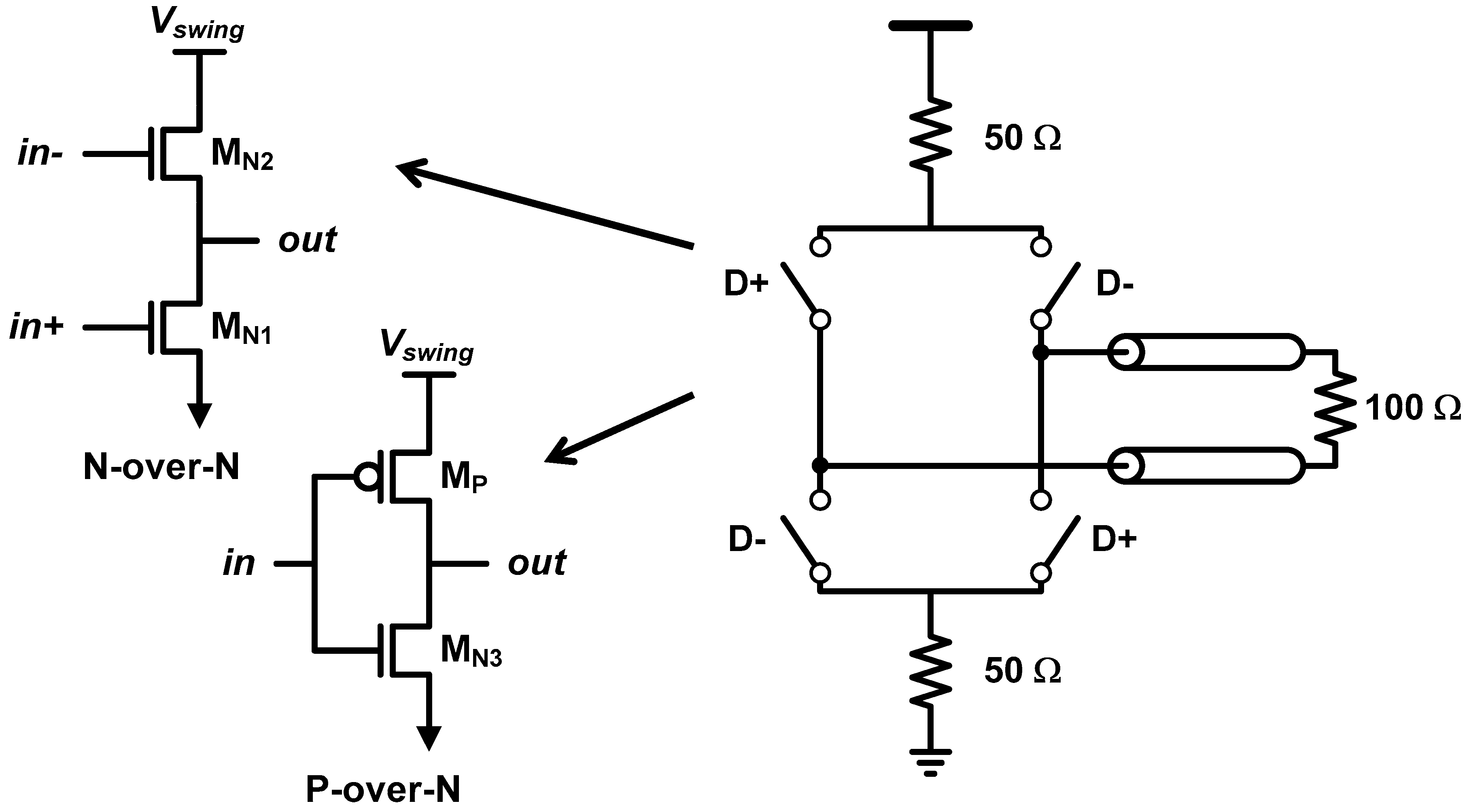

3. High Speed Buffer

- Since AC coupling completely blocks the DC component of the clock signal, the duty-cycle distortion does not propagate. Thanks to the self-biasing to the cross-over voltage, the duty-cycle is restored to the ideal value regardless of the input duty-cycle (Figure 11).

- Combined with the low-pass characteristic of the inverter, AC coupling results in a band-pass characteristic. Because a band-pass filter attenuates all out-of-band noise, it suppresses phase noise and jitter from the input clock [54].

- Because the clock buffer does not have to deal with a wide-band signal, the high-frequency cut-off frequency can be fairly high (<~1/10 of the clock frequency). Therefore, a small capacitor can be used [39].

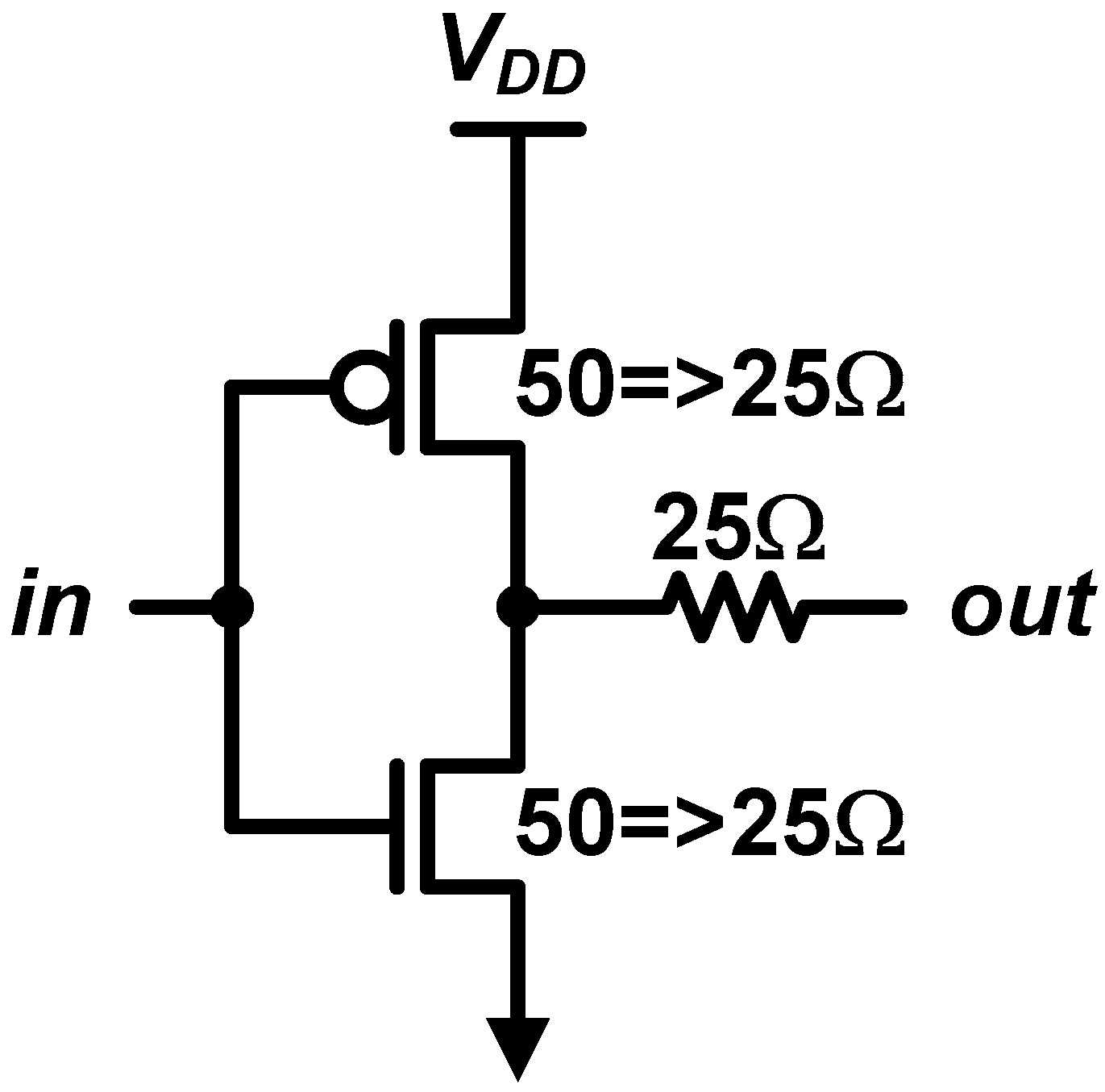

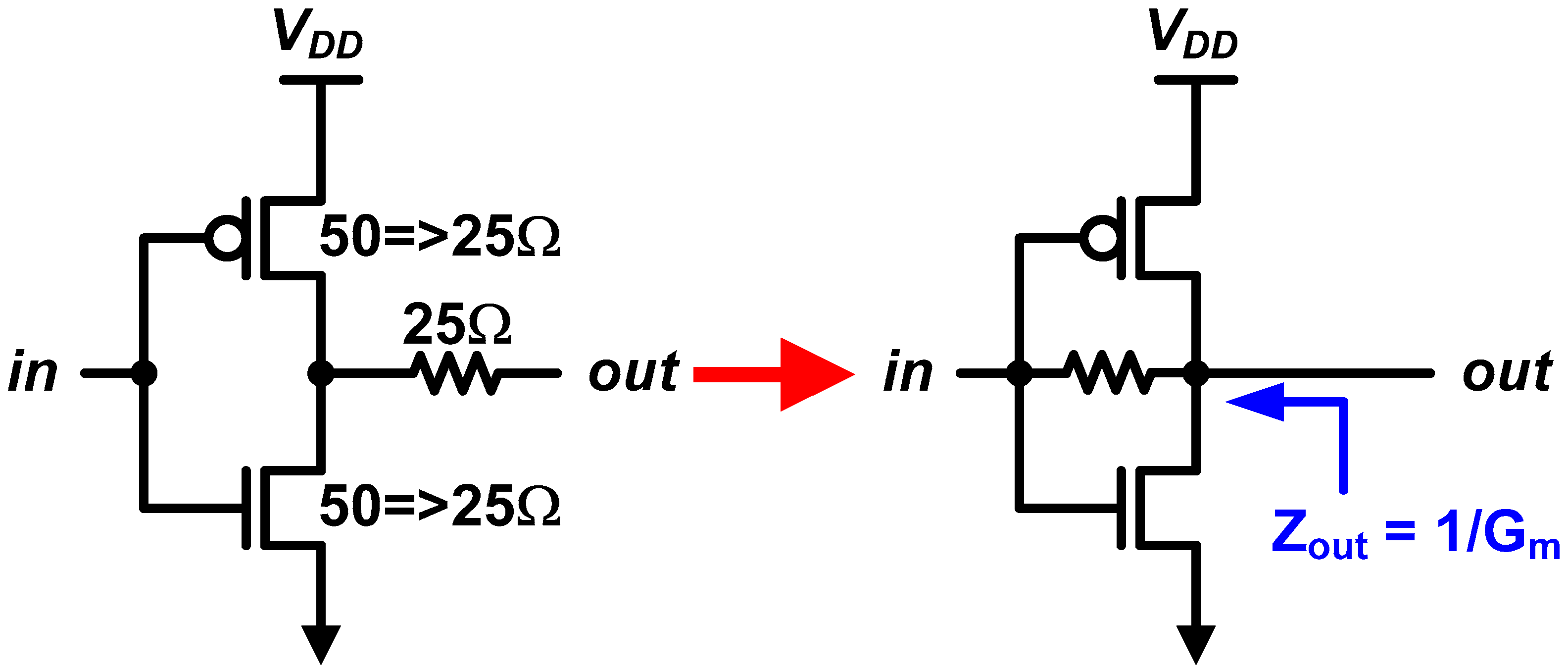

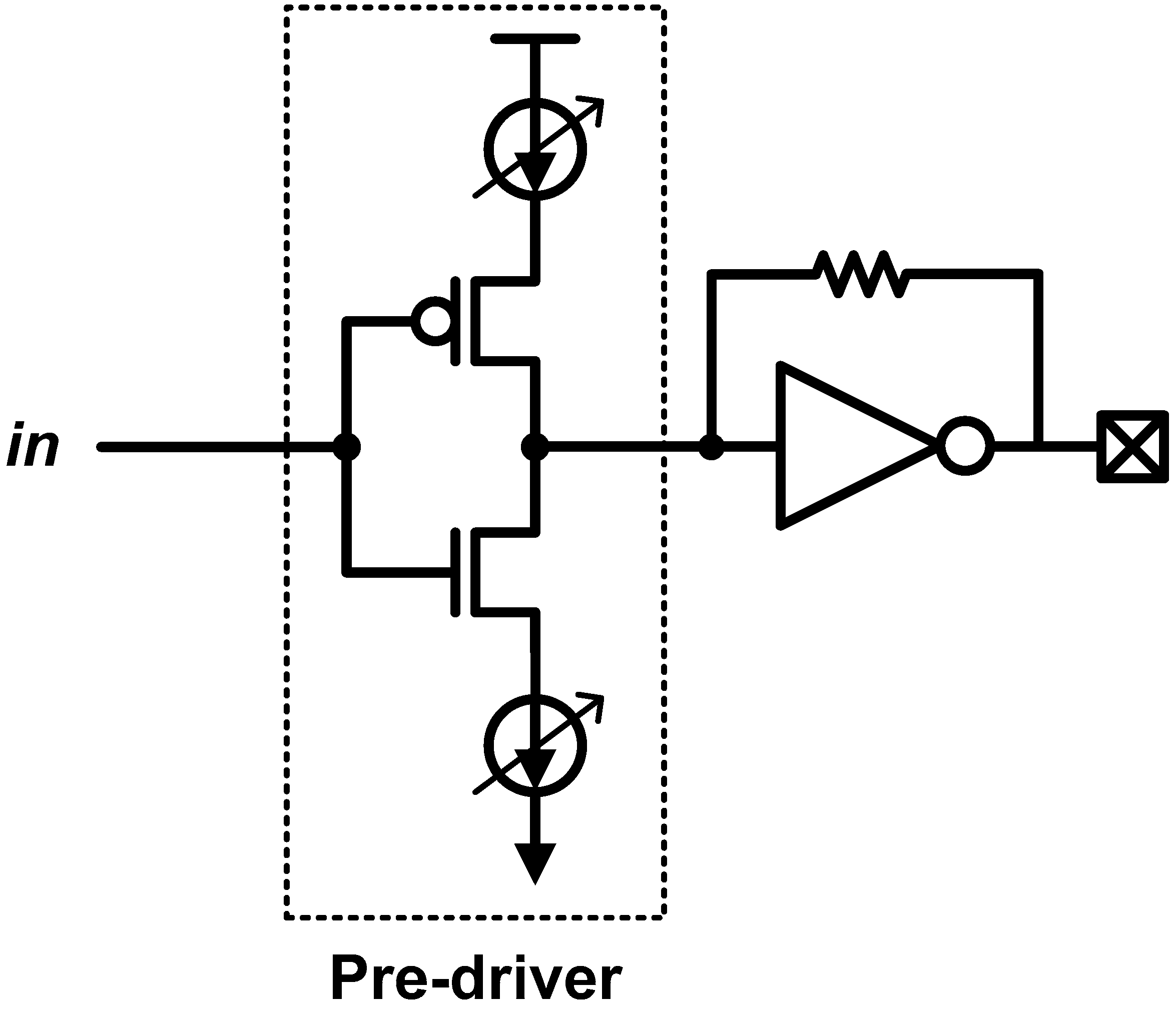

4. Output Driver for High-Speed Wireline Communication

5. Conclusions

Funding

Conflicts of Interest

References

- Vertregt, M. The analog challenge of nanometer CMOS. In Proceedings of the 2006 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–8. [Google Scholar]

- Horowitz, M. 1.1 computing’s energy problem (and what we can do about it). In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 10–14. [Google Scholar]

- Babayan-Mashhadi, S.; Lotfi, R. Analysis and design of a low-voltage low-power double-tail comparator. IEEE Trans. VLSI Syst. 2013, 22, 343–352. [Google Scholar] [CrossRef]

- Rajput, S.S.; Jamuar, S.S. Low voltage analog circuit design techniques. IEEE Circuits Syst. Mag. 2002, 2, 24–42. [Google Scholar] [CrossRef]

- Hou, C. 1.1 A smart design paradigm for smart chips. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Frsancisco, CA, USA, 5–9 February 2017; pp. 8–13. [Google Scholar]

- Bae, W.; Jeong, G.S.; Kim, Y.; Chi, H.K.; Jeong, D.K. Design of silicon photonic interconnect ICS in 65-nm CMOS technology. IEEE Trans. VLSI Syst. 2015, 24, 2234–2243. [Google Scholar] [CrossRef]

- Frans, Y.; McLeod, S.; Hedayati, H.; Elzeftawi, M.; Namkoong, J.; Lin, W.; Im, J.; Upadhyaya, P.; Chang, K. A 40-to-64 Gb/s NRZ transmitter with supply-regulated front-end in 16 nm FinFET. IEEE J. Solid-State Circuits 2016, 51, 3167–3177. [Google Scholar] [CrossRef]

- Okuma, Y.; Ishida, K.; Ryu, Y.; Zhang, X.; Chen, P.H.; Watanabe, K.; Sakurai, T. 0.5-V input digital LDO with 98.7% current efficiency and 2.7-µA quiescent current in 65nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Chae, Y.; Han, G. Low voltage, low power, inverter-based switched-capacitor delta-sigma modulator. IEEE J. Solid-State Circuits 2009, 44, 458–472. [Google Scholar] [CrossRef]

- Thompson, S.E.; Sun, G.; Choi, Y.S.; Nishida, T. Uniaxial-process-induced strained-Si: Extending the CMOS roadmap. IEEE Trans. Electron Devices 2006, 53, 1010–1020. [Google Scholar] [CrossRef]

- Pidin, S.; Mori, T.; Inoue, K.; Fukuta, S.; Itoh, N.; Mutoh, E.; Saiki, T. A novel strain enhanced CMOS architecture using selectively deposited high tensile and high compressive silicon nitride films. In Proceedings of the IEDM Technical Digest. IEEE International Electron Devices Meeting, San Francisco, CA, USA, 13–15 December 2004; pp. 213–216. [Google Scholar]

- Ghani, T.; Armstrong, M.; Auth, C.; Bost, M.; Charvat, P.; Glass, G.; McIntyre, B. A 90nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 8–10 December 2003; pp. 11.6.1–11.6.3. [Google Scholar]

- Jeong, G.S.; Chu, S.H.; Kim, Y.; Jang, S.; Kim, S.; Bae, W.; Jeong, D.K. A 20 Gb/s 0.4 pJ/b Energy-Efficient Transmitter Driver Utilizing Constant-Gm Bias. IEEE J. Solid-State Circuits 2016, 51, 2312–2327. [Google Scholar] [CrossRef]

- Woodward, T.K.; Krishnamoorthy, A.V. 1 Gbit/s CMOS photoreceiver with integrated detector operating at 850 nm. Electron. Lett. 1998, 34, 1252–1253. [Google Scholar] [CrossRef]

- Pan, Q.; Wang, Y.; Yue, C.P. A 42-dBΩ 25-Gb/s CMOS Transimpedance Amplifier with Multiple-Peaking Scheme for Optical Communications. IEEE Transactions on Circuits and Systems II: Express Briefs; IEEE: Piscataway, NJ, USA, 2019. [Google Scholar]

- Martins, M.A.; Mak, P.I.; Martins, R.P. A 0.02-to-6GHz SDR balun-LNA using a triple-stage inverter-based amplifier. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems, Seoul, North Korea, 20–23 May 2012; pp. 472–475. [Google Scholar]

- Costa, A.L.T.; Klimach, H.; Bampi, S. Ultra-low voltage wideband inductorless balun LNA with high gain and high IP2 for sub-GHz applications. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 289–292. [Google Scholar]

- Proesel, J.; Schow, C.; Rylyakov, A. 25Gb/s 3.6 pJ/b and 15Gb/s 1.37 pJ/b VCSEL-based optical links in 90 nm CMOS. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 418–420. [Google Scholar]

- Kim, J.; Buckwalter, J.F. A 40-Gb/s optical transceiver front-end in 45 nm SOI CMOS. IEEE J. Solid-State Circuits 2012, 47, 615–626. [Google Scholar] [CrossRef]

- Sun, C.; Georgas, M.; Orcutt, J.; Moss, B.; Chen, Y.H.; Shainline, J.; Miller, D. A monolithically-integrated chip-to-chip optical link in bulk CMOS. IEEE J. Solid-State Circuits 2015, 50, 828–844. [Google Scholar] [CrossRef]

- Chu, S.H.; Bae, W.; Jeong, G.S.; Jang, S.; Kim, S.; Joo, J.; Kim, G.; Jeong, D.K. A 22 to 26.5 Gb/s optical receiver with all-digital clock and data recovery in a 65 nm CMOS process. IEEE J. Solid-State Circuits 2015, 50, 2603–2612. [Google Scholar] [CrossRef]

- Subramaniyan, H.K.; Klumperink, E.A.; Srinivasan, V.; Kiaei, A.; Nauta, B. RF transconductor linearization robust to process, voltage and temperature variations. IEEE J. Solid-State Circuits 2015, 50, 2591–2602. [Google Scholar] [CrossRef]

- Yu, K.; Li, C.; Li, H.; Titriku, A.; Shafik, A.; Wang, B.; Chiang, P.Y. A 25 gb/s hybrid-integrated silicon photonic source-synchronous receiver with microring wavelength stabilization. IEEE J. Solid-State Circuits 2016, 51, 2129–2141. [Google Scholar] [CrossRef]

- Shopov, S.; Voinigescu, S.P. A 3 × 60 Gb/s Transmitter/Repeater Front-End With 4.3 VPP Single-Ended Output Swing in a 28nm UTBB FD-SOI Technology. IEEE J. Solid-State Circuits 2016, 51, 1651–1662. [Google Scholar] [CrossRef]

- Ozkaya, I.; Cevrero, A.; Francese, P.A.; Menolfi, C.; Morf, T.; Brändli, M.; Kossel, M. A 64-Gb/s 1.4-pJ/b NRZ optical receiver data-path in 14-nm CMOS FinFET. IEEE J. Solid-State Circuits 2017, 52, 3458–3473. [Google Scholar] [CrossRef]

- Fard, M.M.P.; Liboiron-Ladouceur, O.; Cowan, G.E. 1.23-pJ/bit 25-Gb/s Inductor-Less Optical Receiver With Low-Voltage Silicon Photodetector. IEEE J. Solid-State Circuits 2018, 53, 1793–1805. [Google Scholar] [CrossRef]

- Hiratsuka, A.; Tsuchiya, A.; Onodera, H. Power-bandwidth trade-off analysis of multi-stage inverter-type transimpedance amplifier for optical communication. In Proceedings of the 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), Medford, MA, USA, 6–9 August 2017; pp. 795–798. [Google Scholar]

- Jeong, G.S.; Bae, W.; Jeong, D.K. Review of CMOS integrated circuit technologies for high-speed photo-detection. Sensors 2017, 17, 1962. [Google Scholar] [CrossRef]

- Li, H.; Balamurugan, G.; Jaussi, J.; Casper, B. A 112 Gb/s PAM4 Linear TIA with 0.96 pJ/bit Energy Efficiency in 28 nm CMOS. In Proceedings of the ESSCIRC 2018-IEEE 44th European Solid State Circuits Conference (ESSCIRC), Dresden, Germany, 3–6 September 2018; pp. 238–241. [Google Scholar]

- Wang, P.; Ytterdal, T. A 54- μW Inverter-Based Low-Noise Single-Ended to Differential VGA for Second Harmonic Ultrasound Probes in 65-nm CMOS. IEEE Trans. Circuits Syst. I Express Br. 2016, 63, 623–627. [Google Scholar]

- Li, H.; Chen, S.; Yang, L.; Bai, R.; Hu, W.; Zhong, F.Y.; Chiang, P.Y. A 0.8 V, 560fJ/bit, 14Gb/s injection-locked receiver with input duty-cycle distortion tolerable edge-rotating 5/4X sub-rate CDR in 65nm CMOS. In Proceedings of the 2014 Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 10–13 June 2014; pp. 1–2. [Google Scholar]

- Bae, J.; Kim, J.Y.; Yoo, H.J.A. 0.6 pJ/b 3Gb/s/ch Transceiver in 0.18 μm CMOS for 10mm On-chip Interconnects. In Proceedings of the 2008 IEEE International Symposium on Circuits and Systems, Seattle, WA, USA, 18–21 May 2008; pp. 2861–2864. [Google Scholar]

- Chen, S.; Zhou, L.; Zhuang, I.; Im, J.; Melek, D.; Namkoong, J.; Chang, K. A 4-to-16GHz inverter-based injection-locked quadrature clock generator with phase interpolators for multi-standard I/Os in 7nm FinFET. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 390–392. [Google Scholar]

- Wang, H.; Lee, J. A 21-Gb/s 87-mW transceiver with FFE/DFE/analog equalizer in 65-nm CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 909–920. [Google Scholar] [CrossRef]

- Song, Y.H.; Bai, R.; Hu, K.; Yang, H.W.; Chiang, P.Y.; Palermo, S. A 0.47–0.66 pJ/bit, 4.8–8 Gb/s I/O transceiver in 65 nm CMOS. IEEE J. Solid-State Circuits 2013, 48, 1276–1289. [Google Scholar] [CrossRef]

- Savoj, J.; Hsieh, K.C.H.; An, F.T.; Gong, J.; Im, J.; Jiang, X.; Turker, D.Z. A low-power 0.5–6.6 Gb/s wireline transceiver embedded in low-cost 28 nm FPGAs. IEEE J. Solid-State Circuits 2013, 48, 2582–2594. [Google Scholar] [CrossRef]

- Menolfi, C.; Toifl, T.; Buchmann, P.; Kossel, M.; Morf, T.; Weiss, J.; Schmatz, M. A 16Gb/s source-series terminated transmitter in 65nm CMOS SOI. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2007; pp. 446–614. [Google Scholar]

- Song, Y.H.; Yang, H.W.; Li, H.; Chiang, P.Y.; Palermo, S. An 8–16 Gb/s, 0.65–1.05 pJ/b, voltage-mode transmitter with analog impedance modulation equalization and sub-3 ns power-state transitioning. IEEE J. Solid-State Circuits 2014, 49, 2631–2643. [Google Scholar] [CrossRef]

- Bae, W.; Ju, H.; Park, K.; Cho, S.Y.; Jeong, D.K. A 7.6 mW, 414 fs RMS-jitter 10 GHz phase-locked loop for a 40 Gb/s serial link transmitter based on a two-stage ring oscillator in 65 nm CMOS. IEEE J. Solid-State Circuits 2016, 51, 2357–2367. [Google Scholar] [CrossRef]

- Ju, H.; Choi, M.C.; Jeong, G.S.; Bae, W.; Jeong, D.K. A 28 Gb/s 1.6 pJ/b PAM-4 Transmitter Using Fractionally Spaced 3-Tap FFE and $ G_ {m} $-Regulated Resistive-Feedback Driver. IEEE Trans. Circuits Syst. Ii: Express Br. 2017, 64, 1377–1381. [Google Scholar] [CrossRef]

- Jeong, G.S.; Hwang, J.; Choi, H.S.; Do, H.; Koh, D.; Yun, D.; Joo, J. 25-Gb/s Clocked Pluggable Optics for High-Density Data Center Interconnections. IEEE Trans. Circuits Syst. Ii: Express Br. 2018, 65, 1395–1399. [Google Scholar] [CrossRef]

- Bae, W.; Ju, H.; Park, K.; Han, J.; Jeong, D.K. A supply-scalable-serializing transmitter with controllable output swing and equalization for next-generation standards. IEEE Trans. Ind. Electron. 2018, 65, 5979–5989. [Google Scholar] [CrossRef]

- Bae, W.; Jeong, D.K. A power-efficient 600-mVpp voltage-mode driver with independently matched pull-up and pull-down impedances. Int. J. Circuit Theory Appl. 2015, 43, 2057–2071. [Google Scholar] [CrossRef]

- Ahn, G.; Jeong, D.K.; Kim, G. A 2-Gbaud 0.7-V swing voltage-mode driver and on-chip terminator for high-speed NRZ data transmission. IEEE J. Solid-State Circuits 2000, 35, 915–918. [Google Scholar]

- Fukuda, K.; Yamashita, H.; Ono, G.; Nemoto, R.; Suzuki, E.; Masuda, N.; Saito, T. A 12.3-mW 12.5-Gb/s complete transceiver in 65-nm CMOS process. IEEE J. Solid-State Circuits 2010, 45, 2838–2849. [Google Scholar] [CrossRef]

- Kaviani, K.; Wu, T.; Wei, J.; Amirkhany, A.; Shen, J.; Chin, T.J.; Chuang, B.R. A tri-modal 20-Gbps/link differential/DDR3/GDDR5 memory interface. IEEE J. Solid-State Circuits 2012, 47, 926–937. [Google Scholar] [CrossRef]

- Kaviani, K.; Amirkhany, A.; Huang, C.; Le, P.; Beyene, W.T.; Madden, C.; Yuan, X.C. A 0.4-mW/Gb/s near-ground receiver front-end with replica transconductance termination calibration for a 16-Gb/s source-series terminated transceiver. IEEE J. Solid-State Circuits 2013, 48, 636–648. [Google Scholar] [CrossRef]

- Chan, K.L.; Tan, K.H.; Frans, Y.; Im, J.; Upadhyaya, P.; Lim, S.W.; Chiang, P.C. A 32.75-Gb/s voltage-mode transmitter with three-tap FFE in 16-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 2663–2678. [Google Scholar] [CrossRef]

- Upadhyaya, P.; Poon, C.F.; Lim, S.W.; Cho, J.; Roldan, A.; Zhang, W.; Zhang, H. A Fully Adaptive 19–58-Gb/s PAM-4 and 9.5–29-Gb/s NRZ Wireline Transceiver with Configurable ADC in 16-nm FinFET. IEEE J. Solid-State Circuits 2018, 54, 18–28. [Google Scholar] [CrossRef]

- Bae, W.; Jeong, G.S.; Jeong, D.K. A 1-pJ/bit, 10-Gb/s/ch forwarded-clock transmitter using a resistive feedback inverter-based driver in 65-nm CMOS. IEEE Trans. Circuits Syst. Express Br. 2016, 63, 1106–1110. [Google Scholar] [CrossRef]

- Park, S.M.; Toumazou, C. A packaged low-noise high-speed regulated cascode transimpedance amplifier using a 0.6 µm N-well CMOS technology. In Proceedings of the 26th European Solid-State Circuits Conference, Stockholm, Sweden, 19–21 September 2000; pp. 431–434. [Google Scholar]

- Kromer, C.; Sialm, G.; Morf, T.; Schmatz, M.L.; Ellinger, F.; Erni, D.; Jackel, H. A low-power 20-GHz 52-dB/spl Omega/transimpedance amplifier in 80-nm CMOS. IEEE J. Solid-State Circuits 2004, 39, 885–894. [Google Scholar] [CrossRef]

- Bae, W.; Nikolić, B.; Jeong, D.K. Use of Phase Delay Analysis for Evaluating Wideband Circuits: An Alternative to Group Delay Analysis. Ieee Trans. VLSI Syst. 2017, 25, 3543–3547. [Google Scholar] [CrossRef]

- Casper, B.; O’Mahony, F. Clocking analysis, implementation and measurement techniques for high-speed data links—A tutorial. IEEE Trans. Circuits Syst. I: Regul. Pap. 2009, 56, 17–39. [Google Scholar] [CrossRef]

- Jeong, D.K.; Borriello, G.; Hodges, D.A.; Katz, R.H. Design of PLL-based clock generation circuits. IEEE J. Solid-State Circuits 1987, 22, 255–261. [Google Scholar] [CrossRef]

- Mansuri, M.; Yang, C.K. A low-power adaptive bandwidth PLL and clock buffer with supply-noise compensation. IEEE J. Solid-State Circuits 2003, 38, 1804–1812. [Google Scholar] [CrossRef]

- Johns, D.A.; Martin, K. Analog Integrated Circuit Design; John Wiley & Sons: Hoboken, NJ, USA, 2008. [Google Scholar]

© 2019 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, W. CMOS Inverter as Analog Circuit: An Overview. J. Low Power Electron. Appl. 2019, 9, 26. https://doi.org/10.3390/jlpea9030026

Bae W. CMOS Inverter as Analog Circuit: An Overview. Journal of Low Power Electronics and Applications. 2019; 9(3):26. https://doi.org/10.3390/jlpea9030026

Chicago/Turabian StyleBae, Woorham. 2019. "CMOS Inverter as Analog Circuit: An Overview" Journal of Low Power Electronics and Applications 9, no. 3: 26. https://doi.org/10.3390/jlpea9030026

APA StyleBae, W. (2019). CMOS Inverter as Analog Circuit: An Overview. Journal of Low Power Electronics and Applications, 9(3), 26. https://doi.org/10.3390/jlpea9030026