A Sub-Threshold 8T SRAM Macro with 12.29 nW/KB Standby Power and 6.24 pJ/access for Battery-Less IoT SoCs

Abstract

:1. Introduction

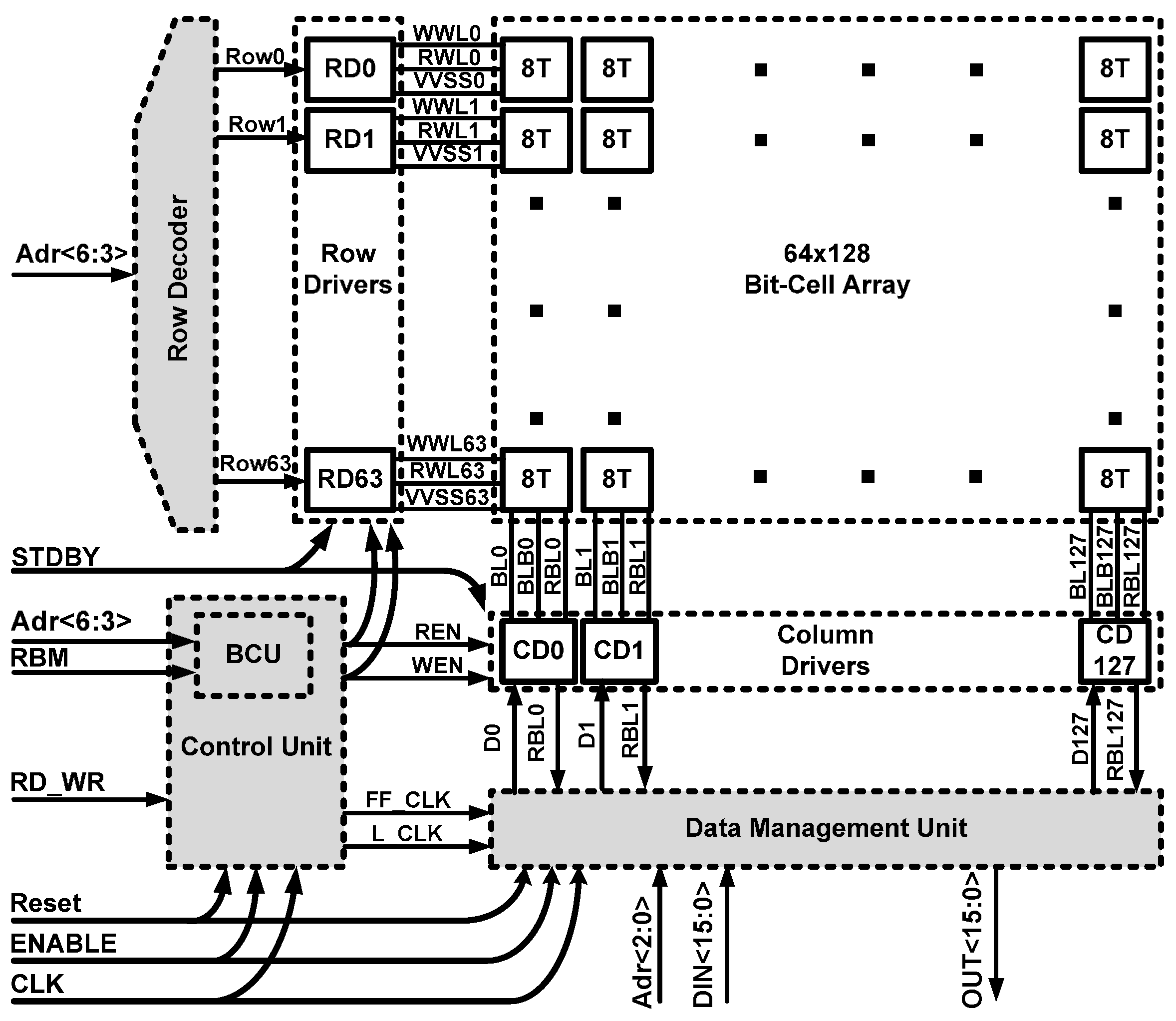

2. Proposed Array Structure

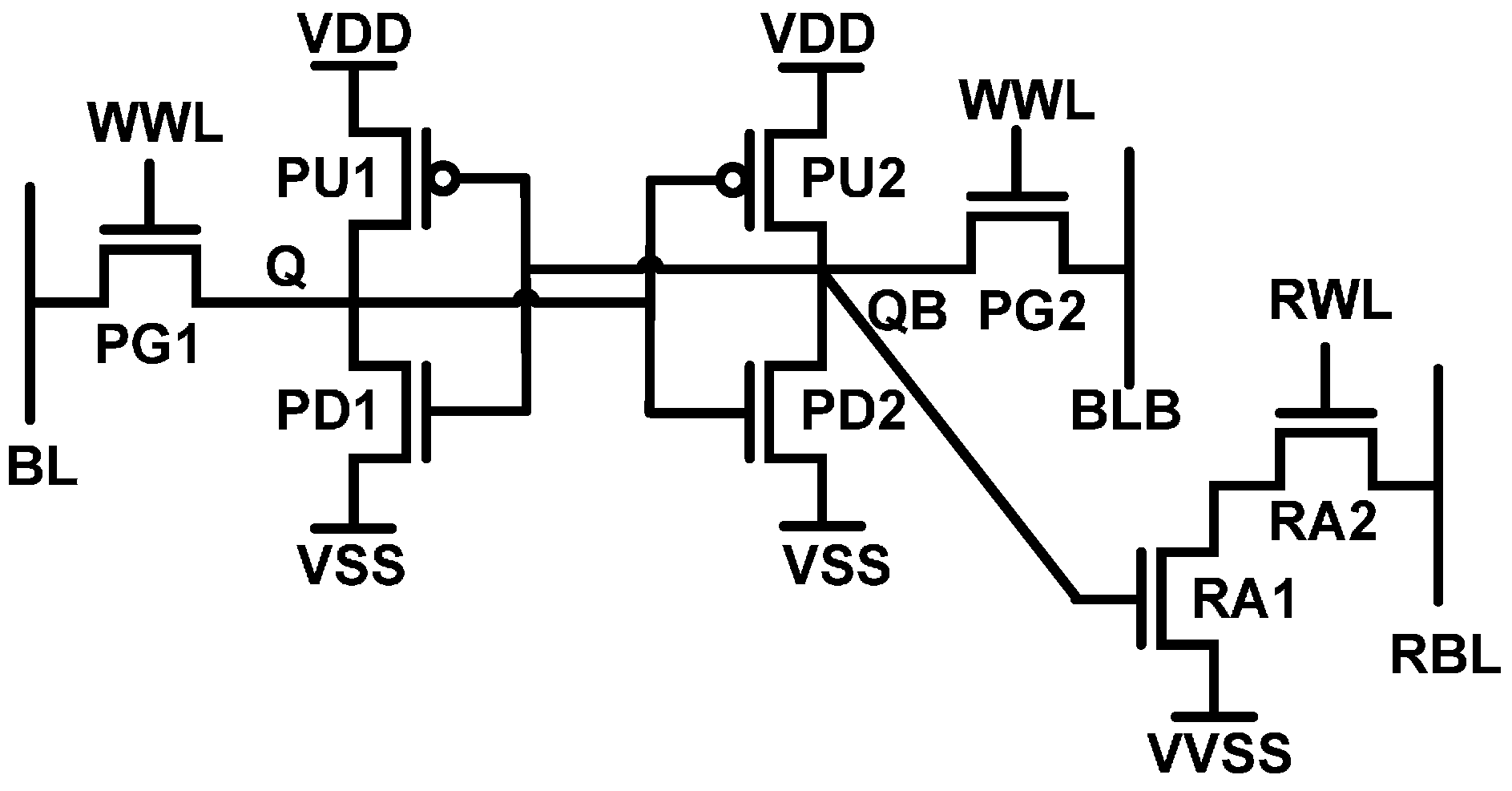

2.1. Bit-Cell Array

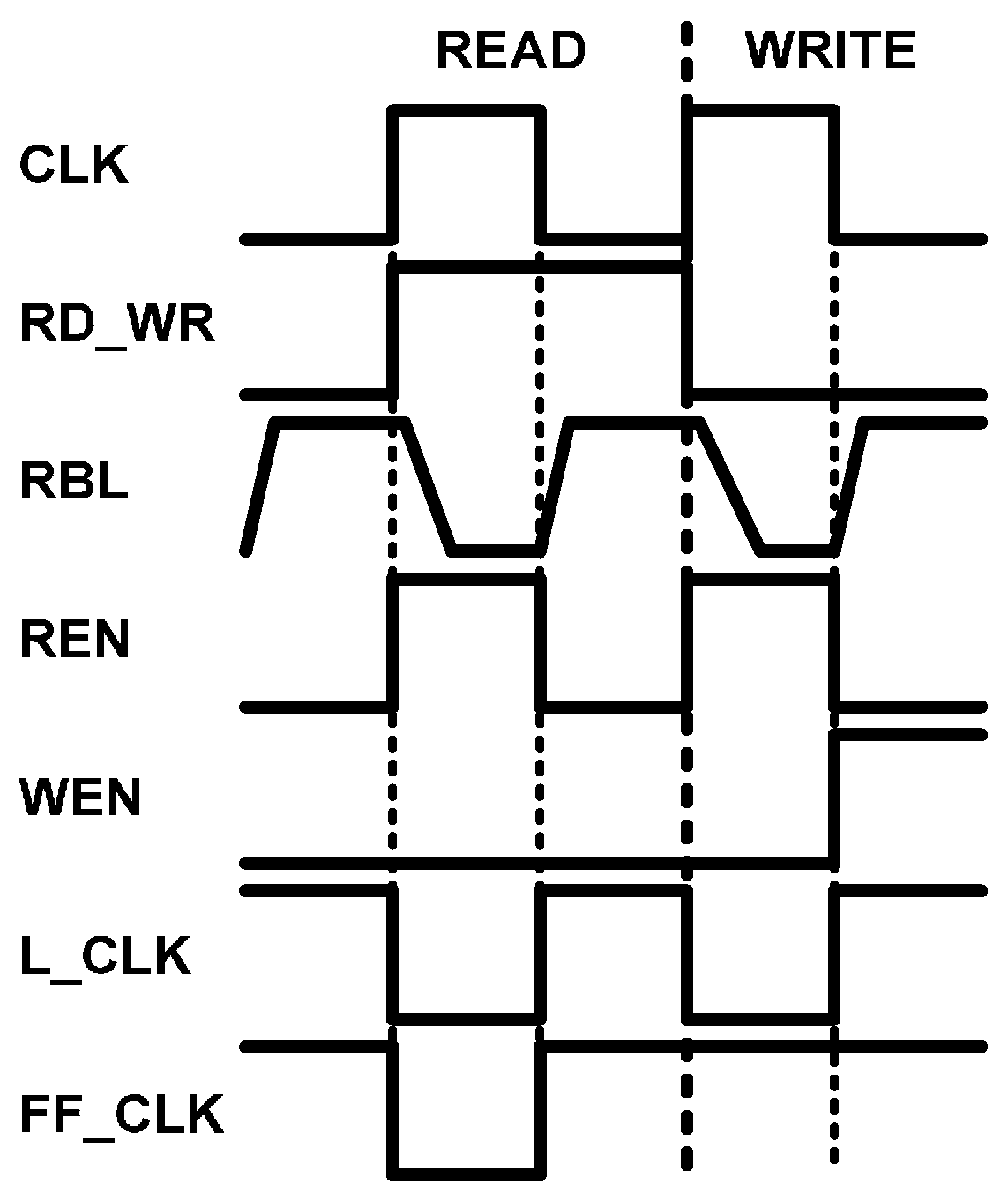

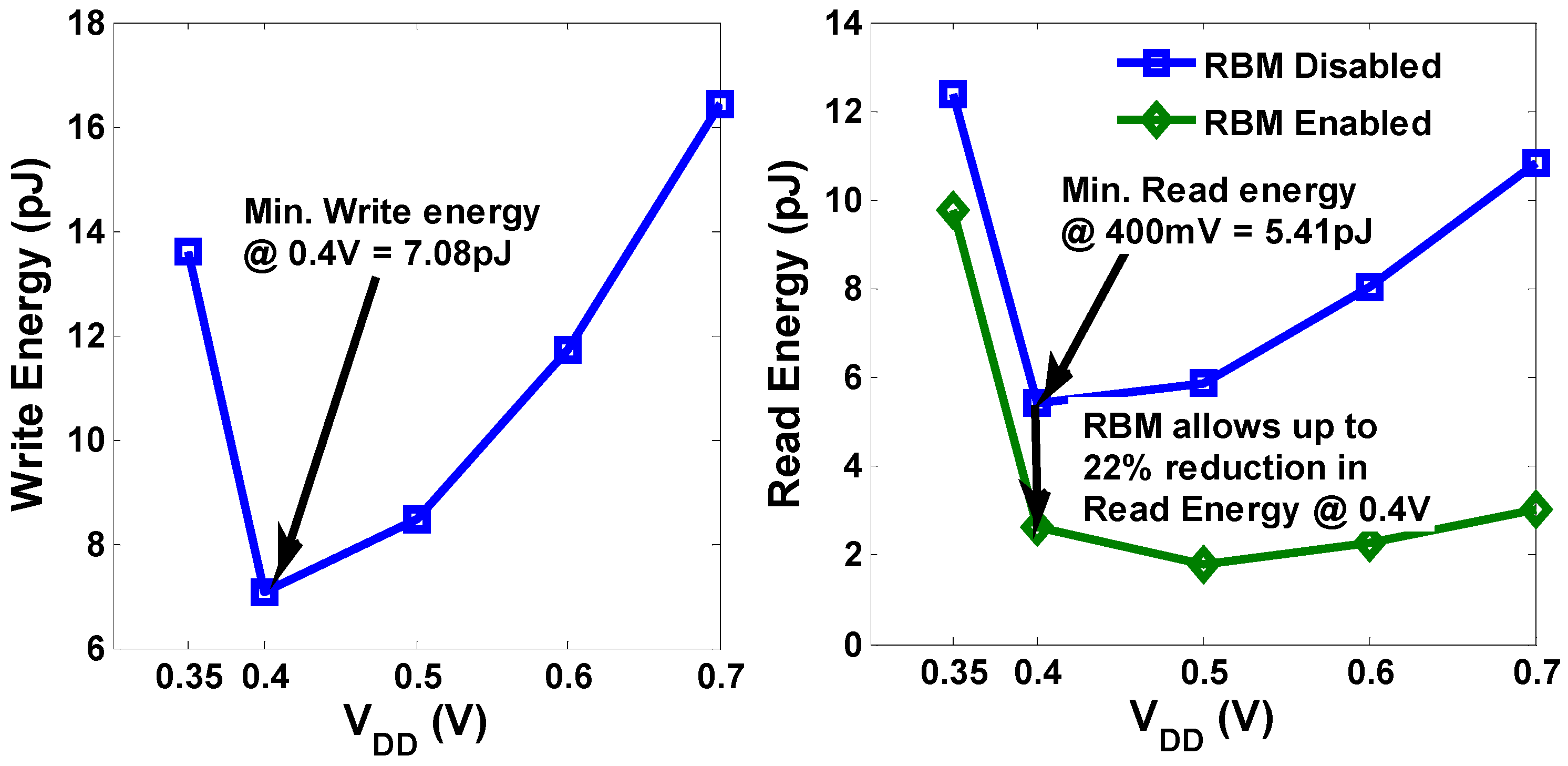

2.1.1. Read Operation

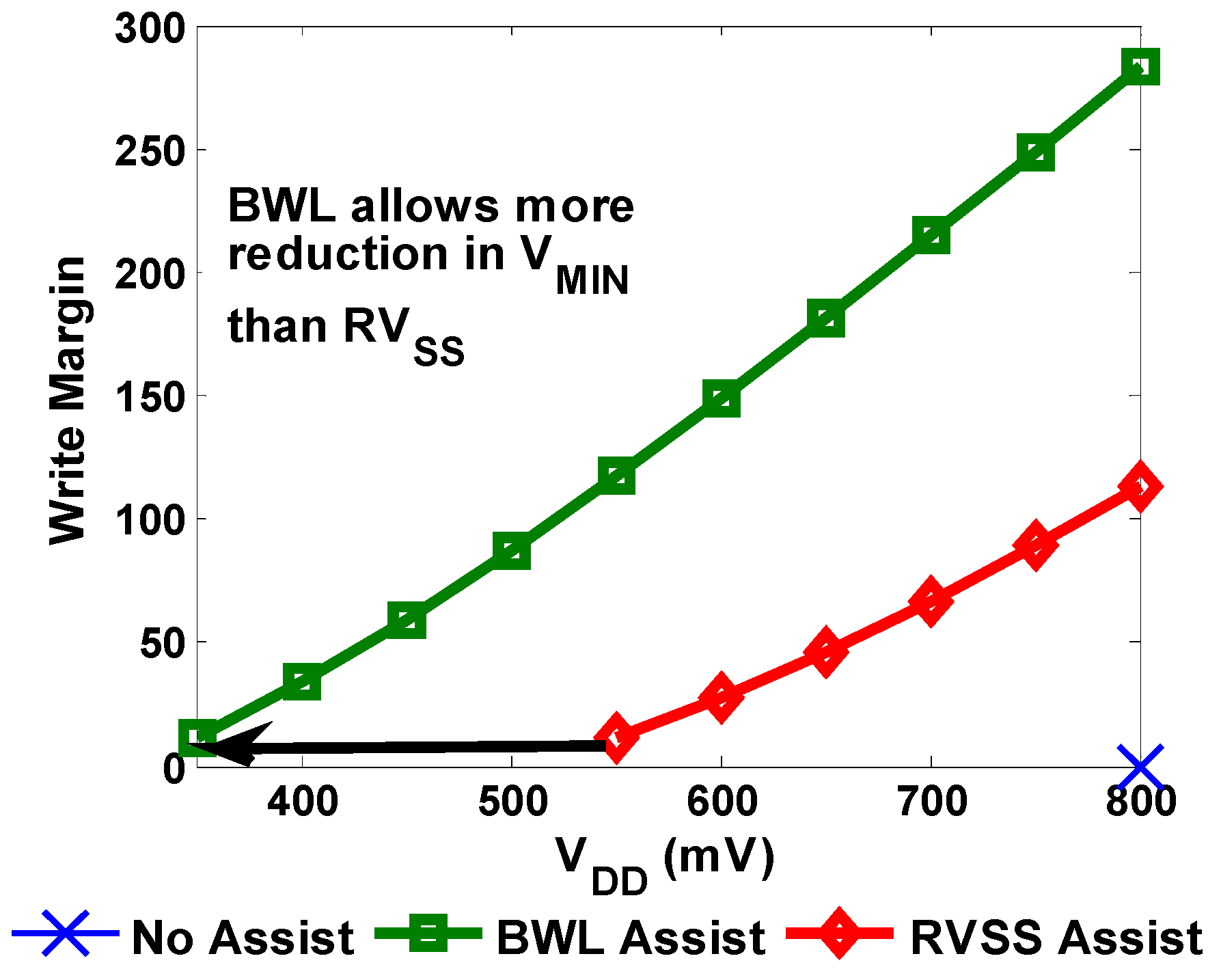

2.1.2. Write Operation

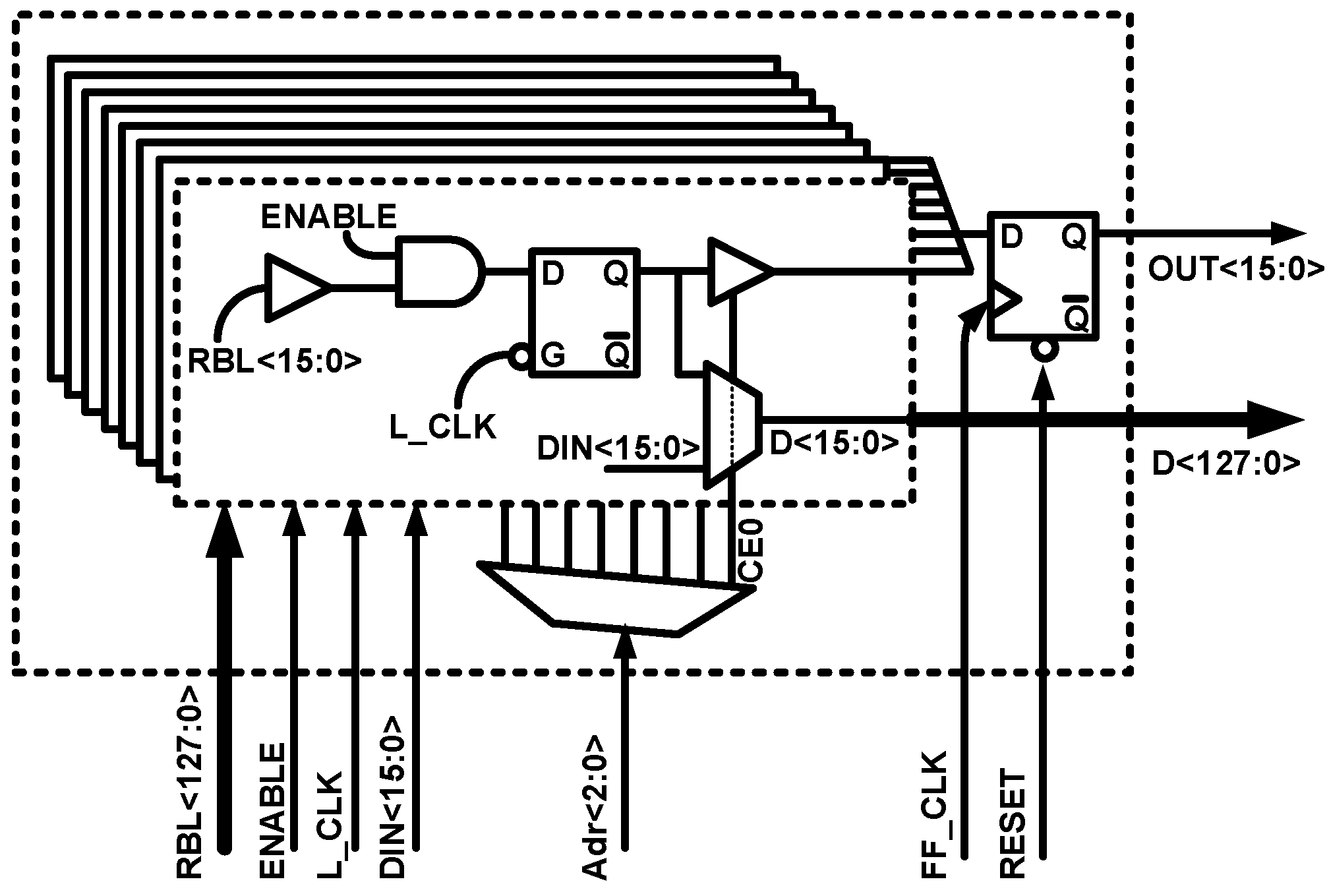

2.2. Control and Data Management Units

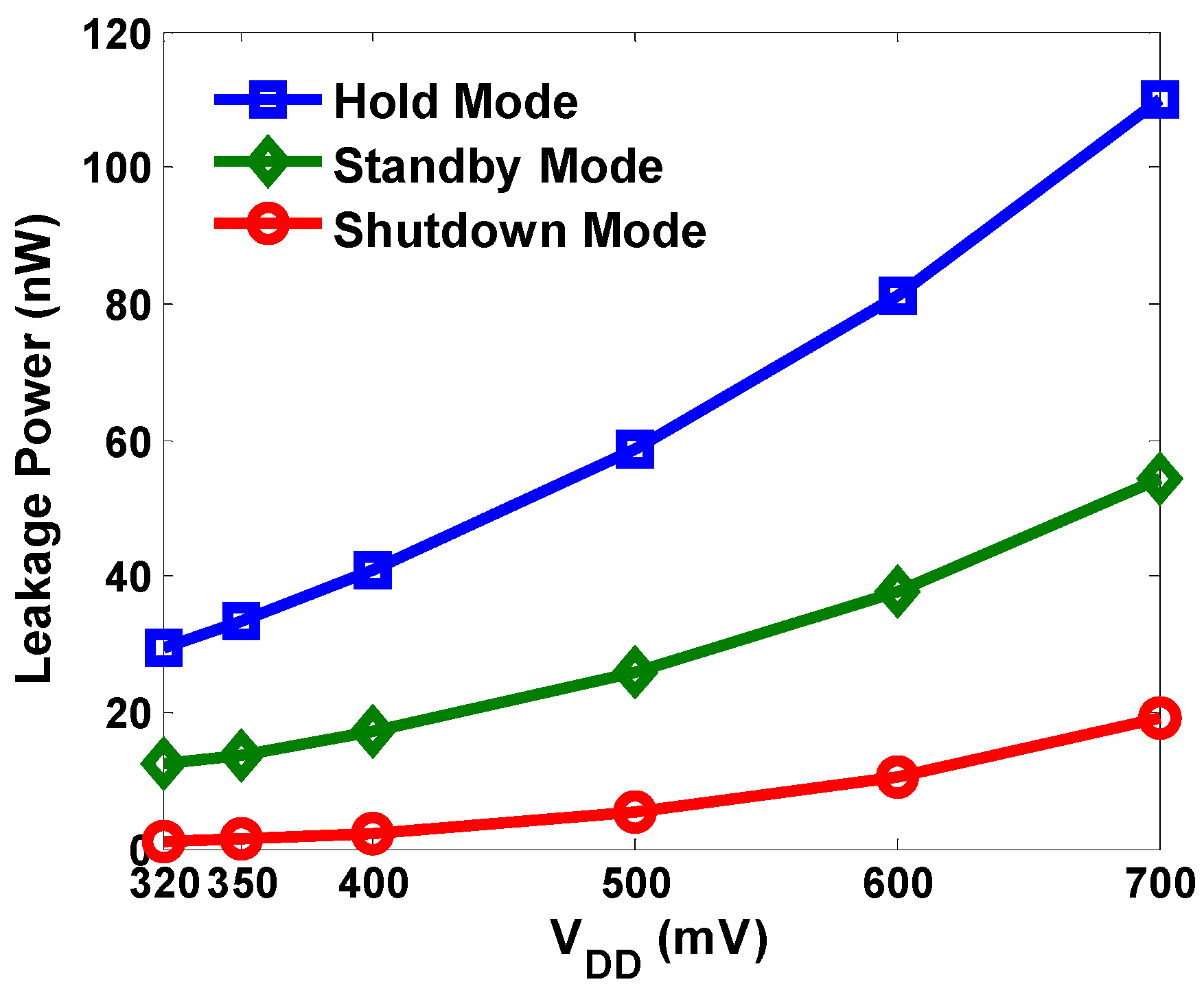

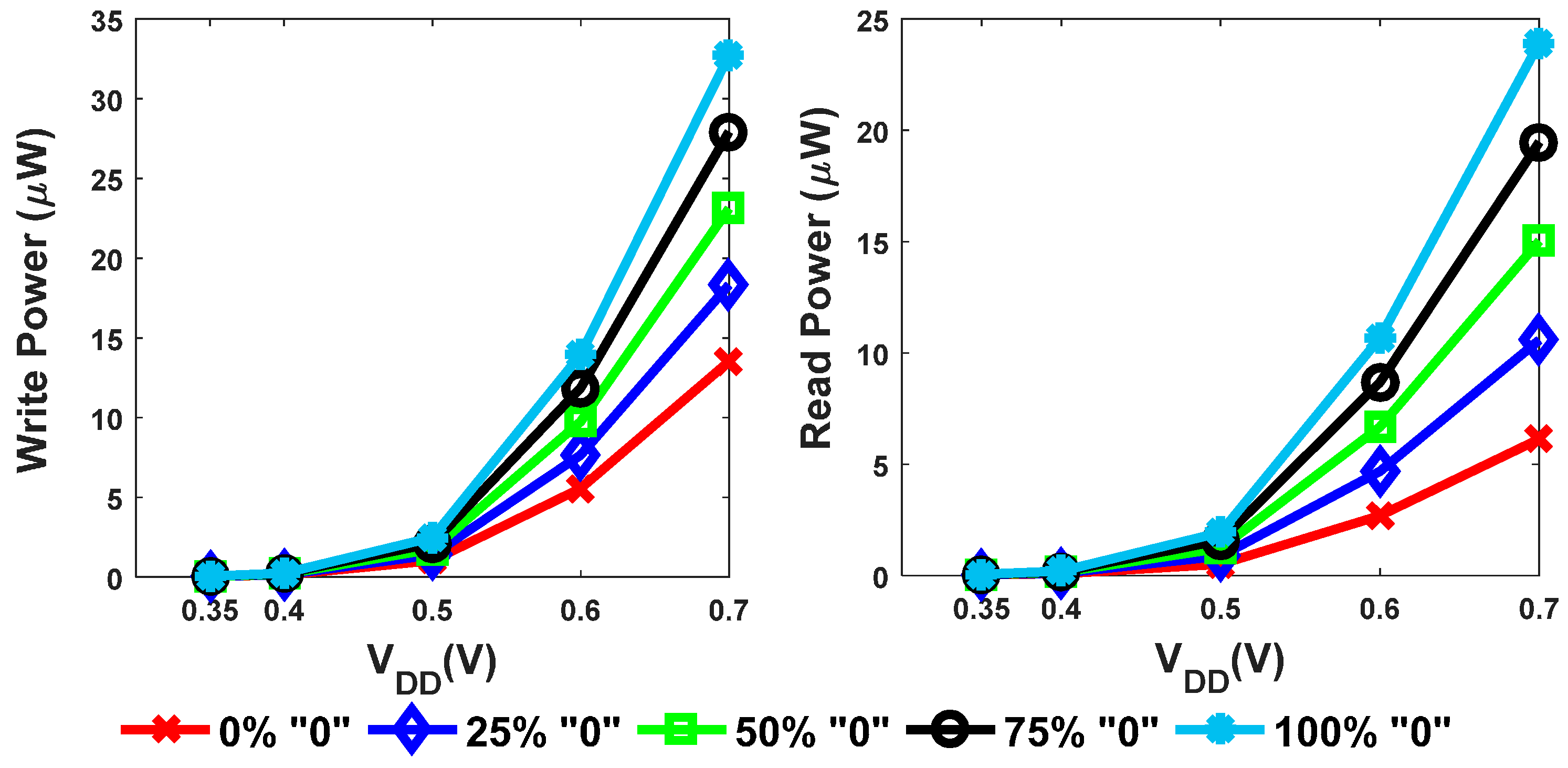

2.3. Power Reduction Features

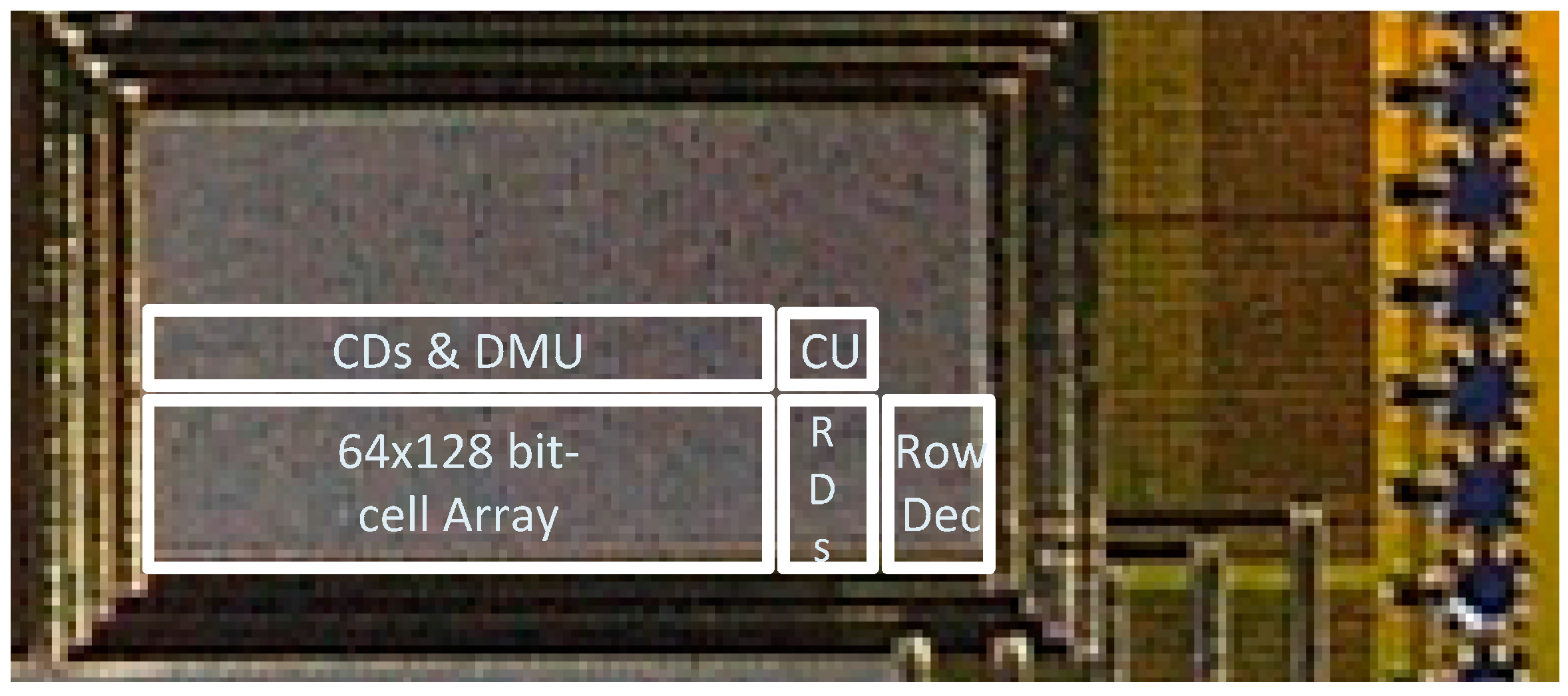

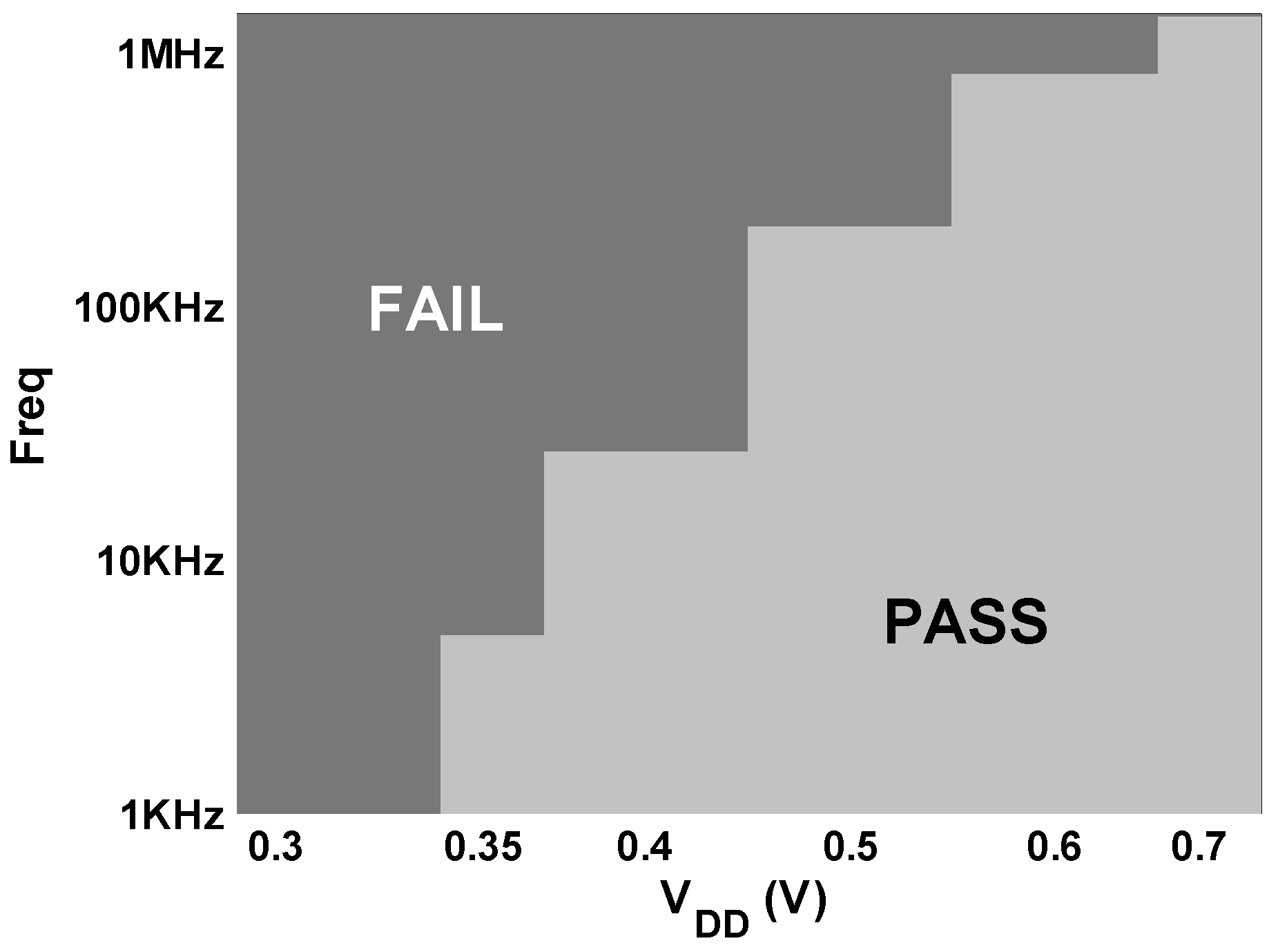

3. Chip Results

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Klinefelter, A.; Roberts, N.E.; Shakhsheer, Y.; Gonzalez, P.; Shrivastava, A.; Roy, A.; Craig, K.; Faisal, M.; Boley, J.; Seunghyun, O.; et al. 21.3 A 6.45 μW self-powered IoT SoC with integrated energy-harvesting power management and ULP asymmetric radios. In Proceedings of the IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 1–3.

- Zhang, Y.; Zhang, F.; Shakhsheer, Y.; Silver, J.D.; Klinefelter, A.; Nagaraju, M.; Boley, J.; Pandey, J.; Shrivastava, A.; Carlson, E.J.; et al. A Batteryless 19 μW MICS/ISM-Band Energy Harvesting Body Sensor Node SoC for ExG Applications. IEEE J. Solid State Circuits 2013, 48, 199–213. [Google Scholar] [CrossRef]

- Calhoun, B.; Wang, A.; Chandrakasan, A.P. Modeling and Sizing for Minimum Energy Operation in Subthreshold Circuit. J. Solid State Circuits 2005, 40, 1778–1786. [Google Scholar] [CrossRef]

- Verma, N.; Chandrakasan, A.P. A 256 kb 65 nm 8T Subthreshold SRAM Employing Sense-Amplifier Redundancy. J. Solid State Circuits 2008, 43, 141–149. [Google Scholar] [CrossRef]

- Lutkemeier, S.; Jungeblut, T.; Berge, H.K.O.; Aunet, S.; Porrmann, M.; Ruckert, U. A 65nm 32 b Subthreshold Processor with 9T Multi-Vt SRAM and Adaptive Supply Voltage Control. J. Solid State Circuits 2013, 48, 8–19. [Google Scholar] [CrossRef]

- Meinerzhagen, P.; Andersson, O.; Mohammadi, B.; Sherazi, Y.; Burg, A.; Rodrigues, J.N. A 500 fW/bit 14 fJ/bit-access 4 kb standard-cell based sub-VT memory in 65 nm CMOS. In Proceedings of the ESSCIRC, 2012, Bordeaux, France, 17–21 September 2012; pp. 321–324.

- Kulkarni, J.; Khellah, M.; Tschanz, J.; Geuskens, B.; Jain, R.; Kim, S.; De, V. Dual-VCC 8T-bitcell SRAM Array in 22 nm tri-gate CMOS for energy-efficient operation across wide dynamic voltage range. In Proceedings of the IEEE Symposium on VLSI Circuits (VLSIC), Kyoto, Japan, 11–13 June 2013.

- Raychowdhury, A.; Geuskens, B.; Kulkarni, J.; Tschanz, J.; Bowman, K.; Karnik, T.; Lu, S.-L.; De, V.; Khellah, M.M. PVT-and-Aging Adaptive Wordline Boosting for 8T SRAM Power Reduction. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7–11 February 2010; pp. 352–353.

- Chang, I.J.; Kim, J.-J.; Park, S.P.; Roy, K. A 32 kb 10T sub-threshold SRAM array with bit-interleaving and differential read scheme in 90 nm CMOS. J. Solid State Circuits 2009, 44, 650–658. [Google Scholar] [CrossRef]

- Kim, T.H.; Liu, J.; Keane, J.; Kim, C.H. A High-Density Subthreshold SRAM with Data-Independent Bitline Leakage and Virtual Ground Replica Scheme. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2007; pp. 330–606.

- Ghaed, M.H.; Chen, G.; Haque, R.-U.; Wieckowski, M.; Kim, Y.; Kim, G.; Lee, Y.; Lee, I.; Fick, D.; Kim, D.; et al. Circuits for a Cubic-Millimeter Energy-Autonomous Wireless Intraocular Pressure Monitor. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 3152–3162. [Google Scholar] [CrossRef]

- Liu, X.; Zhou, J.; Yang, Y.K.; Wang, B.; Lan, J.J.; Wang, C.; Luo, J.W.; Wang, L.G.; Kim, T.T.-H.; Minkyu, J. A 457 nW Near-Threshold Cognitive Multi-Functional ECG Processor for Long-Term Cardiac Monitoring. J. Solid State Circuits 2014, 49, 2422–2434. [Google Scholar] [CrossRef]

- Yahya, F.B.; Patel, H.N.; Chandra, V.; Calhoun, B.H. Combined SRAM read/write assist techniques for near/sub-threshold voltage operation. In Proceedings of the Asia Symposium on Quality Electronic Design (ASQED), Kula Lumpur, Malaysia, 4–5 August 2015; pp. 1–6.

- Sinangil, M.E.; Chandrakasan, A.P. Application-Specific SRAM Design Using Output Prediction to Reduce Bit-Line Switching Activity and Statistically Gated Sense Amplifiers for Up to 1.9x Lower Energy/Access. J. Solid State Circuits 2014, 49, 107–117. [Google Scholar] [CrossRef]

- Stan, M.R.; Burleson, W.P. Bus-invert coding for low-power I/O. IEEE Trans. Very Large Scale Int. (VLSI) Syst. 1995, 3, 49–58. [Google Scholar] [CrossRef]

- Chandra, V.; Pietrzyk, C.; Aitken, R. On the efficacy of write-assist techniques in low voltage nanoscale SRAMs. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 8–12 March 2010; pp. 345–350.

- Guo, Z.; Carlson, A.; Pang, L.-K.; Duong, K.; Liu, T.-J.K.; Nikolic, B. Large-scale read/write margin measurement in 45nm CMOS SRAM arrays. In Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–20 June 2008; pp. 42–43.

- Wang, Y.; Hong, J.A.; Bhattacharya, U.; Chen, Z.P.; Coan, T.; Hamzaoglu, F.; Hafez, W.M.; Jan, C.-H.; Kolar, P.; Kulkarni, S.H.; et al. A 1.1 GHz 12 μA/Mb-leakage SRAM design in 65 nm ultra-low-power CMOS technology with integrated leakage reduction for mobile applications. J. Solid State Circuits 2008, 43, 172–179. [Google Scholar] [CrossRef]

- Sinangil, M.E.; Verma, N.; Chandrakasan, A.P. A reconfigurable 65nm SRAM achieving voltage scalability from 0.25 to 1.2 V and performance scalability from 20 kHz to 200 MHz. In Proceedings of the ESSCIRC 2008 34th European Solid-State Circuits Conference, Edinburgh, UK, 15–19 September 2008.

- Kim, D.; Chen, G.; Fojtik, M.; Seok, M.; Blaauw, D.; Sylvester, D. A 1.85fW/bit ultra low leakage 10T SRAM with speed compensation scheme. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 69–72.

- Chang, M.F.; Chen, M.P.; Chen, L.F.; Yang, S.M.; Kuo, Y.J.; Wu, J.J.; Su, H.Y.; Chu, Y.H.; Wu, W.C.; Yang, T.Y.; et al. A Sub-0.3 V Area-Efficient L-Shaped 7T SRAM With Read Bitline Swing Expansion Schemes Based on Boosted Read-Bitline, Asymmetric-VTH Read-Port, and Offset Cell VDD Biasing Techniques. J. Solid State Circuits 2013, 48, 2558–2569. [Google Scholar] [CrossRef]

- Wu, J.J.; Chen, Y.H.; Chang, M.F.; Chou, P.W.; Chen, C.Y.; Liao, H.J.; Chen, M.B.; Chu, Y.H.; Wu, W.C.; Yamauchi, H. A Large σVTH/VDD Tolerant Zigzag 8T SRAM with Area-Efficient Decoupled Differential Sensing and Fast Write-Back Scheme. J. Solid State Circuits 2011, 46, 815–827. [Google Scholar] [CrossRef]

| Tech. | Commercial 130 nm Complementary Metal Oxide Semiconductor (CMOS) |

| Cell | 8T static random access memory (SRAM) cell |

| Size | 1 Kbyte (64 × 128), 16-bit/word |

| Voltage | 350–700 mV |

| Leakage Power | 12.29 nW @ 320 mV (standby) 1.09 nW @ 320 mV (shutdown) |

| E/access | 6.24 pJ/access @ 400 mV |

| Special features |

|

| Nominal-VT Read Port | High-VT Read Port with RWL Boosting | |

|---|---|---|

| Read frequency | 114.7 KHz @ 400 mV | 26.6 KHz @ 400 mV |

| Leakage Power per bit | 3.4 pW @ 320 mV | 1.5 pW @ 320 mV |

| Read Power per accessed bit | 35.4 nW @ 400 mV | 9 nW @ 400 mV |

| Area overhead (normalized) | 1x | 1.05x |

| (nW) | 0% “0” bits | 25% “0” bits | 50% “0” bits | 75% “0” bits | 100% “0” bits |

|---|---|---|---|---|---|

| Read Power @ 350 mV | 41.83 | 46.07 | 50.31 | 54.56 | 58.80 |

| Read Power @ 400 mV | 83.07 | 113.48 | 143.89 | 174.3 | 204.71 |

| Write Power @ 350 mV | 44.74 | 49.99 | 55.24 | 60.49 | 65.74 |

| Write Power @ 400 mV | 123.89 | 156.09 | 188.29 | 220.49 | 252.69 |

| Tech. | VDD | Cell Type | Transistor Type | Array(Kb)/Word Size | Freq. (MHz) | Energy (fJ/bit) | Leakage Power (pW/bit) | |

|---|---|---|---|---|---|---|---|---|

| This work | 130 | 0.32 | 8T | High VT | 8/16 | - | - | 1.5 |

| 0.4 | 0.027 | 390 | 1.7 | |||||

| [4] | 65 | 0.35 | 8T | N/A | 256/128 | 0.03 | 870 | 8.4 |

| [5] | 65 | 0.3 | 9T | Mixed VT | 2/32 | 0.22 | 18.2 | 17.8 |

| 0.4 | 2 | 21.8 | 25.4 | |||||

| [6] | 65 | 0.5 | 14T | High VT | 4/32 | 0.11 | 14 | 0.5 @ 0.22 V |

| [18] | 65 | 0.5 | 6T | Low leakage | 1024/- | 250 | N/A | 5.7 |

| [19] | 65 | 0.4 | 8T | Low power | 64/128 | ~0.06 | 78 | 6.1 @ 0.25 V |

| [20] | 180 | 0.35 | 10T | Mixed VT | 24/32 | 0.053 | N/A | 0.0019 |

| [21] | 65 | 0.26 | 7T | N/A | 32/- | 1.8 | 5600 * | - |

| [22] | 90 | 0.23 | Z8T | N/A | 64/- | 0.5 | 80,000 * | 305 |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yahya, F.B.; Patel, H.N.; Boley, J.; Banerjee, A.; Calhoun, B.H. A Sub-Threshold 8T SRAM Macro with 12.29 nW/KB Standby Power and 6.24 pJ/access for Battery-Less IoT SoCs. J. Low Power Electron. Appl. 2016, 6, 8. https://doi.org/10.3390/jlpea6020008

Yahya FB, Patel HN, Boley J, Banerjee A, Calhoun BH. A Sub-Threshold 8T SRAM Macro with 12.29 nW/KB Standby Power and 6.24 pJ/access for Battery-Less IoT SoCs. Journal of Low Power Electronics and Applications. 2016; 6(2):8. https://doi.org/10.3390/jlpea6020008

Chicago/Turabian StyleYahya, Farah B., Harsh N. Patel, James Boley, Arijit Banerjee, and Benton H. Calhoun. 2016. "A Sub-Threshold 8T SRAM Macro with 12.29 nW/KB Standby Power and 6.24 pJ/access for Battery-Less IoT SoCs" Journal of Low Power Electronics and Applications 6, no. 2: 8. https://doi.org/10.3390/jlpea6020008

APA StyleYahya, F. B., Patel, H. N., Boley, J., Banerjee, A., & Calhoun, B. H. (2016). A Sub-Threshold 8T SRAM Macro with 12.29 nW/KB Standby Power and 6.24 pJ/access for Battery-Less IoT SoCs. Journal of Low Power Electronics and Applications, 6(2), 8. https://doi.org/10.3390/jlpea6020008