Abstract

This paper describes the performance prospect of scaled cross-current tetrode (XCT) CMOS devices and demonstrates the outstanding low-energy aspects of sub-30-nm-long gate XCT-SOI CMOS by analyzing device operations. The energy efficiency improvement of such scaled XCT CMOS circuits (two orders higher) stems from the “source potential floating effect”, which offers the dynamic reduction of effective gate capacitance. It is expected that this feature will be very important in many medical implant applications that demand a long device lifetime without recharging the battery.

1. Introduction

Since the 1990s, various families of fully-depleted SOI MOSFET have been proposed and extensively studied [1,2] due to their various merits in terms of device scaling (high drivability, steep swing, less short-channel effects, smaller foot print, etc.). One of the authors (Omura) proposed the cross-current tetrode SOI MOSFET (XCT-SOI MOSFET) for analog applications (see Figure 1), in 1986, on the basis of partially-depleted SOI MOSFET technology [3], and conducted experiments to evaluate the fundamental aspects of the device. While the scaling feasibility of XCT-like devices has been studied recently [4,5], we expect that XCT-SOI devices will yield new applications, such as medical implants, which demand low-energy operation with high noise margin. In order to discuss those applications in detail, device models have already been proposed to perform circuit simulations [6,7]. However, modeling an XCT-SOI device is not so easy due to the three-dimensionality of its operations [3,5]. Recently, our laboratory group examined the device model proposed in [6], and its usefulness was comprehensively revealed [8]. In addition, a mechanism analysis demonstrated the potential of scaled XCT CMOS devices for extremely-low-energy operation [9].

Figure 1.

XCT-SOI MOSFET (bird’s eye view and equivalent circuit models): (a) Bird’s eye view of XCT-SOI device with parameter definitions and current flow. Broken arrows reveal the current flow; (b) Basic equivalent circuit model of n-XCT-SOI MOSFET [3]; and (c) AC circuit model of n-XCT-SOI MOSFET [9].

This paper considers the dynamic and standby power dissipation characteristics of the sub-30-nm-long gate XCT-SOI MOSFET. We start by analyzing the low-energy operation of XCT-SOI CMOS circuits; the model proposed here strongly suggests that the “source potential floating effect (SPFE)” substantially reduces the operation power consumption. The great advantages of the design methodology are also elucidated. In addition, this study addresses the reality of sub-20-nm-long gate XCT-SOI devices and a scaling scheme to suppress the standby power consumption for future low-energy applications.

2. Device Structure and Assumptions for Modeling

The schematic device structure is shown in Figure 1a. In an n-channel XCT-SOI device, the n-channel SOI MOSFET and p-channel JFET are self-merged and the electron current of nMOSFET is relayed to the hole current of pJFET in series; the broken arrows reveal the current flow by the node connection of the MOSFET source and the JFET source.

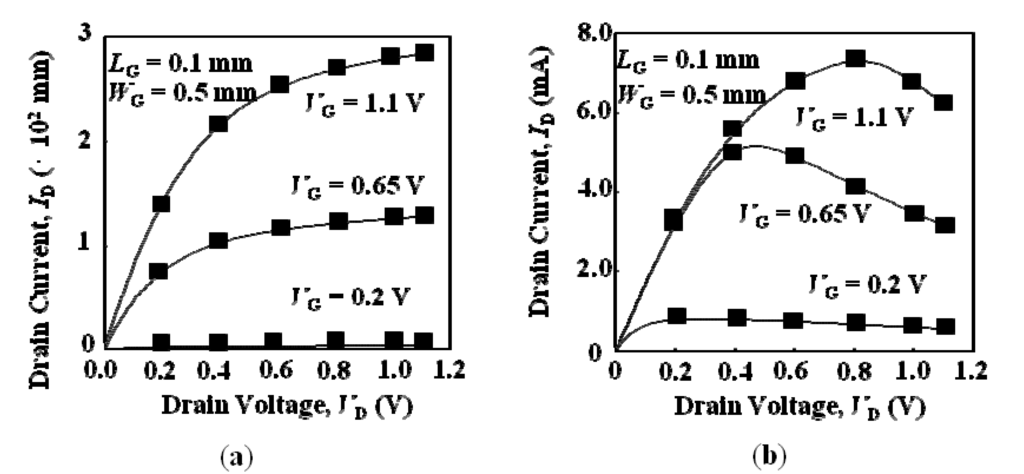

As an example, we show the fundamental ID-VD characteristics of a 0.1-μm-long gate partially-depleted nMOSFET without the parasitic pJFET, see Figure 2a, following 3-D device simulations [10]. Device parameters are summarized in Table 1. As the XCT-SOI device has two active body contacts (B1 and B2) of the SOI MOSFET, the conventional “quasi-static body-floating effect” [1] is eliminated automatically. Details of the device operation are described in a previous paper [8]. The nMOSFET shows slight short-channel effects due to channel length modulation. Figure 2b shows the ID-VD characteristics of an n-channel XCT-SOI MOSFET as determined from 3-D device simulations. It is seen that the XCT-SOI device has lower ID than the MOSFET because of the series resistance of the parasitic pJFET. In addition, the XCT-SOI device shows the negative-differential conductance (NDC) in the saturation region of drain current [3,6,7]. On the other hand, the short-channel effects (SCEs) of the original MOSFET are sufficiently suppressed in the XCT device [8]; subthreshold swing is 76 mV/dec at VD = 1 V. This is one of great advantages of XCT devices.

Figure 2.

Simulated ID-VD characteristics. (a) Original 0.1-μm-gate SOI MOSFET without parasitic JFET; (b) nXCT-SOI MOSFET.

Table 1.

Scaling scheme and device parameters for sub-100-nm-long gate XCT-SOI MOSFET.

| Parameters | NA (cm−3) | LG (nm) | EOT (nm) | tSOI (nm) | tBOX (nm) | VD (V) | VTH (*) (V) |

|---|---|---|---|---|---|---|---|

| Scaling scheme | k4/3 | 1/k | 4/3k | 1/k1/3 | 1/k1/3 | 1/k1/2 | - |

| LG = 100 nm | 2.0 × 1018 | 100 | 2.0 | 129 | 111 | 1.00 | 0.20 |

| LG = 75 nm | 4.0 × 1018 | 75 | 1.5 | 117 | 100 | 0.97 | 0.16 |

| LG = 20 nm | 2.3 × 1019 | 20 | 0.4 | 75 | 65 | 0.50 | −0.06 |

| LG = 15 nm | 3.4 × 1019 | 15 | 0.3 | 69 | 59 | 0.43 | −0.10 |

(*) n+-poly-Si gate is assumed.

In support of XCT-SOI MOSFET modeling, we have already proposed the equivalent circuit (for quasi-static analysis), shown in Figure 1b. The basic feasibility of this model has been examined by circuit simulations [5,7]. In addition, mechanisms of the low-energy operation were examined by a simplified analysis, based on the model shown in Figure 1c [9], where CGn,MOS, CSn,BOX, CDn,BOX and Rch,pJFET denote the gate-to-source capacitance of SOI MOSFET, the source-to-substrate capacitance of SOI MOSFET, the drain-to-substrate capacitance of SOI MOSFET, and the source-to-drain resistance of the parasitic pJFET, respectively. In the case of p-channel XCT-SOI MOSFET, we label them as CGp,MOS, CSp,BOX, CDp,BOX, and Rch,nJFET, respectively.

3. Circuit Simulation Results of SOI CMOS and XCT-SOI CMOS

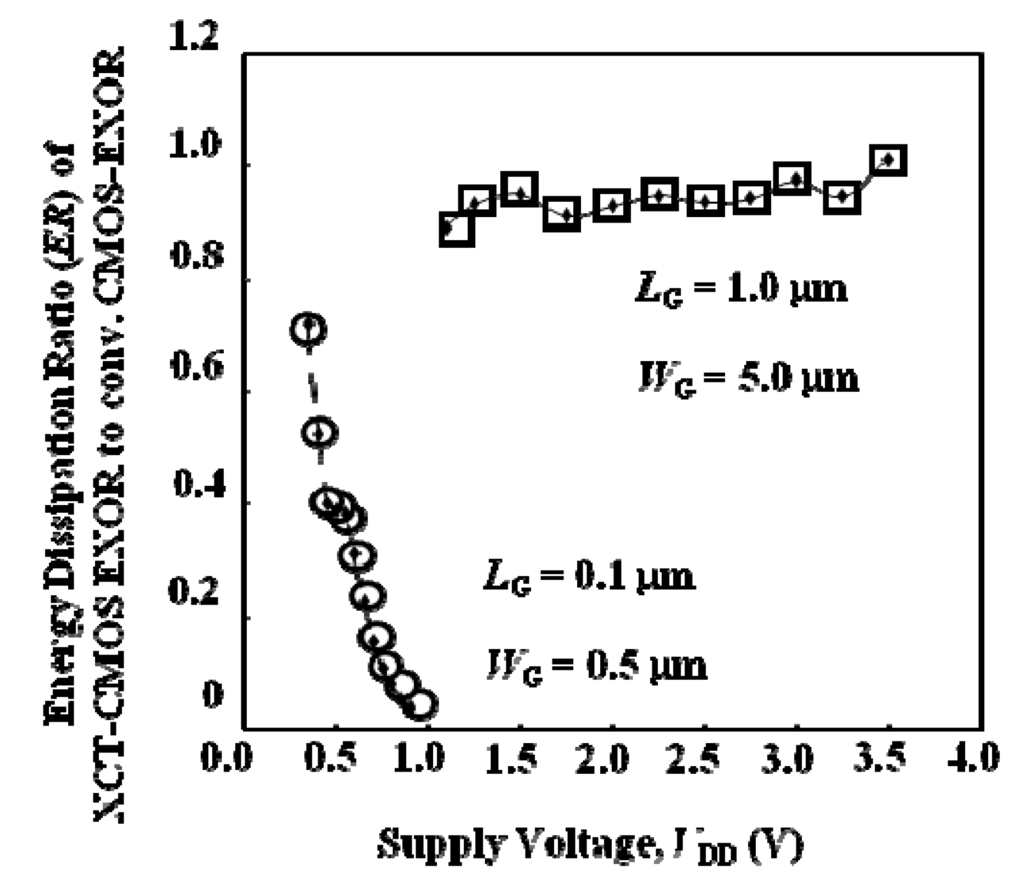

Here, we advance the discussion to better understand XCT-CMOS EXOR circuit features. We assume the OR-NAND type EXOR circuit that consists of four CMOS inverters (standard layout). We concentrate the discussion on the energy ratio of CMOS-EXOR circuits, where energy ratio (ER) is defined as the energy dissipated by the XCT-CMOS EXOR over that of the comparable conventional SOI-CMOS EXOR. Calculation results, based on HSPICE [11] simulation results, are shown in Figure 3.

Figure 3.

Simulation results of energy ratio (ER) of the energy dissipation of 1.0-μm-long gate CMOS EXOR and 100-nm-long gate CMOS EXOR. The energy ratio is defined by the energy dissipated by the XCT-EXOR divided by that of the conventional CMOS EXOR.

First, it is seen that the ER value of 1-μm-long gate devices is almost unity regardless of the VDD value. This behavior is reasonable for the following reasons. The energy dissipation of conventional devices, evaluated by the Pd-td product, is not a function of VDD due to the simple recognition of the MOS gate capacitor’s charging and discharging operations. It is anticipated that the XCT-CMOS, with a 1-μm-long gate, follows this principle. In the case of 0.1-μm-long gate devices, on the other hand, it is seen that the ER value rapidly falls as VDD rises. As this is a very interesting result and somewhat mysterious, we discuss below a possible mechanism based on physics.

Frequency-dependent energy ratio (ER) is defined by [9]:

where CGn,XCT and CGp,XCT denote the effective gate capacitance of n-XCT-SOI MOSFET and p-XCT-SOI MOSFET, respectively. Here, for simplicity, we do not take account of the depletion layer beneath the buried oxide layer. These capacitances are calculated using the equivalent circuit model shown in Figure 1c as:

where CGn,XCT and CGp,XCT denote the effective gate capacitance of n-XCT-SOI MOSFET and p-XCT-SOI MOSFET, respectively. Here, for simplicity, we do not take account of the depletion layer beneath the buried oxide layer. These capacitances are calculated using the equivalent circuit model shown in Figure 1c as:

At the low-frequency limit (ω→0), CGn,XCT and CGp,XCT are reduced to CGn,MOS and CGp,MOS, respectively, as expected. At the high-frequency limit, however, we have:

Generally speaking, reducing the gate length (LG) raises the operation frequency at the same supply voltage. The ER rises when the scaling is enhanced; the scaling scheme assumed here [5,8] slightly reduces CSn,BOXRch,pJFET and CSp,BOXRch,nJFET as the scaling is advanced. For f < 1/(CSn,BOXRch,pJFET) and f < 1/(CSp,BOXRch,nJFET), the roles of CSn,BOX and CSp,BOX are lost; i.e., we have CGn,XCT~ CGn,MOS and CGp,XCT~ CGp,MOS. This is equivalent to the low-frequency limit. As a result, the ER value approaches unity; the intrinsic advantage of the XCT-SOI CMOS is lost. For f > 1/(CSn,BOXRch,pJFET) and f > 1/(CSp,BOXRch,nJFET), on the other hand, we have CGn,XCT < CGn,MOS and CGp,XCT < CGp,MOS. Device operation approaches the high-frequency limit. In this case, the ER value decreases as the frequency rises. The ER value approaches zero as the supply voltage rises, shown in Figure 3. It is anticipated that the depletion layer beneath the buried oxide layer reduces the parasitic capacitance of source diffusion. In order to achieve a small ER value, therefore, we have to increase the effective channel resistance of the parasitic JFET when scaling is advanced.

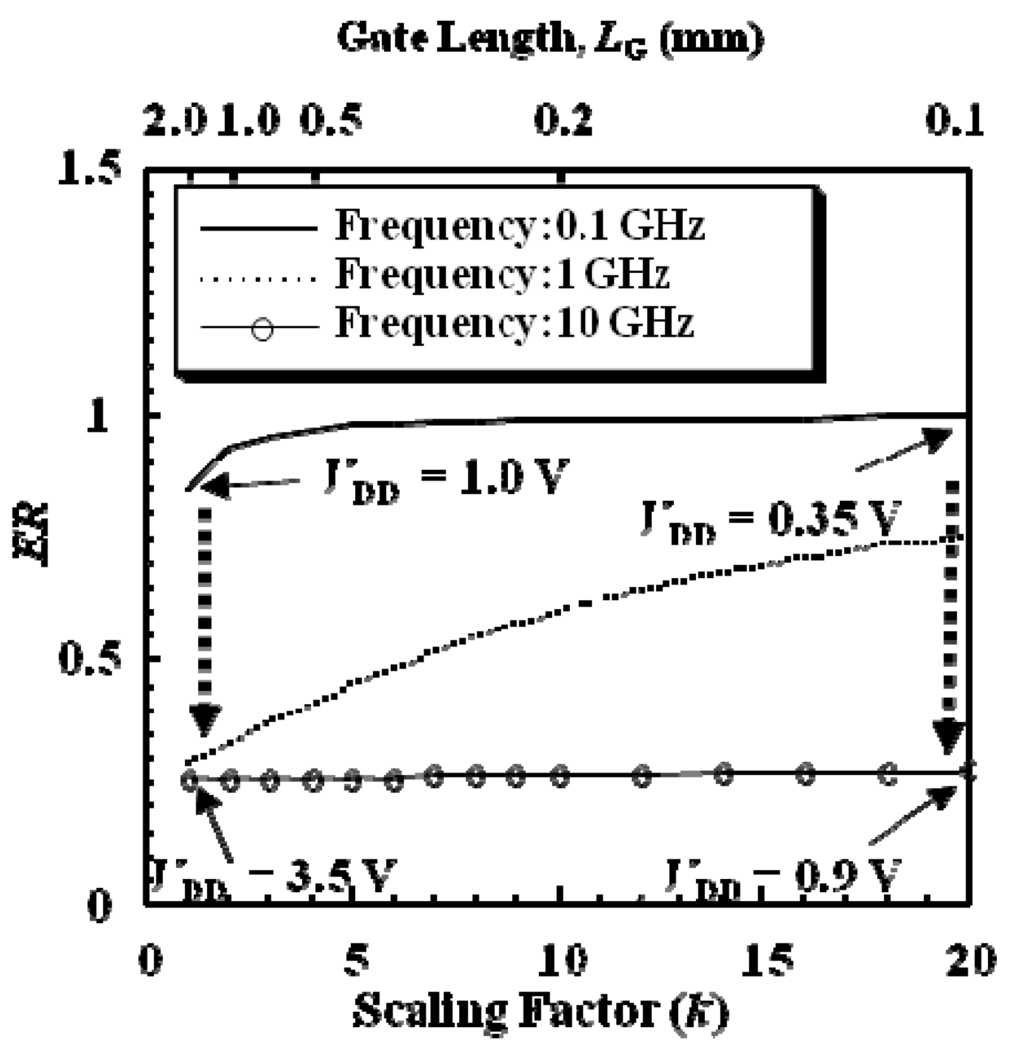

Calculation results of the energy ratio (ER), defined by Equations (1) and (2), are shown in Figure 4. The model clearly predicts that high-frequency drive will drastically reduce XCT-SOI CMOS power consumption. This stems from the “source potential floating effect (SPFE)” obtained by the model shown in Figure 1c. Consequently, we can conclude that the SPFE of the source diffusion of the SOI MOSFET plays an important role in reducing the energy dissipated by XCT-SOI CMOS devices.

Figure 4.

Dissipated energy ratio as a function of the scaling factor. It is assumed that the energy dissipation consists only of the charging and discharging processes of the gate capacitor. Scaling scheme is described in [5]. The dotted arrows reveal the lowest-to-highest range of supply voltage applicable to 1-μm-long gate CMOS (for k = 1) and 0.1-μm-long gate CMOS (k = 20).

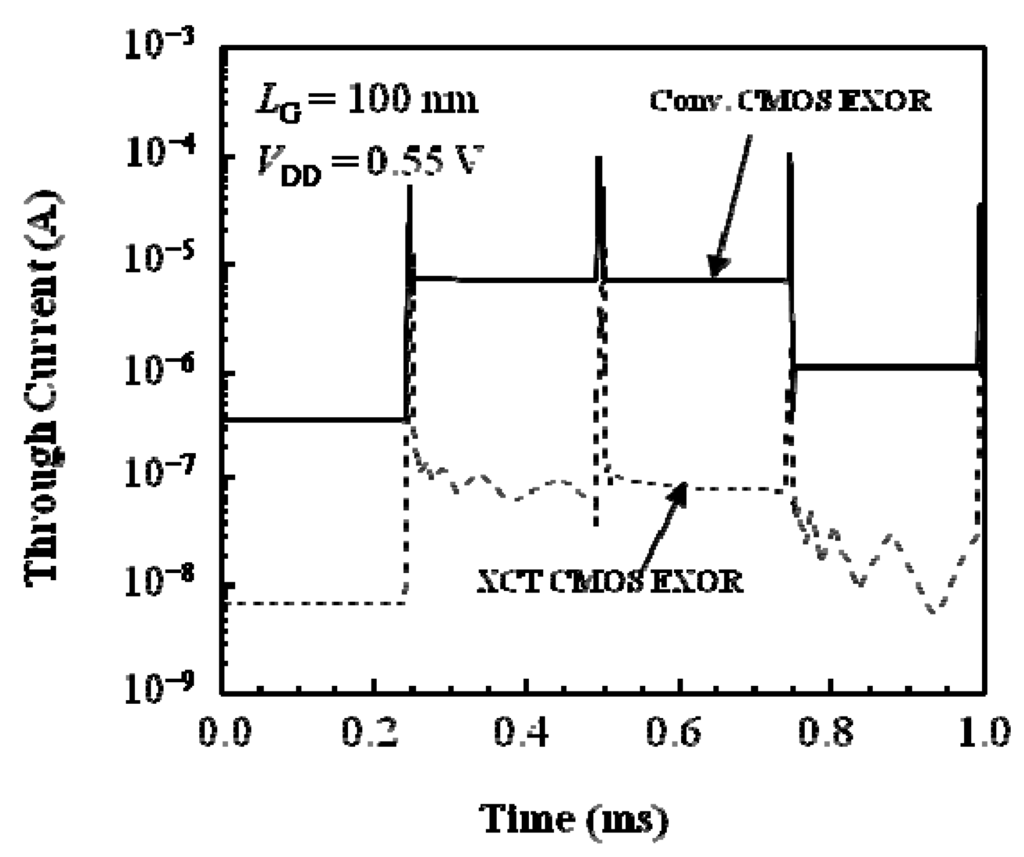

Figure 5 shows simulation results of the time-dependent through-current of the conventional SOI CMOS EXOR chain circuit and the XCT-SOI CMOS EXOR chain circuit, both under dynamic operation. It is seen that the standby power of the XCT-SOI CMOS EXOR chain circuit is about two orders lower than that of the conventional SOI CMOS EXOR chain circuit. This suggests that logic circuits composed of XCT-SOI CMOS can offer drastically lower standby-energy dissipation as well as lower switching-energy dissipation.

Figure 5.

Simulation results of through-current of CMOS EXOR for LG = 100 nm. Arrows show standby power reduction.

4. Further Scaling Potential of XCT-SOI MOSFET

We now investigate the scaling potential of the XCT-SOI CMOS. The fundamental scaling scheme of the XCT-SOI MOSFET has been already studied in [5,8] and a 100-nm-long gate XCT-SOI CMOS has been realized. However, body doping is apt to rise to 1019 cm−3 as the XCT-SOI MOSFET is inherently a partially-depleted SOI device. We investigated how well the XCT-SOI MOSFET can be scaled down to realize a 15-nm-long gate. Using 3D device simulations [10], we simulated the performance of 20-nm-long gate and 15-nm-long gate XCT-SOI MOSFETs under the scaled bias condition, where we assumed abrupt source and drain junctions, for simplicity, in the scaling scheme proposed recently [12]. As the previous scheme [5,8] cannot be applied to the sub-100-nm regime, we restructured the scheme (see Table 1) so that devices work well [12].

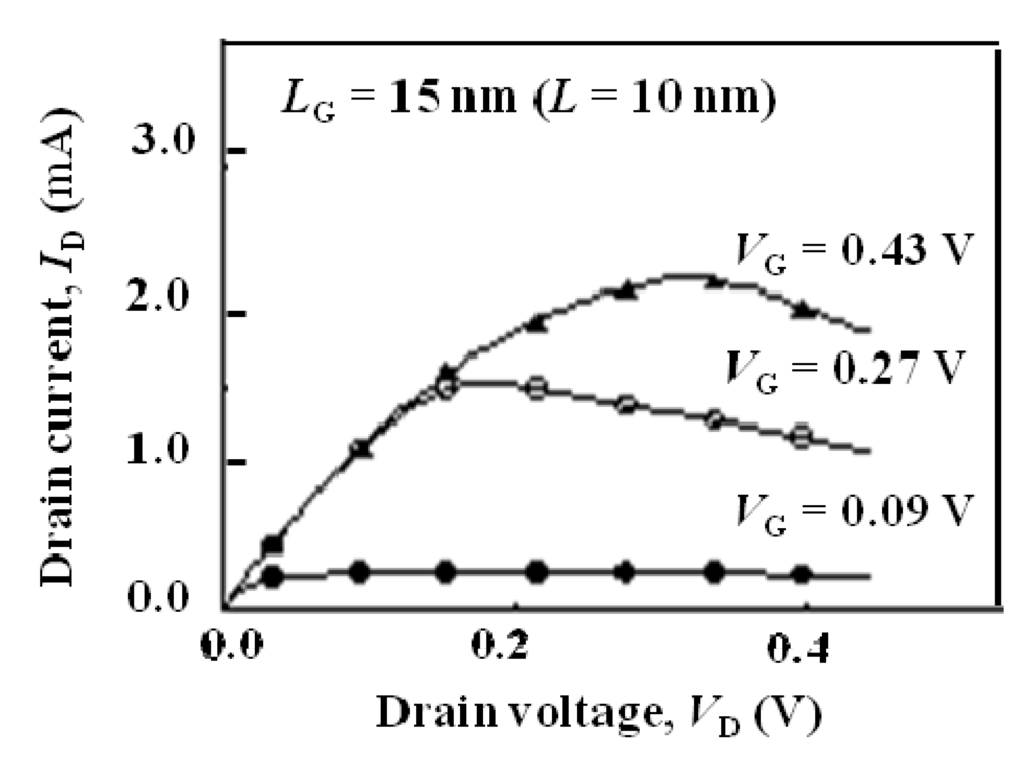

Here, simulated ID-VD characteristics of the 15-nm-long gate XCT-SOI MOSFET, with device parameters, shown in Table 1, shown in Figure 6; the device has the abrupt source and drain junctions. The device shows the negative differential conductance in the saturation region, as is expected.

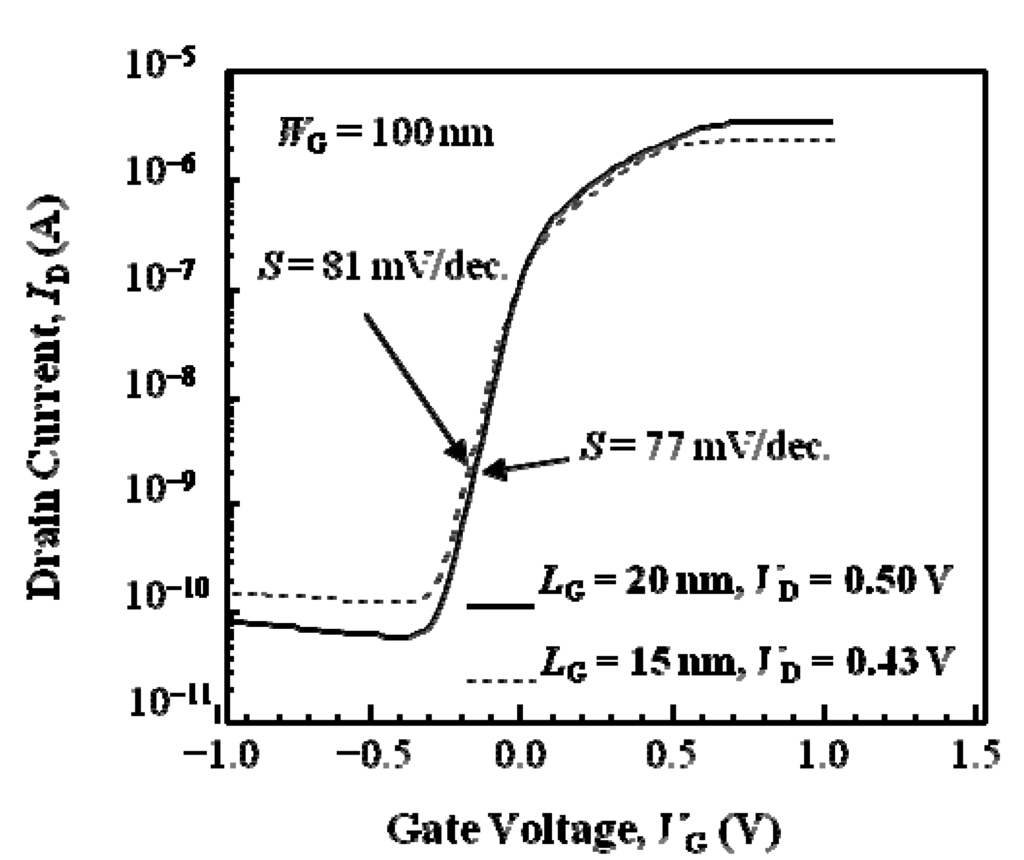

Simulated subthreshold characteristics of the 15-nm-long gate XCT-SOI MOSFET and the 20-nm-long gate XCT-SOIMOSFET are compared in Figure 7; both devices have the abrupt junctions. It is seen in Figure 7 that the subthreshold swing (S) is 77 mV/dec, for the 20-nm-long gate device, and 81 mV/dec, for the 15-nm-long gate device. Short-channel effects are well suppressed. However, the gate-induced drain-leakage (GIDL) current level of the 15-nm-long gate XCT-SOI device is somewhat high (~10−9 A/μm) as the device simulation assumes the abrupt junction for simplicity.

Figure 6.

Simulation results of ID-VD characteristics of 15-nm-long gate XCT-SOI MOSFET. L denotes the effective channel length.

Figure 7.

Simulation results of ID-VG characteristics of 20-nm-long and 15-nm-long gate XCT-SOI MOSFET. It is assumed that the devices have abrupt source and drain junctions.

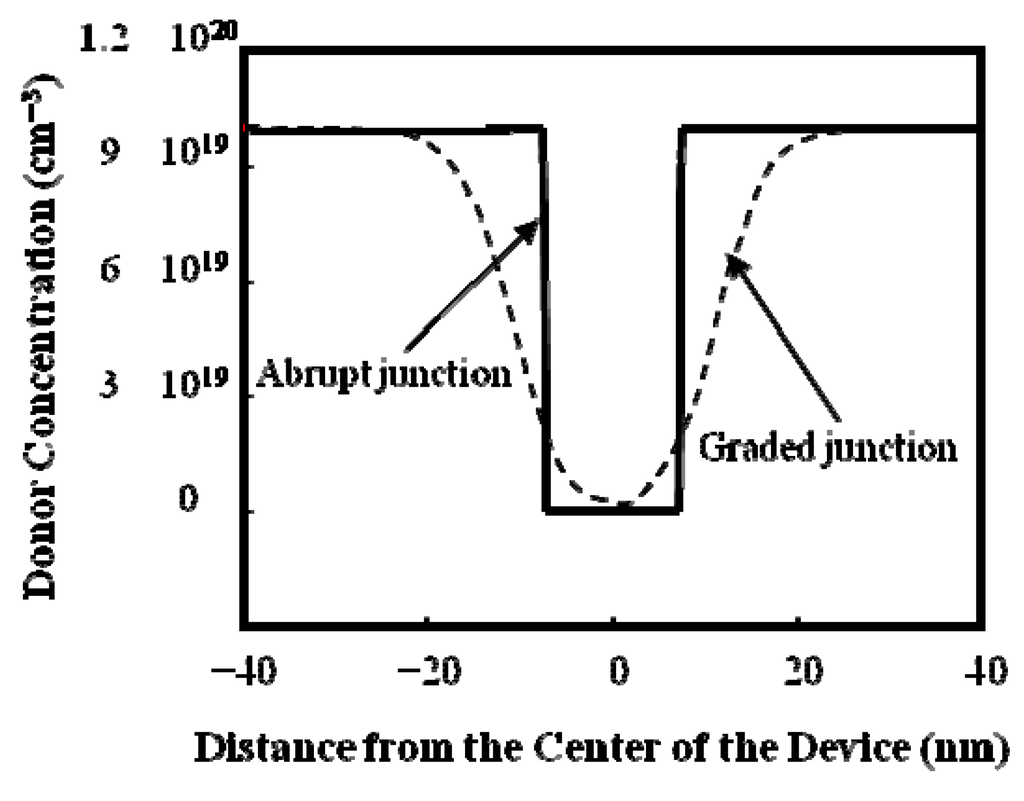

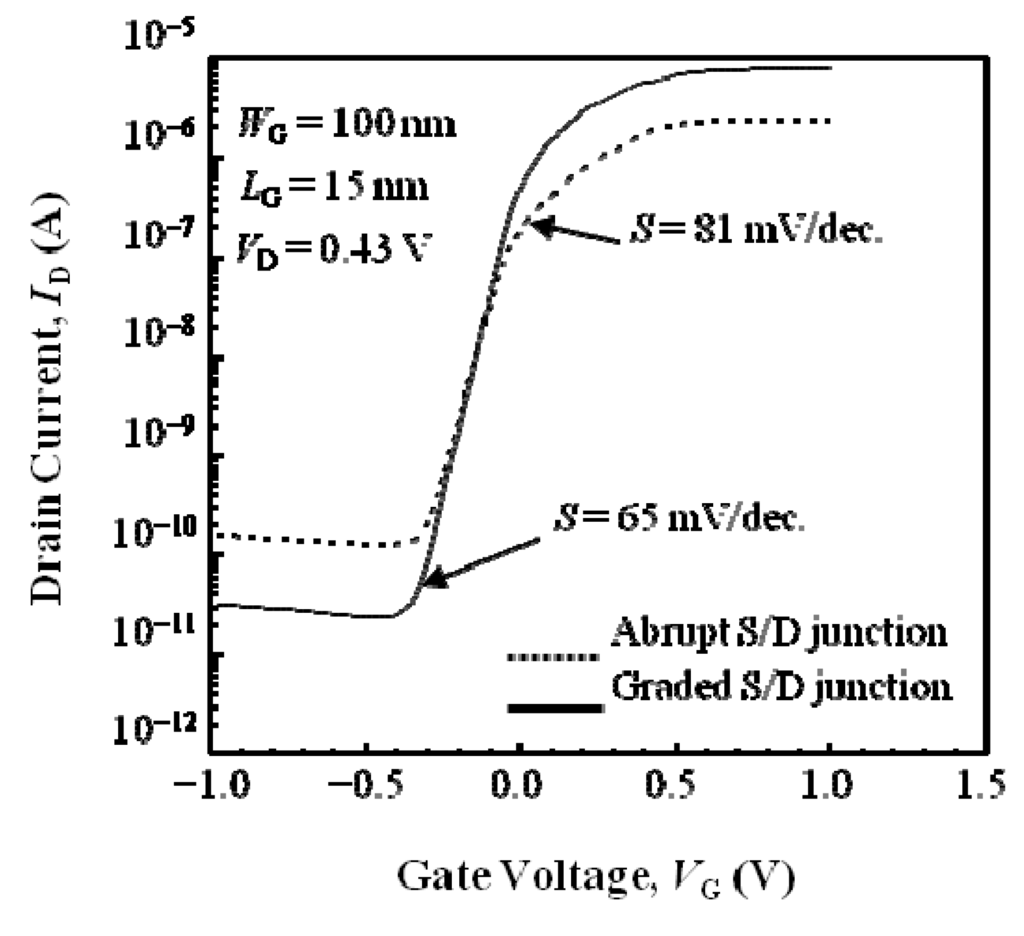

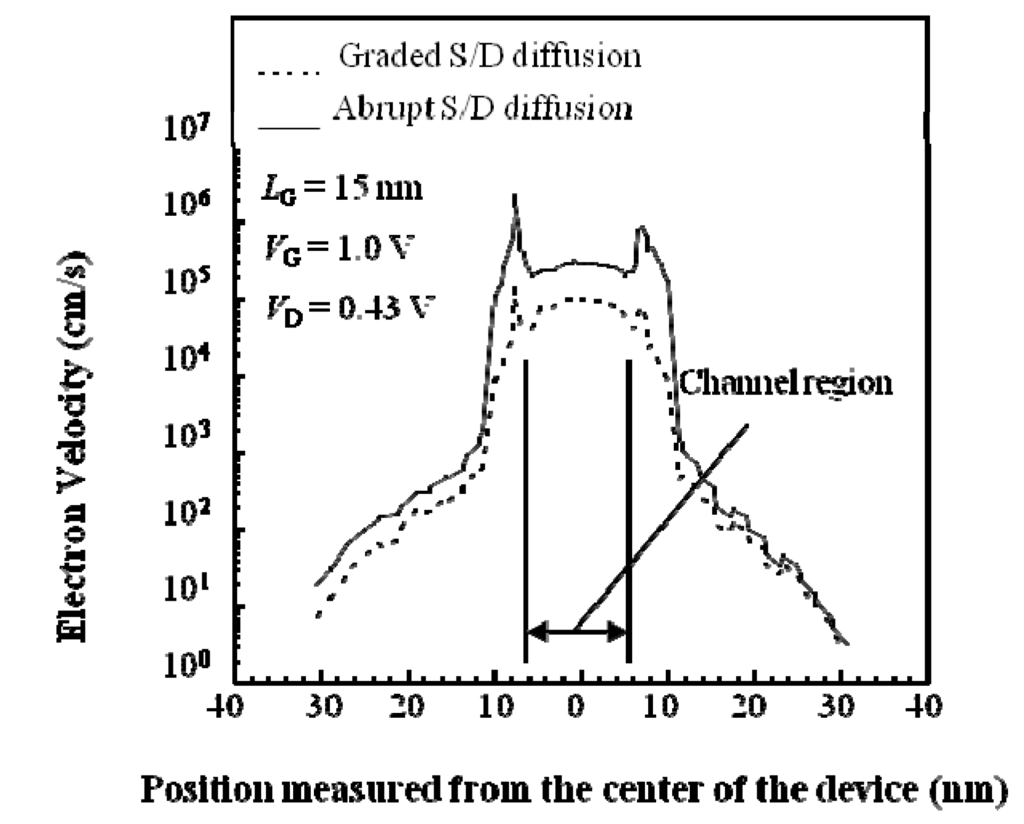

In response, we introduced a 10-nm-long graded doping region for source and drain junctions as a “new” scaling scheme, as shown in Figure 8. Simulated ID-VG characteristics of the 15-nm-long gate XCT-SOI MOSFET are shown in Figure 9. Drain current characteristics of 15-nm-long gate XCT-SOI devices with the abrupt and the graded junctions are compared. It should be noted that the subthreshold swing is 65 mV/dec for the 15-nm-long gate device with the graded junction. Short-channel effects are well suppressed in the 15-nm-long gate XCT-SOI MOSFET. The GIDL current level is lowered to 200 pA/μm. The most noticeable result is the improved drivability of the device with the graded junction; this is due to the remarkable improvement in carrier velocity over the whole device region, as shown in Figure 10 [13], and the reduction of the channel resistance of the parasitic pJFET [12].

Figure 8.

Doping profiles from the source to drain. The doping profile with a graded junction is compared to that with an abrupt junction.

Figure 9.

Simulation results of ID-VG characteristics of 15-nm-long gate XCT-SOI MOSFET. Impact of doping profile on ID-VG characteristics is compared.

Figure 10.

Simulation results of carrier velocity along the channel for the 15-nm-long gate XCT-SOI MOSFET. Impact of doping profile on velocity profile is compared.

5. Performance Expected from the Scaled XCT-SOI MOSFET

This section comprehensively examines the potential of the scaled XCT-SOI MOSFET. Calculated values of the on-current (Ion), the off-current (Ioff), the intrinsic switching time (CGVD/Ion), the switching energy (Esw), and the standby power (Pstby), are summarized in Table 2, where it is assumed that the threshold voltage (VTH) is 0.2 V and WG/LG = 5, regardless of scale. Here, we assume that CG,XCT = CG,MOS; in other words, SPFE is not assumed in Table 2. From Table 2, we can identify the following.

(i) The graded source/drain junction improves the drivability;

(ii) The graded source/drain junction does not always reduce the off-current;

(iii) The intrinsic switching time is degraded as the scaling is advanced if an abrupt junction is assumed. However, it can be drastically improved by using a graded junction due to the improved drivability;

(iv) The switching energy will be further reduced when SPFE is taken into account.

Table 2.

Performance perspectives of scaled XCT-SOI MOSFET.

| LG (nm)/WG (nm) | Ion (A) | Ioff (A) | CGVD/Ion (s)* | Esw (J)* | Pstby (W)* | |

|---|---|---|---|---|---|---|

| 100/500 | 5.4 × 10−6 | 2.5 × 10−9 | 1.7 × 10−10 | 5.1 × 10−16 | 2.8 × 10−9 | |

| 75/375 | 1.0 × 10−5 | 1.3 × 10−9 | 1.6 × 10−11 | 3.0 × 10−16 | 1.3 × 10−9 | |

| 20/100 | abrupt S/D | 1.7 × 10−6 | 7.6 × 10−9 | 4.9 × 10−11 | 2.1 × 10−17 | 3.8 × 10−9 |

| graded S/D | 2.2 × 10−6 | 2.4 × 10−9 | 3.8 × 10−11 | 2.1 × 10−17 | 1.9 × 10−9 | |

| 15/75 | abrupt S/D | 5.2 × 10−7 | 2.1 × 10−10 | 1.4 × 10−10 | 1.2 × 10−17 | 9.0 × 10−11 |

| graded S/D | 4.4 × 10−6 | 1.9 × 10−9 | 1.6 × 10−11 | 1.2 × 10−17 | 8.2 × 10−10 | |

*It is assumed that CG,XCT = CG,MOS.

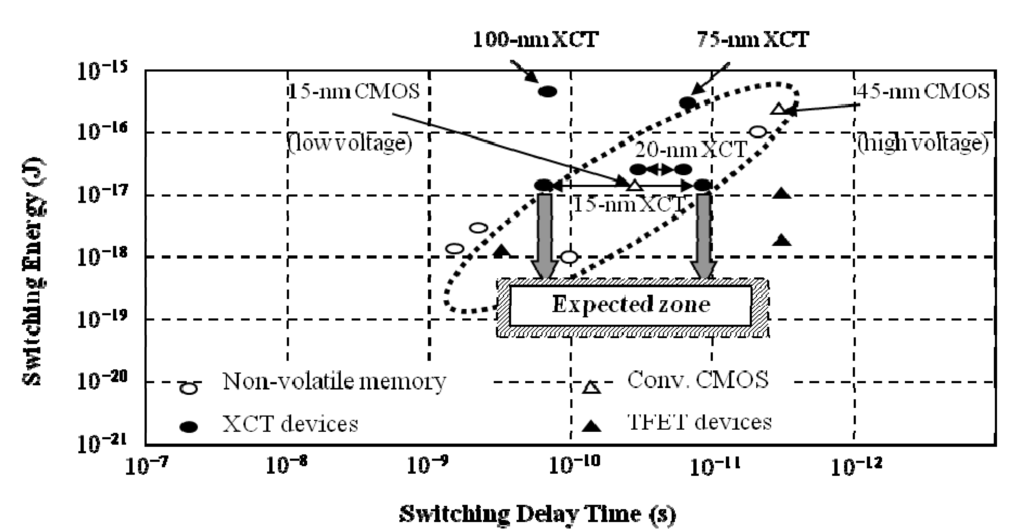

In order to evaluate the above aspects of the scaled XCT-SOI MOSFET, we start by referring to the ITRS roadmap 2011 [14]. Figure 10 shows the projected switching performance suggested by the ITRS roadmap 2011; the calculation results of various XCT-SOI devices are also plotted. Simple calculation results reveal that 15-nm-long gate XCT-SOI devices without SPFE are identical to the non-volatile memory device group. However, it is worthwhile to note that the 15-nm-long gate XCT-SOI device is expected to lie in the zone below the non-volatile memory zone; SPFE should provide XCT-SOI devices with much better performance (“expected zone”) than that shown in Figure 11.

Figure 11.

Comprehensive examination of scaled XCT-SOI MOSFET based on the ITRS roadmap 2011. Expected zone is estimated by assuming the SPFE, based on the model shown in Figure 1c.

6. Conclusions

We demonstrated the low-energy operation of XCT-SOI CMOS devices scaled down to 15 nm and analyzed the key underlying mechanism. It was shown that the source-follower like operation of the XCT-SOI MOSFET dynamically reduces the effective input capacitance, and, thus, the energy dissipated by XCT-SOI devices. This operation should be called the “source potential floating effect (SPFE)”. It is predicted, based on a physics-based model, that realizing SPFE in XCT-CMOS circuits will significantly suppress standby power dissipation.

It was also suggested that such aspects are still available in the sub-30-nm-long gate regime. Therefore, we can state that XCT-SOI CMOS devices are very promising for future extremely-low-energy circuits that suit medical implant applications.

Acknowledgments

A part of this study was supported by “Strategic Project to Support the Formation of Research Bases at Private Universities” in Japan: Matching Fund Subsidy from MEXT (Ministry of Education, Culture, Sports, Science and Technology) in Japan.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Colinge, J.P. Silicon-On-Insulator Technology: Materials to VLSI, 3rd ed.; Kluwer Academic Publishers: Dordrecht, the Netherlands, 2004; pp. 151–277. [Google Scholar]

- FinFETs and Other Multi-Gate Transistors; Colinge, J.P. (Ed.) Springer: New York, NY, USA, 2008; Chapter 1; pp. 4–28.

- Omura, Y.; Izumi, K. High-Gain Cross-Current Tetrode MOSFET/SIMOX and Its Application. In Proceedings of the 18th International Conference of the Solid State Devices and Materials, Tokyo, Japan, 1986; pp. 715–716.

- Blalock, B.J.; Cristoloveanu, S.; Dufrene, B.M.; Allibert, F.; Mojarradi, M. The multiple-gate MOSFET-JFET transistor. Int. J. High Speed Electron. Syst. 2002, 12, 511–520. [Google Scholar]

- Omura, Y.; Fukuchi, K.; Ino, D.; Hayashi, O. Scaling scheme and performance perspective of cross-current tetrode (XCT) SOI MOSFET for future ultra-low power applications. ECS Trans. 2011, 35, 85–90. [Google Scholar]

- Azuma, Y.; Yoshioka, Y.; Omura, Y. Cross-Current SOI MOSFET Model and Important Aspects of CMOS Operations. In Proceedings of the International Conference of the Solid State Devices and Materials, Tsukuba, Japan, 2007; pp. 460–461.

- Omura, Y. Cross-current silicon-on-insulator metal-oxide semiconductor field-effect transistor and application to multiple voltage reference circuits. Jpn. J. Appl. Phys. 2009, 48, 04C07–04C11. [Google Scholar]

- Omura, Y.; Azuma, Y.; Yoshioka, Y.; Fukuchi, K.; Ino, D. Proposal of preliminary device model and scaling scheme of cross-current tetrode silicon-on-insulator metal-oxide-semiconductor field-effect transistor aiming at low-energy circuit applications. Solid-State Electron. 2011, 64, 18–27. [Google Scholar] [CrossRef]

- Omura, Y.; Ino, D. Definite Feature of Low-Energy Operation of Scaled Cross-Current Tetrode (XCTY) SOI CMOS Circuit. In Proceedings of the 17th Workshop on Synthesis and System Integration of Mixed Information Technologies (SASIMI 2012), Beppu, Japan, 2012; pp. 355–360.

- Synopsys Inc. Sentaurus Operations Manual; Synopsys: Mountain View, CA USA, 2008. [Google Scholar]

- Synopsys Inc. HSPICE Users Manual; Synopsys: Mountain View, CA, USA, 2008. [Google Scholar]

- Sato, D.; Omura, Y. Scaling Scheme Prospect of XCT-SOI MOSFET Aiming at Medical Implant Applications Showing Long Lifetime with a Small Battery. In Proceedings of the IEEE International Meeting for Future of Electron Devices, Kansai (IMFEDK), Suita, Japan, 2013; pp. 38–39.

- Omura, Y.; Nakano, S.; Hayashi, O. Gate-field engineering and source/drain diffusion engineering for high-performance Si wire GAA MOSFET and low-power strategy in sub-30-nm-channel regime. IEEE Trans. Nanotechnol. 2011, 10, 715–726. [Google Scholar] [CrossRef]

- ITRS Roadmap. Available online: http://www.itrs.net/Links/2011ITRS/Home2011.htm (accessed on 20 January 2012).

© 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).