Abstract

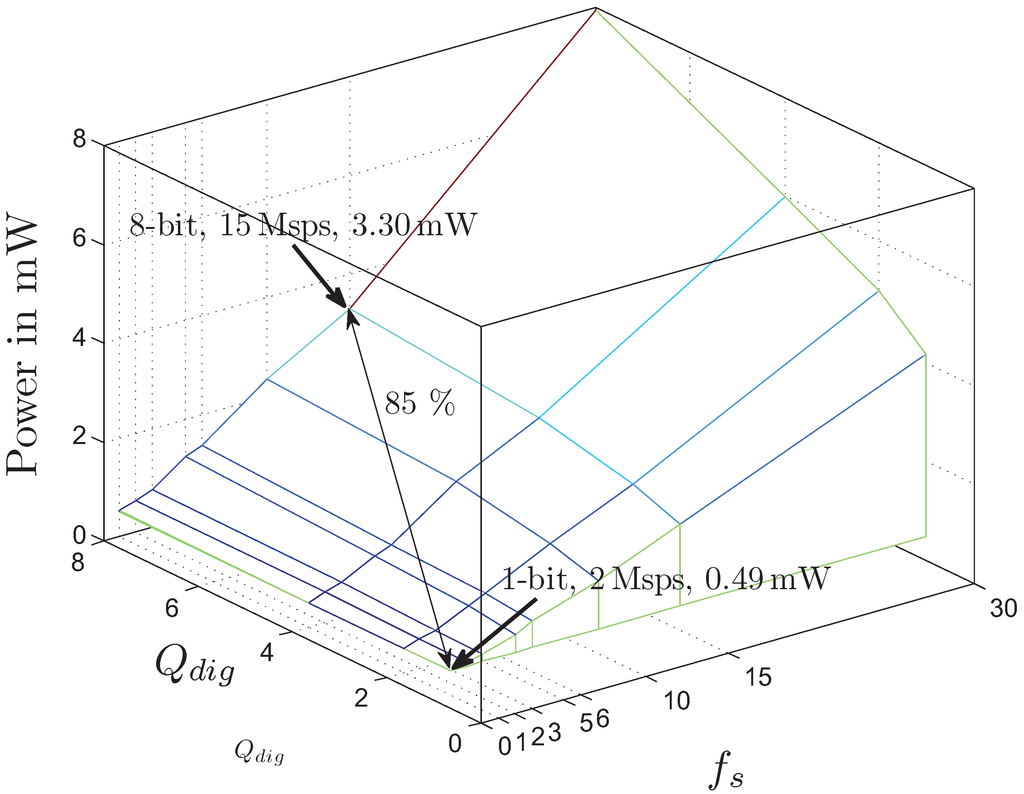

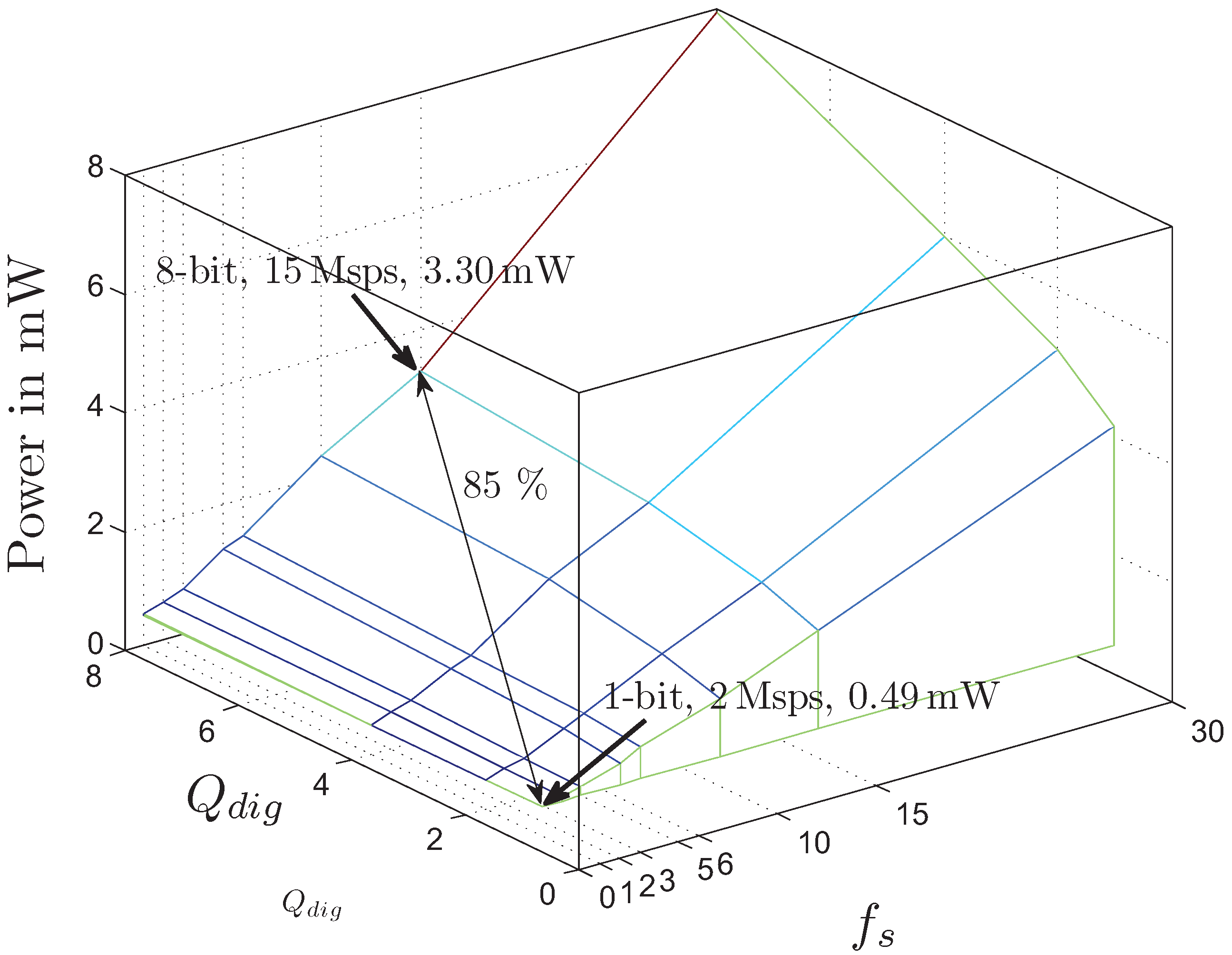

A low power adaptive digital baseband architecture is presented for a low-IF receiver of IEEE 802.15.4-2006. The digital section’s sampling frequency and bit width are used as knobs to reduce the power under favorable signal and interference scenarios, thus recovering the design margins introduced to handle the worst case conditions. We show that in a 0.13 μm CMOS technology, for an adaptive digital baseband section of the receiver, power saving can be up to 85% (0.49 mW against 3.3 mW) in favorable interference and signal conditions. The proposed concepts in the design are tested using a receiver test setup where the design is hosted on a FPGA.

1. Introduction

In this work we propose minimizing power consumption of digital receiver depending on the quality of signal received. The version of IEEE 802.15.4-2006 at  MHz with DSSS physical layer with OQPSK modulation specifies

MHz with DSSS physical layer with OQPSK modulation specifies  dB possible variation in the received signal strength. We take advantage of this large variation by designing a power scalable baseband architecture, which adapts itself to the variation in signal and interference levels. The digital section adapts the word length (

dB possible variation in the received signal strength. We take advantage of this large variation by designing a power scalable baseband architecture, which adapts itself to the variation in signal and interference levels. The digital section adapts the word length (  ) and sampling frequency (

) and sampling frequency (  ). To make the receiver adaptive and low power, various design techniques are proposed in this paper. The key features of this power scalable receiver are interference detector and SNR estimator (IDSE), variable tap and variable coefficient FIR filter, an adaptivity control unit and an adaptation procedure.

). To make the receiver adaptive and low power, various design techniques are proposed in this paper. The key features of this power scalable receiver are interference detector and SNR estimator (IDSE), variable tap and variable coefficient FIR filter, an adaptivity control unit and an adaptation procedure.

MHz with DSSS physical layer with OQPSK modulation specifies

MHz with DSSS physical layer with OQPSK modulation specifies  dB possible variation in the received signal strength. We take advantage of this large variation by designing a power scalable baseband architecture, which adapts itself to the variation in signal and interference levels. The digital section adapts the word length (

dB possible variation in the received signal strength. We take advantage of this large variation by designing a power scalable baseband architecture, which adapts itself to the variation in signal and interference levels. The digital section adapts the word length (  ) and sampling frequency (

) and sampling frequency (  ). To make the receiver adaptive and low power, various design techniques are proposed in this paper. The key features of this power scalable receiver are interference detector and SNR estimator (IDSE), variable tap and variable coefficient FIR filter, an adaptivity control unit and an adaptation procedure.

). To make the receiver adaptive and low power, various design techniques are proposed in this paper. The key features of this power scalable receiver are interference detector and SNR estimator (IDSE), variable tap and variable coefficient FIR filter, an adaptivity control unit and an adaptation procedure.Minimizing power consumption of the receiver has been done by various authors in various ways. Varying  of the receiver to minimize power requires varying number of taps in the FIR filter. Authors in [1] have proposed a variable tap FIR filter based on approximate filtering to reduce power. In doing so, authors have demonstrated power reduction by a factor of 10. Besides varying number of taps to save power, we have used minimum resolution coefficients for FIR filters to save power. Author in [2] controls the resolution of analog-to-digital converter (ADC) in receiver and digital-to-analog converter (DAC) in transmitter. The ADC resolution is controlled depending on signal-to-noise and signal-to-interference ratio and resolution of DAC is controlled based on crest factor of modulation scheme. The author has not suggested any way to measure signal-to-noise and signal-to-interference ratio. Authors in [3] have proposed reconfigurable radio for MIMO wireless systems. Authors have emphasized on optimizing number of operations, latency requirements and the architecture of signal processing elements to minimize complexity of the MIMO signal processing. Number of antennas and modulations levels are reconfigurable in the systems proposed in [3]. Adaptive word length control is used to implement an OFDM based low power wireless baseband processing system [4]. OFDM processing essentially consists of filtering, followed by an FFT engine and then an equalization block. The Error Vector Magnitude (EVM) of the received signal is continuously monitored, to adjust the word length. If EVM is above a threshold, the word length is increased to improve precision and conversely, for good EVM (low error rate), the word length is reduced. Our approach for receiver design incorporates controlling the amplitude quantization and sampling frequency depending on the SNR levels and interference presence. Our approach of scaling power by varying

of the receiver to minimize power requires varying number of taps in the FIR filter. Authors in [1] have proposed a variable tap FIR filter based on approximate filtering to reduce power. In doing so, authors have demonstrated power reduction by a factor of 10. Besides varying number of taps to save power, we have used minimum resolution coefficients for FIR filters to save power. Author in [2] controls the resolution of analog-to-digital converter (ADC) in receiver and digital-to-analog converter (DAC) in transmitter. The ADC resolution is controlled depending on signal-to-noise and signal-to-interference ratio and resolution of DAC is controlled based on crest factor of modulation scheme. The author has not suggested any way to measure signal-to-noise and signal-to-interference ratio. Authors in [3] have proposed reconfigurable radio for MIMO wireless systems. Authors have emphasized on optimizing number of operations, latency requirements and the architecture of signal processing elements to minimize complexity of the MIMO signal processing. Number of antennas and modulations levels are reconfigurable in the systems proposed in [3]. Adaptive word length control is used to implement an OFDM based low power wireless baseband processing system [4]. OFDM processing essentially consists of filtering, followed by an FFT engine and then an equalization block. The Error Vector Magnitude (EVM) of the received signal is continuously monitored, to adjust the word length. If EVM is above a threshold, the word length is increased to improve precision and conversely, for good EVM (low error rate), the word length is reduced. Our approach for receiver design incorporates controlling the amplitude quantization and sampling frequency depending on the SNR levels and interference presence. Our approach of scaling power by varying  and

and  applies the concepts of adaptive signal processing to minimize power. Traditionally, adaptive signal processing is well known for minimizing error of signal processing structures [5], whereas our objective is to minimize power while keeping the error criteria as a constraint in the optimization formulation. An adaptation procedure is proposed to facilitate adaptation in packetized communication.

applies the concepts of adaptive signal processing to minimize power. Traditionally, adaptive signal processing is well known for minimizing error of signal processing structures [5], whereas our objective is to minimize power while keeping the error criteria as a constraint in the optimization formulation. An adaptation procedure is proposed to facilitate adaptation in packetized communication.

of the receiver to minimize power requires varying number of taps in the FIR filter. Authors in [1] have proposed a variable tap FIR filter based on approximate filtering to reduce power. In doing so, authors have demonstrated power reduction by a factor of 10. Besides varying number of taps to save power, we have used minimum resolution coefficients for FIR filters to save power. Author in [2] controls the resolution of analog-to-digital converter (ADC) in receiver and digital-to-analog converter (DAC) in transmitter. The ADC resolution is controlled depending on signal-to-noise and signal-to-interference ratio and resolution of DAC is controlled based on crest factor of modulation scheme. The author has not suggested any way to measure signal-to-noise and signal-to-interference ratio. Authors in [3] have proposed reconfigurable radio for MIMO wireless systems. Authors have emphasized on optimizing number of operations, latency requirements and the architecture of signal processing elements to minimize complexity of the MIMO signal processing. Number of antennas and modulations levels are reconfigurable in the systems proposed in [3]. Adaptive word length control is used to implement an OFDM based low power wireless baseband processing system [4]. OFDM processing essentially consists of filtering, followed by an FFT engine and then an equalization block. The Error Vector Magnitude (EVM) of the received signal is continuously monitored, to adjust the word length. If EVM is above a threshold, the word length is increased to improve precision and conversely, for good EVM (low error rate), the word length is reduced. Our approach for receiver design incorporates controlling the amplitude quantization and sampling frequency depending on the SNR levels and interference presence. Our approach of scaling power by varying

of the receiver to minimize power requires varying number of taps in the FIR filter. Authors in [1] have proposed a variable tap FIR filter based on approximate filtering to reduce power. In doing so, authors have demonstrated power reduction by a factor of 10. Besides varying number of taps to save power, we have used minimum resolution coefficients for FIR filters to save power. Author in [2] controls the resolution of analog-to-digital converter (ADC) in receiver and digital-to-analog converter (DAC) in transmitter. The ADC resolution is controlled depending on signal-to-noise and signal-to-interference ratio and resolution of DAC is controlled based on crest factor of modulation scheme. The author has not suggested any way to measure signal-to-noise and signal-to-interference ratio. Authors in [3] have proposed reconfigurable radio for MIMO wireless systems. Authors have emphasized on optimizing number of operations, latency requirements and the architecture of signal processing elements to minimize complexity of the MIMO signal processing. Number of antennas and modulations levels are reconfigurable in the systems proposed in [3]. Adaptive word length control is used to implement an OFDM based low power wireless baseband processing system [4]. OFDM processing essentially consists of filtering, followed by an FFT engine and then an equalization block. The Error Vector Magnitude (EVM) of the received signal is continuously monitored, to adjust the word length. If EVM is above a threshold, the word length is increased to improve precision and conversely, for good EVM (low error rate), the word length is reduced. Our approach for receiver design incorporates controlling the amplitude quantization and sampling frequency depending on the SNR levels and interference presence. Our approach of scaling power by varying  and

and  applies the concepts of adaptive signal processing to minimize power. Traditionally, adaptive signal processing is well known for minimizing error of signal processing structures [5], whereas our objective is to minimize power while keeping the error criteria as a constraint in the optimization formulation. An adaptation procedure is proposed to facilitate adaptation in packetized communication.

applies the concepts of adaptive signal processing to minimize power. Traditionally, adaptive signal processing is well known for minimizing error of signal processing structures [5], whereas our objective is to minimize power while keeping the error criteria as a constraint in the optimization formulation. An adaptation procedure is proposed to facilitate adaptation in packetized communication.Now let us look at power consumption numbers in present day communication receivers on CMOS technologies. In [6] authors have reported IEEE 802.15.4 receiver (CC2420 chip) consuming  mA when active with

mA when active with  V power supply. Low power analog front end design for IEEE 802.15.4 has been proposed in a few papers [7,8] . In [7], authors proposed a front end design in

V power supply. Low power analog front end design for IEEE 802.15.4 has been proposed in a few papers [7,8] . In [7], authors proposed a front end design in

CMOS technology that consumes

CMOS technology that consumes  mW, whereas in a more recent paper the authors in [8] proposed a front end in 90 nm technology that consumes

mW, whereas in a more recent paper the authors in [8] proposed a front end in 90 nm technology that consumes  mW when active. Authors in [9] have discussed power consumption of various wireless technology for WPAN applications. As mentioned, authors in [9] say that the power consumption of wireless devices scales with the data rate. Typically, IEEE 802.15.4 receiver consumes

mW when active. Authors in [9] have discussed power consumption of various wireless technology for WPAN applications. As mentioned, authors in [9] say that the power consumption of wireless devices scales with the data rate. Typically, IEEE 802.15.4 receiver consumes  mA for

mA for  Mbps,

Mbps,  mA for Bluetooth at

mA for Bluetooth at  Mbps,

Mbps,  mA for WLAN at

mA for WLAN at  Mbps. Power consumptions in analog and digital portion separately have been reported in some papers. Authors in [10] have reported that baseband of IEEE 802.15.4 consumes

Mbps. Power consumptions in analog and digital portion separately have been reported in some papers. Authors in [10] have reported that baseband of IEEE 802.15.4 consumes  mA at

mA at  V supply (

V supply (  mW) in

mW) in

m technology whereas the analog portion consumes

m technology whereas the analog portion consumes  mA. The authors in [9] have given break up of analog and digital portion of the receiver for UWB. Here analog portion consumes

mA. The authors in [9] have given break up of analog and digital portion of the receiver for UWB. Here analog portion consumes  mA compared with

mA compared with  mA of digital at

mA of digital at  MHz.

MHz.

mA when active with

mA when active with  V power supply. Low power analog front end design for IEEE 802.15.4 has been proposed in a few papers [7,8] . In [7], authors proposed a front end design in

V power supply. Low power analog front end design for IEEE 802.15.4 has been proposed in a few papers [7,8] . In [7], authors proposed a front end design in

CMOS technology that consumes

CMOS technology that consumes  mW, whereas in a more recent paper the authors in [8] proposed a front end in 90 nm technology that consumes

mW, whereas in a more recent paper the authors in [8] proposed a front end in 90 nm technology that consumes  mW when active. Authors in [9] have discussed power consumption of various wireless technology for WPAN applications. As mentioned, authors in [9] say that the power consumption of wireless devices scales with the data rate. Typically, IEEE 802.15.4 receiver consumes

mW when active. Authors in [9] have discussed power consumption of various wireless technology for WPAN applications. As mentioned, authors in [9] say that the power consumption of wireless devices scales with the data rate. Typically, IEEE 802.15.4 receiver consumes  mA for

mA for  Mbps,

Mbps,  mA for Bluetooth at

mA for Bluetooth at  Mbps,

Mbps,  mA for WLAN at

mA for WLAN at  Mbps. Power consumptions in analog and digital portion separately have been reported in some papers. Authors in [10] have reported that baseband of IEEE 802.15.4 consumes

Mbps. Power consumptions in analog and digital portion separately have been reported in some papers. Authors in [10] have reported that baseband of IEEE 802.15.4 consumes  mA at

mA at  V supply (

V supply (  mW) in

mW) in

m technology whereas the analog portion consumes

m technology whereas the analog portion consumes  mA. The authors in [9] have given break up of analog and digital portion of the receiver for UWB. Here analog portion consumes

mA. The authors in [9] have given break up of analog and digital portion of the receiver for UWB. Here analog portion consumes  mA compared with

mA compared with  mA of digital at

mA of digital at  MHz.

MHz.We start the next section by formulating an optimization problem for minimizing power while varying  and

and  for the digital baseband. Following this we explain our approach to minimize power based on this optimization. Section 3 explains the simulation and interference model used in subsequent sections. Section 4 discusses various blocks of the receiver, which are designed to accommodate variable

for the digital baseband. Following this we explain our approach to minimize power based on this optimization. Section 3 explains the simulation and interference model used in subsequent sections. Section 4 discusses various blocks of the receiver, which are designed to accommodate variable  and

and  and to be compatible with adaptation procedure. Section 5 discusses the implementation specific details and dynamic power estimation of the design. Section 6 discusses experimental setup and results from the experimental setup to validate the concepts. Section 7 concludes the paper.

and to be compatible with adaptation procedure. Section 5 discusses the implementation specific details and dynamic power estimation of the design. Section 6 discusses experimental setup and results from the experimental setup to validate the concepts. Section 7 concludes the paper.

and

and  for the digital baseband. Following this we explain our approach to minimize power based on this optimization. Section 3 explains the simulation and interference model used in subsequent sections. Section 4 discusses various blocks of the receiver, which are designed to accommodate variable

for the digital baseband. Following this we explain our approach to minimize power based on this optimization. Section 3 explains the simulation and interference model used in subsequent sections. Section 4 discusses various blocks of the receiver, which are designed to accommodate variable  and

and  and to be compatible with adaptation procedure. Section 5 discusses the implementation specific details and dynamic power estimation of the design. Section 6 discusses experimental setup and results from the experimental setup to validate the concepts. Section 7 concludes the paper.

and to be compatible with adaptation procedure. Section 5 discusses the implementation specific details and dynamic power estimation of the design. Section 6 discusses experimental setup and results from the experimental setup to validate the concepts. Section 7 concludes the paper.2. Power Scalable Digital Baseband

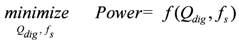

2.1. Optimizing Power

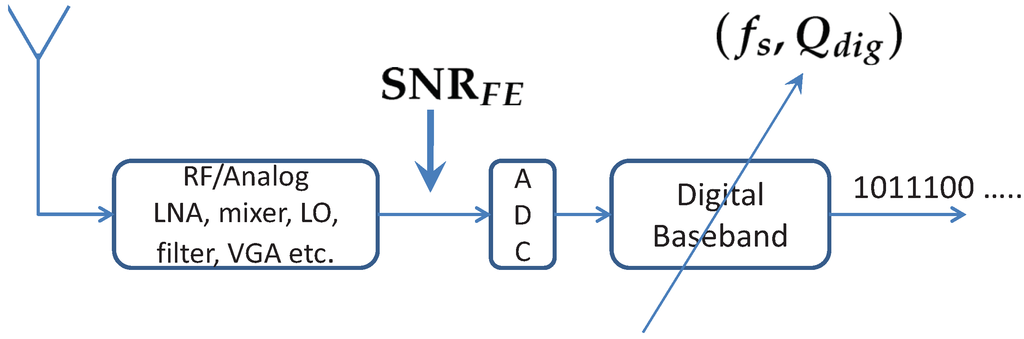

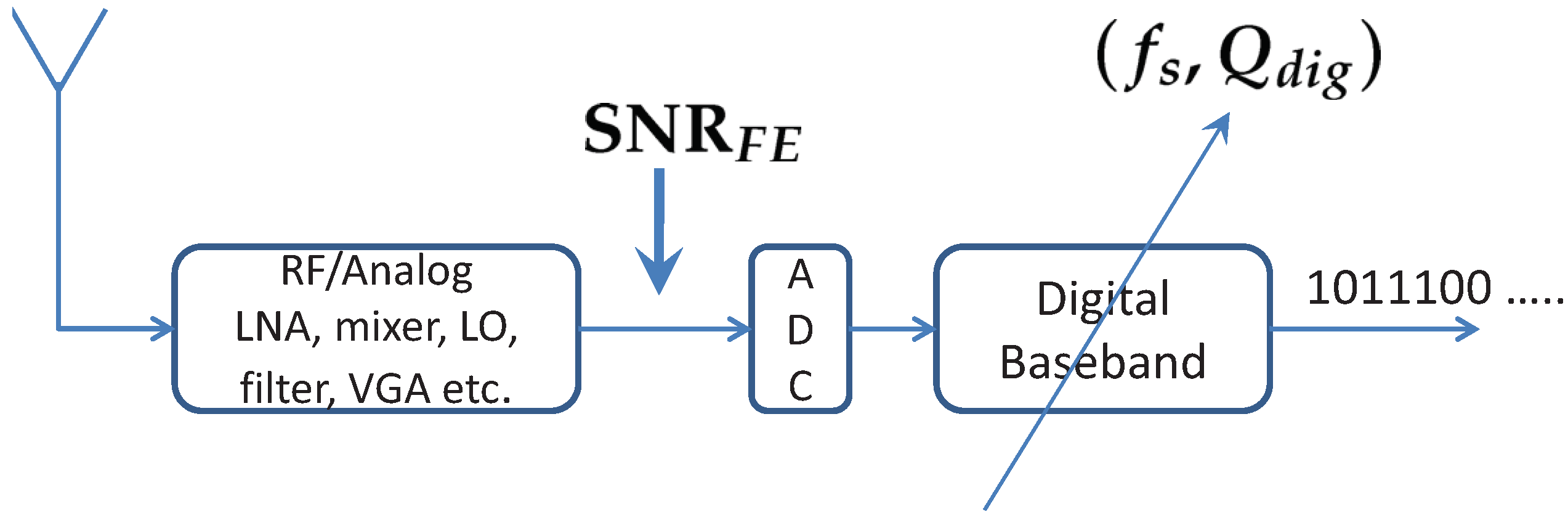

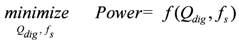

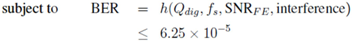

Figure 1.

Cartoon of a typical receiver with variable  and

and  of the digital section.

of the digital section.

and

and  of the digital section.

of the digital section.

Figure 1.

Cartoon of a typical receiver with variable  and

and  of the digital section.

of the digital section.

and

and  of the digital section.

of the digital section.

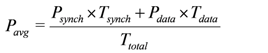

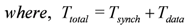

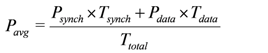

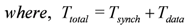

Figure 1 shows a typical receiver.  is the SNR seen at the input of the ADC. It is the ratio of total signal power to the total noise power. It should not be confused with Eb/No typically used in communication theory literature. Input of the ADC, consists of the signal and the noise. We have assumed a 2nd order Butterworth bandpass filter preceding the ADC. The noise present at the input of ADC also has out of desired signal band components. This makes

is the SNR seen at the input of the ADC. It is the ratio of total signal power to the total noise power. It should not be confused with Eb/No typically used in communication theory literature. Input of the ADC, consists of the signal and the noise. We have assumed a 2nd order Butterworth bandpass filter preceding the ADC. The noise present at the input of ADC also has out of desired signal band components. This makes  negative when noise is high. The packet error rate (PER) requirement translates to BER of

negative when noise is high. The packet error rate (PER) requirement translates to BER of  [11].

[11].  and

and  are chosen to minimize power while achieving target BER. More formally:

are chosen to minimize power while achieving target BER. More formally:

BER is independent of

BER is independent of  and

and  , if these parameters are chosen very high. In such a case the implementation of digital portion does not alter the SNR calculation of the receiver, i.e., SNR seen at the input of the ADC is almost the same as SNR seen at the input of the demodulator. But in doing so the digital portion is over-designed and hence wastes power. In order to achieve a given BER, there can be different combinations of

, if these parameters are chosen very high. In such a case the implementation of digital portion does not alter the SNR calculation of the receiver, i.e., SNR seen at the input of the ADC is almost the same as SNR seen at the input of the demodulator. But in doing so the digital portion is over-designed and hence wastes power. In order to achieve a given BER, there can be different combinations of  and

and  for a given

for a given  and interference levels, each with its own power cost. Values of

and interference levels, each with its own power cost. Values of  and

and  that minimize power as given in Equation (1) will be used. Furthermore, with varying values of

that minimize power as given in Equation (1) will be used. Furthermore, with varying values of  and interference, the optimal choices for

and interference, the optimal choices for  and

and  can vary, necessitating an adaptive resolution based digital section. For different levels of

can vary, necessitating an adaptive resolution based digital section. For different levels of  and interference, the optimal design parameters (

and interference, the optimal design parameters (  ) will be stored in the LUT and used to configure the receiver. Finding a closed form expression for the function “

) will be stored in the LUT and used to configure the receiver. Finding a closed form expression for the function “  ” in Equation (2) is hard due to the non-linear relationships. Coarser the ADC quantization

” in Equation (2) is hard due to the non-linear relationships. Coarser the ADC quantization  , harder it becomes to analyze the signal. Hence BER is found through MATLAB simulations, for different (

, harder it becomes to analyze the signal. Hence BER is found through MATLAB simulations, for different (  ) values. The power function in Equation (1) is obtained by Synopsys Prime Power for different

) values. The power function in Equation (1) is obtained by Synopsys Prime Power for different  and

and  values. Finally, the optimum

values. Finally, the optimum  and

and  values are obtained by a simple search over design space.

values are obtained by a simple search over design space.

is the SNR seen at the input of the ADC. It is the ratio of total signal power to the total noise power. It should not be confused with Eb/No typically used in communication theory literature. Input of the ADC, consists of the signal and the noise. We have assumed a 2nd order Butterworth bandpass filter preceding the ADC. The noise present at the input of ADC also has out of desired signal band components. This makes

is the SNR seen at the input of the ADC. It is the ratio of total signal power to the total noise power. It should not be confused with Eb/No typically used in communication theory literature. Input of the ADC, consists of the signal and the noise. We have assumed a 2nd order Butterworth bandpass filter preceding the ADC. The noise present at the input of ADC also has out of desired signal band components. This makes  negative when noise is high. The packet error rate (PER) requirement translates to BER of

negative when noise is high. The packet error rate (PER) requirement translates to BER of  [11].

[11].  and

and  are chosen to minimize power while achieving target BER. More formally:

are chosen to minimize power while achieving target BER. More formally:

and

and  , if these parameters are chosen very high. In such a case the implementation of digital portion does not alter the SNR calculation of the receiver, i.e., SNR seen at the input of the ADC is almost the same as SNR seen at the input of the demodulator. But in doing so the digital portion is over-designed and hence wastes power. In order to achieve a given BER, there can be different combinations of

, if these parameters are chosen very high. In such a case the implementation of digital portion does not alter the SNR calculation of the receiver, i.e., SNR seen at the input of the ADC is almost the same as SNR seen at the input of the demodulator. But in doing so the digital portion is over-designed and hence wastes power. In order to achieve a given BER, there can be different combinations of  and

and  for a given

for a given  and interference levels, each with its own power cost. Values of

and interference levels, each with its own power cost. Values of  and

and  that minimize power as given in Equation (1) will be used. Furthermore, with varying values of

that minimize power as given in Equation (1) will be used. Furthermore, with varying values of  and interference, the optimal choices for

and interference, the optimal choices for  and

and  can vary, necessitating an adaptive resolution based digital section. For different levels of

can vary, necessitating an adaptive resolution based digital section. For different levels of  and interference, the optimal design parameters (

and interference, the optimal design parameters (  ) will be stored in the LUT and used to configure the receiver. Finding a closed form expression for the function “

) will be stored in the LUT and used to configure the receiver. Finding a closed form expression for the function “  ” in Equation (2) is hard due to the non-linear relationships. Coarser the ADC quantization

” in Equation (2) is hard due to the non-linear relationships. Coarser the ADC quantization  , harder it becomes to analyze the signal. Hence BER is found through MATLAB simulations, for different (

, harder it becomes to analyze the signal. Hence BER is found through MATLAB simulations, for different (  ) values. The power function in Equation (1) is obtained by Synopsys Prime Power for different

) values. The power function in Equation (1) is obtained by Synopsys Prime Power for different  and

and  values. Finally, the optimum

values. Finally, the optimum  and

and  values are obtained by a simple search over design space.

values are obtained by a simple search over design space.2.2. Proposed Architecture and Functioning

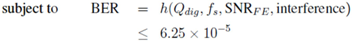

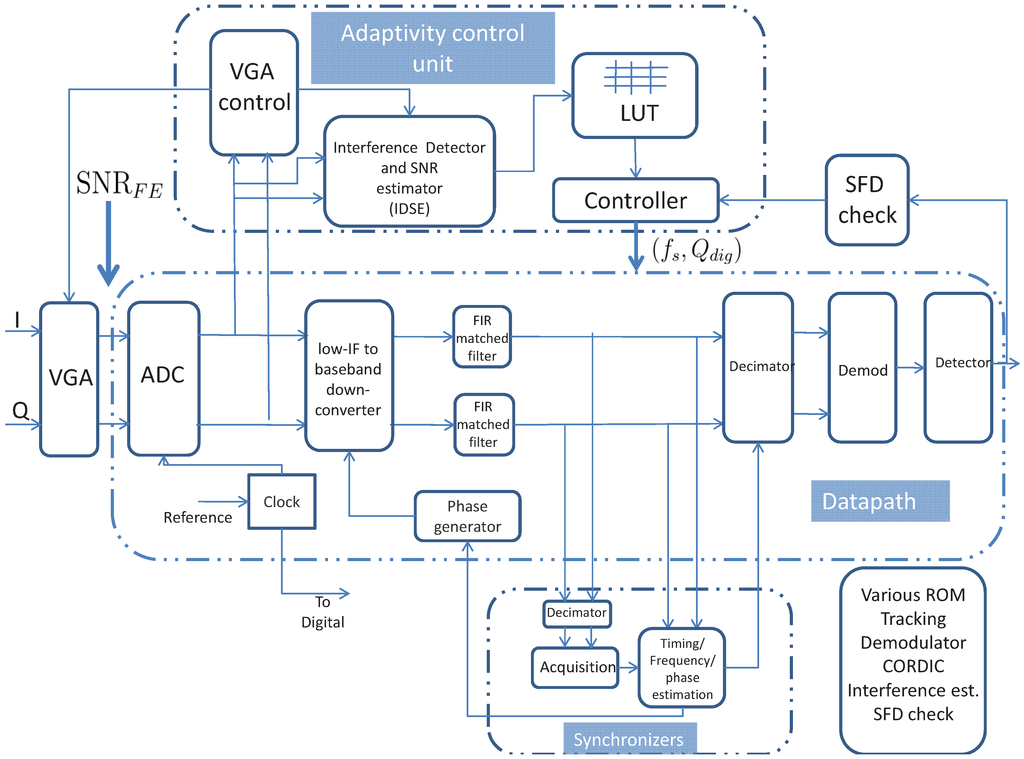

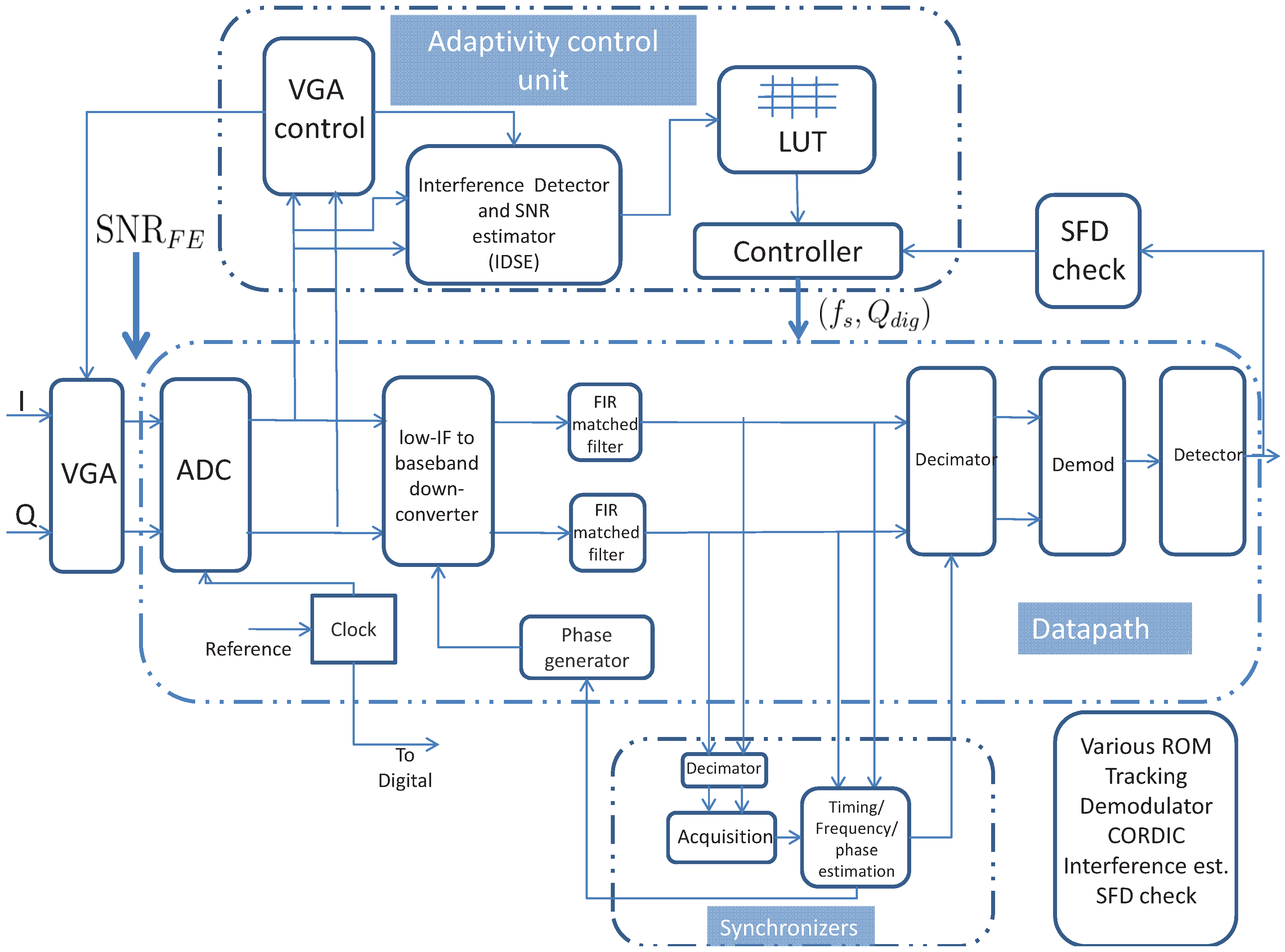

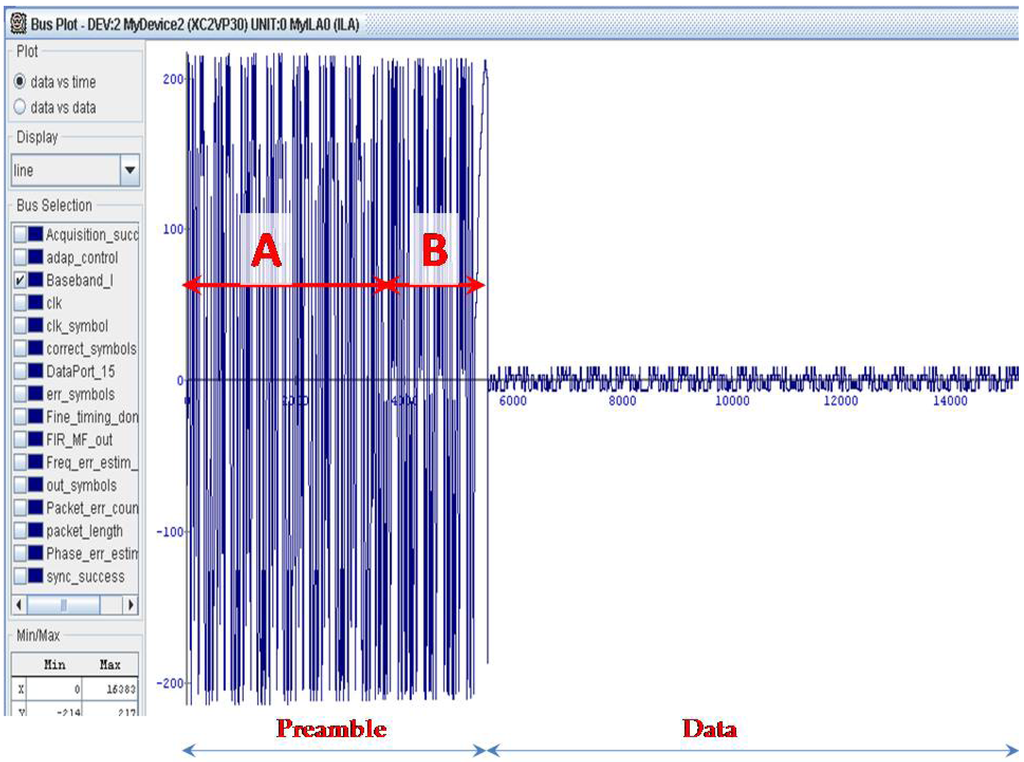

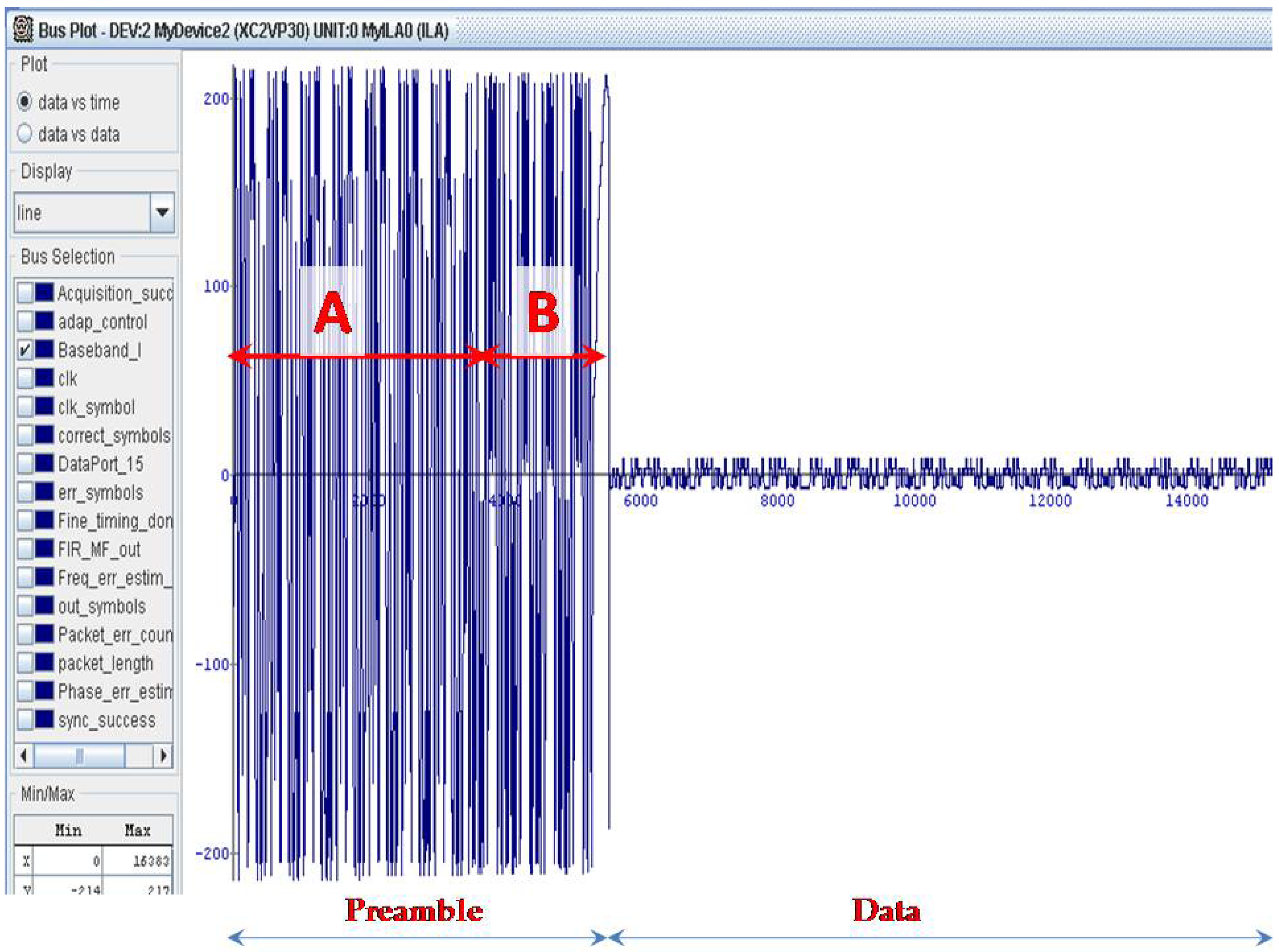

Figure 2 shows the architecture of the power scalable receiver. It includes synchronization units (acquisition, tracking, phase error estimator, frequency error estimator), CORDIC based NCO(Numerically Controlled Oscillator), FIR matched filters, decimator, demodulator, etc. Other than these units, the proposed receiver has units that make it adaptive. As shown in figure, it has an interference detector and an SNR estimator (IDSE), and an adaptivity control unit that decides the  and

and  of different sections of the receiver. For every packet the receiver starts off with the highest resolution and sampling frequency settings during the packet preamble. Synchronization (Timing, Frequency, Phase) is done with the highest settings and simultaneously, the interference and signal levels are estimated. By the end of the preamble, a LUT containing optimal values is consulted and the optimum

of different sections of the receiver. For every packet the receiver starts off with the highest resolution and sampling frequency settings during the packet preamble. Synchronization (Timing, Frequency, Phase) is done with the highest settings and simultaneously, the interference and signal levels are estimated. By the end of the preamble, a LUT containing optimal values is consulted and the optimum  and

and  is used for the rest of the packet reception. All sections of the receiver in Figure 2 except the VGA and ADC are implemented in HDL for power estimation.

is used for the rest of the packet reception. All sections of the receiver in Figure 2 except the VGA and ADC are implemented in HDL for power estimation.

and

and  of different sections of the receiver. For every packet the receiver starts off with the highest resolution and sampling frequency settings during the packet preamble. Synchronization (Timing, Frequency, Phase) is done with the highest settings and simultaneously, the interference and signal levels are estimated. By the end of the preamble, a LUT containing optimal values is consulted and the optimum

of different sections of the receiver. For every packet the receiver starts off with the highest resolution and sampling frequency settings during the packet preamble. Synchronization (Timing, Frequency, Phase) is done with the highest settings and simultaneously, the interference and signal levels are estimated. By the end of the preamble, a LUT containing optimal values is consulted and the optimum  and

and  is used for the rest of the packet reception. All sections of the receiver in Figure 2 except the VGA and ADC are implemented in HDL for power estimation.

is used for the rest of the packet reception. All sections of the receiver in Figure 2 except the VGA and ADC are implemented in HDL for power estimation.

Figure 2.

Proposed Adaptive Receiver.  is sampling frequency and

is sampling frequency and  is word length.

is word length.

is sampling frequency and

is sampling frequency and  is word length.

is word length.

Figure 2.

Proposed Adaptive Receiver.  is sampling frequency and

is sampling frequency and  is word length.

is word length.

is sampling frequency and

is sampling frequency and  is word length.

is word length.

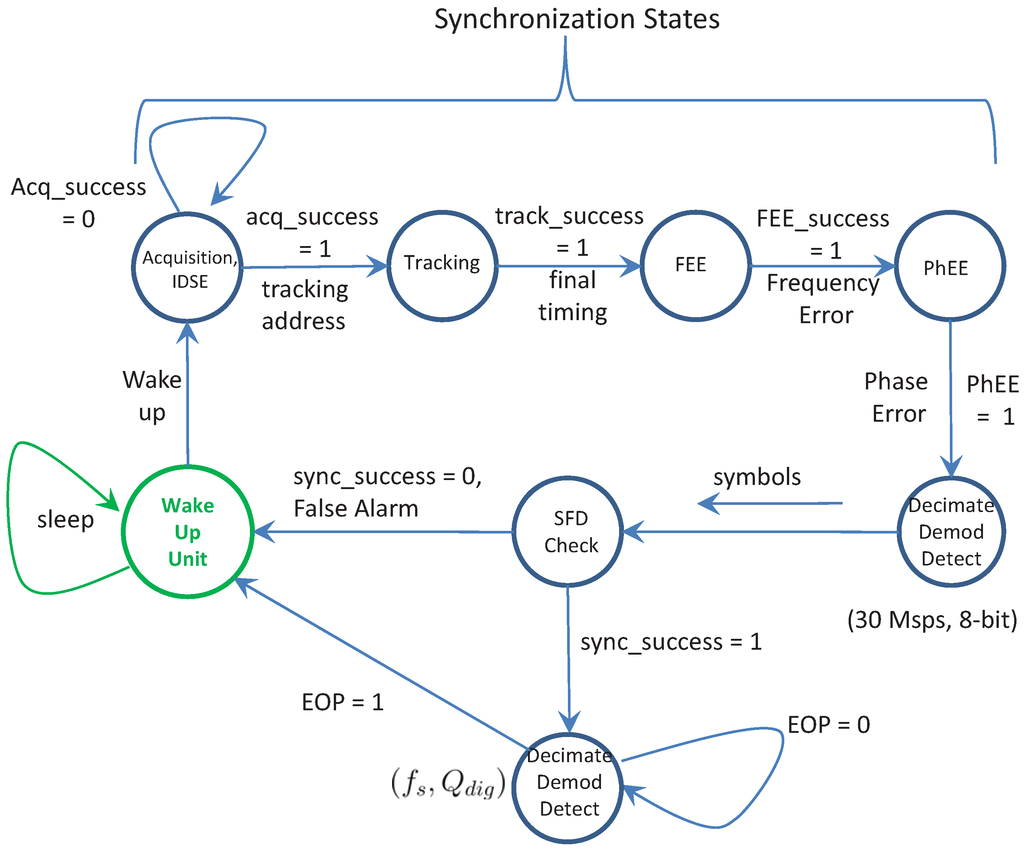

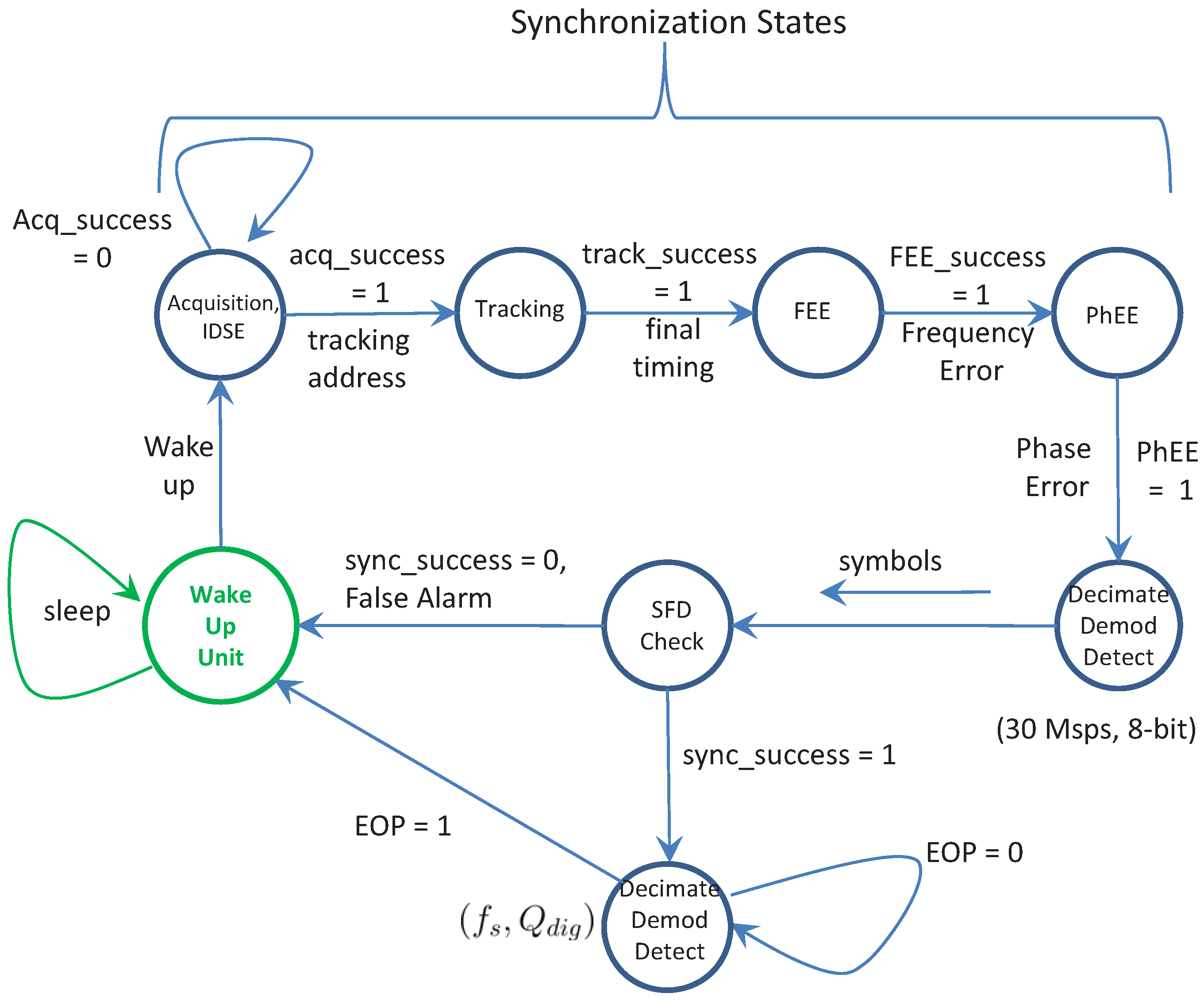

Figure 3 shows the state diagram of the receiver with seven states. Timing synchronization is achieved over Acquisition and Tracking. The Frequency Error Estimator (FEE) estimates the error between carrier frequency of the desired signal and frequency of the local oscillators that down-converts the signal. Similarly, Phase Error Estimator (PhEE) estimates the error in phase of input signal and down-converting signals. These estimates are used to correct the errors in frequency and phase to allow coherent demodulation of the signal. Start-Frame-Delimiter (SFD) check provides a means to check if the synchronization achieved is reliable to further demodulate the data. As shown in the figure, acq_success, track_success, FEE_success and PhEE cause transition of states during synchronization. The synchronizing units work in tandem. sync_succ signifies completion of synchronization and preamble of the packet. Detailed architecture of these synchronization units can be found in [12,13,14]. The decimator, demodulator and detector work in two different settings of  and

and  . The first setting as shown in the Figure 3 (

. The first setting as shown in the Figure 3 (  Msps,

Msps,  -bit) is the setting of word length and sampling frequency for the receiver during preamble of the packet. The second setting (

-bit) is the setting of word length and sampling frequency for the receiver during preamble of the packet. The second setting (  ,

,  ) applies for rest of the packet, i.e., PHY service data unit (PSDU).

) applies for rest of the packet, i.e., PHY service data unit (PSDU).

and

and  . The first setting as shown in the Figure 3 (

. The first setting as shown in the Figure 3 (  Msps,

Msps,  -bit) is the setting of word length and sampling frequency for the receiver during preamble of the packet. The second setting (

-bit) is the setting of word length and sampling frequency for the receiver during preamble of the packet. The second setting (  ,

,  ) applies for rest of the packet, i.e., PHY service data unit (PSDU).

) applies for rest of the packet, i.e., PHY service data unit (PSDU).

Figure 3.

State Diagram of Receiver. STATES: (1) Acquisition; (2) Tracking; (3) Frequency error estimation (FEE); (4) Phase error estimation (PhEE); (5) Decimate, demodulate and detect at  and

and  ; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at

; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at  and

and  .

.

and

and  ; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at

; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at  and

and  .

.

Figure 3.

State Diagram of Receiver. STATES: (1) Acquisition; (2) Tracking; (3) Frequency error estimation (FEE); (4) Phase error estimation (PhEE); (5) Decimate, demodulate and detect at  and

and  ; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at

; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at  and

and  .

.

and

and  ; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at

; (6) Start-Frame-Delimiter (SFD) check; (7) Decimate, demodulate and detect at  and

and  .

.

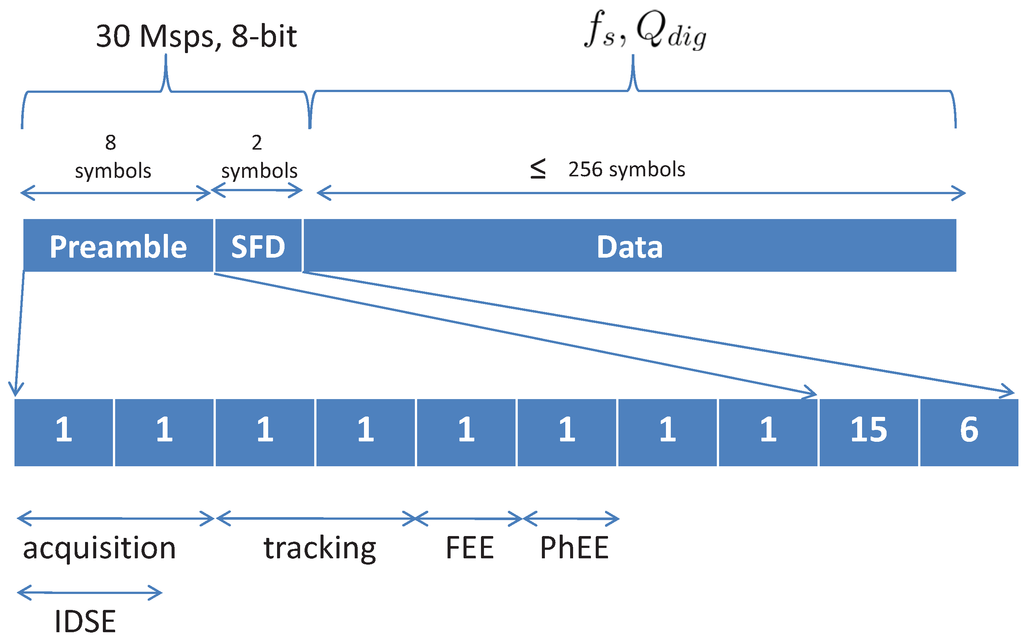

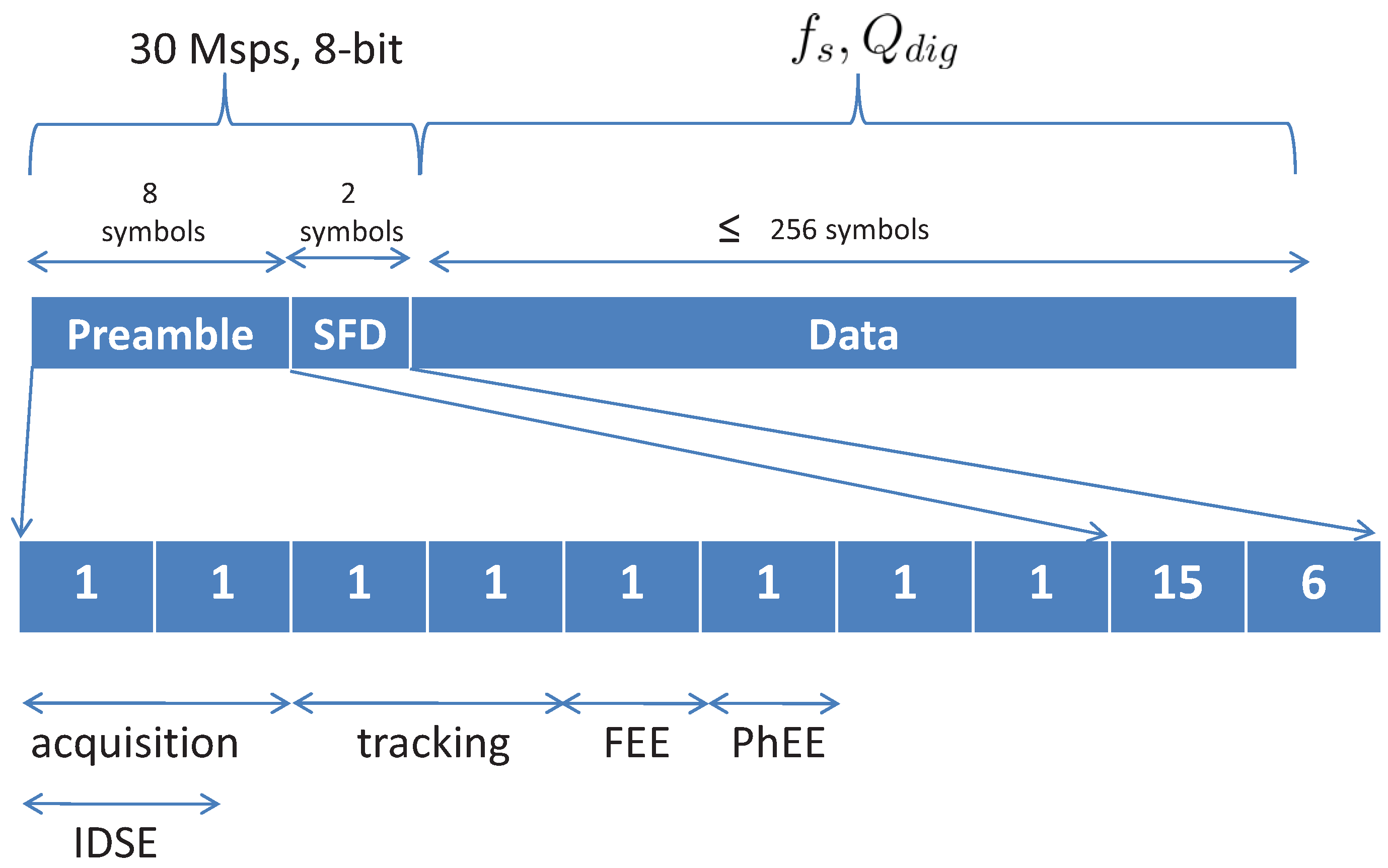

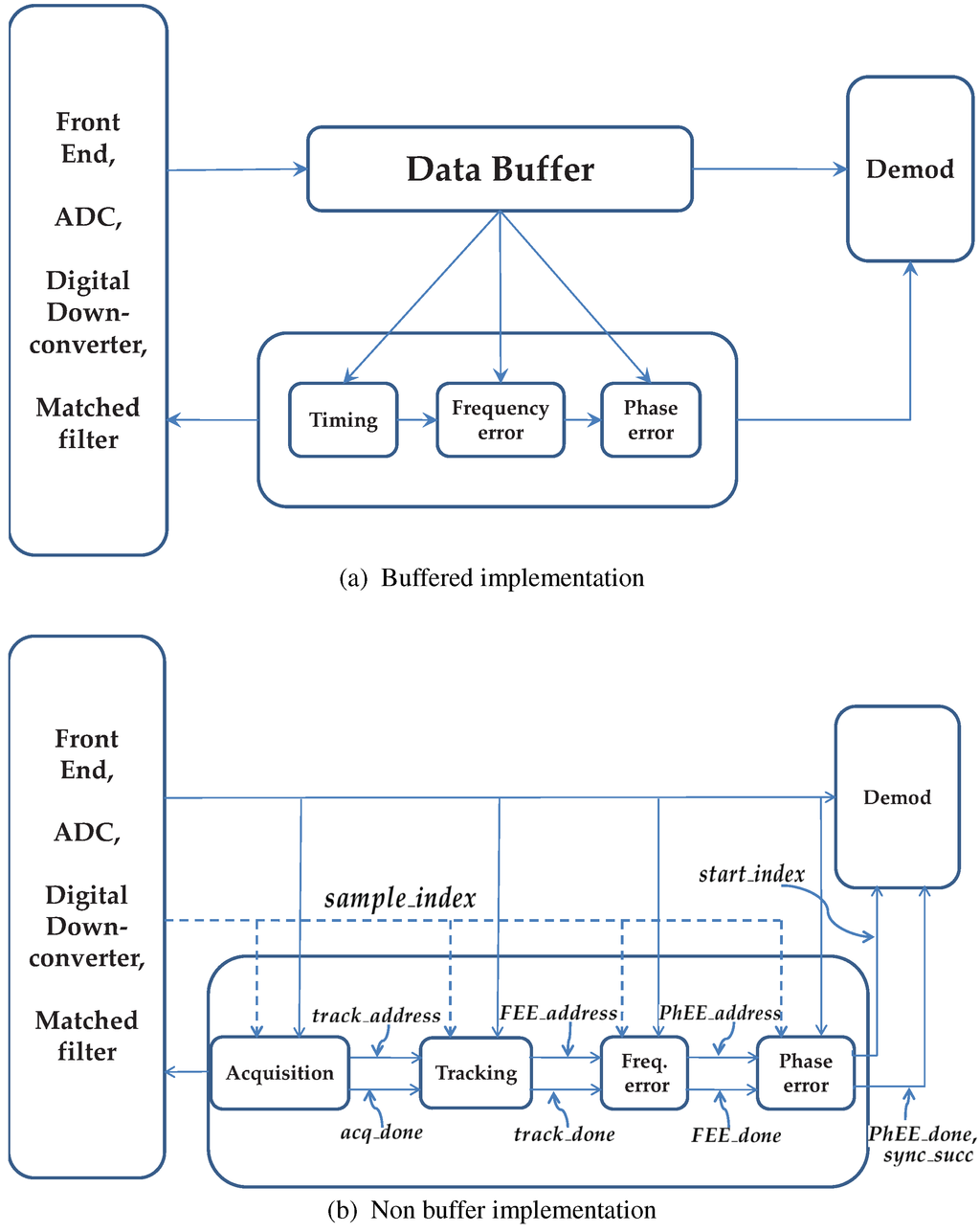

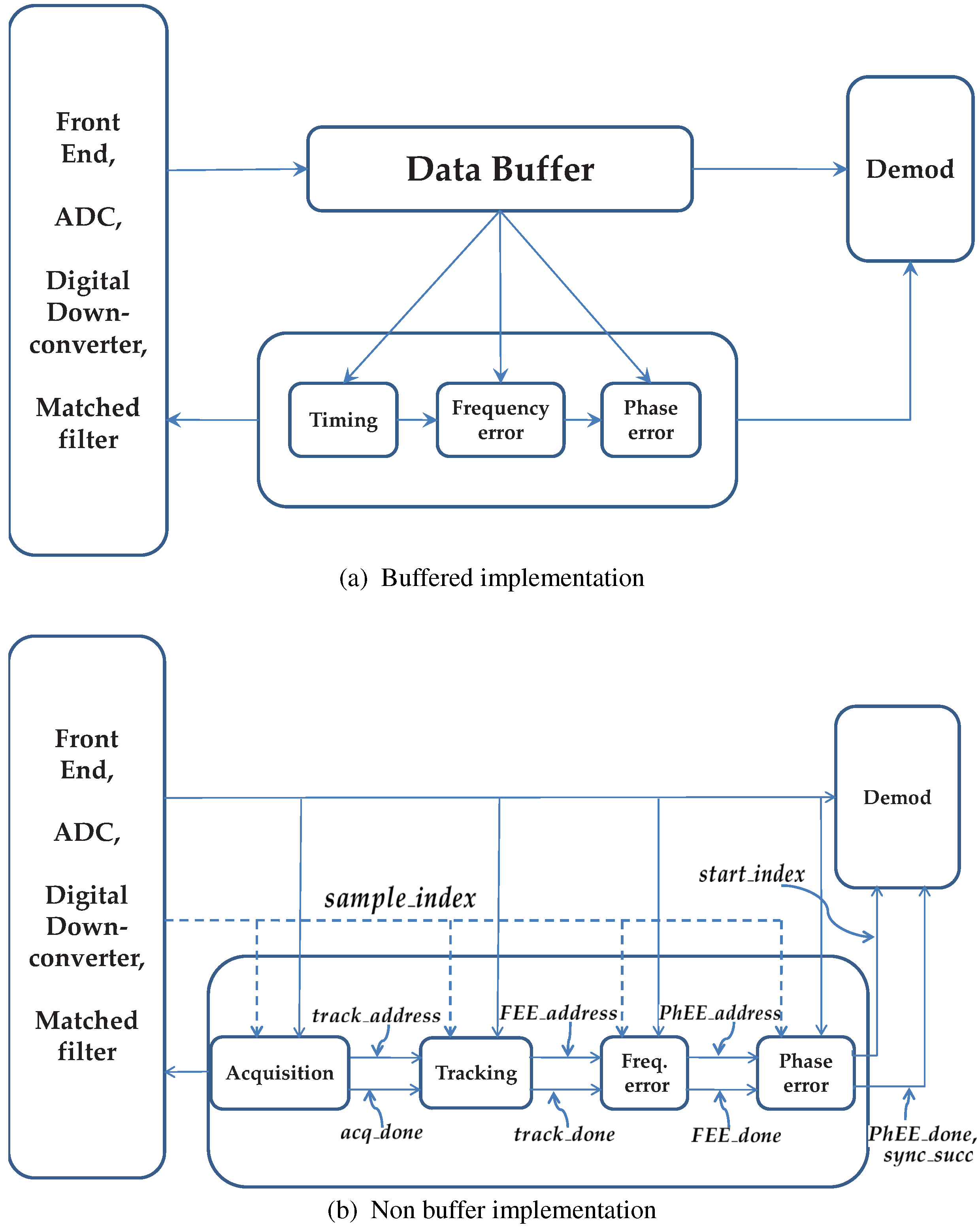

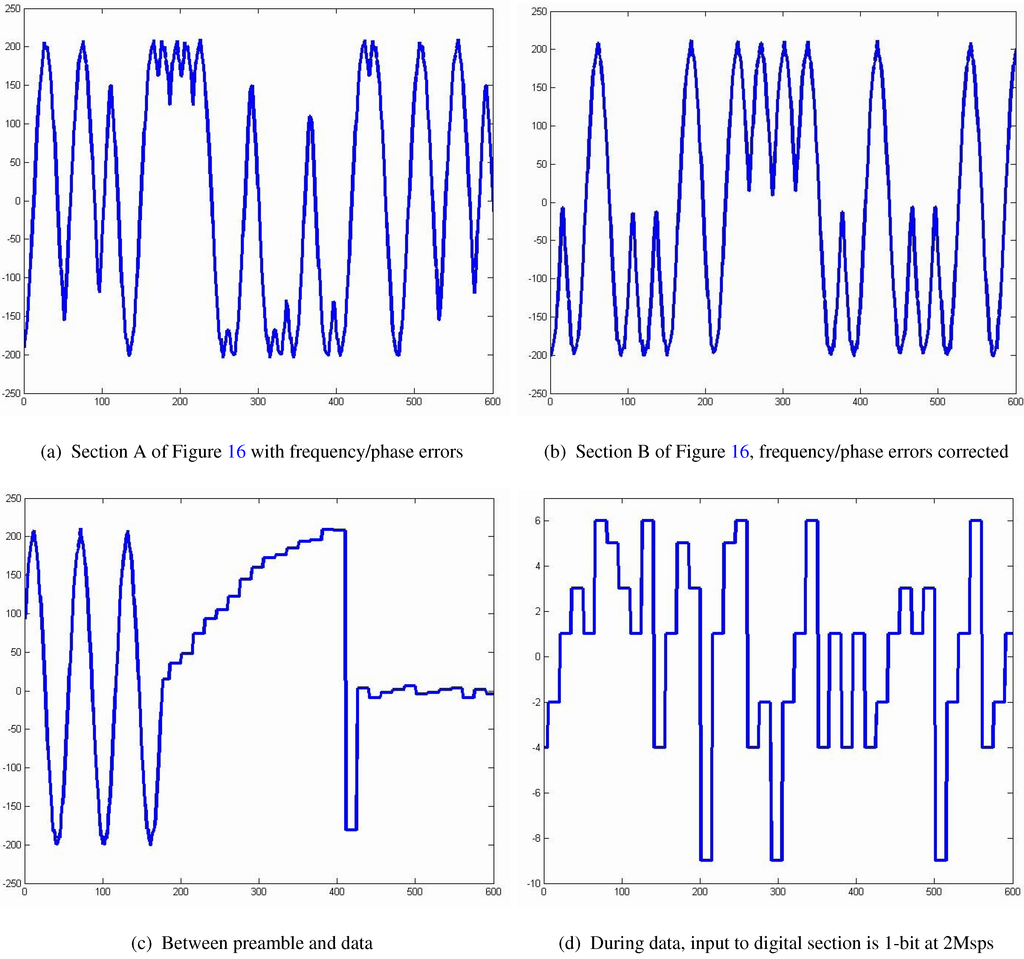

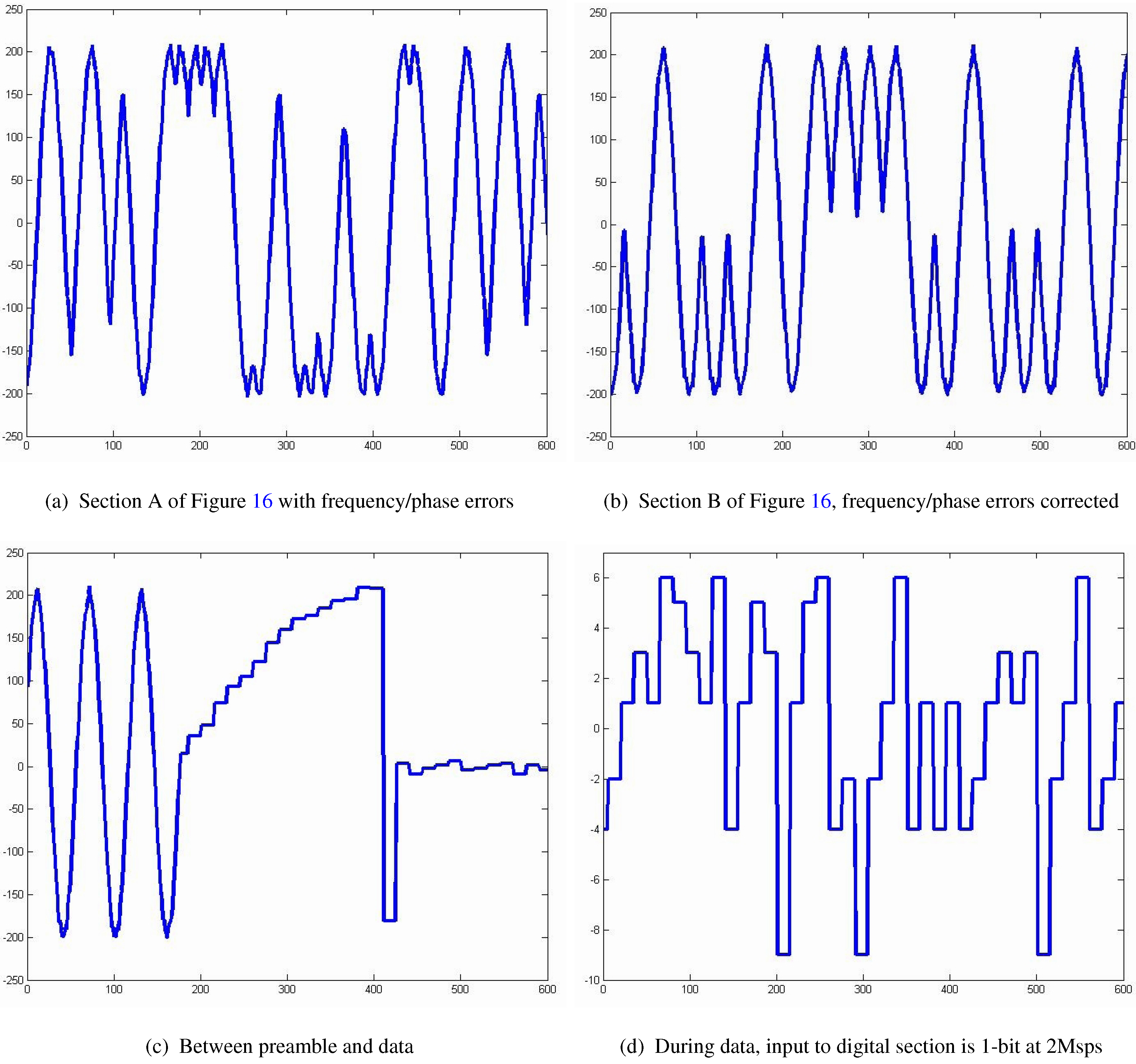

The preamble is a sequence of symbol “1” followed by two SFD symbols as shown in the Figure 4. The figure shows a typical packet structure and the average time taken by various synchronization steps during the preamble when  is high. The synchronization designed for this receiver works on the continuous flowing sampled data from ADC. Figure 5(a) shows the typical buffered implementation of a receiver. Here, various signal processing blocks inside the receiver access the data from the buffer. This allows the receiver algorithms to reuse the data and gives better convergence performance. However, our approach for the receiver design does not use any buffer to save area and power. Figure 5(b) shows the non-buffered approach. Here, besides passing information regarding completion of its functioning as discussed above, every module passes a sample index to the subsequent module. For, e.g., acquisition unit passes acq_success and a count track_address to the tracking block once acquisition is done. The tracking unit initiates a counter when acq_success is received. The counter counts number of samples and the tracking begins when the counter reaches the count track_address. Once the synchronization is done (

is high. The synchronization designed for this receiver works on the continuous flowing sampled data from ADC. Figure 5(a) shows the typical buffered implementation of a receiver. Here, various signal processing blocks inside the receiver access the data from the buffer. This allows the receiver algorithms to reuse the data and gives better convergence performance. However, our approach for the receiver design does not use any buffer to save area and power. Figure 5(b) shows the non-buffered approach. Here, besides passing information regarding completion of its functioning as discussed above, every module passes a sample index to the subsequent module. For, e.g., acquisition unit passes acq_success and a count track_address to the tracking block once acquisition is done. The tracking unit initiates a counter when acq_success is received. The counter counts number of samples and the tracking begins when the counter reaches the count track_address. Once the synchronization is done (  ) is raised, all synchronization blocks turn off and receiver data-path (NCO, Matched filters, decimator, demodulator and detector) adjusts itself to new settings of

) is raised, all synchronization blocks turn off and receiver data-path (NCO, Matched filters, decimator, demodulator and detector) adjusts itself to new settings of  and

and

is high. The synchronization designed for this receiver works on the continuous flowing sampled data from ADC. Figure 5(a) shows the typical buffered implementation of a receiver. Here, various signal processing blocks inside the receiver access the data from the buffer. This allows the receiver algorithms to reuse the data and gives better convergence performance. However, our approach for the receiver design does not use any buffer to save area and power. Figure 5(b) shows the non-buffered approach. Here, besides passing information regarding completion of its functioning as discussed above, every module passes a sample index to the subsequent module. For, e.g., acquisition unit passes acq_success and a count track_address to the tracking block once acquisition is done. The tracking unit initiates a counter when acq_success is received. The counter counts number of samples and the tracking begins when the counter reaches the count track_address. Once the synchronization is done (

is high. The synchronization designed for this receiver works on the continuous flowing sampled data from ADC. Figure 5(a) shows the typical buffered implementation of a receiver. Here, various signal processing blocks inside the receiver access the data from the buffer. This allows the receiver algorithms to reuse the data and gives better convergence performance. However, our approach for the receiver design does not use any buffer to save area and power. Figure 5(b) shows the non-buffered approach. Here, besides passing information regarding completion of its functioning as discussed above, every module passes a sample index to the subsequent module. For, e.g., acquisition unit passes acq_success and a count track_address to the tracking block once acquisition is done. The tracking unit initiates a counter when acq_success is received. The counter counts number of samples and the tracking begins when the counter reaches the count track_address. Once the synchronization is done (  ) is raised, all synchronization blocks turn off and receiver data-path (NCO, Matched filters, decimator, demodulator and detector) adjusts itself to new settings of

) is raised, all synchronization blocks turn off and receiver data-path (NCO, Matched filters, decimator, demodulator and detector) adjusts itself to new settings of  and

and

Figure 4.

Preamble and timing for various synchronization units. Figure shows how various synchronization blocks work in tandem.  =

=  MHz,

MHz,  =

=  -bit.

-bit.  —1 to 30 MHz.

—1 to 30 MHz.  —1 to 8 bits.

—1 to 8 bits.

=

=  MHz,

MHz,  =

=  -bit.

-bit.  —1 to 30 MHz.

—1 to 30 MHz.  —1 to 8 bits.

—1 to 8 bits.

Figure 4.

Preamble and timing for various synchronization units. Figure shows how various synchronization blocks work in tandem.  =

=  MHz,

MHz,  =

=  -bit.

-bit.  —1 to 30 MHz.

—1 to 30 MHz.  —1 to 8 bits.

—1 to 8 bits.

=

=  MHz,

MHz,  =

=  -bit.

-bit.  —1 to 30 MHz.

—1 to 30 MHz.  —1 to 8 bits.

—1 to 8 bits.

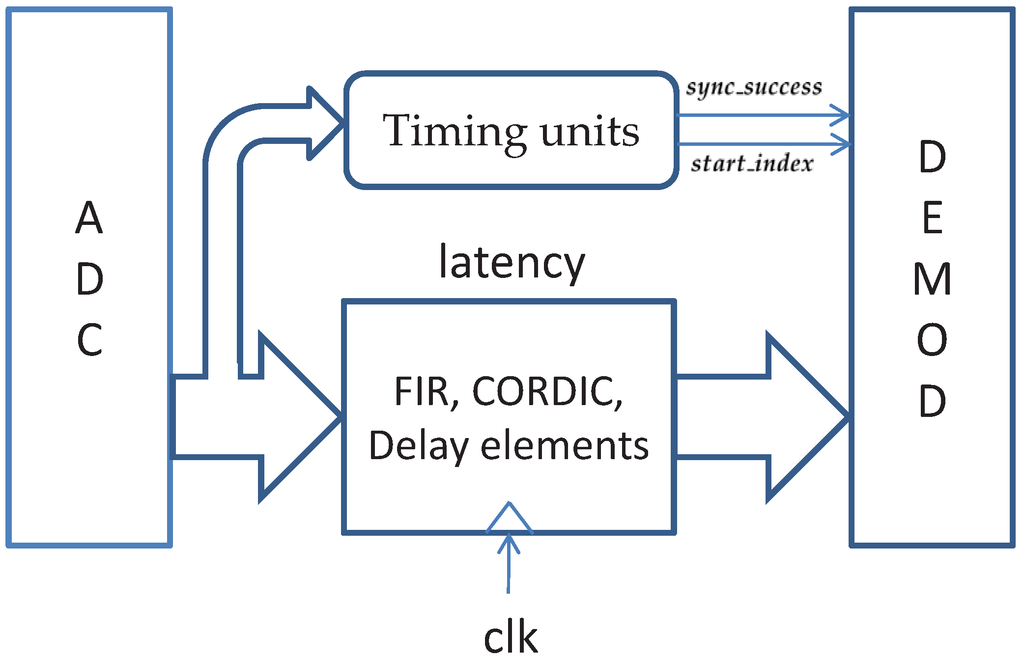

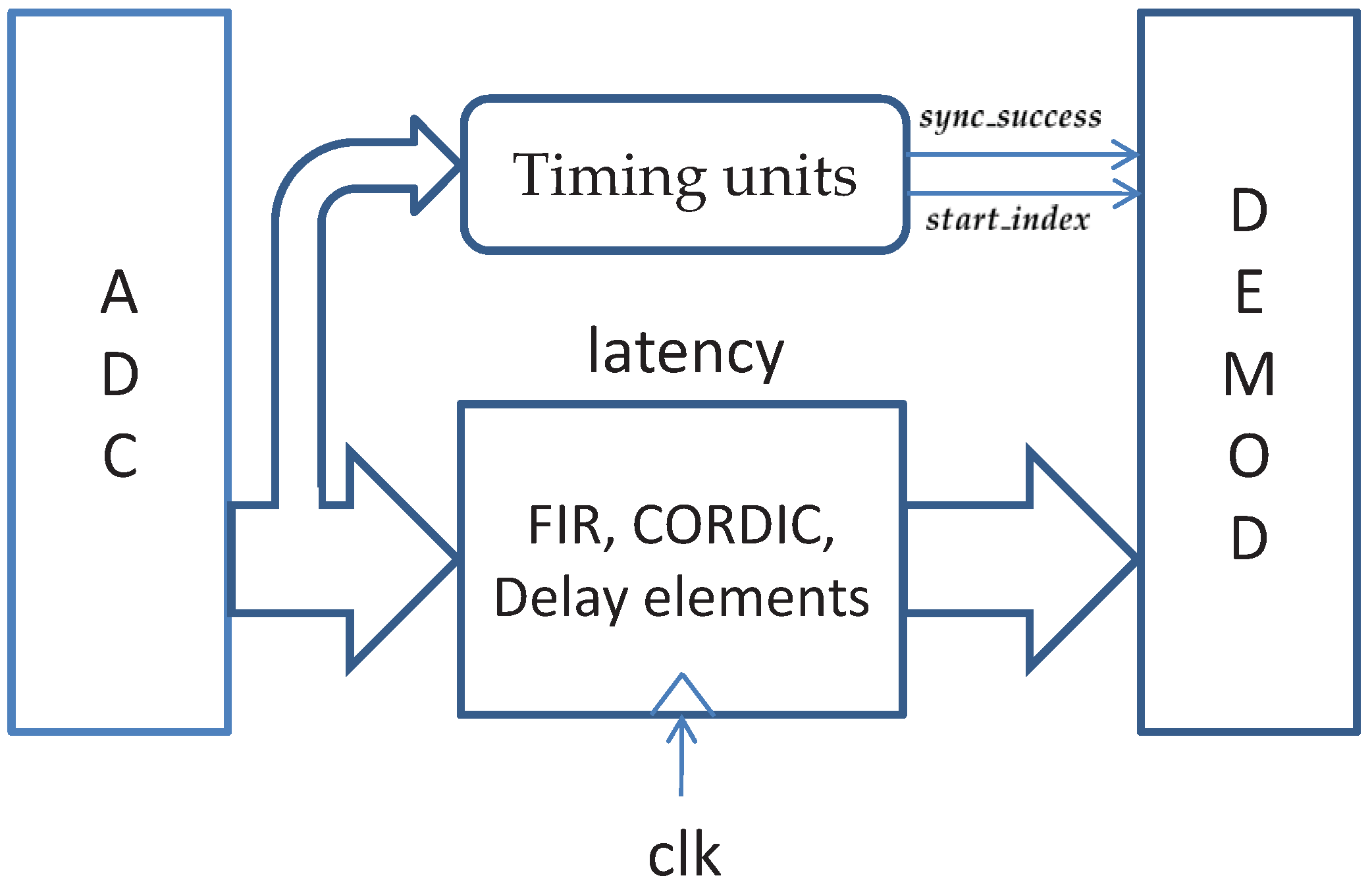

Changing sampling frequency requires the estimates for synchronization computed during preamble to be preserved. Values of the estimate depend on the sampling frequency [13]. The frequency estimate needs to be scaled and the phase continuity has to be preserved. The path from ADC output to the input of the demodulator has a latency of a number of clock cycles due to FIR, CORDIC pipelines, decimator, etc., as shown in Figure 6. When the sampling frequency of the receiver is changed after the packet preamble, the delay elements in these contain samples sampled at the highest sampling frequency used during preamble. The receiver is very sensitive to timing error when the sampling frequency is very low. For, e.g., for sampling frequency of 2 Msps, every pulse is sampled twice. In such a case, an error of one sample results in offset by half a pulse. Hence the delay across the data-path needs to be carefully accounted, particularly, when the sampling frequency is low. While changing  and

and  , it is proposed to discard all samples in delay elements across the receiver. This is due to the fact that the samples in delay elements across the receiver is sampled at higher sampling frequency than the new assigned

, it is proposed to discard all samples in delay elements across the receiver. This is due to the fact that the samples in delay elements across the receiver is sampled at higher sampling frequency than the new assigned  and

and  for the data duration. Delay elements are reset when the adap_ctrl goes high. As shown in Figure 6, once the sync_succ goes high, demodulator waits until the sample_index reaches start_index. Value of start_index is equal to number of clock cycle delay from output of ADC to demodulator.

for the data duration. Delay elements are reset when the adap_ctrl goes high. As shown in Figure 6, once the sync_succ goes high, demodulator waits until the sample_index reaches start_index. Value of start_index is equal to number of clock cycle delay from output of ADC to demodulator.

and

and  , it is proposed to discard all samples in delay elements across the receiver. This is due to the fact that the samples in delay elements across the receiver is sampled at higher sampling frequency than the new assigned

, it is proposed to discard all samples in delay elements across the receiver. This is due to the fact that the samples in delay elements across the receiver is sampled at higher sampling frequency than the new assigned  and

and  for the data duration. Delay elements are reset when the adap_ctrl goes high. As shown in Figure 6, once the sync_succ goes high, demodulator waits until the sample_index reaches start_index. Value of start_index is equal to number of clock cycle delay from output of ADC to demodulator.

for the data duration. Delay elements are reset when the adap_ctrl goes high. As shown in Figure 6, once the sync_succ goes high, demodulator waits until the sample_index reaches start_index. Value of start_index is equal to number of clock cycle delay from output of ADC to demodulator.

Figure 5.

Buffered and non-buffered implementation of the receiver.

Figure 5.

Buffered and non-buffered implementation of the receiver.

Figure 6.

Latency in data-path and preserving timing.

Figure 6.

Latency in data-path and preserving timing.

3. Determining Optimal LUT

As discussed in previous section, we use simulations to determine the combinations of quantization parameters that guarantee the BER for Equation (2). Thus for each input  and interference, we evaluate BER of the receiver for several different settings of

and interference, we evaluate BER of the receiver for several different settings of  and

and  .

.

and interference, we evaluate BER of the receiver for several different settings of

and interference, we evaluate BER of the receiver for several different settings of  and

and  .

.3.1. Simulation Model

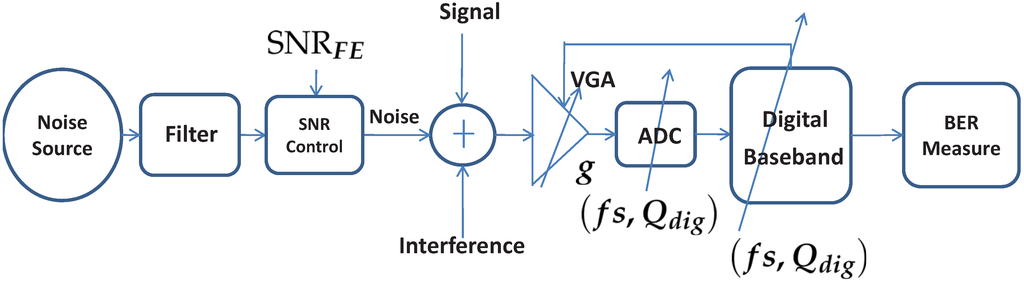

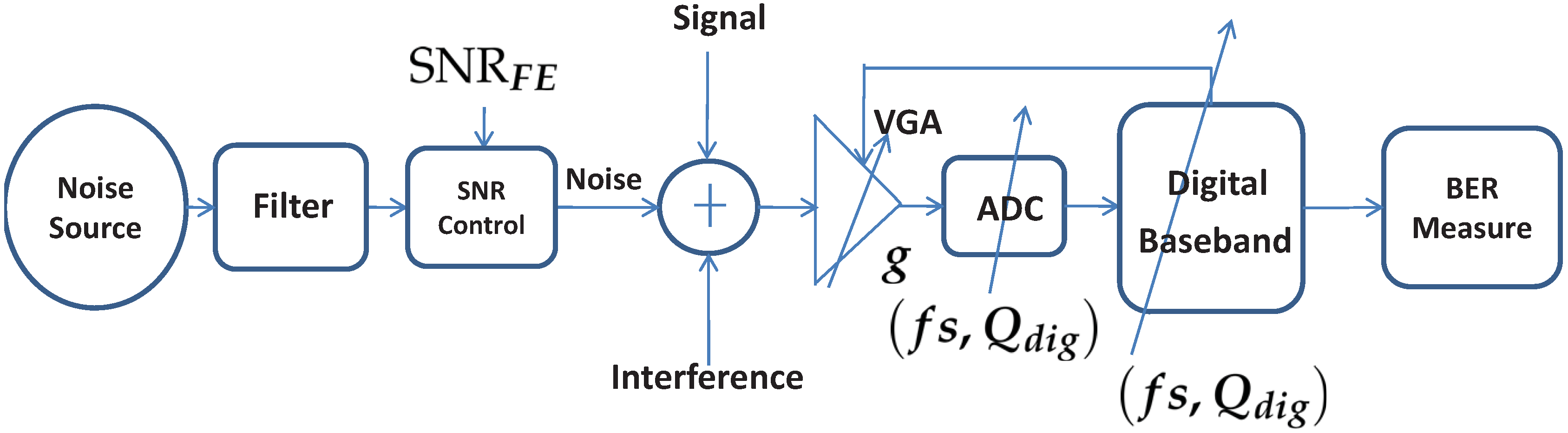

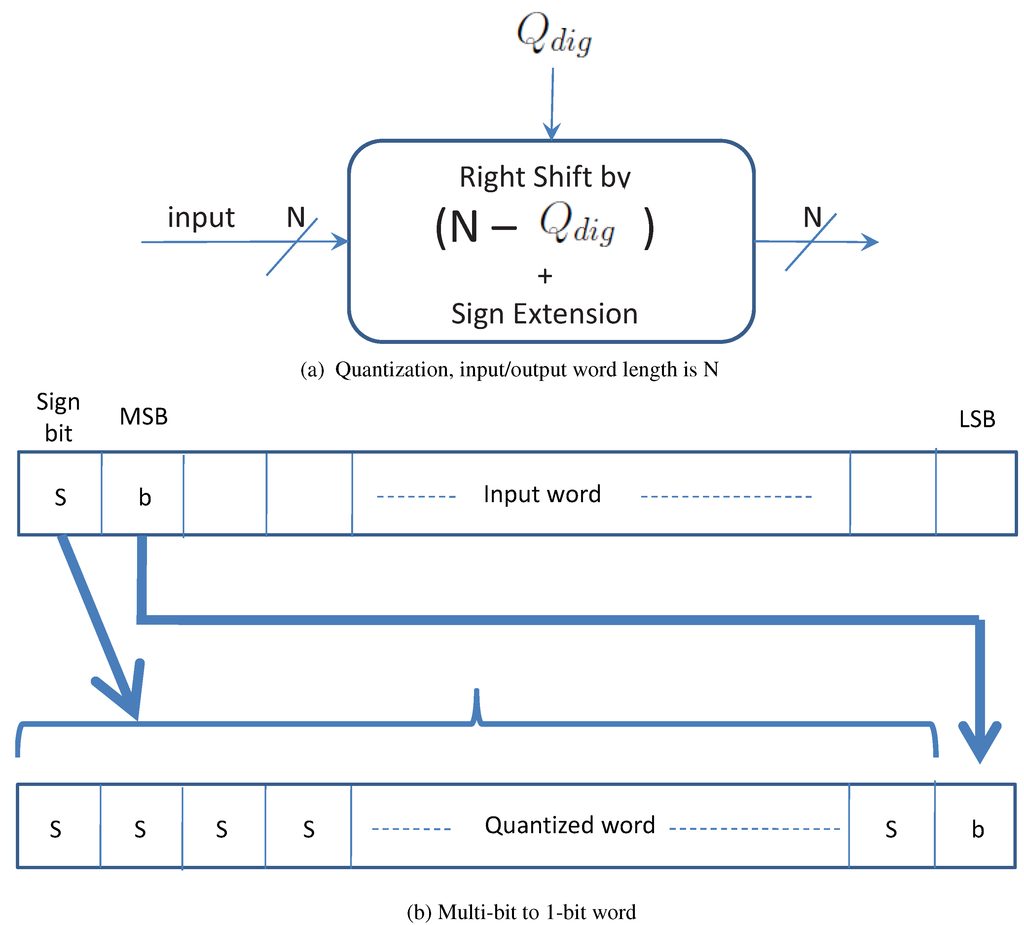

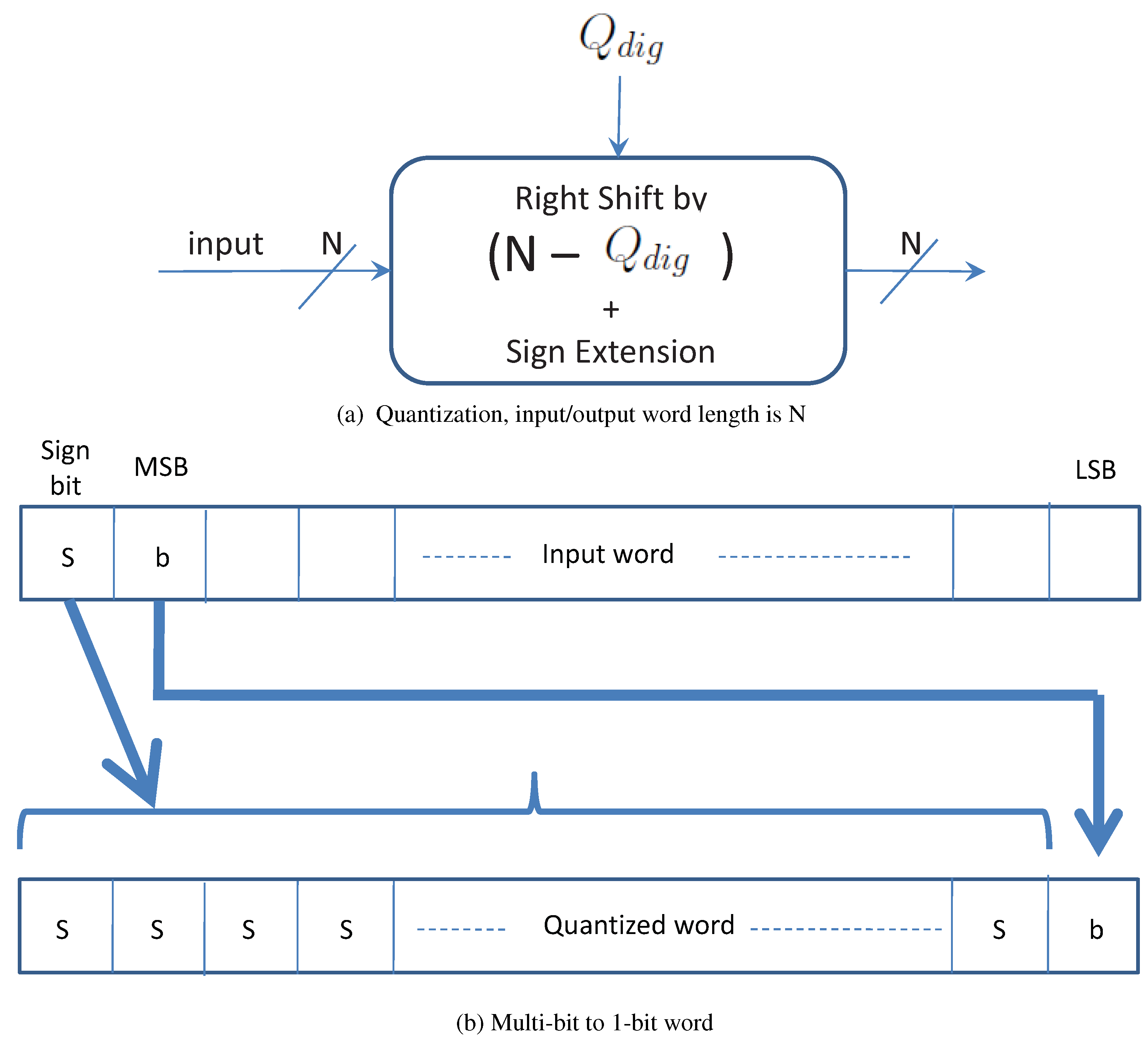

We use the fixed point toolbox of Matlab for quantization simulations. The simulation model used is shown in Figure 7. As we see in the simulation model signal, noise and interference pass through the channel select filter. The variable gain amplifier (VGA), upon getting feedback from digital portion of the receiver, re-sizes signal levels to full scale of ADC. Noise levels are controlled by the SNR control to maintain a  at the input of ADC. Amplitude and time resolutions of ADC and digital baseband sections are variable.

at the input of ADC. Amplitude and time resolutions of ADC and digital baseband sections are variable.

at the input of ADC. Amplitude and time resolutions of ADC and digital baseband sections are variable.

at the input of ADC. Amplitude and time resolutions of ADC and digital baseband sections are variable.

Figure 7.

Simulation Model,  is the variable gain of VGA,

is the variable gain of VGA,  and

and  are sampling frequency and bitwidth respectively.

are sampling frequency and bitwidth respectively.

is the variable gain of VGA,

is the variable gain of VGA,  and

and  are sampling frequency and bitwidth respectively.

are sampling frequency and bitwidth respectively.

Figure 7.

Simulation Model,  is the variable gain of VGA,

is the variable gain of VGA,  and

and  are sampling frequency and bitwidth respectively.

are sampling frequency and bitwidth respectively.

is the variable gain of VGA,

is the variable gain of VGA,  and

and  are sampling frequency and bitwidth respectively.

are sampling frequency and bitwidth respectively.

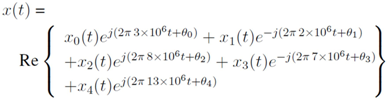

3.2. Interference Modeling

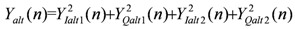

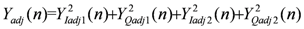

The standard specifies four interfering channels [15]. Channels adjacent to the desired channel transmit at same power level as the desired,  dBm, whereas alternate channels should be considered transmitting

dBm, whereas alternate channels should be considered transmitting  dBm. Adjacent channels are

dBm. Adjacent channels are  MHz apart from the desired channel on either side. Similarly, alternate channels are

MHz apart from the desired channel on either side. Similarly, alternate channels are  MHz apart. For an IF of

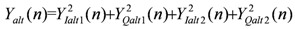

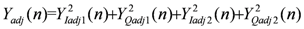

MHz apart. For an IF of  MHz [16], input to the ADC can be given as

MHz [16], input to the ADC can be given as

is the desired baseband signal.

is the desired baseband signal.  and

and  are adjacent baseband signals.

are adjacent baseband signals.  and

and  are alternate baseband signals.

are alternate baseband signals.

dBm, whereas alternate channels should be considered transmitting

dBm, whereas alternate channels should be considered transmitting  dBm. Adjacent channels are

dBm. Adjacent channels are  MHz apart from the desired channel on either side. Similarly, alternate channels are

MHz apart from the desired channel on either side. Similarly, alternate channels are  MHz apart. For an IF of

MHz apart. For an IF of  MHz [16], input to the ADC can be given as

MHz [16], input to the ADC can be given as

is the desired baseband signal.

is the desired baseband signal.  and

and  are adjacent baseband signals.

are adjacent baseband signals.  and

and  are alternate baseband signals.

are alternate baseband signals.BER simulation to find all combination of  and

and  can be very time consuming [17]. Instead we have developed a technique to reduce the computation time. Initially we find the variance of correlations at the output of correlation demodulator. We use the same variance measure in our subsequent simulations with different receiver settings. We found that this technique reduces the simulation complexity lot in comparison with doing BER simulations with bandpass signals.

can be very time consuming [17]. Instead we have developed a technique to reduce the computation time. Initially we find the variance of correlations at the output of correlation demodulator. We use the same variance measure in our subsequent simulations with different receiver settings. We found that this technique reduces the simulation complexity lot in comparison with doing BER simulations with bandpass signals.

and

and  can be very time consuming [17]. Instead we have developed a technique to reduce the computation time. Initially we find the variance of correlations at the output of correlation demodulator. We use the same variance measure in our subsequent simulations with different receiver settings. We found that this technique reduces the simulation complexity lot in comparison with doing BER simulations with bandpass signals.

can be very time consuming [17]. Instead we have developed a technique to reduce the computation time. Initially we find the variance of correlations at the output of correlation demodulator. We use the same variance measure in our subsequent simulations with different receiver settings. We found that this technique reduces the simulation complexity lot in comparison with doing BER simulations with bandpass signals.4. Implementation Details

4.1. Interference Detector and  Estimator (IDSE)

Estimator (IDSE)

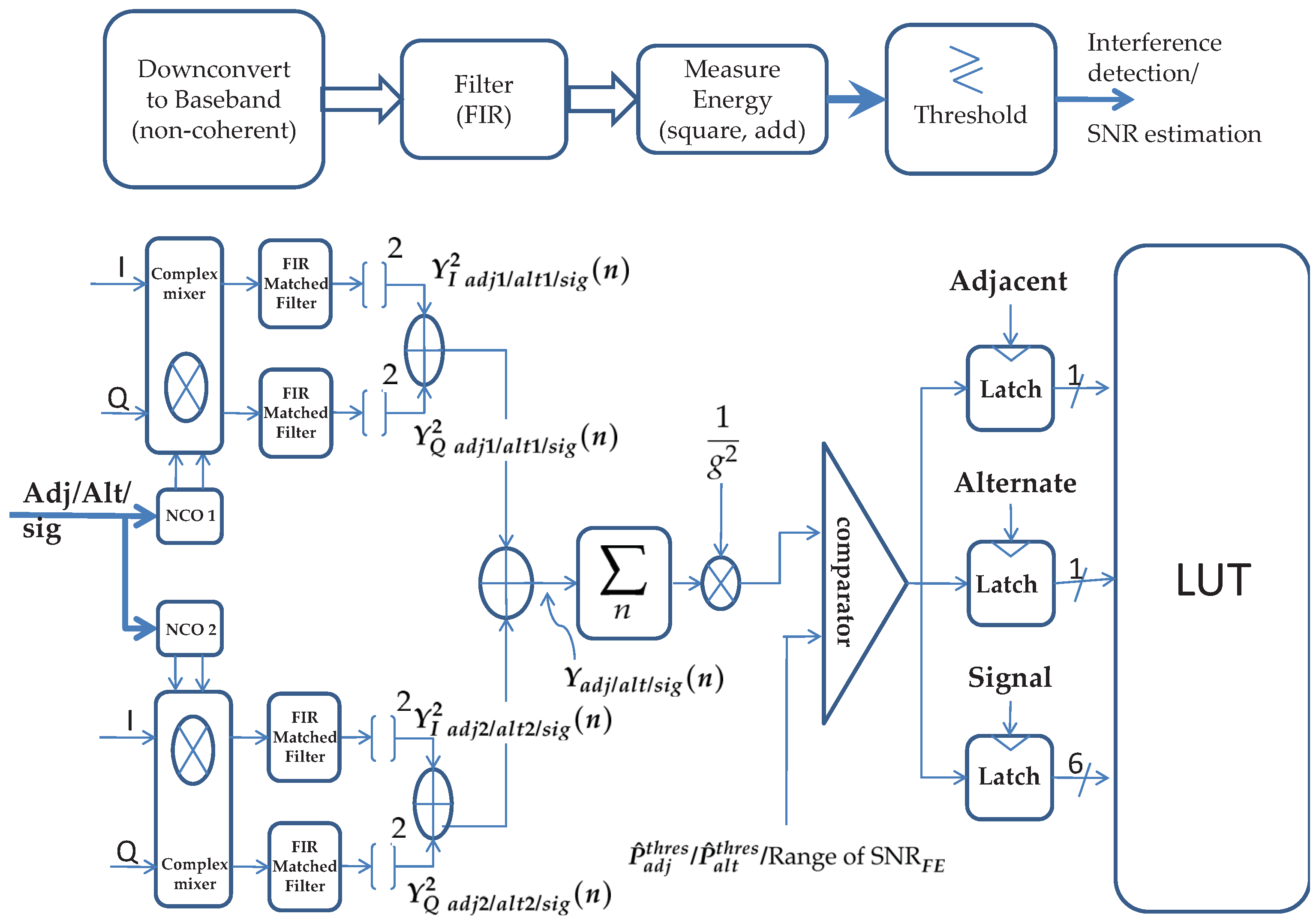

As mentioned in previous sections, central to the adaptive receiver is the Interference detector and SNR estimator. IDSE is active during the preamble. Power in adjacent, alternate and desired signal bands is measured non-coherently.  is the power measured in adjacent channels,

is the power measured in adjacent channels,  is the total power in alternate channels and

is the total power in alternate channels and  is the power in the desired signal’s channel.

is the power in the desired signal’s channel.

is the power measured in adjacent channels,

is the power measured in adjacent channels,  is the total power in alternate channels and

is the total power in alternate channels and  is the power in the desired signal’s channel.

is the power in the desired signal’s channel.4.1.1. Interference Detector

Proximity of the adjacent channel to the desired channel makes it more harmful to the signal than the alternate channels.

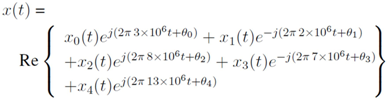

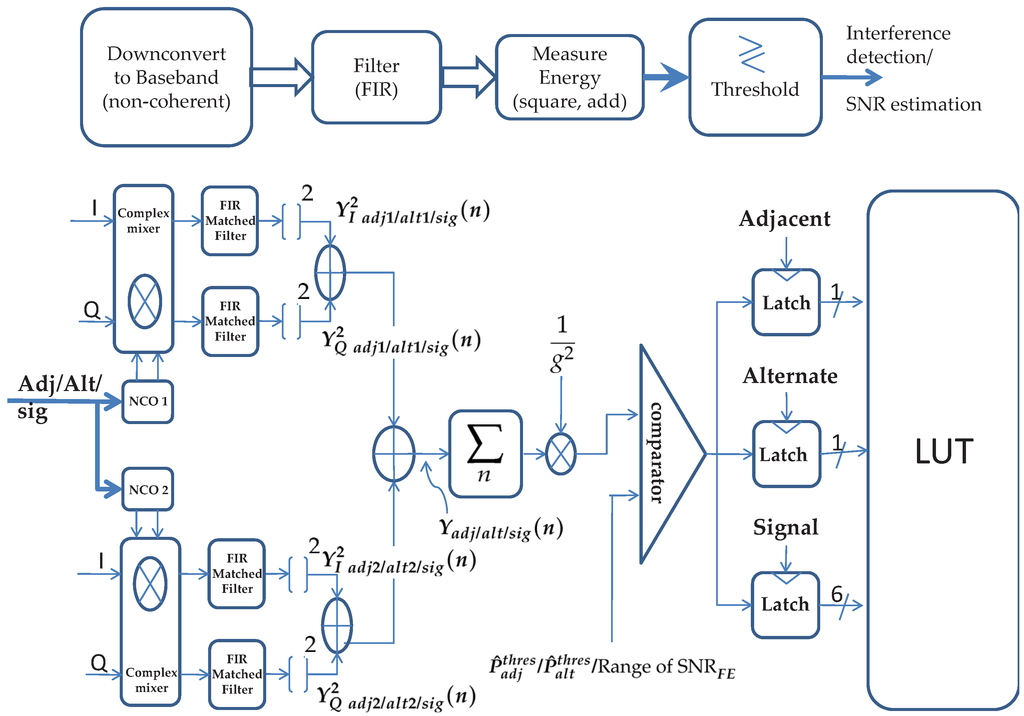

As can be seen from Figure 8, IDSE has three inputs: I and Q inputs from ADC and a signal that indicates if detection or estimation should be done. This input signal has three states: detect alternate, detect adjacent and estimate  . For all three states, setting of NCO is changed to down-convert adjacent or alternate or desired signal. IDSE consists of two arms, one each for one adjacent or alternate channel. Only one arm is active during

. For all three states, setting of NCO is changed to down-convert adjacent or alternate or desired signal. IDSE consists of two arms, one each for one adjacent or alternate channel. Only one arm is active during  estimation. Both arms have a CORDIC NCO unit to down-convert the interference or signal. Output of detectors/estimator goes to a comparator that compares it with threshold. For interference detection, output of comparators is 1-bit to indicate presence of interferences. In estimator mode, comparator finds the range in which the measured

estimation. Both arms have a CORDIC NCO unit to down-convert the interference or signal. Output of detectors/estimator goes to a comparator that compares it with threshold. For interference detection, output of comparators is 1-bit to indicate presence of interferences. In estimator mode, comparator finds the range in which the measured  falls. LUT has SNR steps with difference of

falls. LUT has SNR steps with difference of  dB. Since SNR variation can be up-to

dB. Since SNR variation can be up-to  dB so it has

dB so it has  SNR steps, requiring 6-bit index. There are four possible combinations from interference detection: Alternate present/absent and Adjacent present/absent, it is indicated by

SNR steps, requiring 6-bit index. There are four possible combinations from interference detection: Alternate present/absent and Adjacent present/absent, it is indicated by  bits. So, LUT is indexed by

bits. So, LUT is indexed by  -bits.

-bits.

. For all three states, setting of NCO is changed to down-convert adjacent or alternate or desired signal. IDSE consists of two arms, one each for one adjacent or alternate channel. Only one arm is active during

. For all three states, setting of NCO is changed to down-convert adjacent or alternate or desired signal. IDSE consists of two arms, one each for one adjacent or alternate channel. Only one arm is active during  estimation. Both arms have a CORDIC NCO unit to down-convert the interference or signal. Output of detectors/estimator goes to a comparator that compares it with threshold. For interference detection, output of comparators is 1-bit to indicate presence of interferences. In estimator mode, comparator finds the range in which the measured

estimation. Both arms have a CORDIC NCO unit to down-convert the interference or signal. Output of detectors/estimator goes to a comparator that compares it with threshold. For interference detection, output of comparators is 1-bit to indicate presence of interferences. In estimator mode, comparator finds the range in which the measured  falls. LUT has SNR steps with difference of

falls. LUT has SNR steps with difference of  dB. Since SNR variation can be up-to

dB. Since SNR variation can be up-to  dB so it has

dB so it has  SNR steps, requiring 6-bit index. There are four possible combinations from interference detection: Alternate present/absent and Adjacent present/absent, it is indicated by

SNR steps, requiring 6-bit index. There are four possible combinations from interference detection: Alternate present/absent and Adjacent present/absent, it is indicated by  bits. So, LUT is indexed by

bits. So, LUT is indexed by  -bits.

-bits.

Figure 8.

Non-coherent interference detection procedure.

Figure 8.

Non-coherent interference detection procedure.

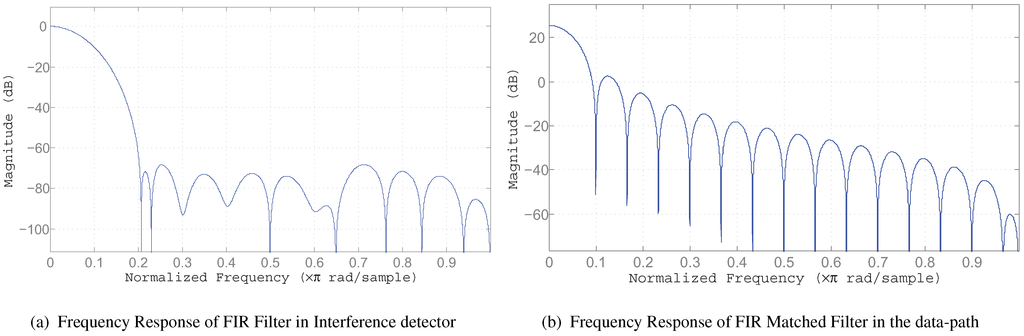

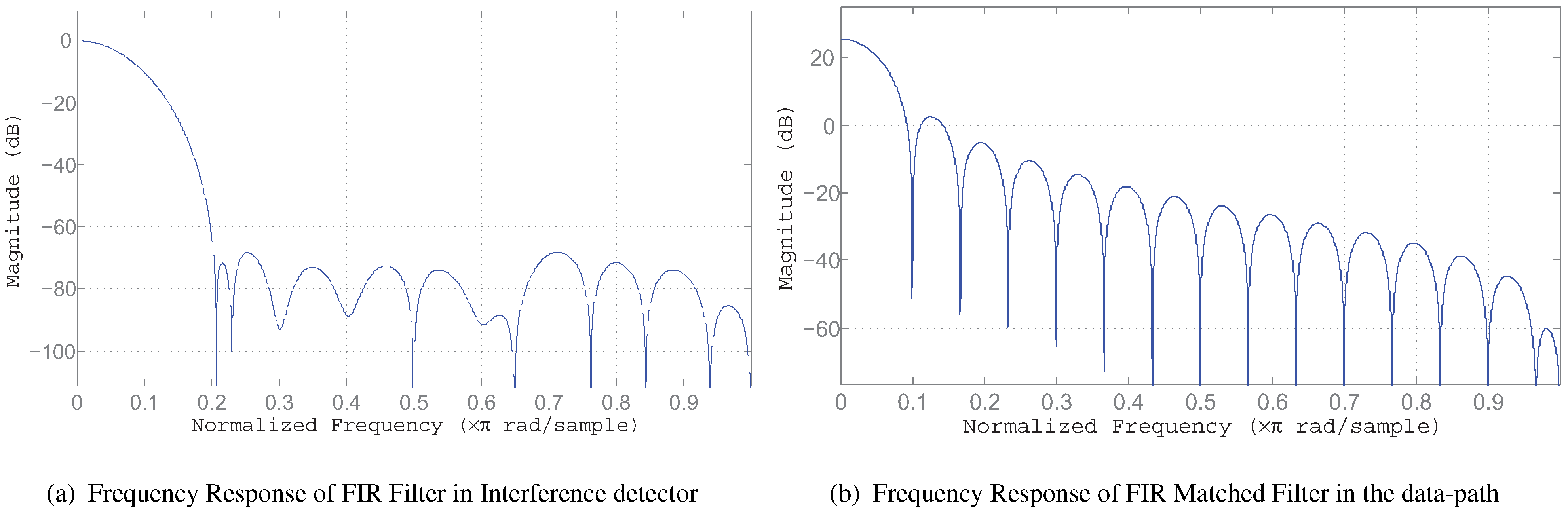

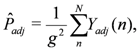

Figure 9(a) and Figure 9(b) are frequency responses of FIR filters used in IDSE and data-path of the receiver. The filter used for IDSE has a sharper roll-off. Interference from each interfering channel is down-converted to baseband and filtered by this filter. It can be seen from the filter’s frequency response that the attenuation at  MHz and

MHz and  MHz distance is approximately

MHz distance is approximately  dB. When measuring the desired signal power, due to attenuation by the matched filter, adjacent signal level falls to

dB. When measuring the desired signal power, due to attenuation by the matched filter, adjacent signal level falls to  dB and alternate signal level falls to

dB and alternate signal level falls to  dB. These levels of interference are quite low and do not corrupt the signal power estimation. Whereas, while measuring interference power, signal power from desired band can affect the interference power measurement. This is due to the fact that the maximum possible signal power is

dB. These levels of interference are quite low and do not corrupt the signal power estimation. Whereas, while measuring interference power, signal power from desired band can affect the interference power measurement. This is due to the fact that the maximum possible signal power is  dBm and it can spill to neighboring bands. At such high signal level even after the attenuation by the matched filter, its strength in neighboring channels is high enough to affect interference power measurement.

dBm and it can spill to neighboring bands. At such high signal level even after the attenuation by the matched filter, its strength in neighboring channels is high enough to affect interference power measurement.

MHz and

MHz and  MHz distance is approximately

MHz distance is approximately  dB. When measuring the desired signal power, due to attenuation by the matched filter, adjacent signal level falls to

dB. When measuring the desired signal power, due to attenuation by the matched filter, adjacent signal level falls to  dB and alternate signal level falls to

dB and alternate signal level falls to  dB. These levels of interference are quite low and do not corrupt the signal power estimation. Whereas, while measuring interference power, signal power from desired band can affect the interference power measurement. This is due to the fact that the maximum possible signal power is

dB. These levels of interference are quite low and do not corrupt the signal power estimation. Whereas, while measuring interference power, signal power from desired band can affect the interference power measurement. This is due to the fact that the maximum possible signal power is  dBm and it can spill to neighboring bands. At such high signal level even after the attenuation by the matched filter, its strength in neighboring channels is high enough to affect interference power measurement.

dBm and it can spill to neighboring bands. At such high signal level even after the attenuation by the matched filter, its strength in neighboring channels is high enough to affect interference power measurement.

Figure 9.

Frequency Response of FIR Filters.

Figure 9.

Frequency Response of FIR Filters.

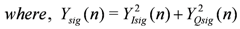

Let  and

and  be the in-phase and

be the in-phase and  and

and  are the quadrature phase adjacent channels. These terms are analogously defined for alternate channels too.

are the quadrature phase adjacent channels. These terms are analogously defined for alternate channels too.  is the gain of VGA [18,19]. Measured power in adjacent and alternate channels (

is the gain of VGA [18,19]. Measured power in adjacent and alternate channels (  ) can be defined as:

) can be defined as:

where,

where,

and

and  be the in-phase and

be the in-phase and  and

and  are the quadrature phase adjacent channels. These terms are analogously defined for alternate channels too.

are the quadrature phase adjacent channels. These terms are analogously defined for alternate channels too.  is the gain of VGA [18,19]. Measured power in adjacent and alternate channels (

is the gain of VGA [18,19]. Measured power in adjacent and alternate channels (  ) can be defined as:

) can be defined as:

If  exceeds a-priori calculated threshold,

exceeds a-priori calculated threshold,  , then adjacent interference is detected. Similarly,

, then adjacent interference is detected. Similarly,  is the threshold what is compared with

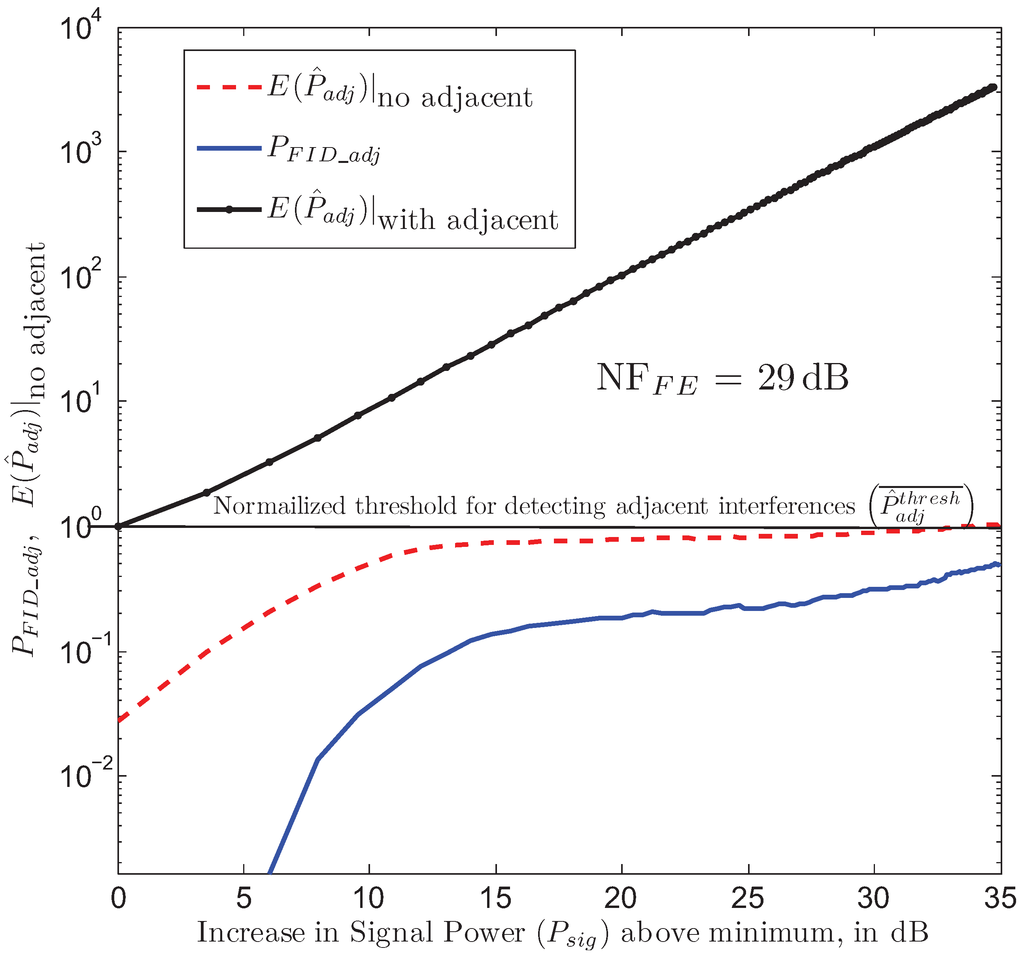

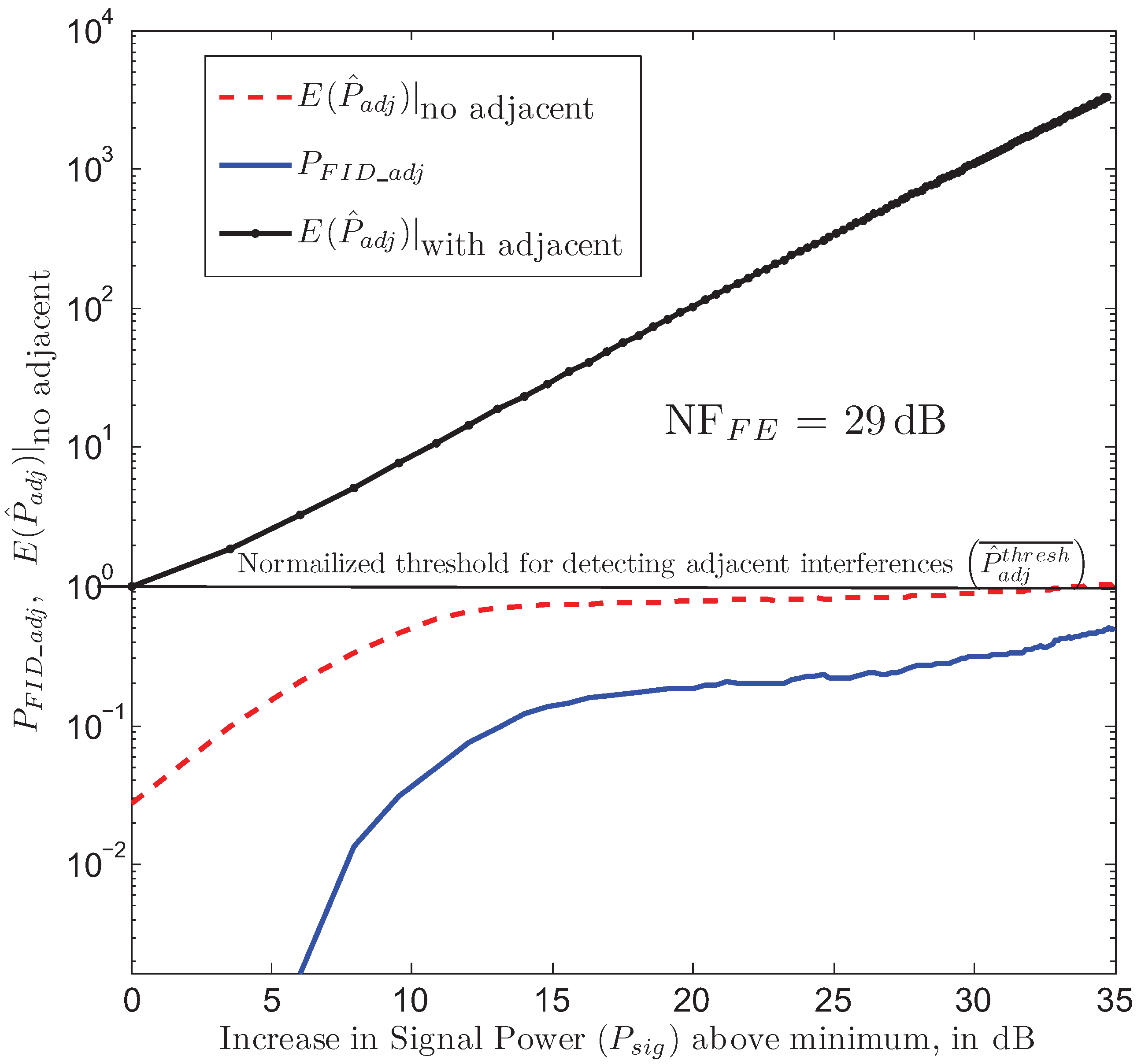

is the threshold what is compared with  . Figure 10 shows the effect of desired signal power on adjacent channel interference detection. The figure is obtained for front end noise figure (

. Figure 10 shows the effect of desired signal power on adjacent channel interference detection. The figure is obtained for front end noise figure (  ) of

) of  dB [20].

dB [20].  is the normalized threshold for detecting presence of adjacent interference. When signal power is large, then even in absence of adjacent interference,

is the normalized threshold for detecting presence of adjacent interference. When signal power is large, then even in absence of adjacent interference,  can exceed

can exceed  .

.  in figure is probability of false adjacent interference detection.

in figure is probability of false adjacent interference detection.  increases with increase in desired signal strength. When signal power is more than

increases with increase in desired signal strength. When signal power is more than  dBm, then even in absence of adjacent interference

dBm, then even in absence of adjacent interference  exceeds

exceeds  . As shown later, when

. As shown later, when  is high (

is high (  ),

),  and

and  settings of receiver is a minimum irrespective of outcome of interference detection. Effect of

settings of receiver is a minimum irrespective of outcome of interference detection. Effect of  is less severe on detecting alternate interference as alternate channels are farther in frequency domain. Variance of interference detector reduces with increase in number of pulses utilized for detection. Interference detection is done over four half sine pulses, as the variance does not change much for further increase in duration of detection.

is less severe on detecting alternate interference as alternate channels are farther in frequency domain. Variance of interference detector reduces with increase in number of pulses utilized for detection. Interference detection is done over four half sine pulses, as the variance does not change much for further increase in duration of detection.

exceeds a-priori calculated threshold,

exceeds a-priori calculated threshold,  , then adjacent interference is detected. Similarly,

, then adjacent interference is detected. Similarly,  is the threshold what is compared with

is the threshold what is compared with  . Figure 10 shows the effect of desired signal power on adjacent channel interference detection. The figure is obtained for front end noise figure (

. Figure 10 shows the effect of desired signal power on adjacent channel interference detection. The figure is obtained for front end noise figure (  ) of

) of  dB [20].

dB [20].  is the normalized threshold for detecting presence of adjacent interference. When signal power is large, then even in absence of adjacent interference,

is the normalized threshold for detecting presence of adjacent interference. When signal power is large, then even in absence of adjacent interference,  can exceed

can exceed  .

.  in figure is probability of false adjacent interference detection.

in figure is probability of false adjacent interference detection.  increases with increase in desired signal strength. When signal power is more than

increases with increase in desired signal strength. When signal power is more than  dBm, then even in absence of adjacent interference

dBm, then even in absence of adjacent interference  exceeds

exceeds  . As shown later, when

. As shown later, when  is high (

is high (  ),

),  and

and  settings of receiver is a minimum irrespective of outcome of interference detection. Effect of

settings of receiver is a minimum irrespective of outcome of interference detection. Effect of  is less severe on detecting alternate interference as alternate channels are farther in frequency domain. Variance of interference detector reduces with increase in number of pulses utilized for detection. Interference detection is done over four half sine pulses, as the variance does not change much for further increase in duration of detection.

is less severe on detecting alternate interference as alternate channels are farther in frequency domain. Variance of interference detector reduces with increase in number of pulses utilized for detection. Interference detection is done over four half sine pulses, as the variance does not change much for further increase in duration of detection.

Figure 10.

Performance of Interference detector for  =

=  dB. Minimum

dB. Minimum  =

=  dBm. NF is calculated for minimum

dBm. NF is calculated for minimum  . As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until

. As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until  is

is  dB above minimum.

dB above minimum.  of

of  dB corresponds to

dB corresponds to  dB

dB  .

.

=

=  dB. Minimum

dB. Minimum  =

=  dBm. NF is calculated for minimum

dBm. NF is calculated for minimum  . As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until

. As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until  is

is  dB above minimum.

dB above minimum.  of

of  dB corresponds to

dB corresponds to  dB

dB  .

.

Figure 10.

Performance of Interference detector for  =

=  dB. Minimum

dB. Minimum  =

=  dBm. NF is calculated for minimum

dBm. NF is calculated for minimum  . As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until

. As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until  is

is  dB above minimum.

dB above minimum.  of

of  dB corresponds to

dB corresponds to  dB

dB  .

.

=

=  dB. Minimum

dB. Minimum  =

=  dBm. NF is calculated for minimum

dBm. NF is calculated for minimum  . As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until

. As figure shows, large desired signal power hinders accurate interference detection. But as evident from Table 1, accurate interference detection is needed until  is

is  dB above minimum.

dB above minimum.  of

of  dB corresponds to

dB corresponds to  dB

dB  .

.

4.1.2. SNR Estimation

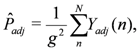

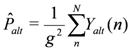

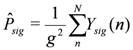

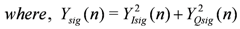

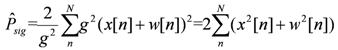

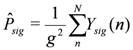

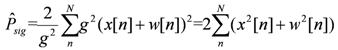

Similar to power measurement of interferences, power measured in desired signal channel is

If

If  and

and  are given by

are given by  , where

, where  is AWGN, then

is AWGN, then

Since signal and noise are uncorrelated,

Since signal and noise are uncorrelated,  ,

,

and

and  are given by

are given by  , where

, where  is AWGN, then

is AWGN, then

,

,

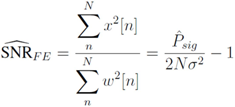

Thus to measure  , Equations (8) and (9) can be used. Front end of the receiver is designed for a constant noise figure. Thus the worst case variance of noise

, Equations (8) and (9) can be used. Front end of the receiver is designed for a constant noise figure. Thus the worst case variance of noise  contributed by the front end is known. Hence, SNR can be estimated using Equation (11).

contributed by the front end is known. Hence, SNR can be estimated using Equation (11).  estimator is ON for one symbol duration.

estimator is ON for one symbol duration.

, Equations (8) and (9) can be used. Front end of the receiver is designed for a constant noise figure. Thus the worst case variance of noise

, Equations (8) and (9) can be used. Front end of the receiver is designed for a constant noise figure. Thus the worst case variance of noise  contributed by the front end is known. Hence, SNR can be estimated using Equation (11).

contributed by the front end is known. Hence, SNR can be estimated using Equation (11).  estimator is ON for one symbol duration.

estimator is ON for one symbol duration.4.2. CORDIC Down-Converter and Phase Generation for CORDIC Blocks

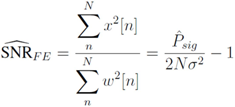

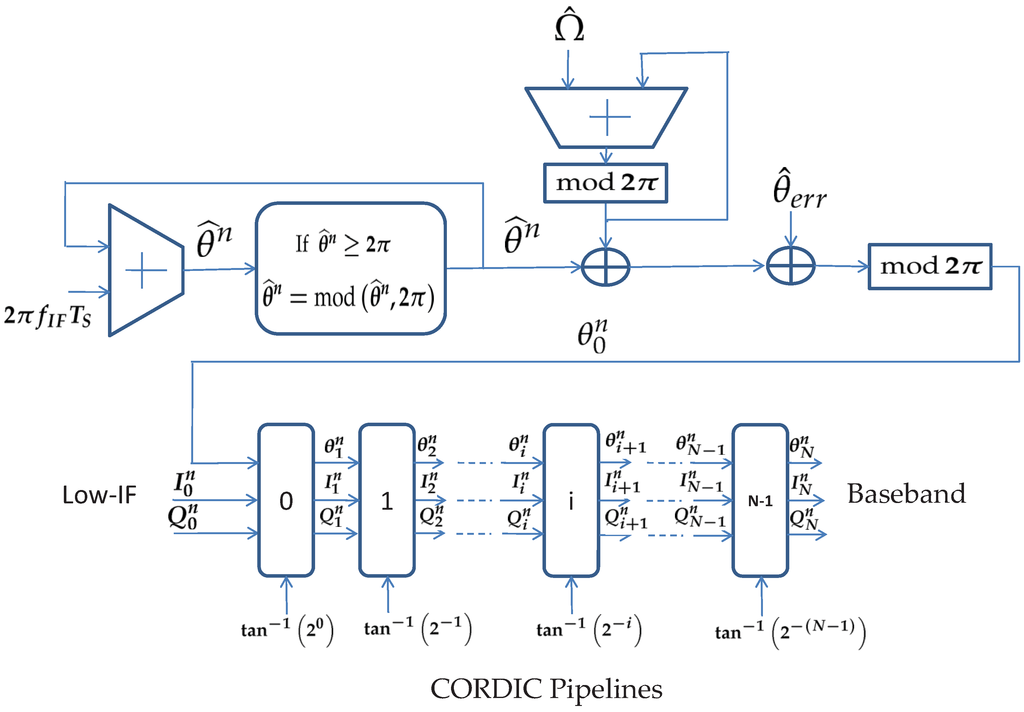

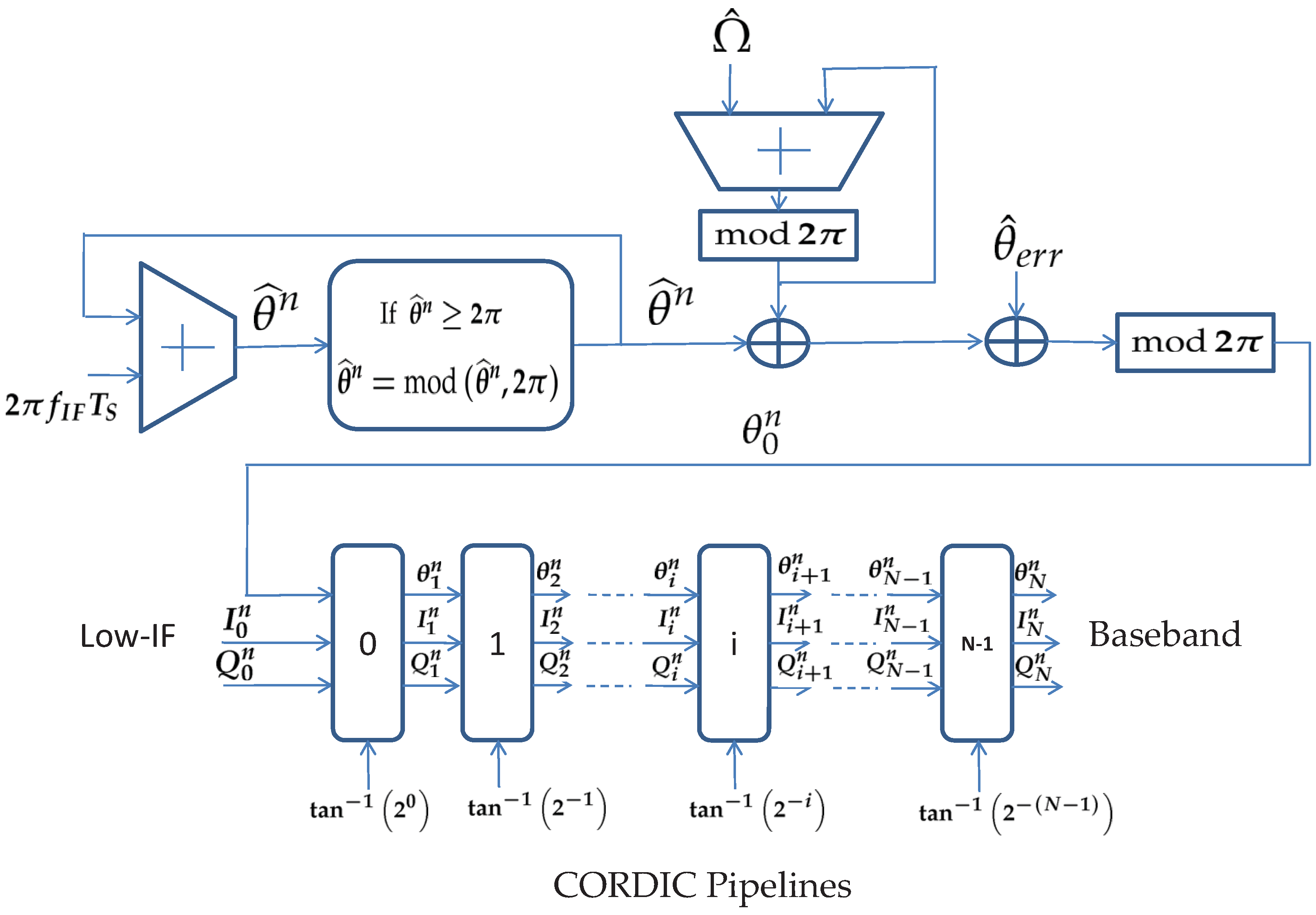

Figure 11.

Variable phase generation for CORDIC units. Such units are used in NCO to downconvert the IF signal to baseband, In interference estimators to down-convert interferences to baseband and in adaptive FIR unit to generate sinusoid coefficients. Input to this unit is only  , which is fed from LUT.

, which is fed from LUT.

, which is fed from LUT.

, which is fed from LUT.

Figure 11.

Variable phase generation for CORDIC units. Such units are used in NCO to downconvert the IF signal to baseband, In interference estimators to down-convert interferences to baseband and in adaptive FIR unit to generate sinusoid coefficients. Input to this unit is only  , which is fed from LUT.

, which is fed from LUT.

, which is fed from LUT.

, which is fed from LUT.

CORDIC is used in rotation mode to down-convert the signal from IF to baseband [21]. Change in sampling frequency requires variable phase generation for CORDIC unit. Figure 11 shows the variable phase generator for various CORDIC/NCO units mentioned above. Input to this block is sampling frequency provided by LUT. We have used 11 pipelined stage of CORDIC for IF to baseband conversion. The phase is represented by  bits. Number of pipeline stages and word length for phase representation are optimized based on analysis in [22], with the constraint that errors introduced by quantization in above two parameters should not corrupt a full length packet.

bits. Number of pipeline stages and word length for phase representation are optimized based on analysis in [22], with the constraint that errors introduced by quantization in above two parameters should not corrupt a full length packet.  is the estimated frequency error generated by FEE.

is the estimated frequency error generated by FEE.  is the phase error estimated by PhEE.

is the phase error estimated by PhEE.

bits. Number of pipeline stages and word length for phase representation are optimized based on analysis in [22], with the constraint that errors introduced by quantization in above two parameters should not corrupt a full length packet.

bits. Number of pipeline stages and word length for phase representation are optimized based on analysis in [22], with the constraint that errors introduced by quantization in above two parameters should not corrupt a full length packet.  is the estimated frequency error generated by FEE.

is the estimated frequency error generated by FEE.  is the phase error estimated by PhEE.

is the phase error estimated by PhEE.4.3. FIR Filter, Decimator and Demodulator

4.3.1. Adaptive FIR Filter

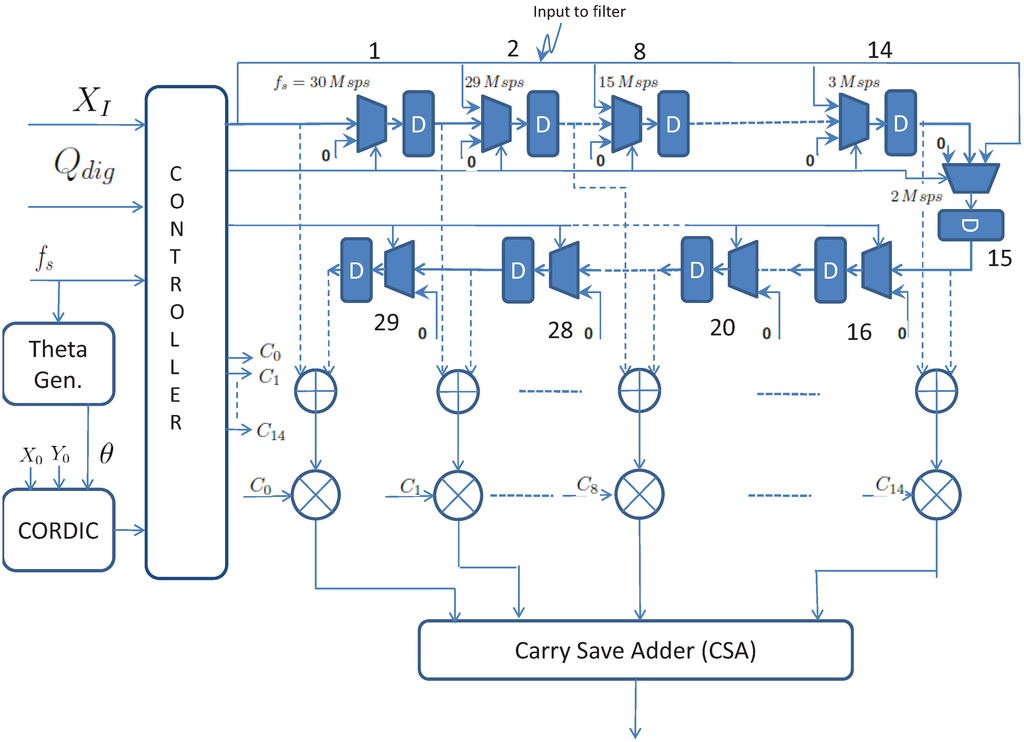

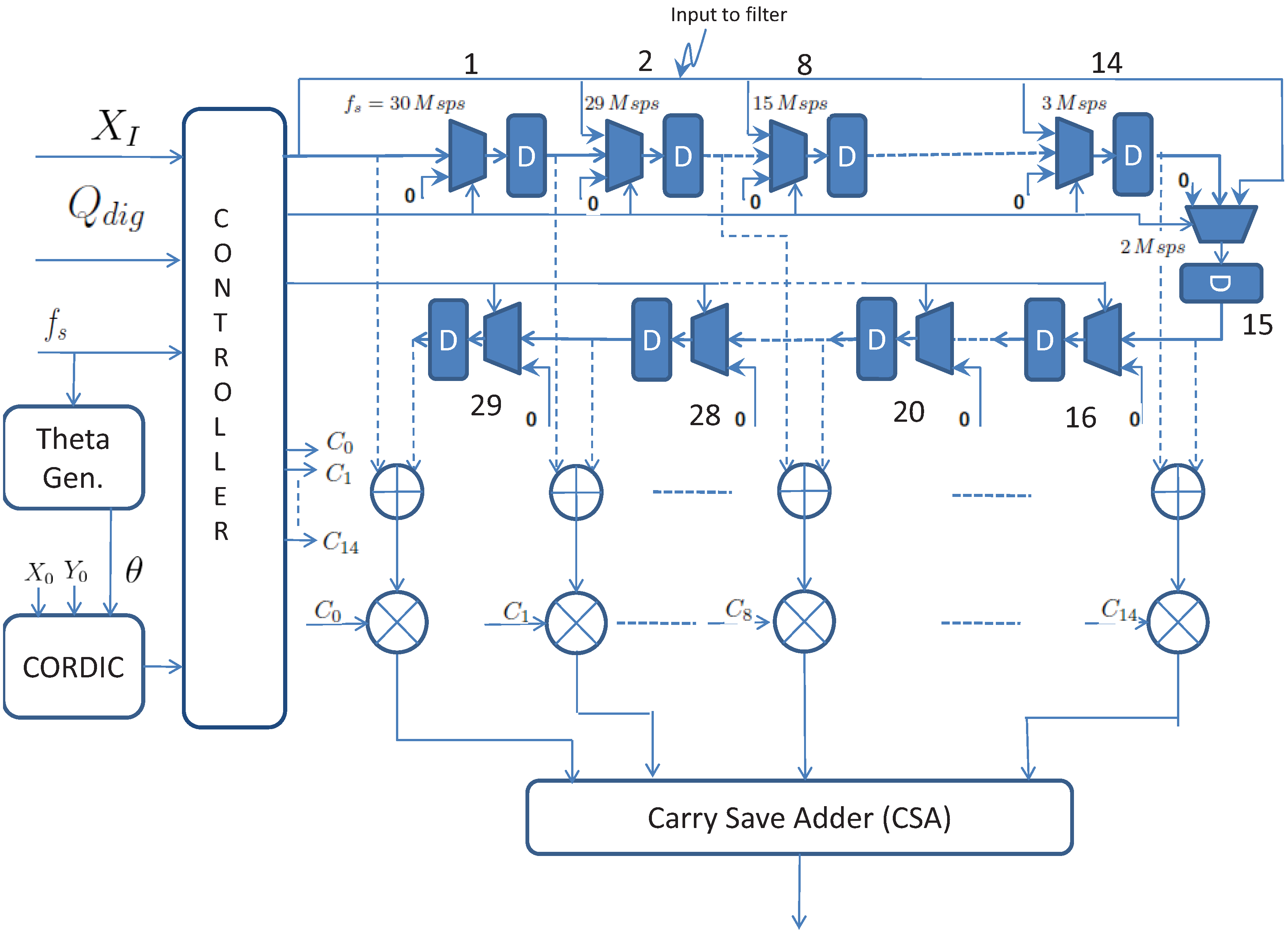

FIR filter in the receiver chain is a matched filter to the baseband half-sine pulse. Frequency response of the filter is shown in Figure 9(b). Figure 12 shows the structure of the adaptive FIR filter. As shown, the adaptive FIR structure has one CORDIC unit for coefficient generation, a theta generator for CORDIC unit, one central controller, and  taps (corresponding to maximum sampling frequency). The CORDIC unit generates FIR coefficients that are input to multipliers. The theta generator supplies phase values to CORDIC unit to generate coefficients. Generating FIR coefficients with CORDIC makes it more amenable to adaptive architecture. The phase values depend on

taps (corresponding to maximum sampling frequency). The CORDIC unit generates FIR coefficients that are input to multipliers. The theta generator supplies phase values to CORDIC unit to generate coefficients. Generating FIR coefficients with CORDIC makes it more amenable to adaptive architecture. The phase values depend on  . Resolution of coefficients are controlled based on

. Resolution of coefficients are controlled based on  .

.

taps (corresponding to maximum sampling frequency). The CORDIC unit generates FIR coefficients that are input to multipliers. The theta generator supplies phase values to CORDIC unit to generate coefficients. Generating FIR coefficients with CORDIC makes it more amenable to adaptive architecture. The phase values depend on

taps (corresponding to maximum sampling frequency). The CORDIC unit generates FIR coefficients that are input to multipliers. The theta generator supplies phase values to CORDIC unit to generate coefficients. Generating FIR coefficients with CORDIC makes it more amenable to adaptive architecture. The phase values depend on  . Resolution of coefficients are controlled based on

. Resolution of coefficients are controlled based on  .

.

Figure 12.

Adaptive FIR Filter. Controller controls the multiplexer to select which input to pass on to next delay element. A filter tap is deactivated by feeding a zero to its delay elements. Based on  controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

Figure 12.

Adaptive FIR Filter. Controller controls the multiplexer to select which input to pass on to next delay element. A filter tap is deactivated by feeding a zero to its delay elements. Based on  controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

controller controls the word length of FIR coefficients. Multipliers are Baugh–Wooley multipliers.

Tap coefficients are sampled half sinusoid. Frequency response of filter is shown in Figure 9(b). Since the tap coefficients are symmetric, the filter has folded architecture with number of taps equal to half of number of coefficients. Number of taps need to be adjusted with change in sampling frequency to keep it matched. Each tap in the filter consists of a multiplexed delay element, an adder and a multiplier. The multiplexer is a  multiplexer. Depending on the sampling frequency, either a zero or output of the preceding delay element or input to the FIR filter is multiplexed to the input of delay element. As shown in the figure, when the sampling frequency is

multiplexer. Depending on the sampling frequency, either a zero or output of the preceding delay element or input to the FIR filter is multiplexed to the input of delay element. As shown in the figure, when the sampling frequency is  Msps, delay elements numbered 14 and 15 are active and all other delay elements have zero inputs. Multipliers corresponding to inactive taps get zeros at its input and hence have no dynamic power. The carry save adder adds outputs of the multipliers.

Msps, delay elements numbered 14 and 15 are active and all other delay elements have zero inputs. Multipliers corresponding to inactive taps get zeros at its input and hence have no dynamic power. The carry save adder adds outputs of the multipliers.

multiplexer. Depending on the sampling frequency, either a zero or output of the preceding delay element or input to the FIR filter is multiplexed to the input of delay element. As shown in the figure, when the sampling frequency is

multiplexer. Depending on the sampling frequency, either a zero or output of the preceding delay element or input to the FIR filter is multiplexed to the input of delay element. As shown in the figure, when the sampling frequency is  Msps, delay elements numbered 14 and 15 are active and all other delay elements have zero inputs. Multipliers corresponding to inactive taps get zeros at its input and hence have no dynamic power. The carry save adder adds outputs of the multipliers.

Msps, delay elements numbered 14 and 15 are active and all other delay elements have zero inputs. Multipliers corresponding to inactive taps get zeros at its input and hence have no dynamic power. The carry save adder adds outputs of the multipliers.4.3.2. Decimator, Demodulator and Detector

Decimator in the data-path is an adaptive decimator. It decimates incoming samples depending on the sampling frequency. The demodulator is the 16-ary quasi orthogonal correlation demodulator. It correlates the incoming samples with the stored modulation symbols. Output of demodulator is 16 correlation values. The detector finds the maximum of these correlation values and declares it as the symbol arrived.

5. Implementation and Power Estimation

The design is coded in verilog HDL. Once pre-synthesis simulations are successful, RTL is synthesized for ASIC and FPGA implementation. The power estimation and comparison is done for ASIC implementation and design validation is done on FPGA platform. For power estimation, it is synthesized in  -nm UMC CMOS process for maximum sampling frequency of

-nm UMC CMOS process for maximum sampling frequency of  Msps using Synopsys Design Compiler. The power estimation is done once post synthesis simulation is successful. Synopsys Prime Power is used for estimating dynamic power. Input to Prime Power is the VCD (Value Change Dump) file generated from verilog simulation and the synthesized netlist. The VCD file contains all signal transition that occurred during the simulation. For generating VCD file, input to the simulator are the synthesized netlist, test vectors generated in MATLAB and SDF (Standard Delay Format) file used for synthesis.

Msps using Synopsys Design Compiler. The power estimation is done once post synthesis simulation is successful. Synopsys Prime Power is used for estimating dynamic power. Input to Prime Power is the VCD (Value Change Dump) file generated from verilog simulation and the synthesized netlist. The VCD file contains all signal transition that occurred during the simulation. For generating VCD file, input to the simulator are the synthesized netlist, test vectors generated in MATLAB and SDF (Standard Delay Format) file used for synthesis.

-nm UMC CMOS process for maximum sampling frequency of

-nm UMC CMOS process for maximum sampling frequency of  Msps using Synopsys Design Compiler. The power estimation is done once post synthesis simulation is successful. Synopsys Prime Power is used for estimating dynamic power. Input to Prime Power is the VCD (Value Change Dump) file generated from verilog simulation and the synthesized netlist. The VCD file contains all signal transition that occurred during the simulation. For generating VCD file, input to the simulator are the synthesized netlist, test vectors generated in MATLAB and SDF (Standard Delay Format) file used for synthesis.

Msps using Synopsys Design Compiler. The power estimation is done once post synthesis simulation is successful. Synopsys Prime Power is used for estimating dynamic power. Input to Prime Power is the VCD (Value Change Dump) file generated from verilog simulation and the synthesized netlist. The VCD file contains all signal transition that occurred during the simulation. For generating VCD file, input to the simulator are the synthesized netlist, test vectors generated in MATLAB and SDF (Standard Delay Format) file used for synthesis.

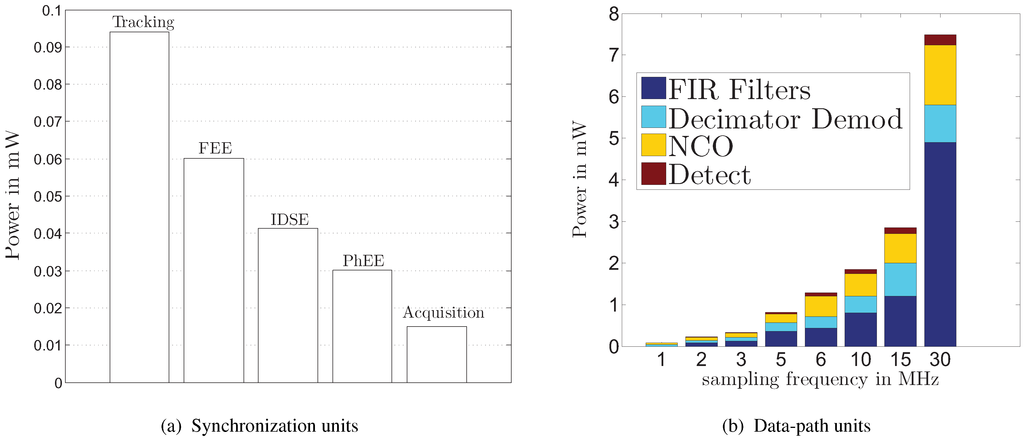

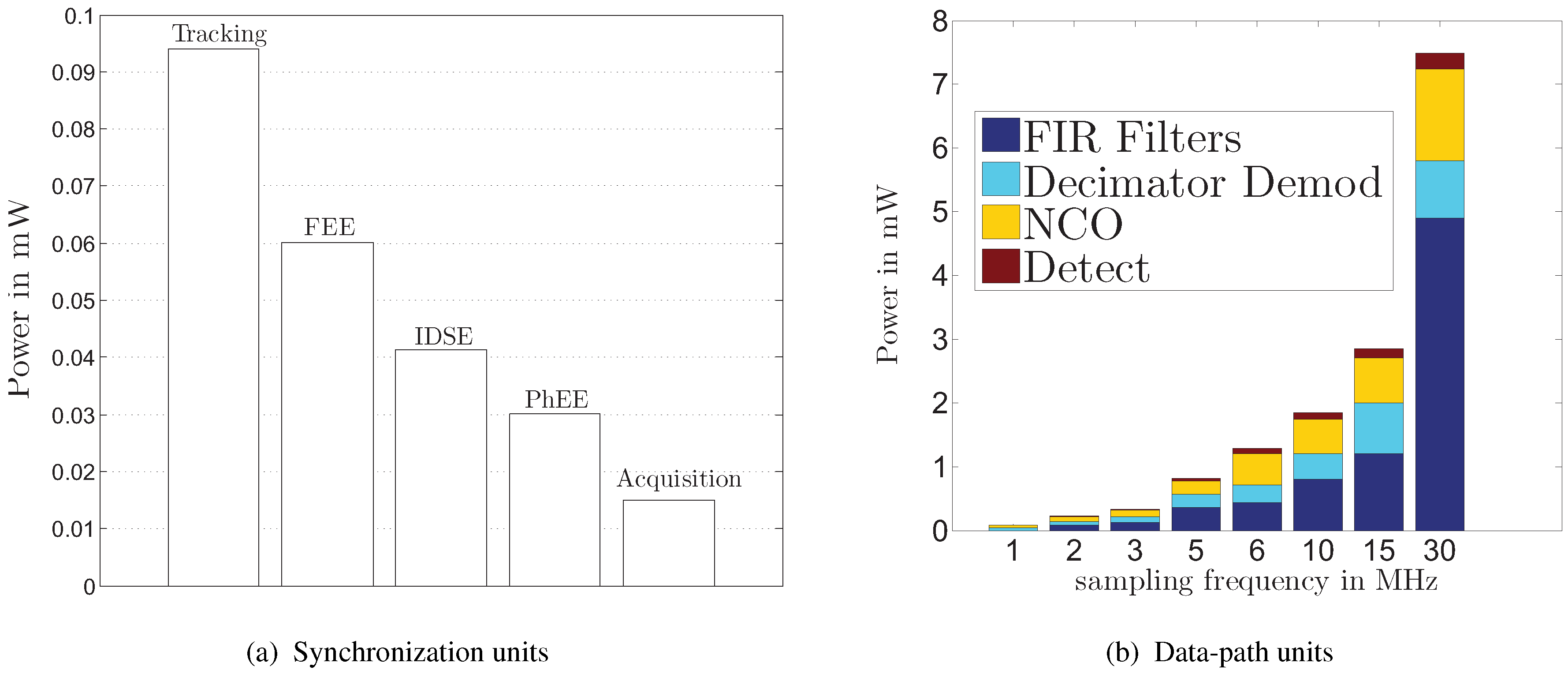

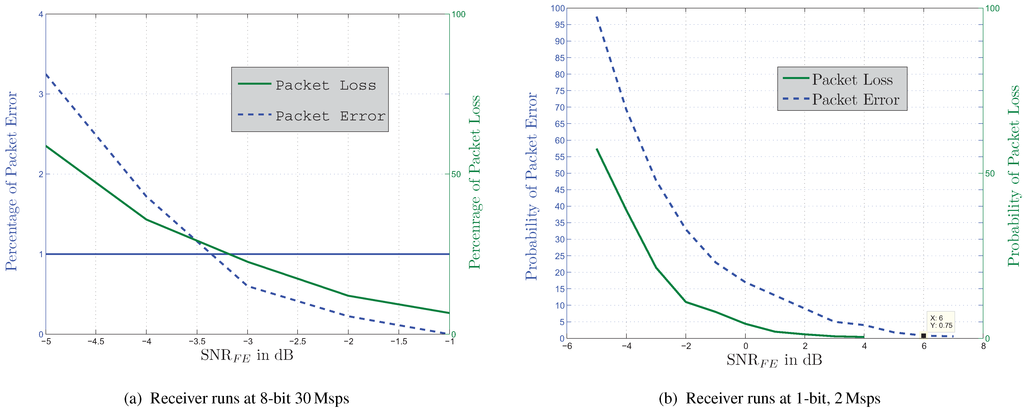

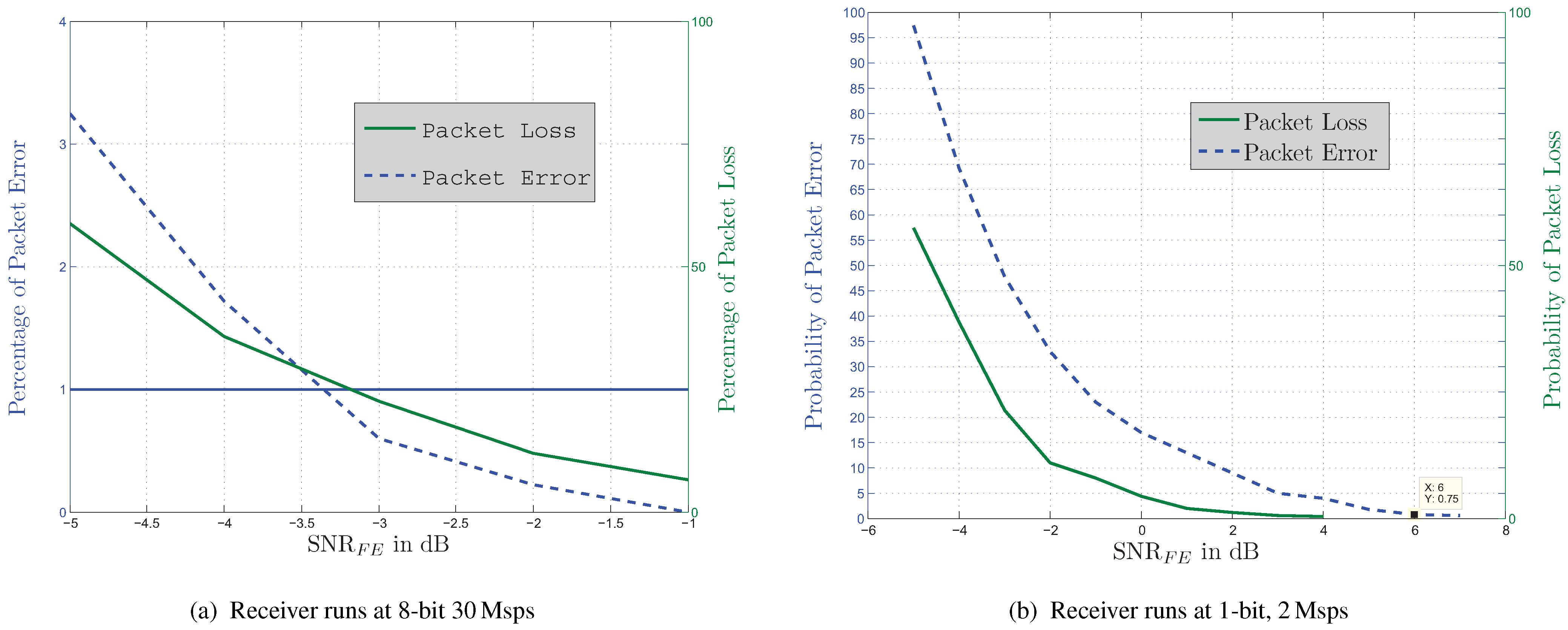

Figure 13.