An Ultra-Low-Power 0.8 V, 60 nW Temperature Sensor for Battery-Less Wireless Sensor Networks

Abstract

1. Introduction

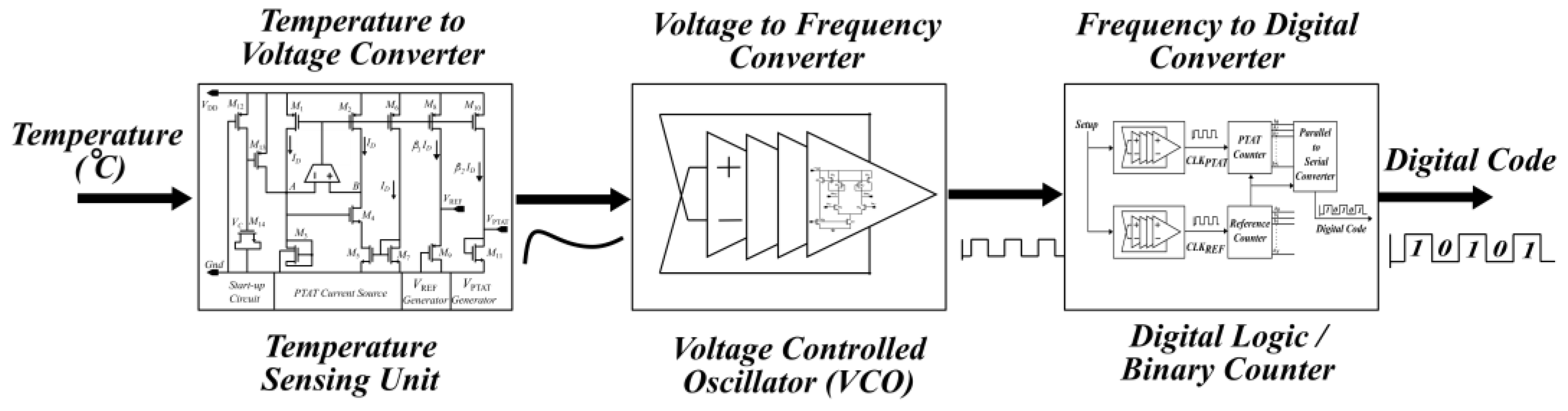

2. Architecture of the Proposed Temperature Sensor

2.1. Temperature Sensing Unit

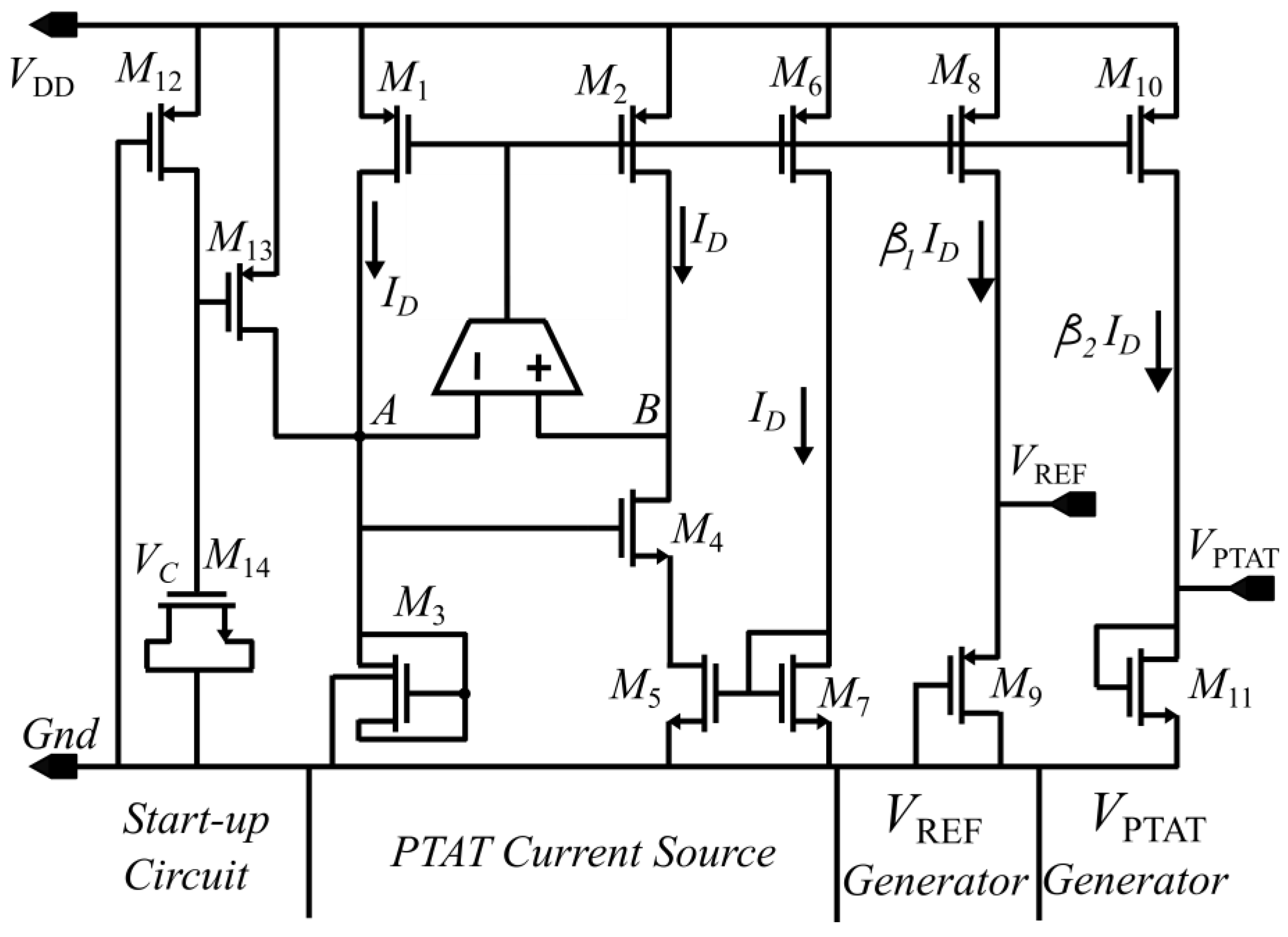

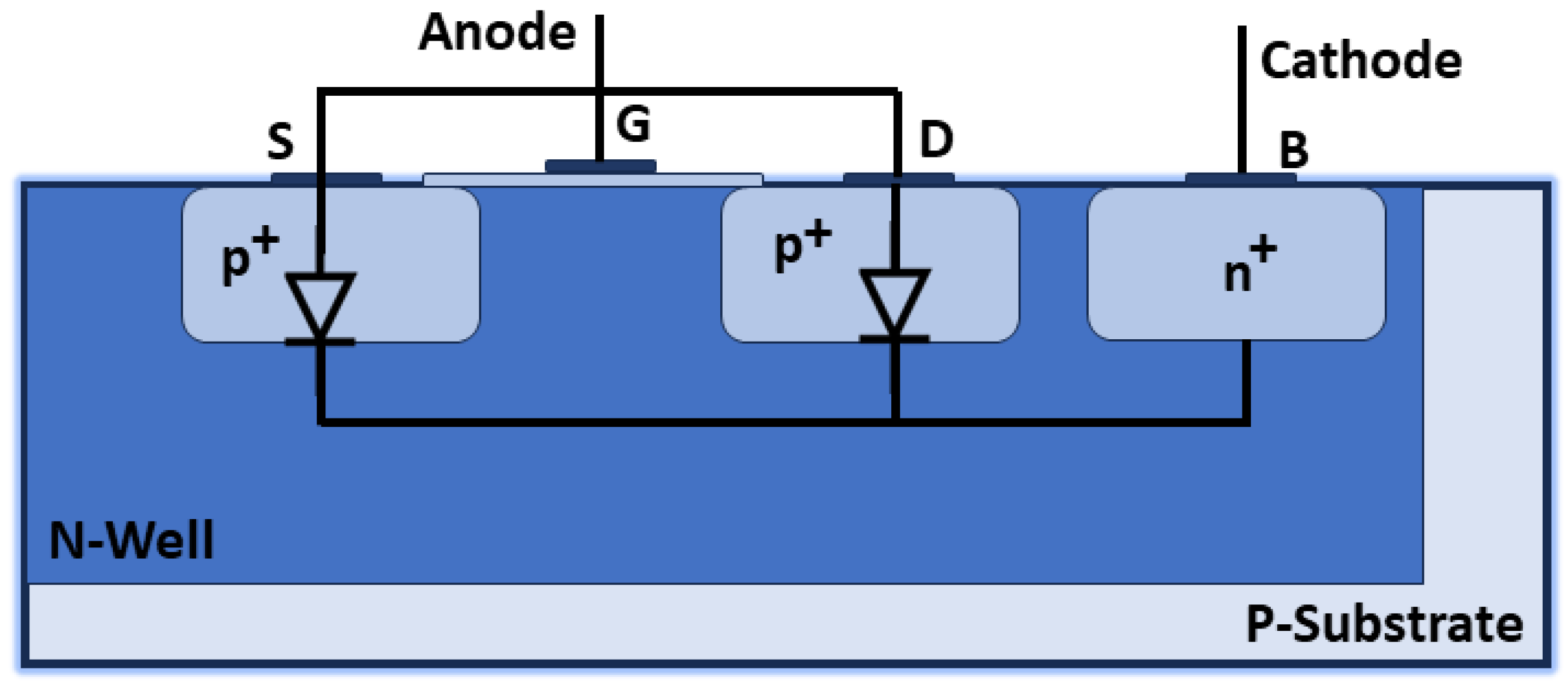

2.1.1. Temperature Sensing Circuit

2.1.2. Current Source Design

2.2. Voltage-to-Frequency Converter

2.3. Frequency-to-Digital Converter

3. Experimental Results

4. Integration with the Wireless Sensor Node

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Zrnić, M.; Spišić, J.; Pejković, A.; Grgić, K.; Balen, J.; Žagar, D. Low-Cost Wireless Sensor Node for Smart Agriculture Applications. In Proceedings of the 2021 16th International Conference on Telecommunications (ConTEL), Zagreb, Croatia, 30 June–2 July 2021. [Google Scholar]

- Satam, V.; Kulkarni, C.; Kholapure, A. Microstrip Antenna as a Temperature Sensor for IoT Applications. In Proceedings of the 2022 IEEE Microwaves, Antennas, and Propagation Conference (MAPCON), Bangalore, India, 12–16 December 2022. [Google Scholar]

- Sarkar, S.; Akshatha, K.S.; Saurabh, A.; Samanvitha, B.; Sarwar, M.F. IoT Enabled Cold Supply Chain Monitoring System. In Proceedings of the 2022 IEEE 3rd Global Conference for Advancement in Technology (GCAT), Bangalore, India, 7–9 October 2022. [Google Scholar]

- Chew, Z.J.; Ruan, T.; Zhu, M. Energy Harvesting Powered Wireless Sensor Nodes with Energy Efficient Network Joining Strategies. In Proceedings of the 2019 IEEE 17th International Conference on Industrial Informatics (INDIN), Helsinki, Finland, 22–25 July 2019. [Google Scholar]

- Shakya, A.S.; Kashyap, V.S. Temperature monitoring system with remote calibration capability. In Proceedings of the 2017 International Conference on Advances in Mechanical, Industrial, Automation and Management Systems (AMIAMS), Allahabad, India, 3–5 February 2017. [Google Scholar]

- Smart Temperature Sensor Survey. Available online: http://ei.ewi.tudelft.nl/docs/TSensor_survey.xls (accessed on 12 January 2023).

- Huang, Z.; Tang, Z.; Yu, X.P.; Shi, Z.; Lin, L.; Tan, N.N. A BJT-Based CMOS Temperature Sensor with Duty-Cycle-Modulated Output and ±0.5 °C (3σ) Inaccuracy From −40 °C to 125 °C. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2780–2784. [Google Scholar] [CrossRef]

- Qian, F.; Zhang, X.; Chen, Y.; Xi, J.; Zhu, Q.; He, L. A BJT-based SAR Temperature Sensor with a 5.12 pJ⋅K2 Resolution FoM from −40 °C to 125 °C. In Proceedings of the 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 21–25 May 2023. [Google Scholar]

- Qin, C.; Huang, Z.; Liu, Y.; Li, J.; Lin, L.; Tan, N.; Yu, X. An Energy-Efficient BJT-Based Temperature Sensor with ±0.8 °C (3σ) Inaccuracy from −50 to 150 °C. Sensors 2022, 22, 9381. [Google Scholar] [CrossRef]

- Pan, S.; Makinwa, K.A. A 0.25 mm2-Resistor-Based Temperature Sensor with an Inaccuracy of 0.12 °C (3σ) From −55 °C to 125 °C. IEEE J. Solid-State Circuits 2018, 53, 3347–3355. [Google Scholar] [CrossRef]

- Park, P.; Makinwa, K.A.A.; Ruffieux, D. A resistor-based temperature sensor for a real-time clock with ±2 ppm frequency stability. In Proceedings of the ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, Italy, 22–26 September 2014. [Google Scholar]

- Fan, S.; Zhao, L.; Wang, P.; Wei, R.; Zheng, X.Q.; Wang, Z.; Feng, P.X.L. A battery-less, 255 nA quiescent current temperature sensor with voltage regulator fully powered by harvesting ambient vibrational energy. In Proceedings of the 2017 IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Someya, T.; Islam, A.K.M.; Sakurai, T.; Takamiya, M. An 11-nW CMOS temperature-to-digital converter utilizing sub-threshold current at sub-thermal drain voltage. IEEE J. Solid-State Circuits 2019, 54, 613–622. [Google Scholar] [CrossRef]

- Li, J.; Lin, Y.; Ning, N.; Yu, Q. A +0.44 °C/−0.4 °C Inaccuracy Temperature Sensor with Multi-Threshold MOSFET-Based Sensing Element and CMOS Thyristor-Based VCO. IEEE Trans. Circuits Syst. I 2021, 68, 1102–1113. [Google Scholar] [CrossRef]

- Ku, C.-Y.; Liu, T.-T. A voltage-scalable low-power all-digital temperature sensor for on-chip thermal monitoring. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 1658–1662. [Google Scholar] [CrossRef]

- Tang, Z.; Tan, N.N.; Shi, Z.; Yu, X.-P. A 1.2V Self-Referenced Temperature Sensor with a Time-Domain Readout and a Two-Step Improvement on Output Dynamic Range. IEEE Sens. J. 2018, 18, 1849–1858. [Google Scholar] [CrossRef]

- Yousefzadeh, B.; Shalmany, S.H.; Makinwa, K.A.A. A BJT-Based Temperature-to-Digital Converter With ±60 mK (3σ) Inaccuracy From −55 °C to +125 °C in 0.16-µm CMOS. IEEE J. Solid-State Circuits 2017, 52, 1044–1052. [Google Scholar] [CrossRef]

- Rerkratn, A.; Prombut, S.; Kamsri, T.; Riewruja, V.; Petchmaneelumka, W. A Procedure for Precise Determination and Compensation of Lead-Wire Resistance of a Two-Wire Resistance Temperature Detector. Sensors 2022, 22, 4176. [Google Scholar] [CrossRef] [PubMed]

- Park, J.; Kim, J.; Kim, K.; Yang, J.-H.; Choi, M.; Shin, J. A 0.65 V 1316 μm2 fully synthesizable digital temperature sensor using wire metal achieving 0.16 nJ·%2-accuracy FoM in 5 nm FinFET CMOS. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), Gyeonggi, Republic of Korea, 20–26 February 2022. [Google Scholar]

- Seok, M.; Kim, G.; Blaauw, D.; Sylvester, D. A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 V. IEEE J. Solid-State Circuit 2012, 47, 2534–2545. [Google Scholar] [CrossRef]

- Jeong, S.; Foo, Z.; Lee, Y.; Sim, J.-Y.; Blaauw, D.; Sylvester, D. A Fully Integrated 71 nW CMOS Temperature Sensor for Low Power Wireless Sensor Nodes. IEEE J. Solid-State Circuits 2014, 49, 1682–1693. [Google Scholar] [CrossRef]

- Kussener, E.; Rudolff, F.; Guigues, F.; Barthelemy, H.; Liu, W.; Hu, J.; Ismail, M. 50 nA, 1 V nanowatt resistor-free compact CMOS current references. In Proceedings of the 2010 17th IEEE International Conference on Electronics, Circuits and Systems, Athens, Greece, 12–15 December 2010. [Google Scholar]

- Naveed; Dix, J. A Resistor-less, Nano-Watt CMOS Voltage Reference with High PSRR. In Proceedings of the 2021 22nd International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 7–9 April 2021. [Google Scholar]

- Tang, Z.; Fang, Y.; Shi, Z.; Yu, X.-P.; Tan, N.N.; Pan, W. A 1770 µm2 Leakage-Based Digital Temperature Sensor with Supply Sensitivity Suppression in 55-nm CMOS. IEEE J. Solid-State Circuits 2020, 55, 781–793. [Google Scholar] [CrossRef]

- Oguey, H.; Aebischer, D. CMOS current reference without resistance. IEEE J. Solid-State Circuits 1997, 32, 1132–1135. [Google Scholar] [CrossRef]

- Fakharyan, I.; Ehsanian, M.; Hayati, H. A 0.9-V supply, 16.2 nW, fully MOSFET resistorless bandgap reference using sub-threshold operation. Analog. Integr. Circuits Signal Process. 2020, 103, 367–374. [Google Scholar] [CrossRef]

- Colombo, D.; Werle, F.; Wirth, G.; Bampi, S. A CMOS 25.3 ppm/°C bandgap voltage reference using self-cascode composite transistor. In Proceedings of the 2012 IEEE 3rd Latin American Symposium on Circuits and Systems (LASCAS), Playa del Carmen, Mexico, 29 February–2 March 2012. [Google Scholar]

- Docking, S.; Sachdev, M. A method to derive an equation for the oscillation frequency of a ring oscillator. IEEE Trans. Circuits Syst. I 2003, 50, 259–264. [Google Scholar] [CrossRef]

- Li, J.; Yao, B.; Fan, L.; Zhang, T.; Zhang, Y.; Wu, K.; Zhang, Z.; Zhang, Q.; Wang, Y.; Ning, N.; et al. A 20 nW +0.8 °C/−0.8 °C Inaccuracy (3σ) Leakage-Based CMOS Temperature Sensor with Supply Sensitivity of 0.9 °C/V. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 3142–3153. [Google Scholar] [CrossRef]

- Zambrano, B.; Garzón, E.; Strangio, S.; Crupi, F.; Lanuzza, M. A 0.05 mm2, 350 mV, 14 nW Fully Integrated Temperature Sensor in 180-nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 2022, 69, 749–753. [Google Scholar] [CrossRef]

| This Work | TCAS-I’ 21 [14] | TCAS-I’ 23 [29] | TCAS-II’ 19 [15] | JSSC’ 19 [13] | TCAS-II’ 22 [30] | |

|---|---|---|---|---|---|---|

| Process (nm) | 65 | 130 | 180 | 180 | 180 | 180 |

| Type | MOSFET | MOSFET | MOSFET | MOSFET | MOSFET | MOSFET |

| Area (mm2) | 0.02 | 0.07 | 0.055 | 0.007 | 0.074 | 0.049 |

| Supply Range (V) | 0.8 | 0.95 | 1 | 0.6–1.2 | 0.8 | 0.35 |

| Temperature Range (°C) | −20–120 | 0–80 | 0–100 | 0–100 | −20–80 | 0–100 |

| Resolution (°C−1) | 0.2 | 0.1 | 0.12 | 0.55 | 0.14 | 0.27 |

| Conversion Time (ms) | 9.2 ms | 59 ms | 50 ms | 300 ms | 839 ms | 33 ms |

| Calibration Points | 2 | 2 | 2 | 2 | 2 | 2 |

| Error (°C) | +1.5/ −1.6 | +0.44/ −0.4 | +0.8/−0.8 | +0.67/ −1.64 | +1.2/ −0.9 | +3/ −3 |

| Fully Integrated | yes | yes | Yes | yes | yes | yes |

| Power (nW) | 60 | 196 | 20 | 3.92 | 11 | 14 |

| Energy per Conversion (nJ) | 0.55 | 11.56 | 1.0 | 1.2 | 8.9 | 0.46 |

| FOM [nJ·K2] | 0.022 | 0.12 | 0.014 | 0.36 | 0.19 | 0.034 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Naveed; Dix, J. An Ultra-Low-Power 0.8 V, 60 nW Temperature Sensor for Battery-Less Wireless Sensor Networks. J. Low Power Electron. Appl. 2025, 15, 1. https://doi.org/10.3390/jlpea15010001

Naveed, Dix J. An Ultra-Low-Power 0.8 V, 60 nW Temperature Sensor for Battery-Less Wireless Sensor Networks. Journal of Low Power Electronics and Applications. 2025; 15(1):1. https://doi.org/10.3390/jlpea15010001

Chicago/Turabian StyleNaveed, and Jeff Dix. 2025. "An Ultra-Low-Power 0.8 V, 60 nW Temperature Sensor for Battery-Less Wireless Sensor Networks" Journal of Low Power Electronics and Applications 15, no. 1: 1. https://doi.org/10.3390/jlpea15010001

APA StyleNaveed, & Dix, J. (2025). An Ultra-Low-Power 0.8 V, 60 nW Temperature Sensor for Battery-Less Wireless Sensor Networks. Journal of Low Power Electronics and Applications, 15(1), 1. https://doi.org/10.3390/jlpea15010001