A Scalable Formal Framework for the Verification and Vulnerability Analysis of Redundancy-Based Error-Resilient Null Convention Logic Asynchronous Circuits

Abstract

1. Introduction

- Development of a formal verification framework for redundancy based QDI NCL circuits: Over the past two decades, several automated synthesis schemes have been developed for different QDI paradigms, including NCL. NCL circuits are typically synthesized from their synchronous/Boolean specifications utilizing synchronous CAD tools [8,9,10,11,12]. During the synthesis procedure, the circuits undergo numerous transformations. As a result, the synthesized NCL structures differ significantly from their synchronous specifications. A few formal verification methods have also been developed to verify the safety (functional correctness) and liveness (deadlock-free operation) of the synthesized NCL circuits [13,14,15]. However, these formal methods are only applicable to conventional NCL architectures. In addition, the majority of the existing verification schemes suffer from scalability issues due to the highly non-deterministic nature of NCL circuits. Redundancy-based error-resilient NCL circuits are more complex than conventional NCL circuits due to the presence of multiple circuit copies, additional logic components to maintain interdependency between multiple copies, and a more complex handshaking network. To resolve these issues, we propose a structural abstraction-based scalable formal verification methodology for a redundancy-based NCL resiliency scheme known as the dual-modular redundancy-based NCL (DMR-NCL) architecture. The salient aspect of the proposed verification scheme is its versatility, as it can be implemented either as an independent verification tool or integrated into an existing synthesis tool. Moreover, the method can be tailored to be applicable to existing redundancy-based SCL and PCHB architectures.

- Development of a formal framework for vulnerability analysis during error scenarios: The majority of the existing resilient QDI schemes test for circuit vulnerabilities and recovery procedures in the presence of soft errors through extensive simulation. However, simulation alone cannot guarantee complete resilience. Formal methods have been shown to be more effective at covering corner-case scenarios, which simulations fail to detect. Our second contribution is the development of a formal framework for analyzing the vulnerability of the synthesized DMR-NCL circuits, which verifies whether the circuit can recover from a SEU/SEL without causing incorrect output or deadlock. Both the proposed verification and vulnerability analysis methodologies have been demonstrated on multiple DMR-NCL combinational benchmark circuits of varying sizes and complexities.

2. Background and Related Work

2.1. NCL Framework: An Overview

2.2. Error-Resilient QDI Architectures

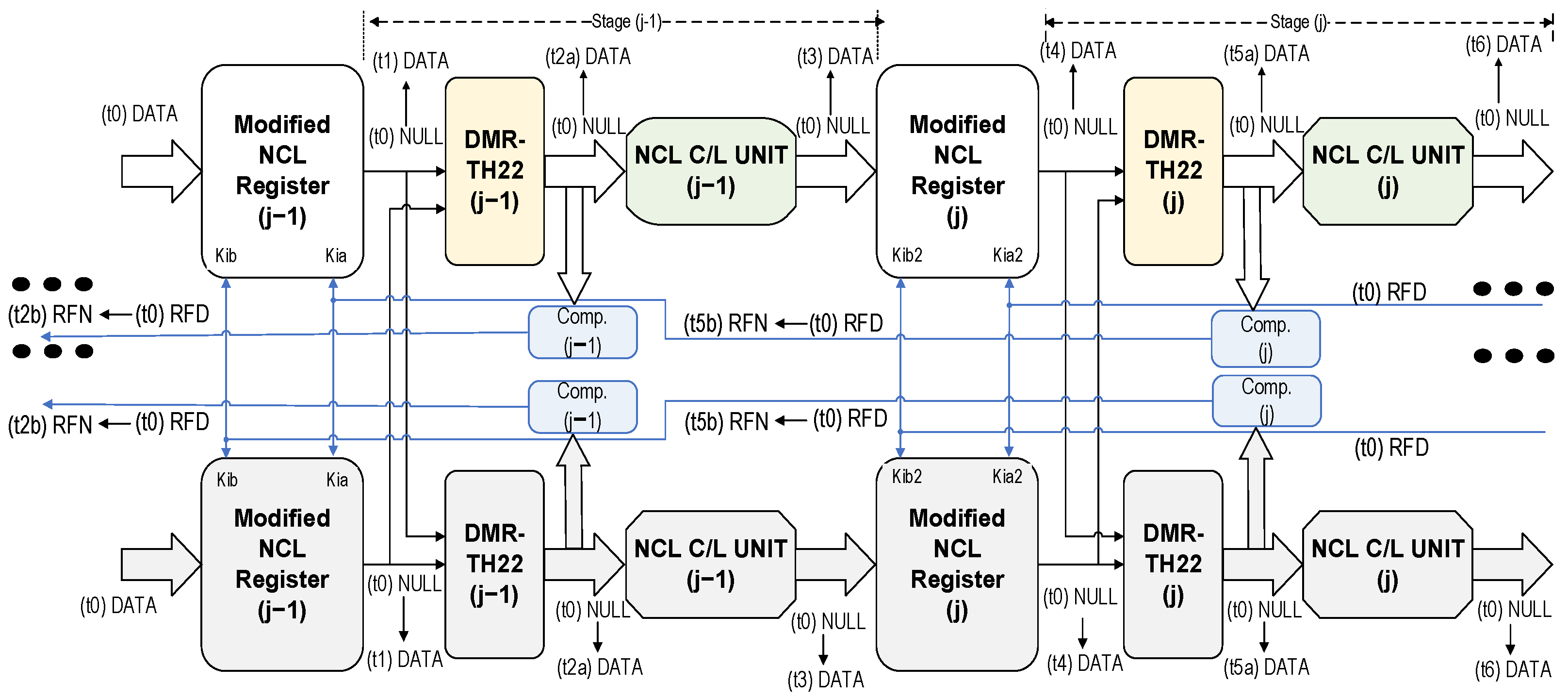

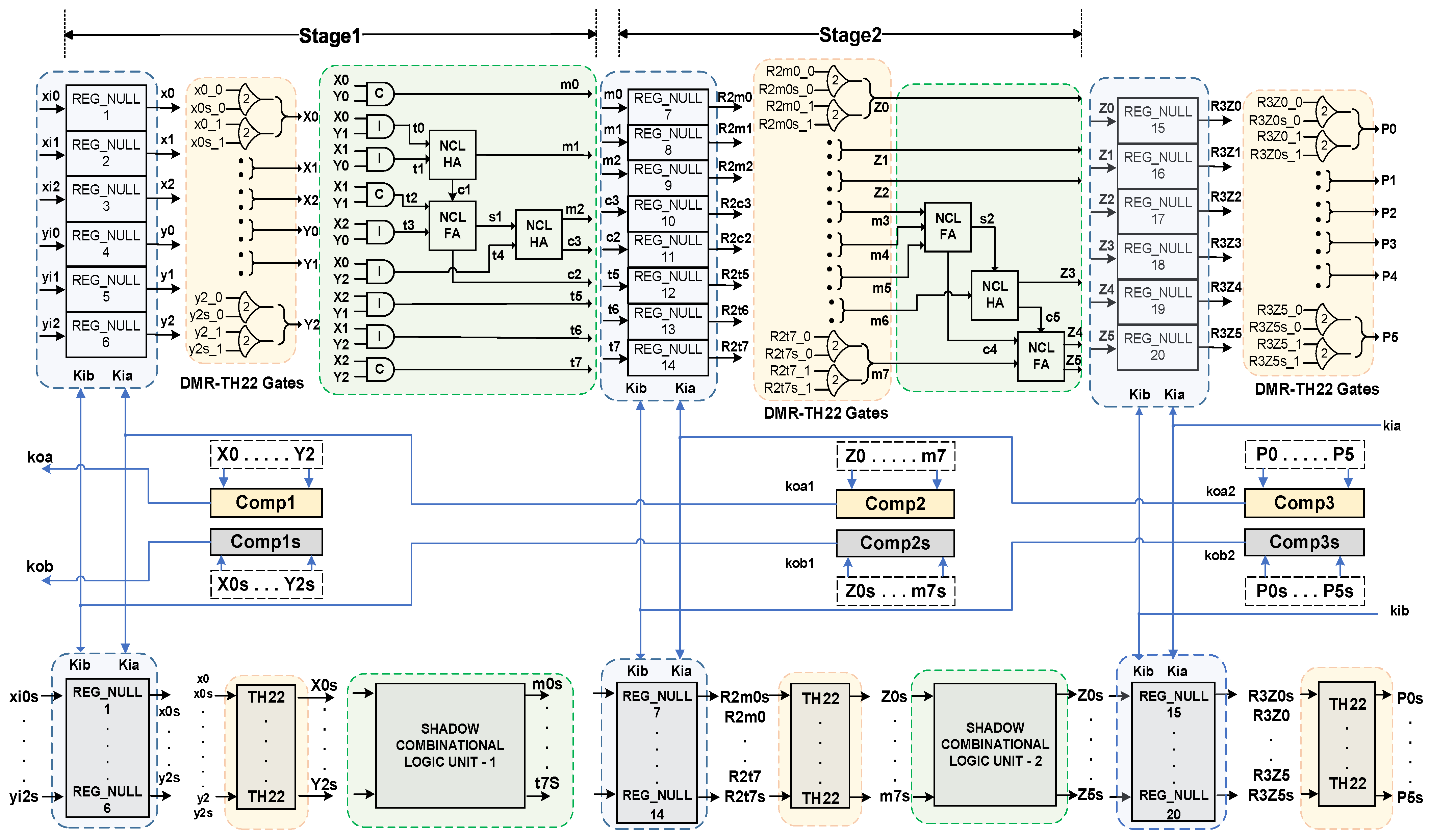

2.3. Dual Modular Redundancy (DMR)-Based NCL (DMR-NCL) Architecture

3. Proposed Formal Framework for the Verification and Vulnerability Analysis of DMR-NCL Architecture

3.1. Comprehensive Set of Possible DMR-NCL Synthesis Faults: A Case Study

3.2. Proposed Safety Check

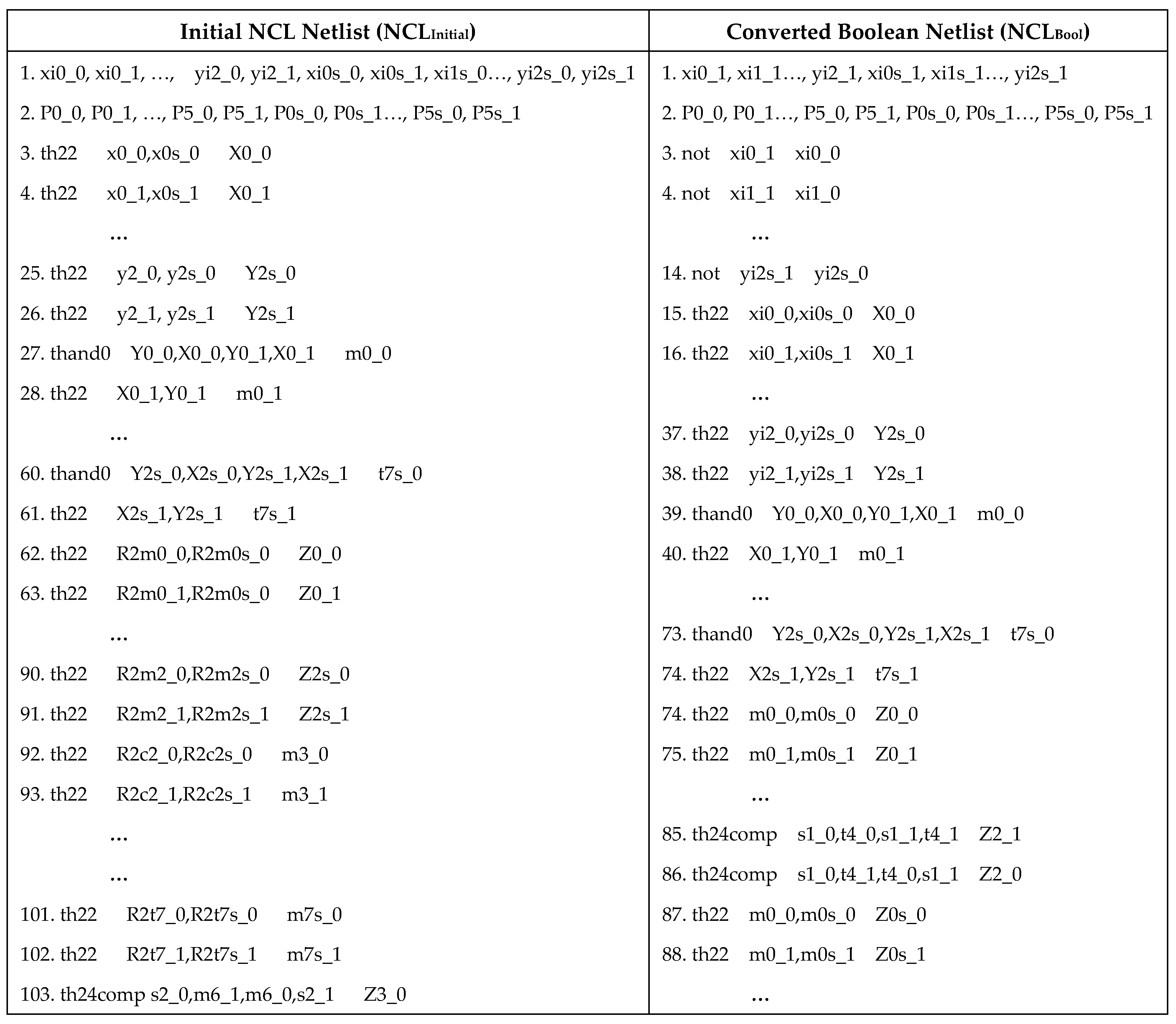

3.2.1. Functional Equivalence Check

| Algorithm 1: Procedure to generate an equivalent Boolean circuit from a DMR-NCL circuit |

| //Input to the procedure: NCLInitial; Output of the procedure NCLBool// 1: Create list_pIs (rail1.data_inputs(NCLInitial)) 2: Create list_pOs (data_outputs(NCLInitial)) 3: Create NCL_comp (NCLInitial) 4: for i← to component_count do 5: if NCL_comp(i).instance_type == Reg_NULL then 6: merge NCL gates separated by NCL_comp(i) 7: delete NCL_comp(i) 8: end if 9: end for 10: for i← to component_count do 11: if NCL_comp(i).instance_type == Comp then 12: delete NCL_comp(i) 13: end if 14: end for 15: for j← to list_pIs do 16: generate_rail0_signals (list_pIs(j)) 17: end for 18: for i← to component_count do 19: convert_to_Boolean (NCL_comp(i)) 20: end for |

3.2.2. Invariant Check for Verifying the rail0 Network

3.3. Proposed Liveness Check and Handshaking Connection Verification

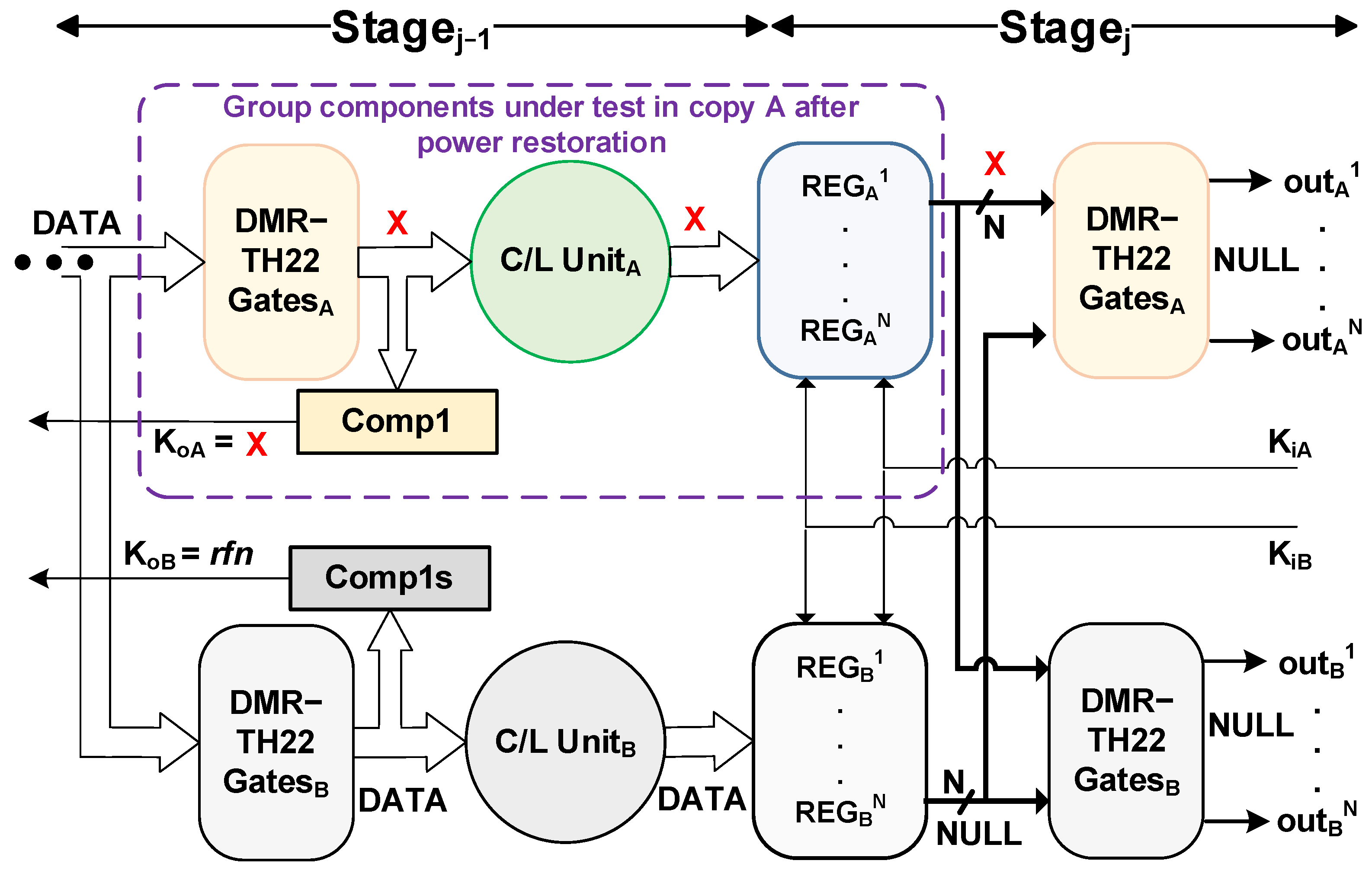

4. Proposed Vulnerability Analysis Framework: SEL/SEU Will Not Cause Incorrect Outputs and/or Deadlock

5. Results and Discussions

5.1. Verification Results

5.2. Detection of All Possible Synthesis Faults

5.3. Vulnerability Analysis Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Di, J.; Smith, S.C. (Eds.) Asynchronous Circuit Applications; IET: Stevenage, UK, December 2019; Available online: https://digital-library.theiet.org/content/books/cs/pbcs061e (accessed on 1 November 2023).

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Shoga, M.; Binder, D. Theory of single event latchup in complementary metal oxide semiconductor circuits. IEEE Trans. Nucl. Sci. 1986, NS-33, 1714–1717. [Google Scholar] [CrossRef]

- Sakib, A.A. Soft error tolerant quasi-delay insensitive asynchronous circuits: Advancements and challenges. In Proceedings of the 34th SBC/SBMicro/IEEE/ACM Symposium on Integrated Circuits and Systems Design (SBCCI), Campinas, Brazil, 23–27 August 2021; pp. 1–6. [Google Scholar] [CrossRef]

- Fant, K.M.; Brandt, S.A. Null convention logic: A complete and consistent logic for asynchronous digital circuit synthesis. In Proceedings of the International Conference on Application Specific Systems, Architectures and Processors: ASAP’96, Chicago, IL, USA, 19–21 August 1996; pp. 261–273. [Google Scholar]

- Martin, A.J.; Nystrom, M. Asynchronous Techniques for System-on-Chip Design. Proc. IEEE 2006, 94, 1089–1120. [Google Scholar] [CrossRef]

- Zhou, L.; Parameswaran, R.; Parsan, F.; Smith, S.; Di, J. Multi-Threshold NULL Convention Logic (MTNCL): An Ultra-Low Power Asynchronous Circuit Design Methodology. J. Low Power Electron. Appl. 2015, 5, 81–100. [Google Scholar] [CrossRef]

- Ligthart, M.; Fant, K.; Smith, R.; Taubin, A.; Kondratyev, A. Asynchronous design using commercial HDL synthesis tools. In Proceedings of the Sixth International Symposium on Advanced Research in Asynchronous Circuits and System, Eilat, Israel, 2–6 April 2000; pp. 114–125. [Google Scholar] [CrossRef]

- Kondratyev, A.; Lwin, K. Design of asynchronous circuits using synchronous CAD tools. IEEE Des. Test Comput. 2002, 19, 107–117. [Google Scholar] [CrossRef]

- Zhou, Y.; Sokolov, D.; Yakovlev, A. Cost-aware synthesis of asynchronous circuits based on partial acknowledgement. In Proceedings of the IEEE/ACM International Conference on Computer Aided Design, San Jose, CA, USA, 5–9 November 2006; pp. 158–163. [Google Scholar]

- Reese, R.B.; Smith, S.C.; Thornton, M.A. Uncle—An RTL approach to asynchronous design. In Proceedings of the IEEE 18th International Symposium on Asynchronous Circuits and Systems, Kgs, Lyngby, Denmark, 7–9 May 2012; pp. 65–72. [Google Scholar] [CrossRef]

- Khodosevych, D.; Sakib, A.A. Evolution of NULL convention logic based asynchronous paradigm: An overview and outlook. IEEE Access 2022, 10, 78650–78666. [Google Scholar] [CrossRef]

- Sakib, A.A.; Le, S.; Smith, S.C.; Srinivasan, S.K. Formal verification of NCL circuits. In Asynchronous Circuit Applications; IET: Stevenage, UK, 2018; pp. 309–338. Available online: https://digital-library.theiet.org/content/books/10.1049/pbcs061e_ch15 (accessed on 1 November 2023).

- Wijayasekara, V.; Srinivasan, S.K.; Smith, S.C. Equivalence verification for NULL convention logic (NCL) circuits. In Proceedings of the 32nd IEEE International Conference on Computer Design (ICCD), Seoul, Republic of Korea, 19–22 October 2014; pp. 195–201. [Google Scholar]

- Wijayasekara, V.M.; Rollie, A.T.; Hodges, R.G.; Srinivasan, S.K.; Smith, S.C. Abstraction techniques to improve scalability of equivalence verification for NCL circuits. Electron. Lett. 2016, 52, 1594–1596. [Google Scholar] [CrossRef]

- Smith, S.C.; Di, J. Designing Asynchronous Circuits Using NULL Convention Logic (NCL); Morgan & Claypool: San Rafael, CA, USA, 2009. [Google Scholar]

- Seitz, C.L. System Timing. In Introduction to VLSI Systems; Addison-Wesley: Reading, MA, USA, 1980; pp. 218–262. [Google Scholar]

- Lyons, R.E.; Vanderkulk, W. The use of triple-modular redundancy to improve computer reliability. IBM J. Res. Dev. 1962, 6, 200–209. [Google Scholar] [CrossRef]

- Monnet, Y.; Renaudin, M.; Leveugle, R. Asynchronous circuits sensitivity to fault injection. In Proceedings of the 10th IEEE International Online Testing Symposium, Funchal, Portugal, 14 July 2004; pp. 121–126. [Google Scholar]

- Kuang, W.; Zhao, P.; Yuan, J.S.; DeMara, R.F. Design of asynchronous circuits for high soft error tolerance in deep submicrometer CMOS circuits. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 2010, 18, 410–422. [Google Scholar] [CrossRef]

- Gardiner, K.T.; Yakovlev, A.; Bystrov, A. A C-element latch scheme with increased transient fault tolerance for asynchronous circuits. In Proceedings of the 13th IEEE International On-Line Testing Symposium (IOLTS 2007), Heraklion, Greece, 8–11 July 2007; pp. 223–230. [Google Scholar] [CrossRef]

- Lodhi, F.K.; Hasan, O.; Hasan, S.R.; Awwad, F. Modified null convention logic pipeline to detect soft errors in both null and data phases. In Proceedings of the IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, USA, 5–8 August 2012; pp. 402–405. [Google Scholar] [CrossRef]

- Lodhi, F.K.; Hasan, S.R.; Hasan, O.; Awwad, F. Analyzing vulnerability of asynchronous pipeline to soft errors: Leveraging formal verification. J. Electron. Test. 2016, 32, 569–586. [Google Scholar] [CrossRef]

- Zhou, L.; Smith, S.; Di, J. Radiation Hardened NULL Convention Logic Asynchronous Circuit Design. J. Low Power Electron. Appl. 2015, 5, 216–233. [Google Scholar] [CrossRef]

- Brady, J.D. Radiation-Hardened Delay-Insensitive Asynchronous Circuits for Multi-Bit SEU Mitigation and Data Retaining SEL Protection; University of Arkansas: Fayetteville, AR, USA, 2014. [Google Scholar]

- Datta, M.; Bodoh, A.; Sakib, A.A. Error Resilient Sleep Convention Logic Asynchronous Circuit Design. In Proceedings of the 2023 21st IEEE Interregional NEWCAS Conference (NEWCAS), Edinburgh, UK, 26–28 June 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Jang, W.; Martin, A.J. A soft-error-tolerant asynchronous microcontroller. In 13th NASA Symposium on VLSI Design; Citeseer: University Park, PA, USA, 2007. [Google Scholar]

- Jang, W.; Martin, A.J. SEU-tolerant QDI circuits [quasi delay-insensitive asynchronous circuits]. In Proceedings of the 11th IEEE International Symposium on Asynchronous Circuits and Systems, New York, NY, USA, 14–16 March 2005; pp. 156–165. [Google Scholar] [CrossRef]

- Jang, W.; Martin, A.J. Soft-Error Tolerant Asynchronous FPGA. In Proceedings of the Dependable System and Network 2005, Rio de Janeiro, Brazil, 22–25 June 2005. [Google Scholar]

- Santos, I. Asynchronous Logic Design with Increased Fault Tolerance and Optimized for Subthreshold Operation; The University of Texas at El Paso: El Paso, TX, USA, 2013. [Google Scholar]

- Jeong, C.; Nowick, S.M. Optimization of robust asynchronous circuits by local input completeness relaxation. In Proceedings of the Asia South Pacific Design Automation Conference, Yokohama, Japan, 23–26 January 2007; pp. 622–627. [Google Scholar]

- Jeong, C.; Nowick, S.M. Block-level relaxation for timing-robust asynchronous circuits based on eager evaluation. In Proceedings of the 14th IEEE International Symposium on Asynchronous Circuits and Systems, Newcastle Upon Tyne, UK, 7–10 April 2008; pp. 95–104. [Google Scholar] [CrossRef]

- Khodosevych, D.; Bodoh, A.C.; Sakib, A.A.; Smith, S.C. Combining relaxation with NCL_X for enhanced optimization of asynchronous NULL convention logic circuits. IEEE Access 2023, 11, 104688–104699. [Google Scholar] [CrossRef]

- Toms, W.B.; Edwards, D.A. A complete synthesis method for block level relaxation in self-timed datapaths. In Proceedings of the 2010 10th International Conference on Application of Concurrency to System Design, Braga, Portugal, 21–25 June 2010; pp. 24–34. [Google Scholar] [CrossRef]

- Sakib, A.A.; Smith, S.C.; Srinivasan, S.K. Formal modeling and verification of PCHB asynchronous circuits. IEEE Trans. Very Large-Scale Integr. (VLSI) Syst. 2019, 27, 2911–2924. [Google Scholar] [CrossRef]

- Le, S.; Srinivasan, S.K.; Smith, S.C. Automated verification of input completeness for NCL circuits. Electron. Lett. 2018, 54, 1158–1160. [Google Scholar] [CrossRef]

- Muller, D.E. Asynchronous logics and application to information processing. In Switching Theory in Space Technology; Stanford University Press: Redwood City, CA, USA, 1963; pp. 289–297. [Google Scholar]

- Monniaux, D. A Survey of Satisfiability Modulo Theory. Available online: https://hal.archives-ouvertes.fr/hal-01332051/document (accessed on 10 September 2023).

- Barrett, C.; Fontaine, P.; Tinelli, C. The SMT-LIB Standard: Version 2.6. Tech. Rep.; Department of Computer Science, The University of Iowa: Iowa City, IA, USA, 2017; Available online: www.SMT-LIB.org (accessed on 10 September 2023).

- de Moura, L.; Bjørner, N. Z3: An efficient SMT solver. In Tools and Algorithms for the Construction and Analysis of Systems (Lecture Notes in Computer Science); Ramakrishnan, C.R., Rehof, J., Eds.; Springer: Berlin/Heidelberg, Germany, 2008; pp. 337–340. [Google Scholar]

| Circuits | Verification Time of Different Procedures | Total Verification | |

|---|---|---|---|

| Safety Check (s) | Liveness and Additional Checks (s) | Time (s) | |

| Test Circuits without Bugs | |||

| 3 × 3 Mult | 0.06 | 0.0155 | 0.0755 |

| 4 × 4 Mult | 0.44 | 0.0157 | 0.4557 |

| 6 × 6 Mult | 1.03 | 0.0158 | 1.0458 |

| 8 × 8 Mult | 14.48 | 0.0159 | 14.4959 |

| 9 × 9 Mult | 128.06 | 0.0312 | 128.0912 |

| 10 × 10 Mult | 1187.59 | 0.0336 | 1187.6236 |

| Test Circuits with Injected Bugs | |||

| B1 − 10 Mult | 296.65 (B) | 0.0336 | 296.774 |

| B2 − 10 Mult | 1.19 (B) | 0.0336 | 1.224 |

| B3 − 10 Mult | 296.88 (B) | 0.0336 | 296.914 |

| B4 − 10 Mult | 1.48 (B) | 0.0336 | 1.514 |

| B5 − 10 Mult | Is detected during Netlist Processing | 0.1220 (B) | --- |

| B6 − 10 Mult | Is Detected during Netlist Processing | ||

| B7 − 10 Mult | 1.55 (B) | 0.0312 (B) | 1.581 |

| B8 − 10 Mult | 1.61 (B) | 0.029 (B) | 1.639 |

| B9 − 10 Mult | 1187.59 | 0.03 (B) | 1187.620 |

| B10 − 10 Mult | 1187.59 | 0.0279 (B) | 1187.618 |

| B11 − 10 Mult | Is Detected during Netlist Processing | ||

| B12 − 10 Mult | Is Detected during Netlist Processing | ||

| B13 − 10 Mult | 1187.59 | 0.0359 (B) | 1187.626 |

| B14 − 10 Mult | 1187.59 | 0.031 (B) | 1187.621 |

| B15 − 10 Mult | 1187.59 | 0.0331 (B) | 1187.623 |

| B16 − 10 Mult | 1.35 (B) | 0.026 (B) | 1.376 |

| B18(i) − 10 Mult | 2.39 (B) | 0.034 (B) | 2.424 |

| B18(ii) − 10 Mult | 1187.59 | 0.0342 (B) | 1187.624 |

| Circuits | Vulnerability Analysis (s) |

|---|---|

| 3 × 3 Mult | 0.04 |

| 4 × 4 Mult | 0.12 |

| 6 × 6 Mult | 1.11 |

| 8 × 8 Mult | 13.54 |

| 9 × 9 Mult | 85.52 |

| 10 × 10 Mult | 257.41 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mazumder, D.; Datta, M.; Bodoh, A.C.; Sakib, A.A. A Scalable Formal Framework for the Verification and Vulnerability Analysis of Redundancy-Based Error-Resilient Null Convention Logic Asynchronous Circuits. J. Low Power Electron. Appl. 2024, 14, 5. https://doi.org/10.3390/jlpea14010005

Mazumder D, Datta M, Bodoh AC, Sakib AA. A Scalable Formal Framework for the Verification and Vulnerability Analysis of Redundancy-Based Error-Resilient Null Convention Logic Asynchronous Circuits. Journal of Low Power Electronics and Applications. 2024; 14(1):5. https://doi.org/10.3390/jlpea14010005

Chicago/Turabian StyleMazumder, Dipayan, Mithun Datta, Alexander C. Bodoh, and Ashiq A. Sakib. 2024. "A Scalable Formal Framework for the Verification and Vulnerability Analysis of Redundancy-Based Error-Resilient Null Convention Logic Asynchronous Circuits" Journal of Low Power Electronics and Applications 14, no. 1: 5. https://doi.org/10.3390/jlpea14010005

APA StyleMazumder, D., Datta, M., Bodoh, A. C., & Sakib, A. A. (2024). A Scalable Formal Framework for the Verification and Vulnerability Analysis of Redundancy-Based Error-Resilient Null Convention Logic Asynchronous Circuits. Journal of Low Power Electronics and Applications, 14(1), 5. https://doi.org/10.3390/jlpea14010005