Class AB Voltage Follower and Low-Voltage Current Mirror with Very High Figures of Merit Based on the Flipped Voltage Follower

Abstract

1. Introduction

2. Proposed Circuits

2.1. High-Performance Class AB Voltage Follower HP_CSCFVF

2.1.1. Description

2.1.2. Class AB Operation of Proposed Voltage Follower

2.2. High-Performance Low-Voltage Current Mirror (HP_CS_CM)

3. Simulation Results

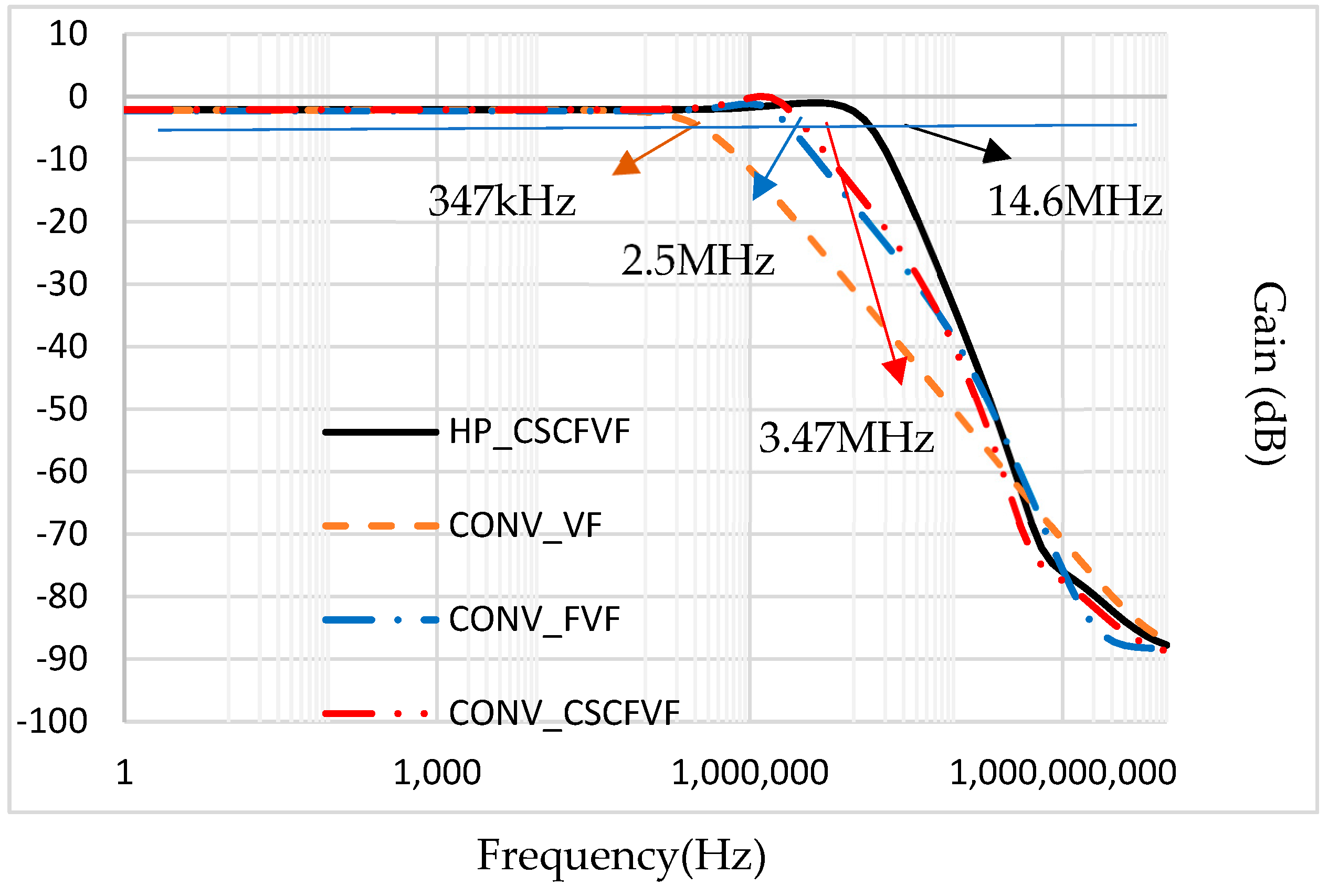

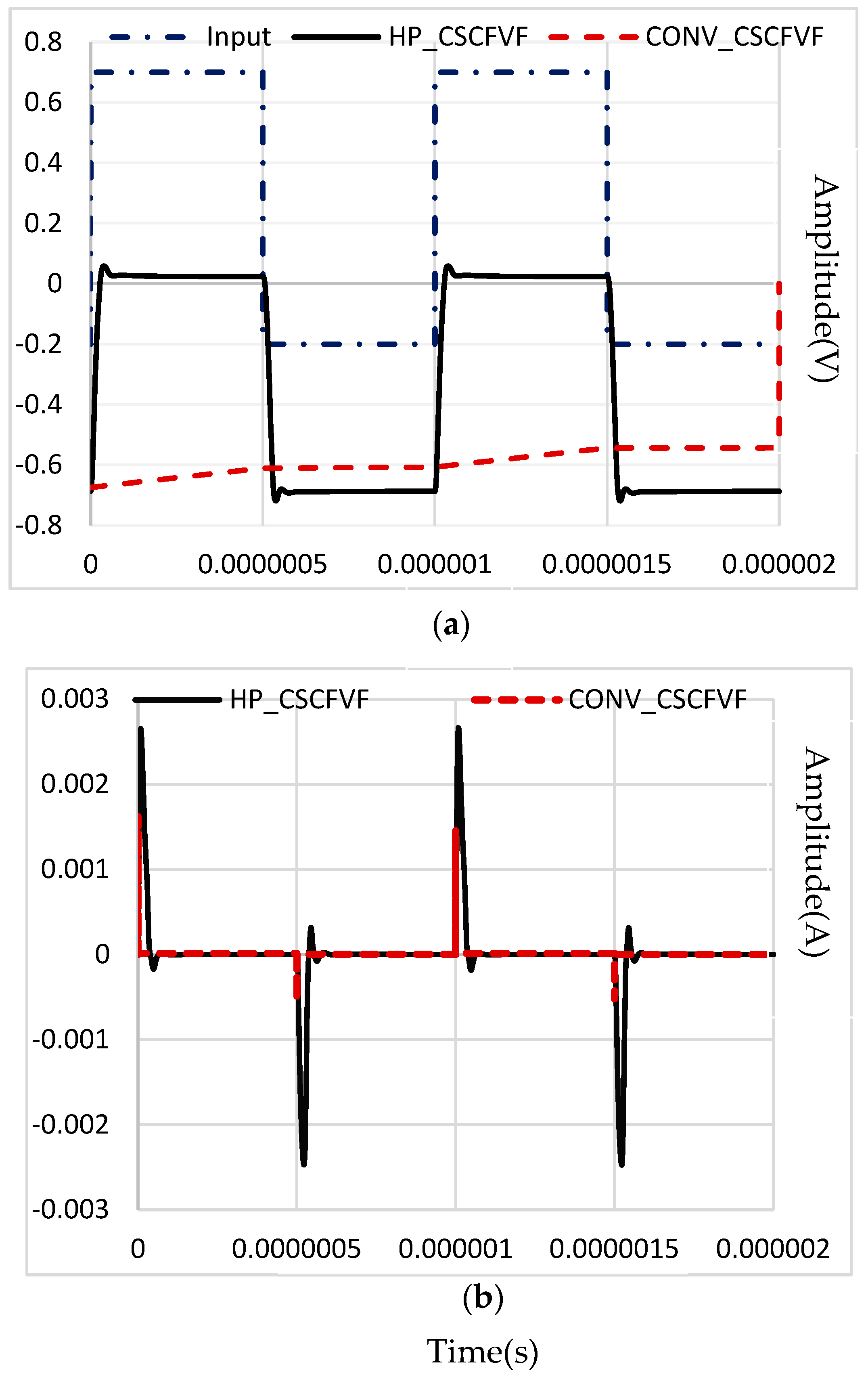

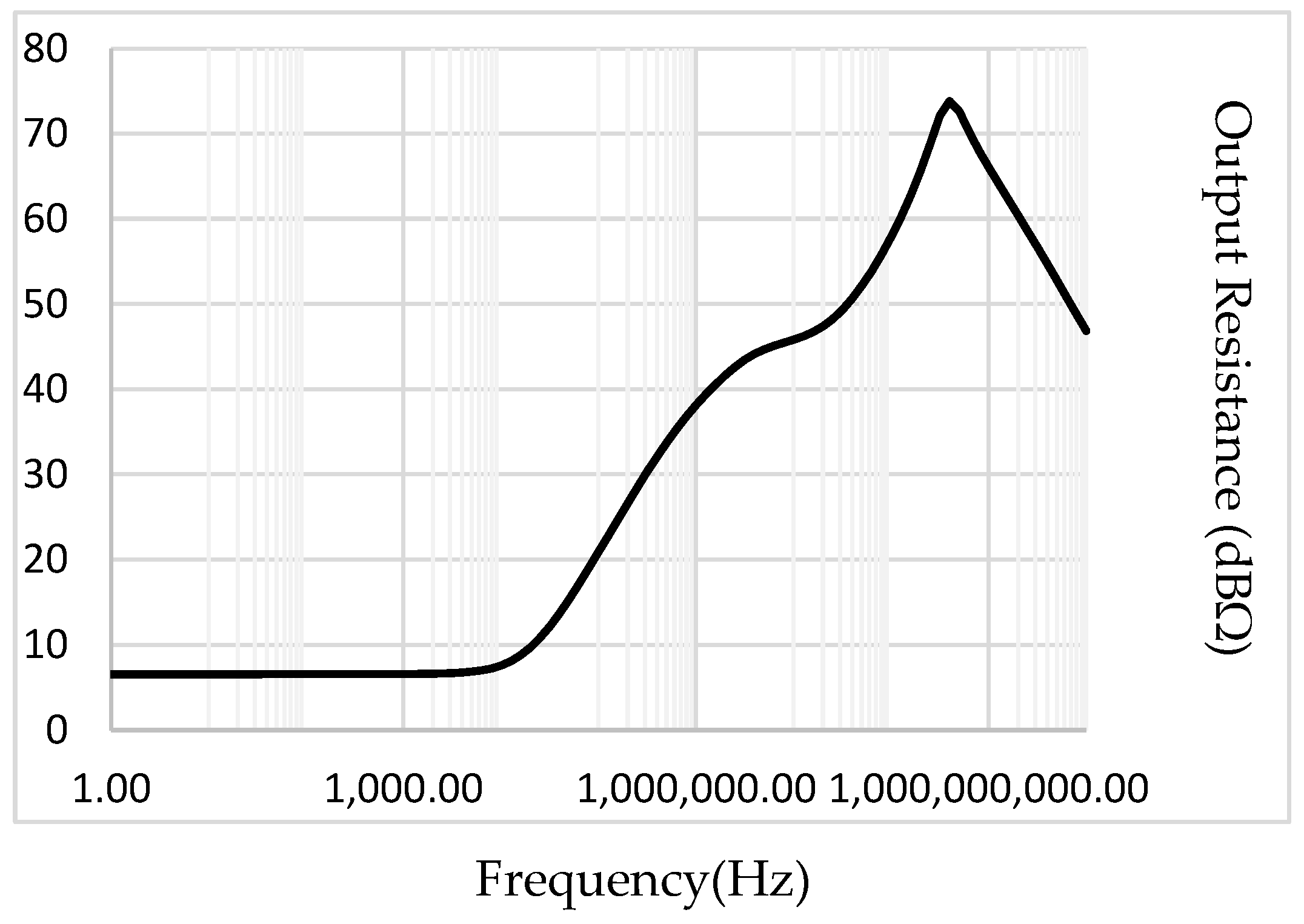

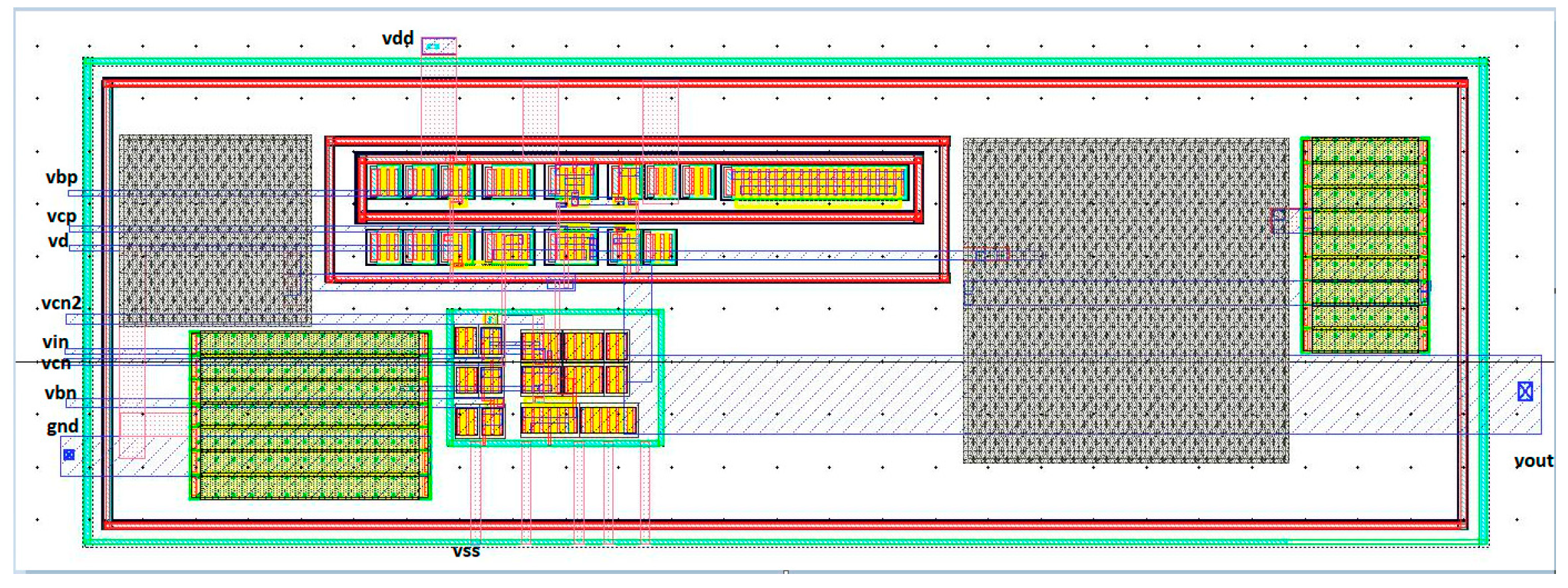

3.1. Simulations of the High-Perfromance Class AB Follower HP_CSCFVF

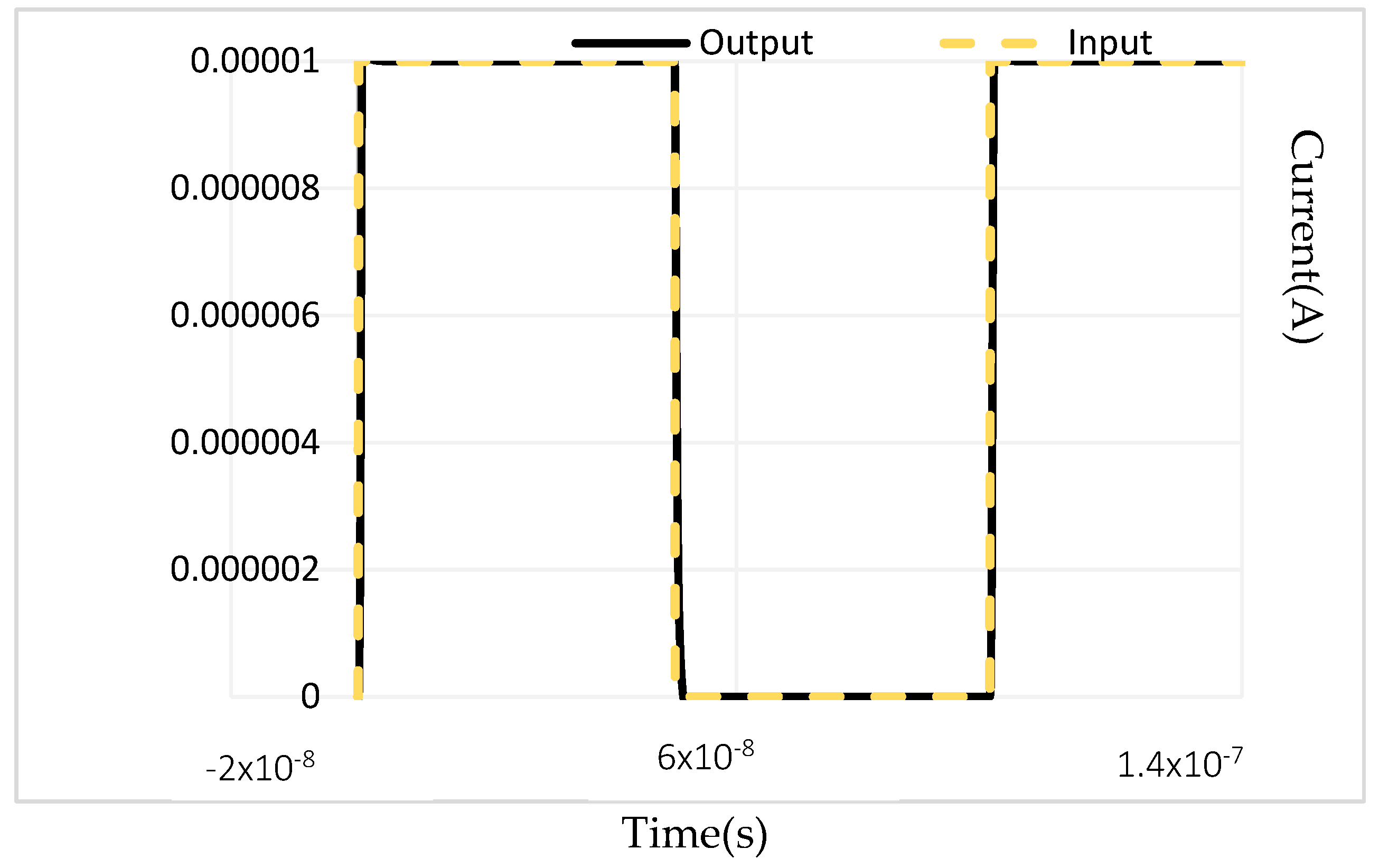

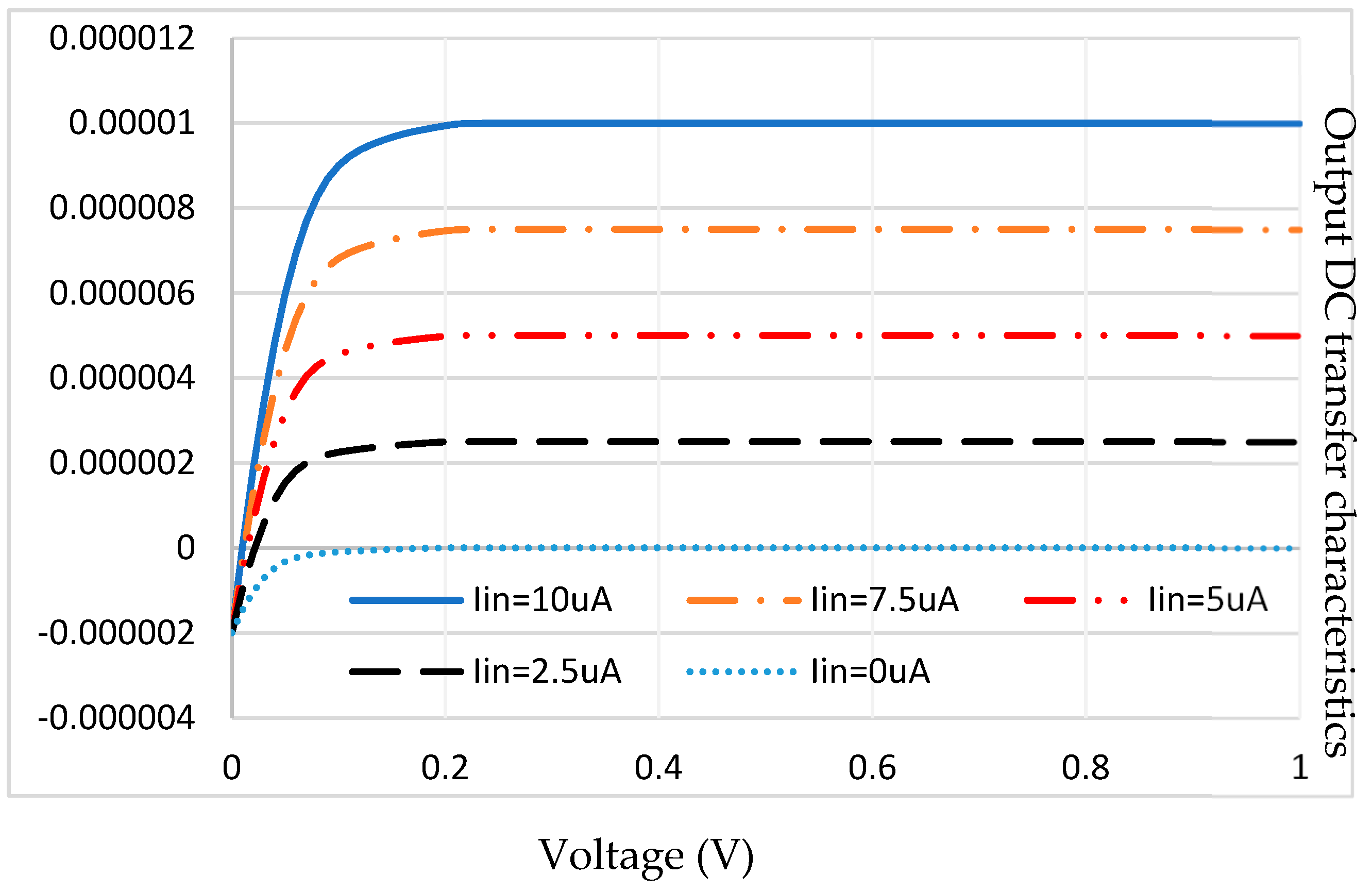

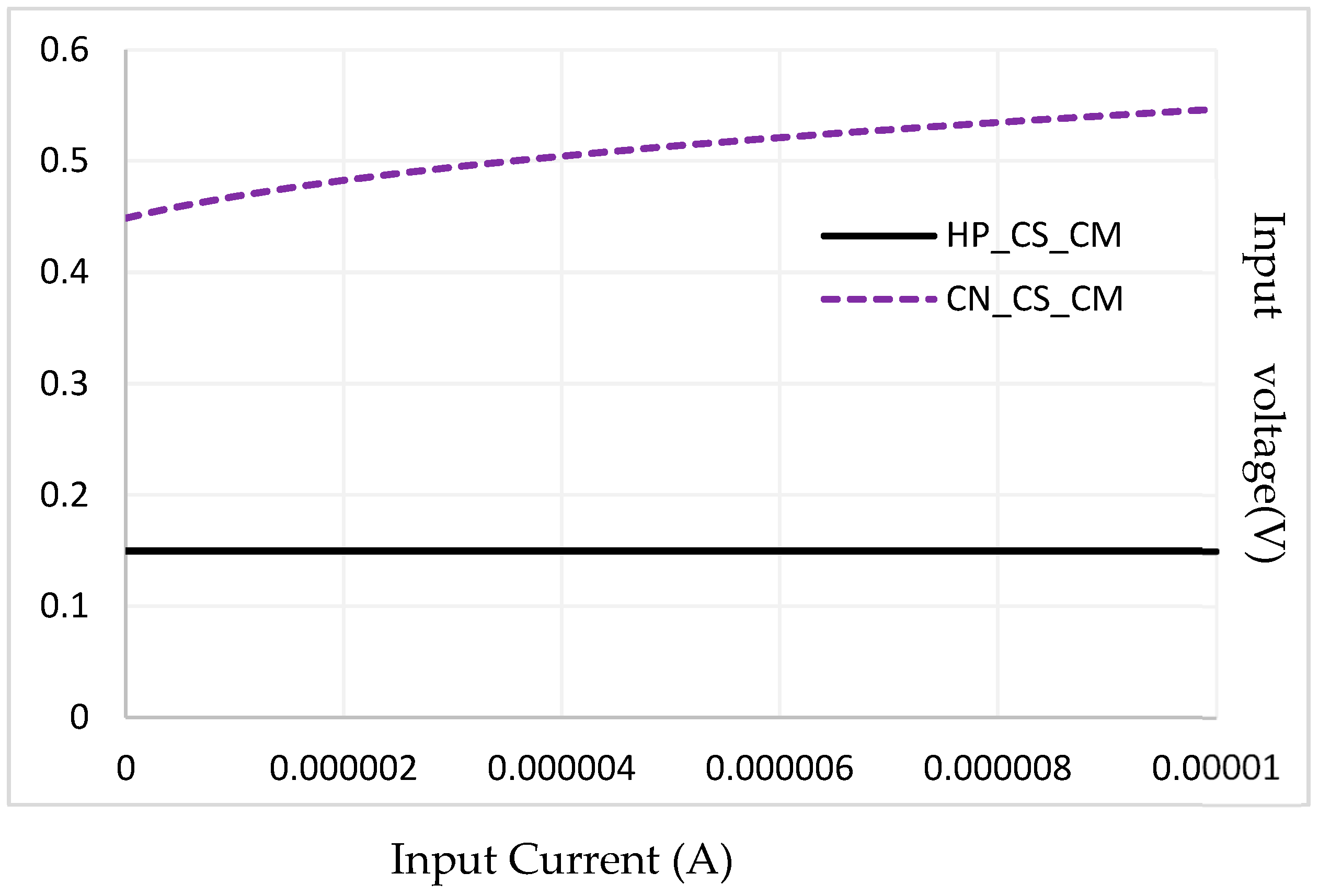

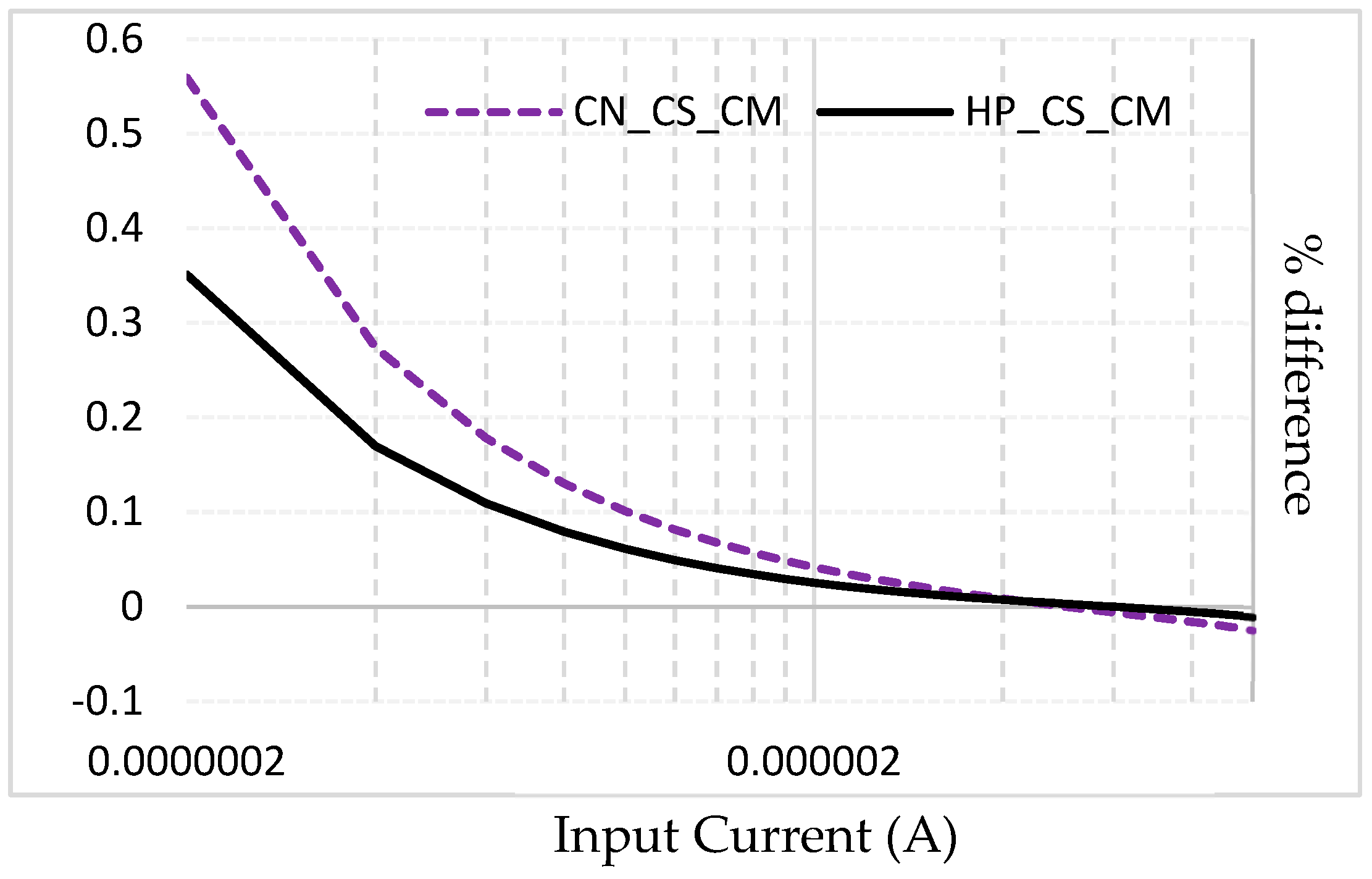

3.2. Simulation Results for Low-Voltage High-Performance Current Mirror HP_CS_CM

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Razavi, B. Design of Analog CMOS Integrated Circuits; McGraw Hill: Boston, MA, USA, 2001. [Google Scholar]

- Filanovsky, I.M.; Järvenhaara, J.; Tchamov, N.T. Source follower: A misunderstood humble circuit. In Proceedings of the 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 4–7 August 2013; pp. 185–188. [Google Scholar]

- Allen, P.E.; Holberg, D.R. CMOS Analog Circuit Design, 2nd ed.; Oxford Univeristy Press: Oxford, UK, 2002; Volume 2. [Google Scholar]

- Carvajal, R.G.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Torralba, A.; Galan, J.A.G.; Carlosena, A.; Chavero, F.M. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Gupta, S.; Padilla, I.; Carvajal, R.G.; Torralba, A.; Jimenez, M.; Munoz, F. Comparison of conventional and new flipped voltage structures with increased input/output signal swing and current sourcing/sinking capabilities. In Proceedings of the 48th Midwest Symposium on Circuits and Systems, Cincinnati, OH, USA, 7–10 August 2005; Volume 1152, pp. 1151–1154. [Google Scholar]

- Sawigun, C.; Demosthenous, A.; Liu, X.; Serdijn, W.A. A Compact Rail-to-Rail Class-AB CMOS Buffer With Slew-Rate Enhancement. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 486–490. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurrò, P.; Trifiletti, A. A class-AB flipped voltage follower output stage. In Proceedings of the 2011 20th European Conference on Circuit Theory and Design (ECCTD), Linkoping, Sweden, 29–31 August 2011; pp. 757–760. [Google Scholar]

- Jindal, C.; Pandey, R. High Slew-Rate and Very-Low Output Resistance Class-AB Flipped Voltage Follower Cell for Low-Voltage Low-Power Analog Circuits. Wirel. Pers. Commun. 2022, 123, 215–228. [Google Scholar] [CrossRef]

- Xing, G.; Lewis, S.H.; Viswanathan, T.R. Self-Biased Unity-Gain Buffers With Low Gain Error. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 36–40. [Google Scholar] [CrossRef]

- Paul, A.; Ramírez-Angulo, J.; Torralba, A. Bandwidth-Enhanced High Current Efficiency Class-AB Buffer With Very Low Output Resistance. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1544–1548. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.; Cruz, C.A.D.l.; Carvajal, R.G. Wide-Swing Class AB Regulated Cascode Current Mirror. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Virtual, 12–14 October 2020; pp. 1–4. [Google Scholar]

- Moaf, M.; Piri, M.; Amiri, P. Two High Slew Rate Buffers Based on Flipped Voltage Follower. Int. J. Electr. Eng. Inform. 2016, 8, 451–460. [Google Scholar] [CrossRef]

- Ocampo-Hidalgo, J.J.; Alducín-Castillo, J.; Vázquez-Álvarez, I.; Oliva-Moreno, L.N.; Molinar-Solís, J.E. A CMOS Low-Voltage Super Follower Using Quasi-Floating Gate Techniques. J. Circuits Syst. Comput. 2017, 27, 1850111. [Google Scholar] [CrossRef]

- Centurelli, F.; Monsurrò, P.; Ruscio, D.; Trifiletti, A. A new class-AB Flipped Voltage Follower using a common-gate auxiliary amplifier. In Proceedings of the 2016 MIXDES—23rd International Conference Mixed Design of Integrated Circuits and Systems, Lodz, Poland, 23–25 June 2016; pp. 143–146. [Google Scholar]

- Ocampo-Hidalgo, J.J.; Molinar-Solis, J.E.; Oliva-Moreno, N.; Ponce-Ponce, V.H.; Ramirez-Salinas, M.A. The Merged Voltage Follower: A Class-AB CMOS Follower with Enhanced Bandwidth to Drive Loads with Low Resistance and Large Capacitance Le suiveur de tension fusionné: Un suiveur CMOS de classe AB avec une bande passante améliorée pour piloter des charges avec une faible résistance et une grande capacité. IEEE Can. J. Electr. Comput. Eng. 2021, 44, 30–40. [Google Scholar] [CrossRef]

- Jindal, C.; Pandey, R. Class-AB level shifted flipped voltage follower cell using bulk-driven technique. IET Circuits Devices Syst. 2018, 12, 286–294. [Google Scholar] [CrossRef]

- Aggarwal, B.; Gupta, M.; Gupta, A.K.; Sangal, A. A new low voltage level-shifted FVF current mirror with enhanced bandwidth and output resistance. Int. J. Electron. 2016, 103, 1759–1775. [Google Scholar] [CrossRef]

- Safari, L.; Minaei, S. A Low-Voltage Low-Power Resistor-Based Current Mirror and Its Applications. J. Circuits Syst. Comput. 2017, 26, 1750180. [Google Scholar] [CrossRef]

- Doreyatim, M.; Akbari, M.; Nazari, M.; Mahani, S. A low-voltage gain boosting-based current mirror with high input/output dynamic range. Microelectron. J. 2019, 90, 88–95. [Google Scholar] [CrossRef]

- Bchir, M.; Aloui, I.; Hassen, N. A bulk-driven quasi-floating gate FVF current mirror for low voltage, low power applications. Integration 2020, 74, 45–54. [Google Scholar] [CrossRef]

| (A) | ||||||

| Corner | tt | ff | fs | sf | ss | SD |

| ITotQ (µA) | 21 | 22 | 21 | 22 | 21 | 0.49 |

| f3dB (MHZ) | 14.6 | 18 | 15.2 | 14.5 | 12.5 | 1.77 |

| SR (V/µs) | 24.3 | 28 | 21.5 | 25.6 | 21.7 | 2.4 |

| Ioutpk (mA) | 2.68 | 3.04 | 2.5 | 2.7 | 2.42 | 0.2 |

| (B) | ||||||

| Corner | tt | ff | fs | sf | ss | SD |

| ITotQ (µA) | 26 | 29 | 26 | 27 | 25 | 1.35 |

| f3dB (MHZ) | 15 | 18.5 | 15.2 | 14.8 | 12.7 | 1.86 |

| SR (V/µs) | 22.5 | 25.5 | 20.18 | 22.34 | 20.13 | 1.9 |

| Ioutpk (mA) | 2.45 | 2.73 | 2.38 | 2.42 | 2.22 | 0.16 |

| (C) | ||||||

| Corner | tt | ff | fs | sf | ss | SD |

| ITotQ (µA) | 20 | 20 | 20 | 19 | 19 | 0.49 |

| f3dB (MHZ) | 14.4 | 17.6 | 15.8 | 14.8 | 12.3 | 1.74 |

| SR (V/µs) | 26.6 | 29.3 | 22.9 | 25.8 | 22.8 | 2.4 |

| Ioutpk (mA) | 2.79 | 3.06 | 2.67 | 2.8 | 2.5 | 0.18 |

| Parameter | Ref./Year [6]/2012 | Ref./Year [12]/2016 | Ref./Year [13]/2018 | Ref./Year [14]/2016 | Ref./Year [15]/2021 | Ref./Year [16]/2018 | CONV_VF Figure 1a | This Work Figure 3 | |

|---|---|---|---|---|---|---|---|---|---|

| Process technology (µm) | 0.35 | 0.18 | 0.18 | 0.5 | 0.045 | 0.5 | 0.18 | 0.18 | 0.18 |

| Exp | Sim by Auth. | Sim | Exp | Sim | Exp | Sim | Sim | Sim | |

| Supply (V) | 3 | ±0.9 | 1.2 | 1.5 | 1.2 | 2 | 1.2 | ±0.75 | ±0.75 |

| ITotQ (µA) | 81 | 243 | 20.8 | 80 | 8.3 | 69 | 20 | 9 | 21 |

| Load Cap. (pF) | 20 | 50 | 10/100 | 50 | 1 | 47 | 1 | 100 | 100 |

| BW (MHz) | 5.8 | 3.65 | 15@100 pF | 10 | 170 | 32 | 670.2 | 0.347 | 14.6 |

| Ioutpk+ (mA) | 1.62 | 3.16 | 0.32 | 1.8 | 0.17 | 1.59 | 0.116 | 0.085 | 2.6 |

| Ioutpk− (mA) | 1.67 | 3.16 | NA | 1.8 | 0.08 | 1.42 | 0.120 | 0.034 | 2.47 |

| SR+ (V/µS) | 79.4 | 63.2 | 32@10 pF | 36 | 42 | 33.8 | 116.6 | 2.5 | 34.47 |

| SR− (V/µS) | 83.6 | 63.2 | NA | 36 | 50 | 30.3 | 120.5 | 12 | 34.03 |

| Output resistance (Ω) | NA | NA | 56 | NA | 1.15k | NA | 144 | 1.2k | 2.11 |

| Quiescent power PdissQ (µWatt) | 243 | 437 | 25 | 120 | 10 | 138 | 24 | 13.5 | 31.5 |

| FOMCE = Ioutpk/ITotQ | 20 | 12 | 15 | 22.5 | 10 | 20 | 5.8 | 3.7 | 118 |

| FOMSS = BWxCL/PdissQ [(MHz)pF]/µW | 0.47 | 0.42 | 60 | 4.16 | 17 | 10.9 | 28 | 2.5 | 46 |

| FOMGlobal | 3.06 | 2.24 | 30 | 9.7 | 13 | 15 | 12.7 | 3.04 | 73 |

| Frequency (Hz) | THD (dB) |

|---|---|

| 500 | −60 |

| 10 k | −62 |

| 1 M | −60 |

| 100 M | −40 |

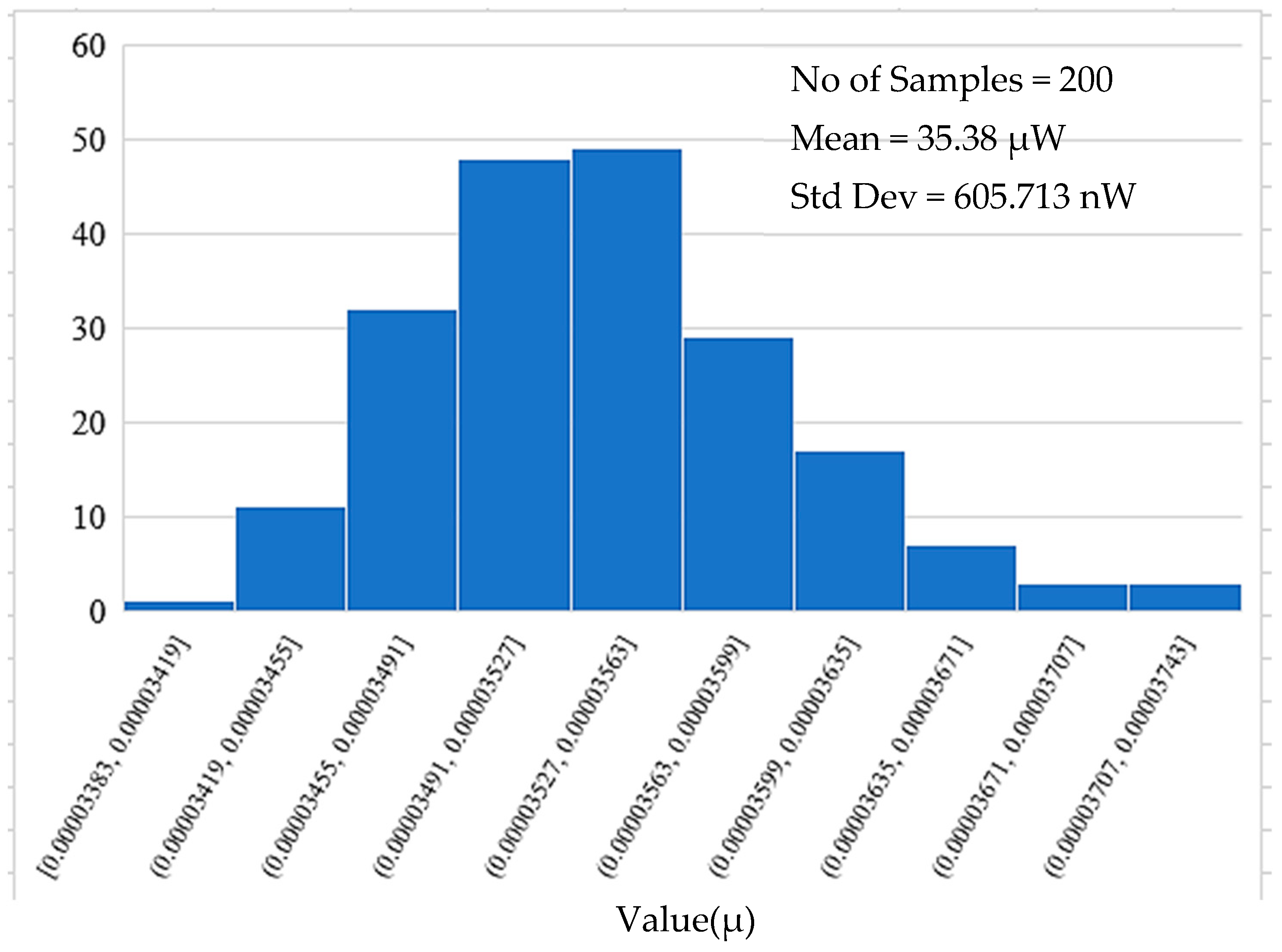

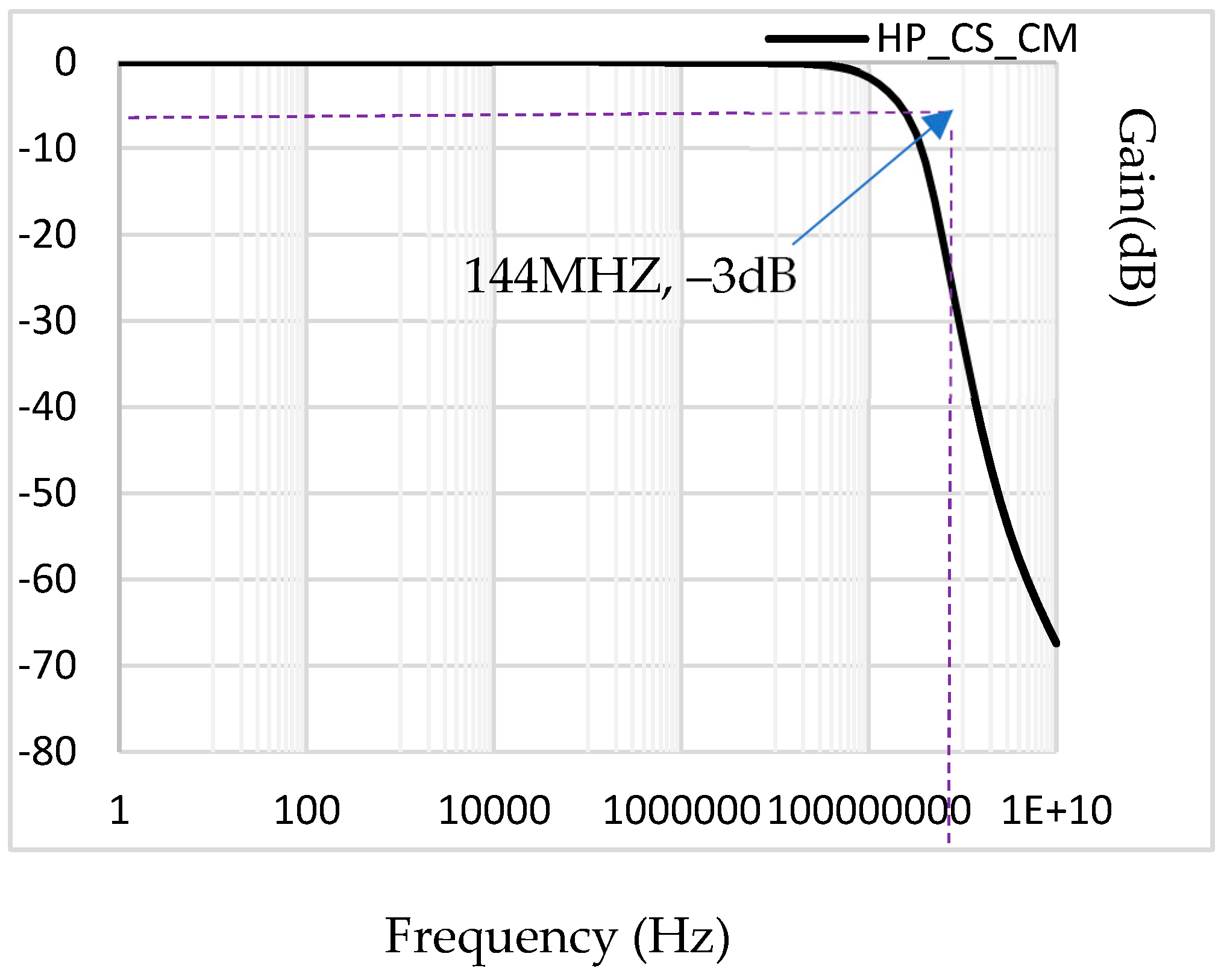

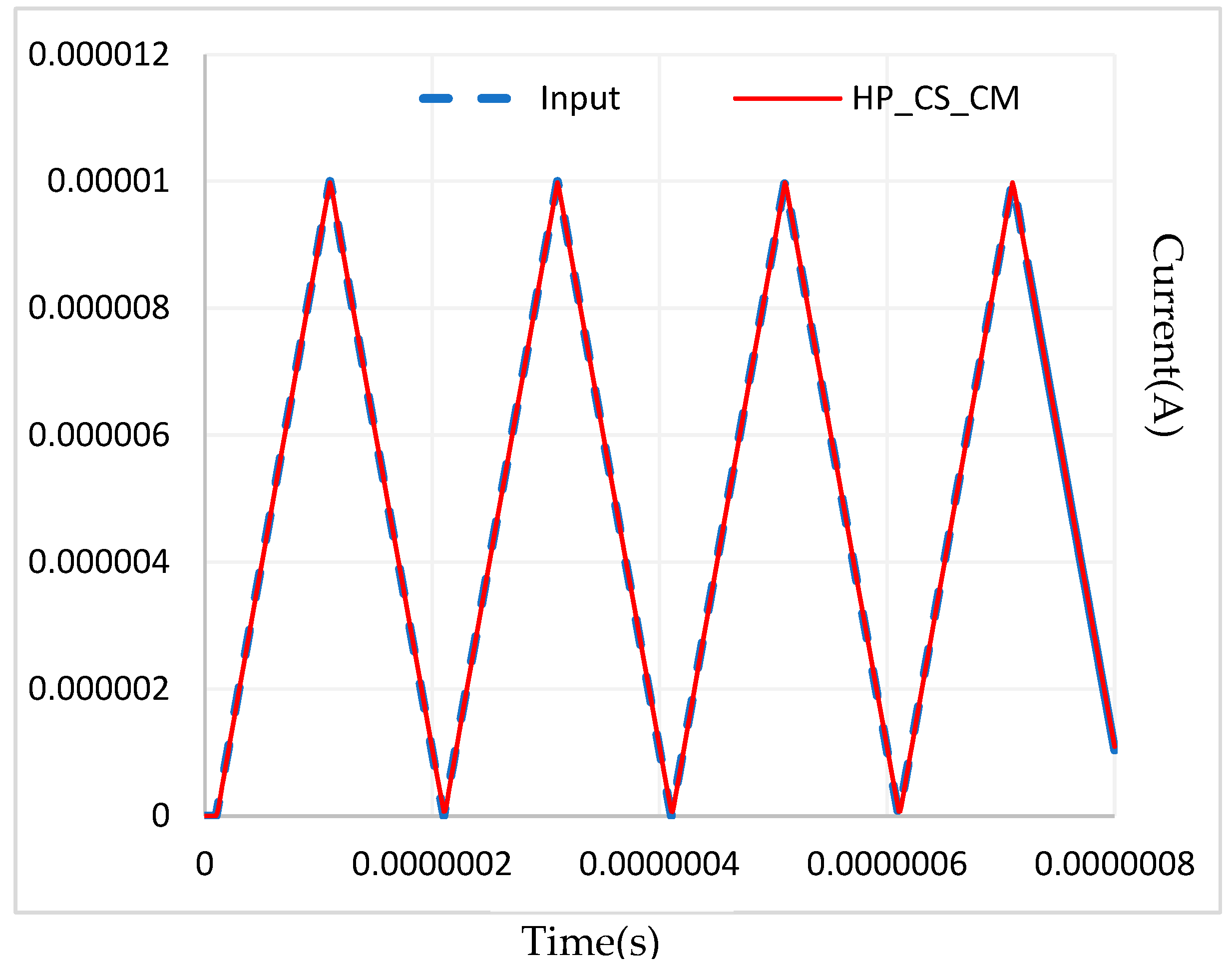

| Parameter Name | Mean Value | Standard Deviation |

|---|---|---|

| Bandwidth (MHz) | 144 | 0.789 |

| Input resistance (dBΩ) | −13.7 | 0.728 |

| Output Resistance(dBΩ) | 221 | 0.505 |

| Quiescent Power (µW) | 5.33 | 0.066 |

| Gain (A/A) | 0.999 | 17.8 µ |

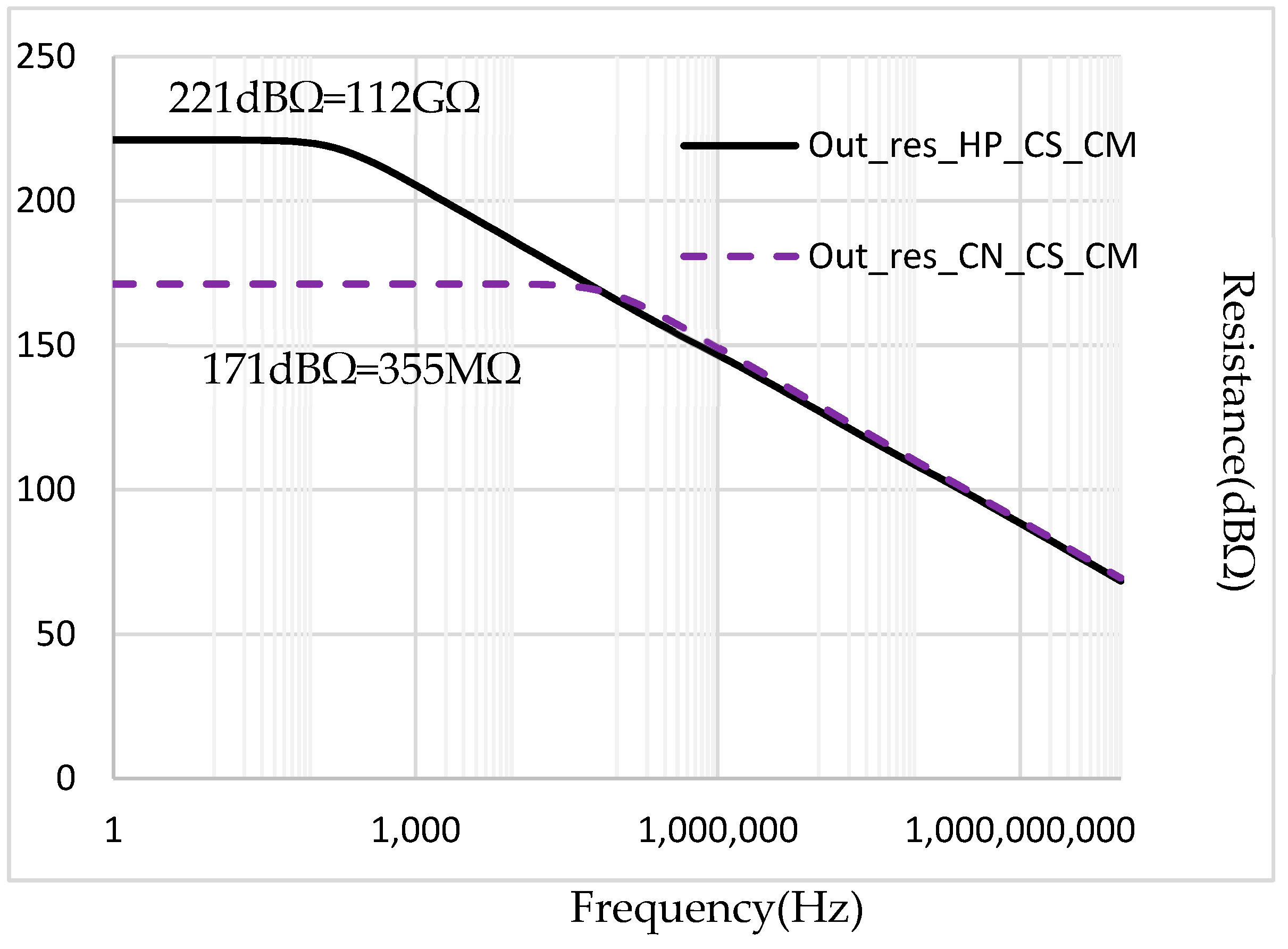

| Parameter | [17] | [18] | [19] | [20] | This Work |

|---|---|---|---|---|---|

| Input Compliance Voltage | 520 m | 39.6 m | - | - | 150 m |

| Current Transfer error (%) | 1.71 | 0.6 | 0.16 | 0.22 | 0.1 |

| Input resistance (Ω) | 21.43 | 496 | 68.3 | 130 | 0.212 |

| Output Resistance (Ω) | 1.14 G | 1 M | 10.5 G | 9.5 G | 112 G |

| Bandwidth (Hz) | 6.17 G | 181 M | 402 M | 2.7 G | 144 M |

| Noise (pA/√Hz) | - | - | 7.8 | - | - |

| Supply (V) | 1 | 0.9 | 1 | 1 | 1 |

| Power (µW) | 916.65 | 154 | 110 | 142.9 | 5 |

| FOMCM (MHZ/µW) | 6.73 | 1.17 | 3.6 | 18.89 | 28.8 |

| Technology (µm) | 0.18 | 0.18 | 0.18 | 0.18 | 0.18 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramírez-Angulo, J.; Paul, A.; Gangineni, M.; Hinojo-Montero, J.M.; Huerta-Chua, J. Class AB Voltage Follower and Low-Voltage Current Mirror with Very High Figures of Merit Based on the Flipped Voltage Follower. J. Low Power Electron. Appl. 2023, 13, 28. https://doi.org/10.3390/jlpea13020028

Ramírez-Angulo J, Paul A, Gangineni M, Hinojo-Montero JM, Huerta-Chua J. Class AB Voltage Follower and Low-Voltage Current Mirror with Very High Figures of Merit Based on the Flipped Voltage Follower. Journal of Low Power Electronics and Applications. 2023; 13(2):28. https://doi.org/10.3390/jlpea13020028

Chicago/Turabian StyleRamírez-Angulo, Jaime, Anindita Paul, Manaswini Gangineni, Jose Maria Hinojo-Montero, and Jesús Huerta-Chua. 2023. "Class AB Voltage Follower and Low-Voltage Current Mirror with Very High Figures of Merit Based on the Flipped Voltage Follower" Journal of Low Power Electronics and Applications 13, no. 2: 28. https://doi.org/10.3390/jlpea13020028

APA StyleRamírez-Angulo, J., Paul, A., Gangineni, M., Hinojo-Montero, J. M., & Huerta-Chua, J. (2023). Class AB Voltage Follower and Low-Voltage Current Mirror with Very High Figures of Merit Based on the Flipped Voltage Follower. Journal of Low Power Electronics and Applications, 13(2), 28. https://doi.org/10.3390/jlpea13020028