An Innovative Successive Approximation Register Analog-to-Digital Converter for a Nine-Axis Sensing System

Abstract

1. Introduction

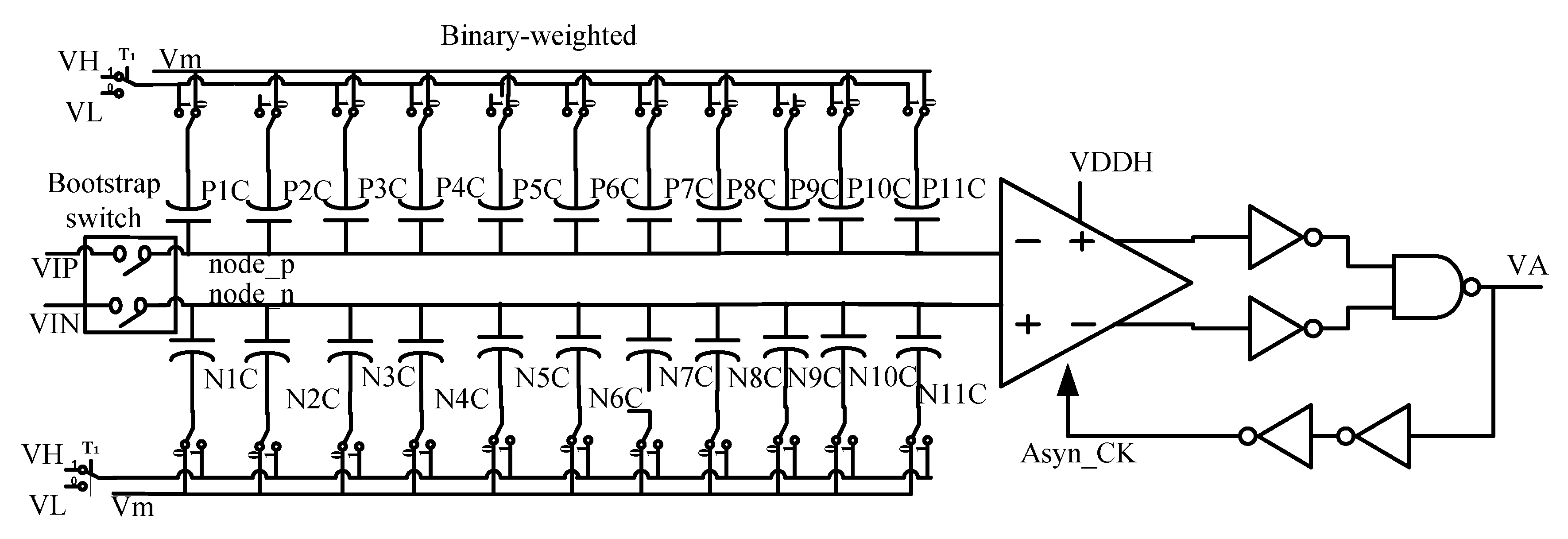

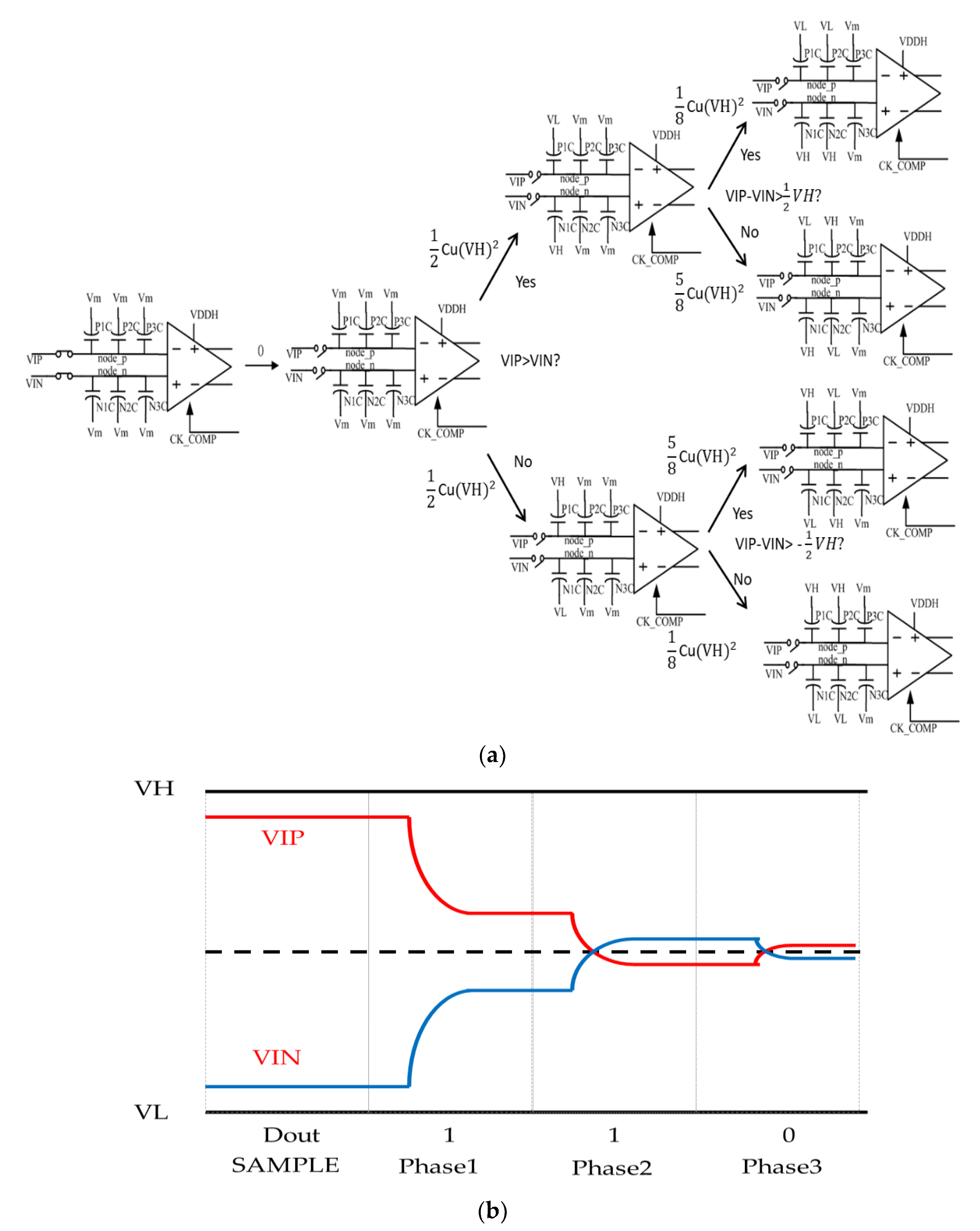

1.1. Analysis of the Switching Base Vm (SW-B-M) Algorithm and Architecture

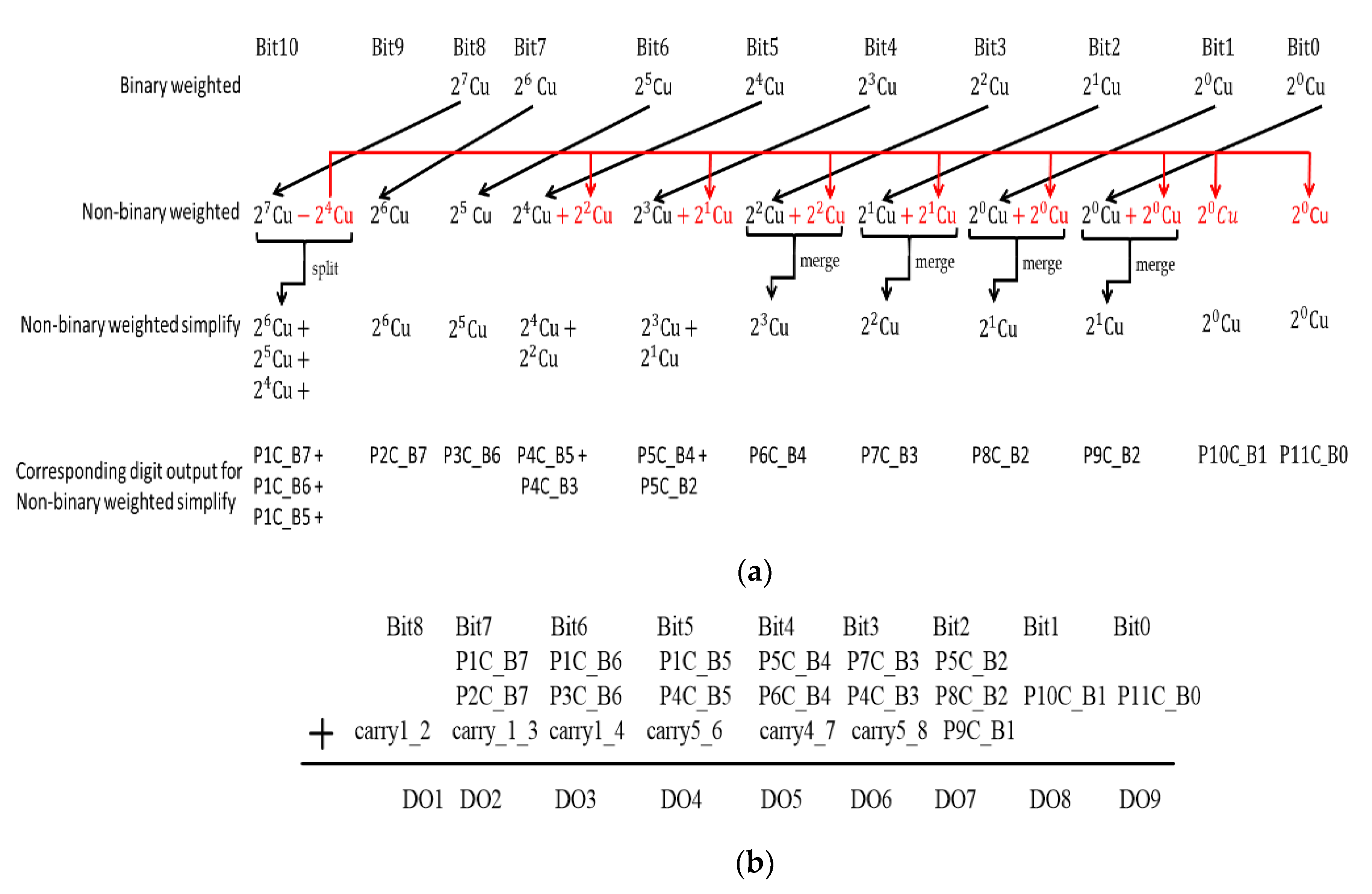

1.2. Non-Binary Algorithm

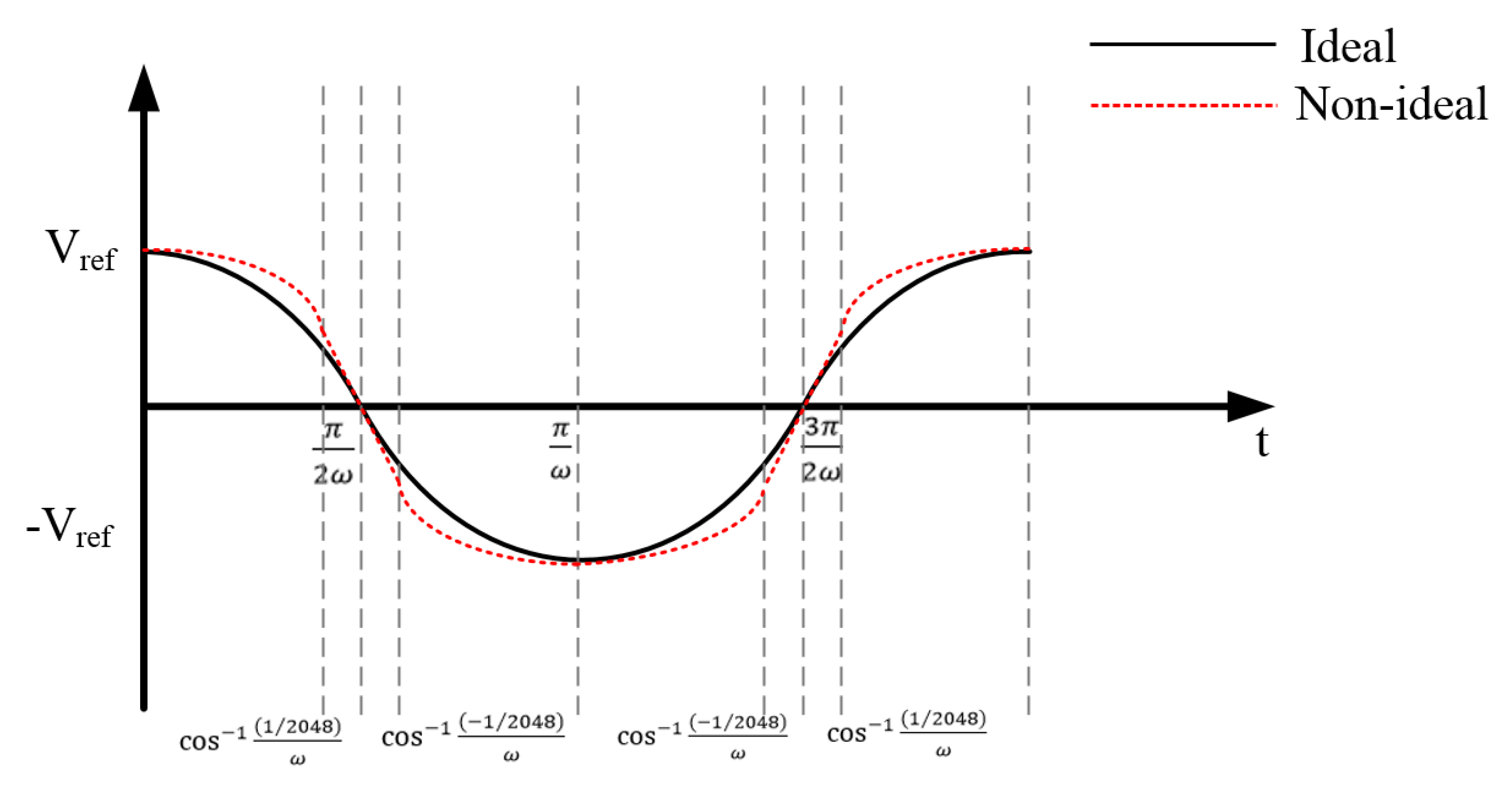

1.3. Linearity Analysis

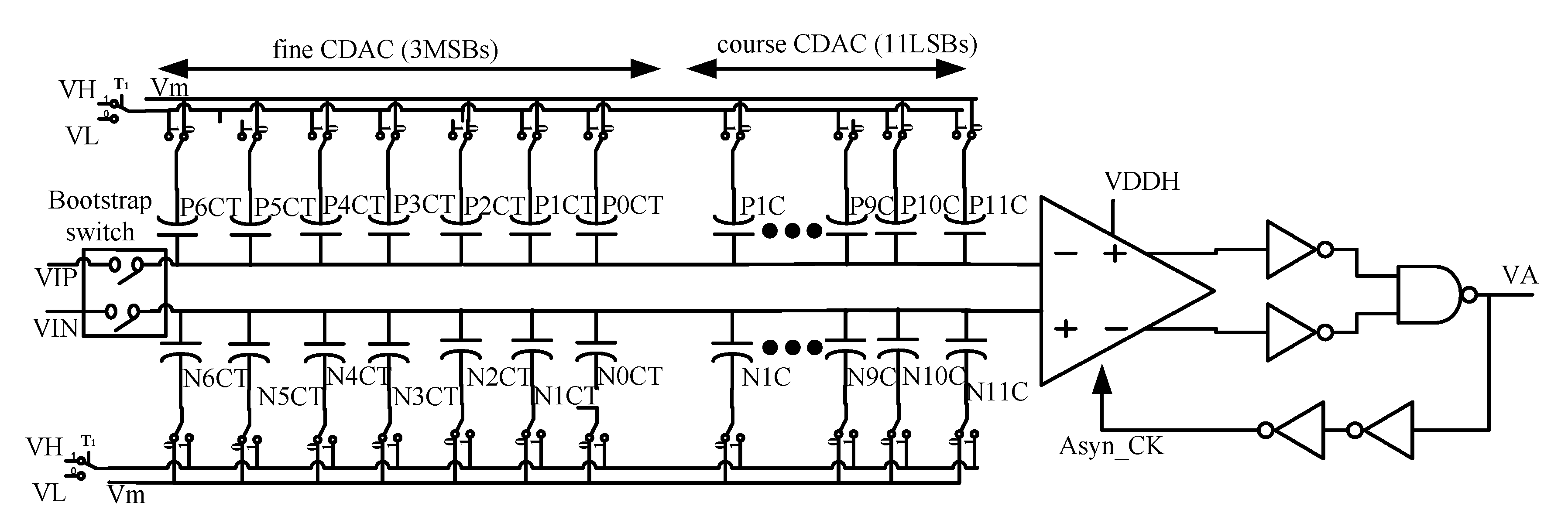

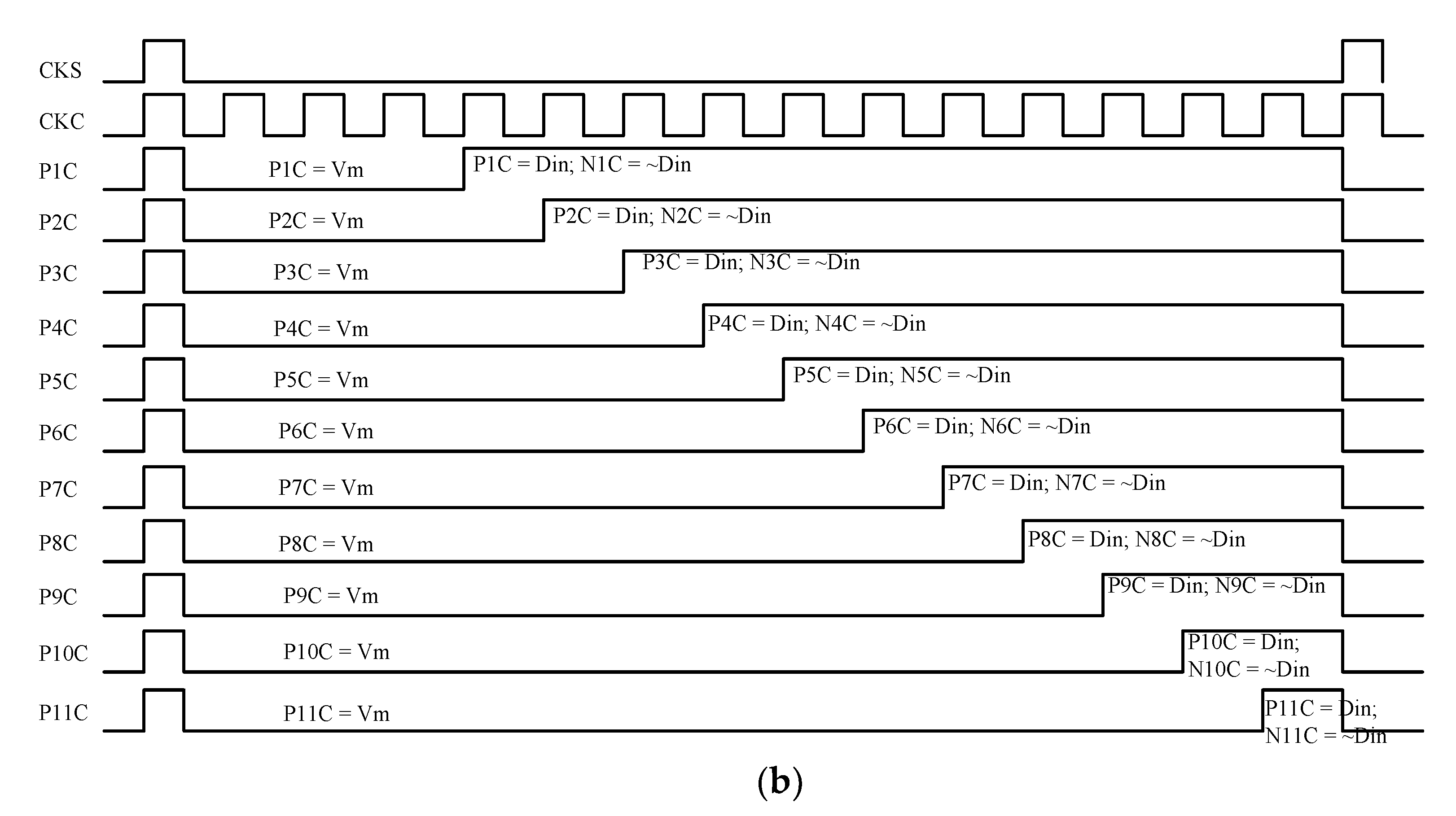

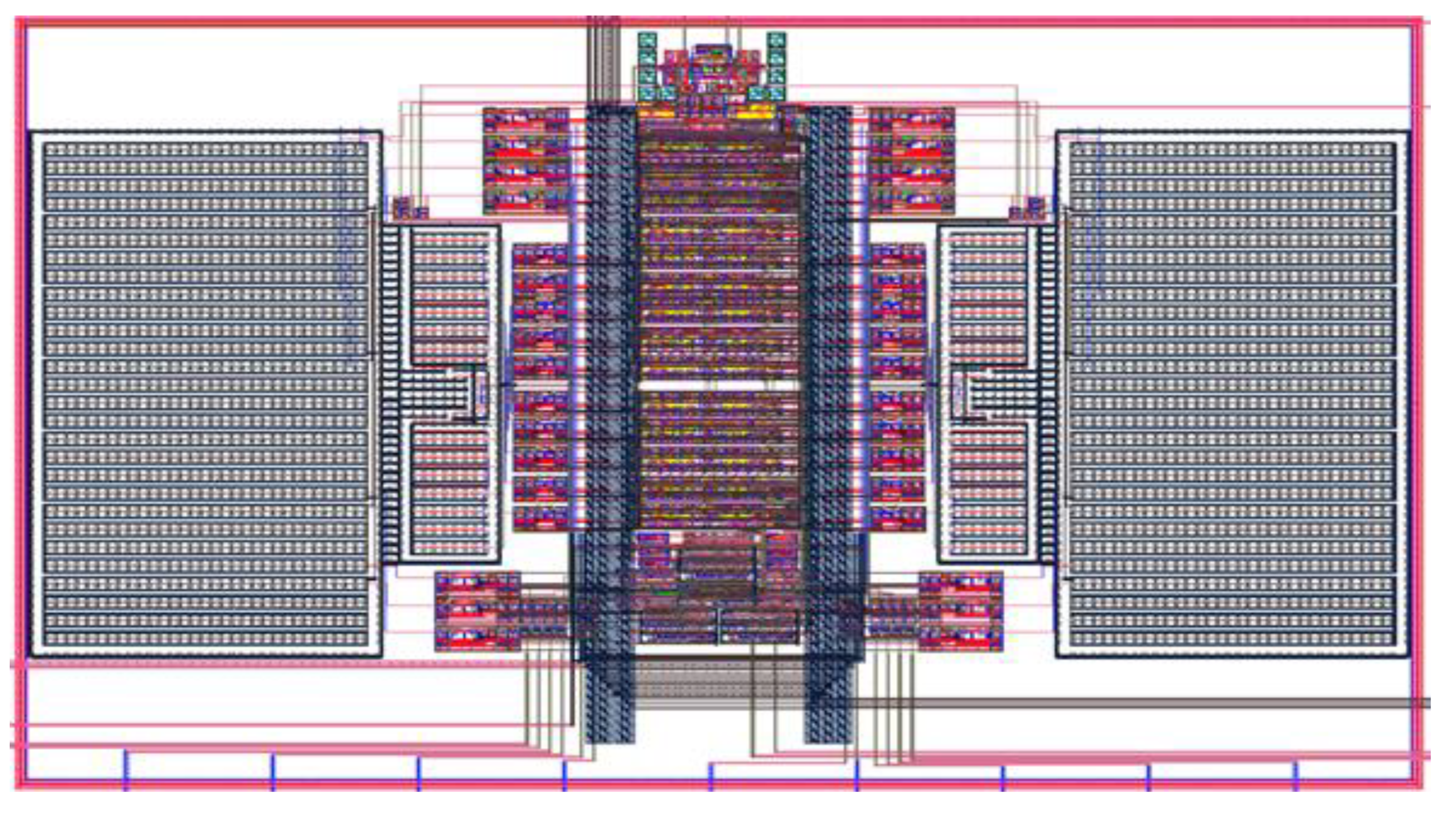

2. The Successive Approximation Register Analog-to-Digital Converter with the Fine (Three Most Significant Bits) Plus Course Conversion (11 Least Significant Bits) Capacitive Digital-to-Analog Converter Architecture

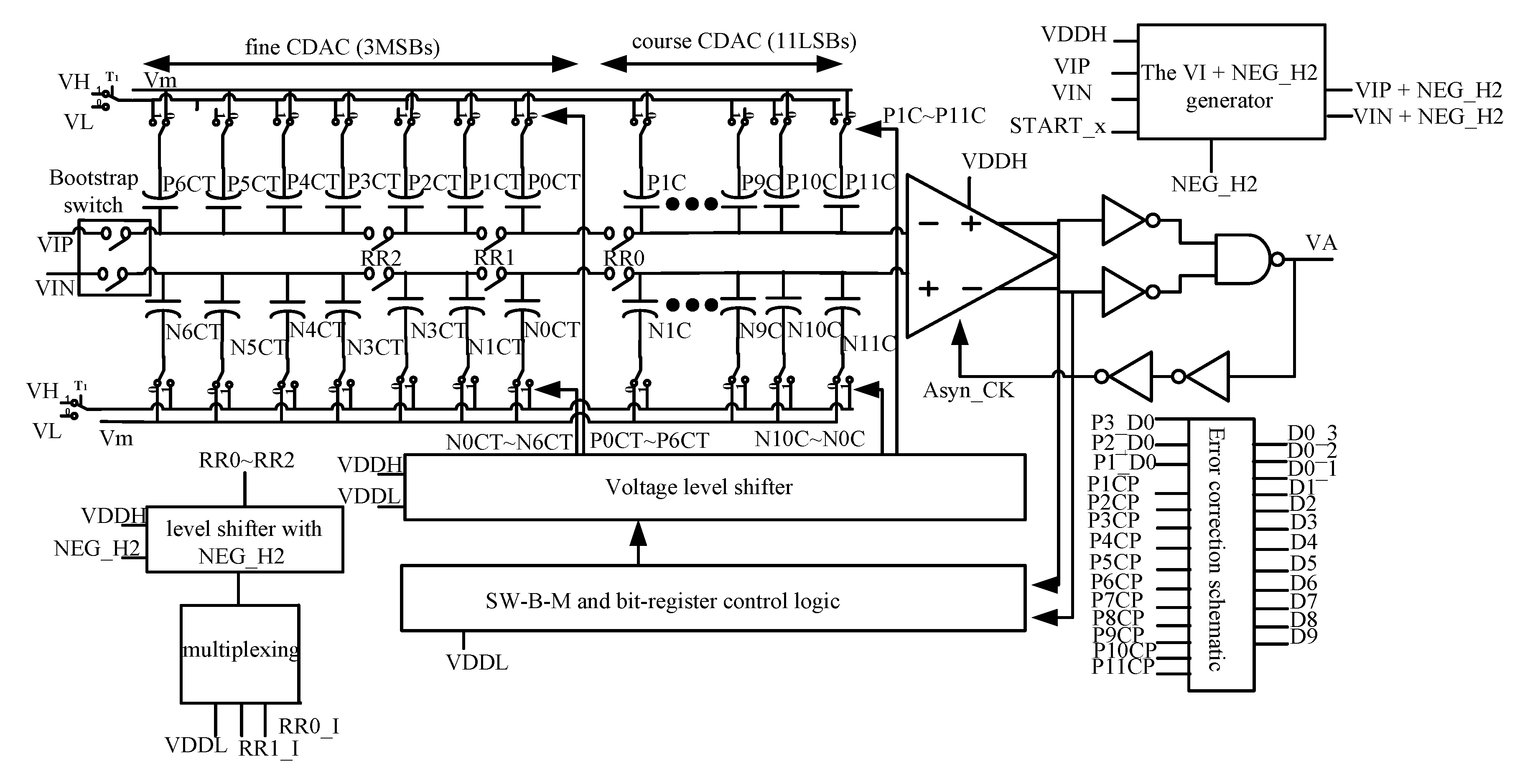

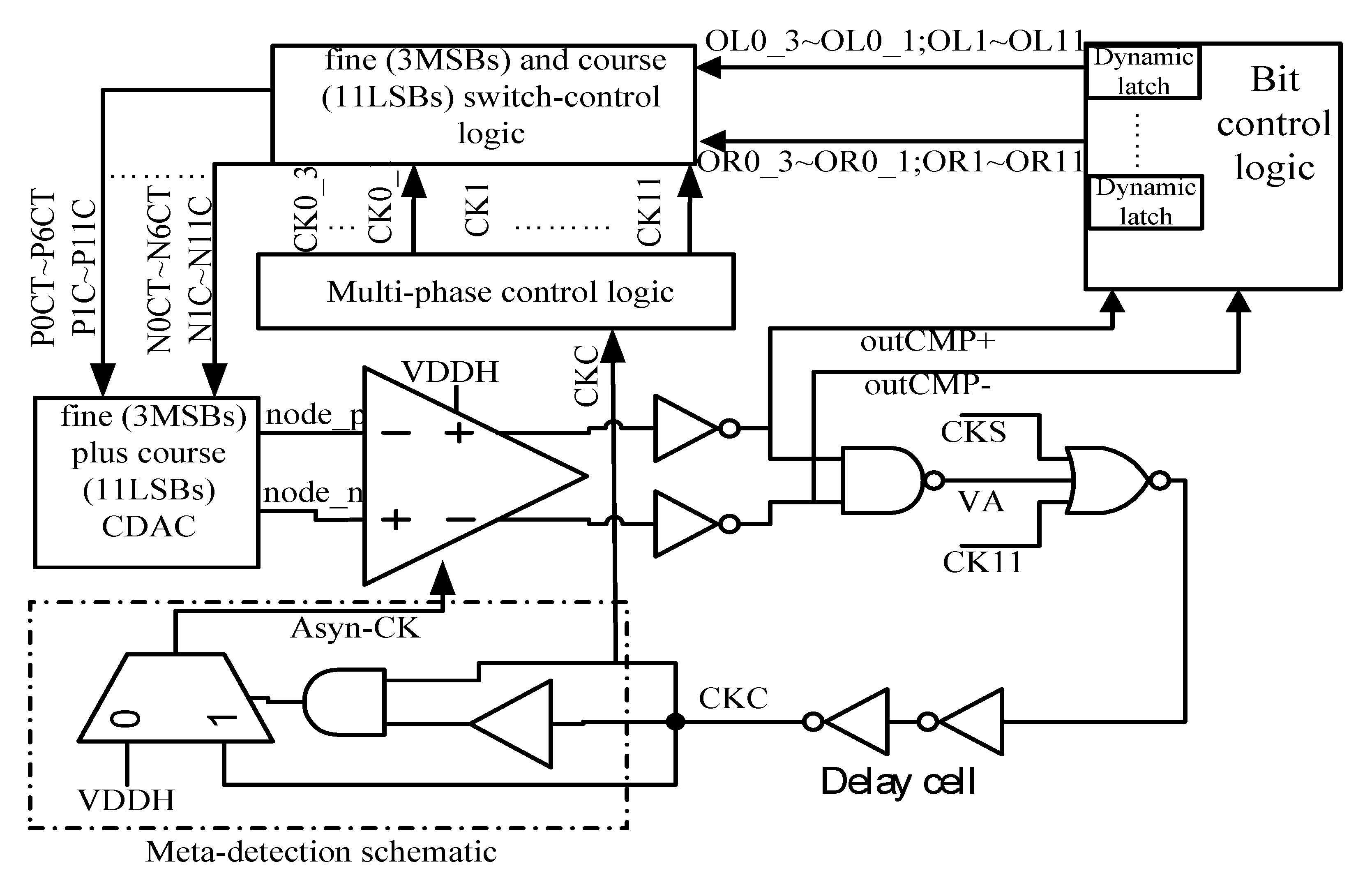

2.1. Block Diagram of the Successive Approximation—Register Analog-to-Digital Converter with the Fine Plus Course Conversion Capacitive Digital-to-Analog Converter (SAR-ADC-WFC-CDA)

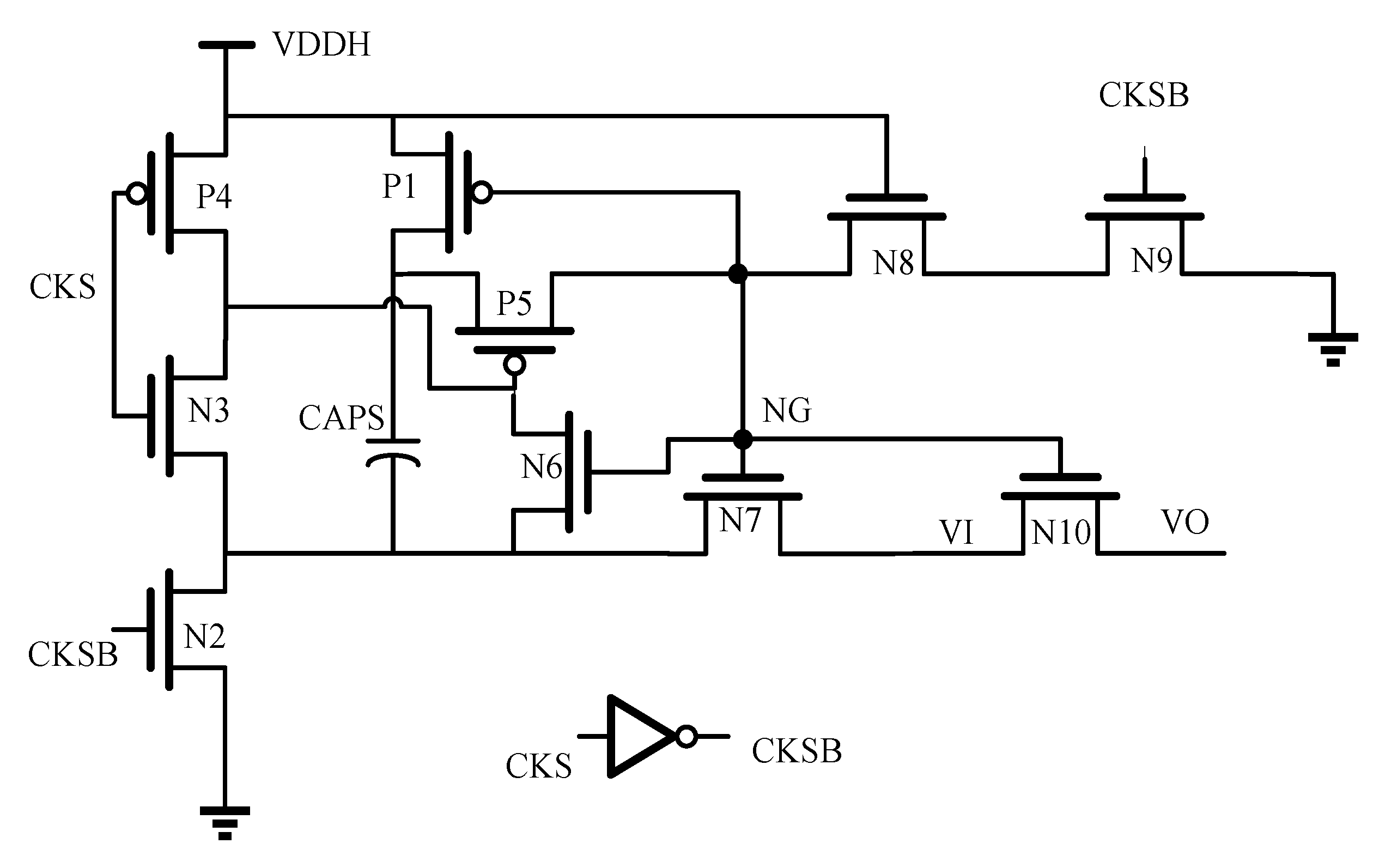

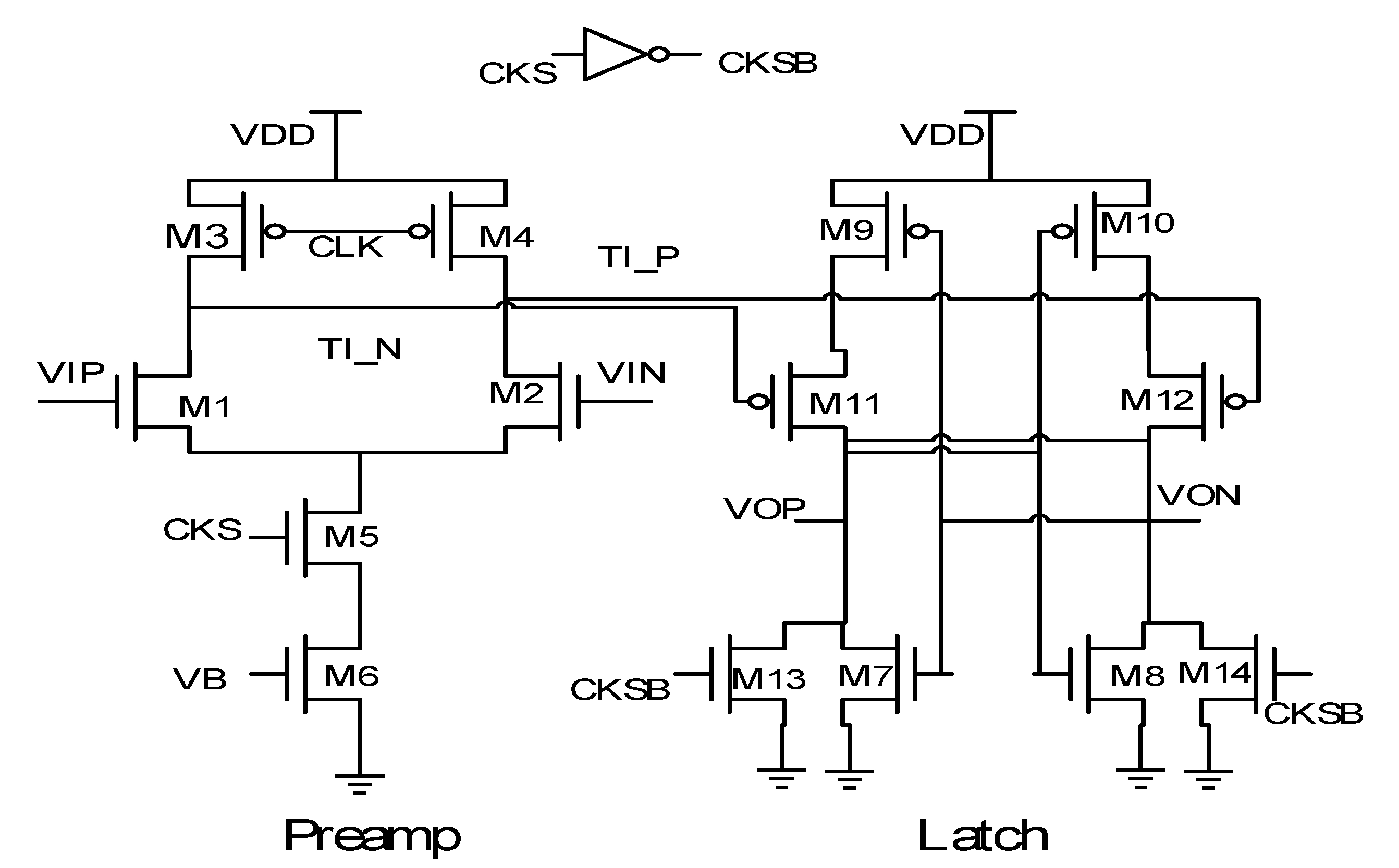

2.2. Bootstrapped Sample-and-Hold Circuit for Low-Power Application

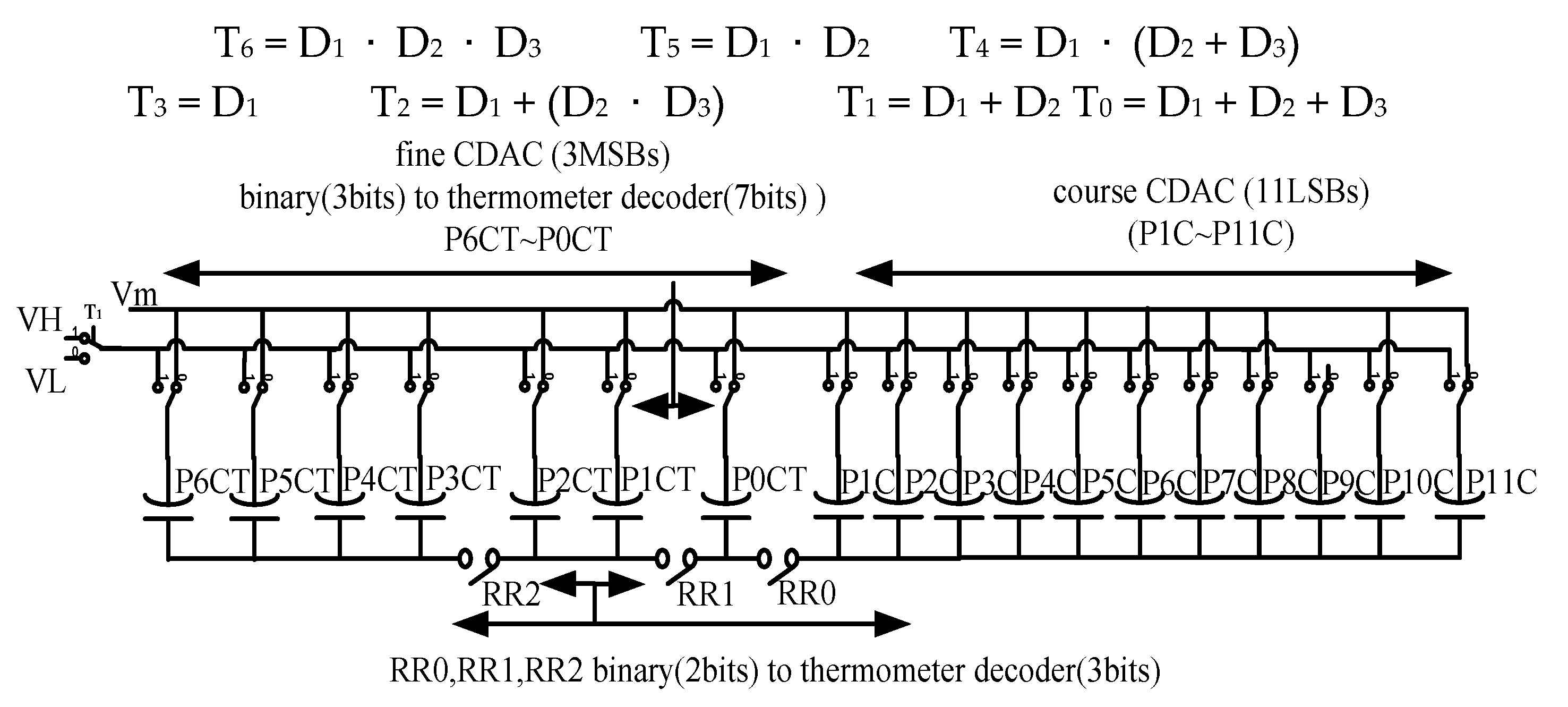

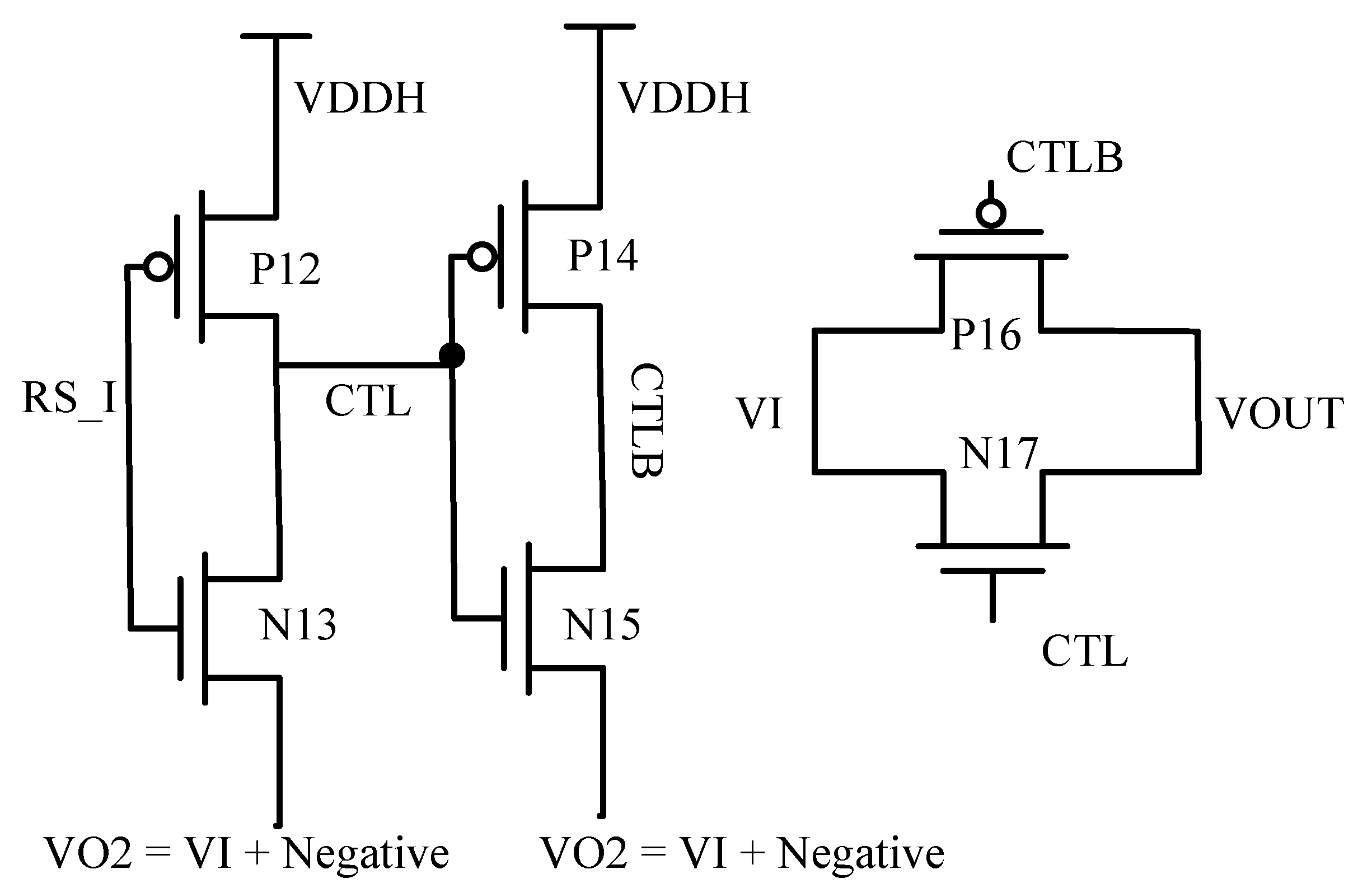

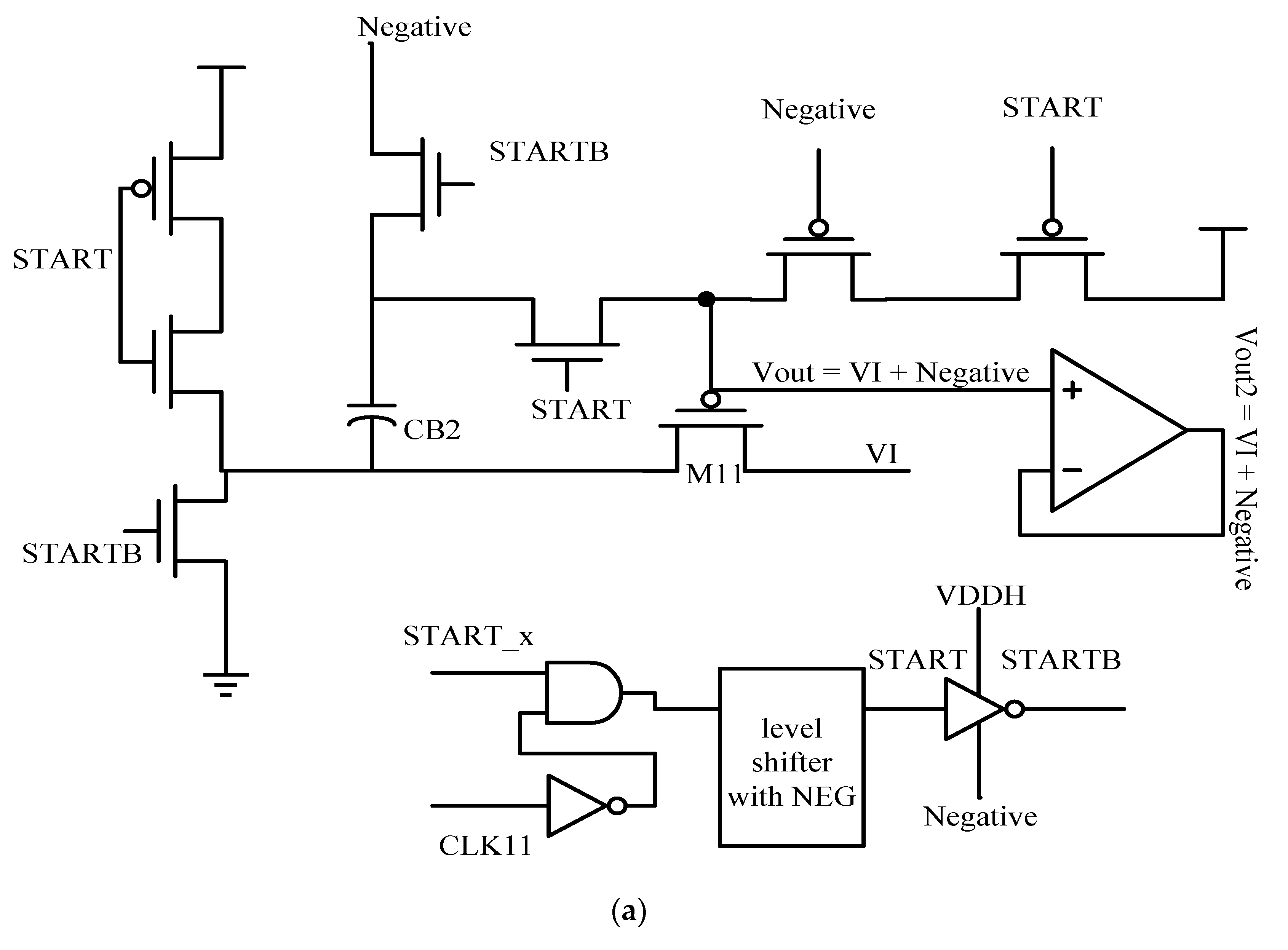

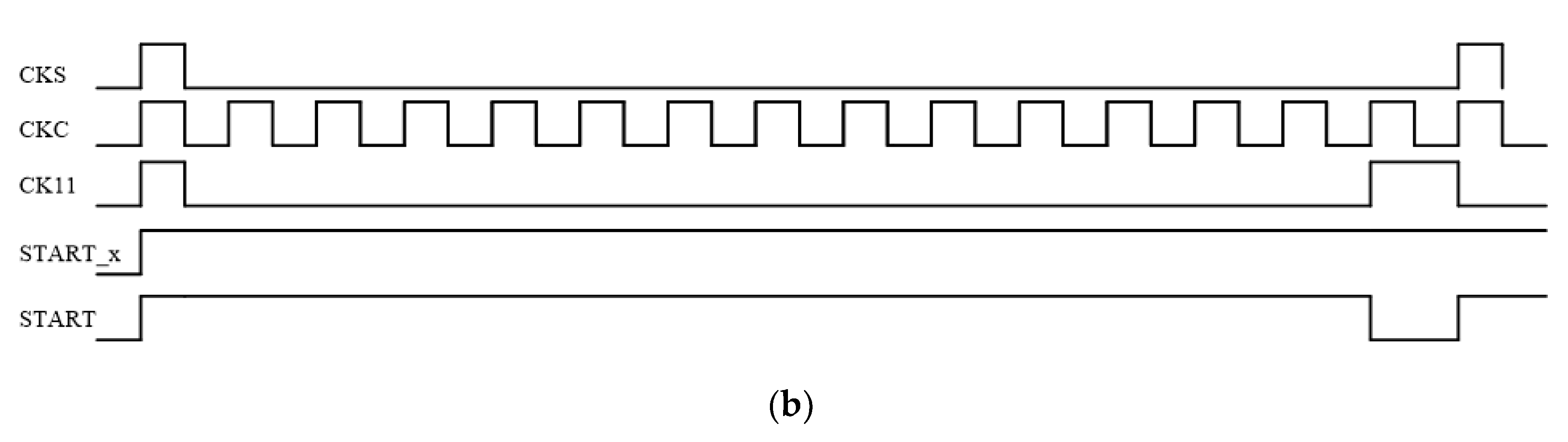

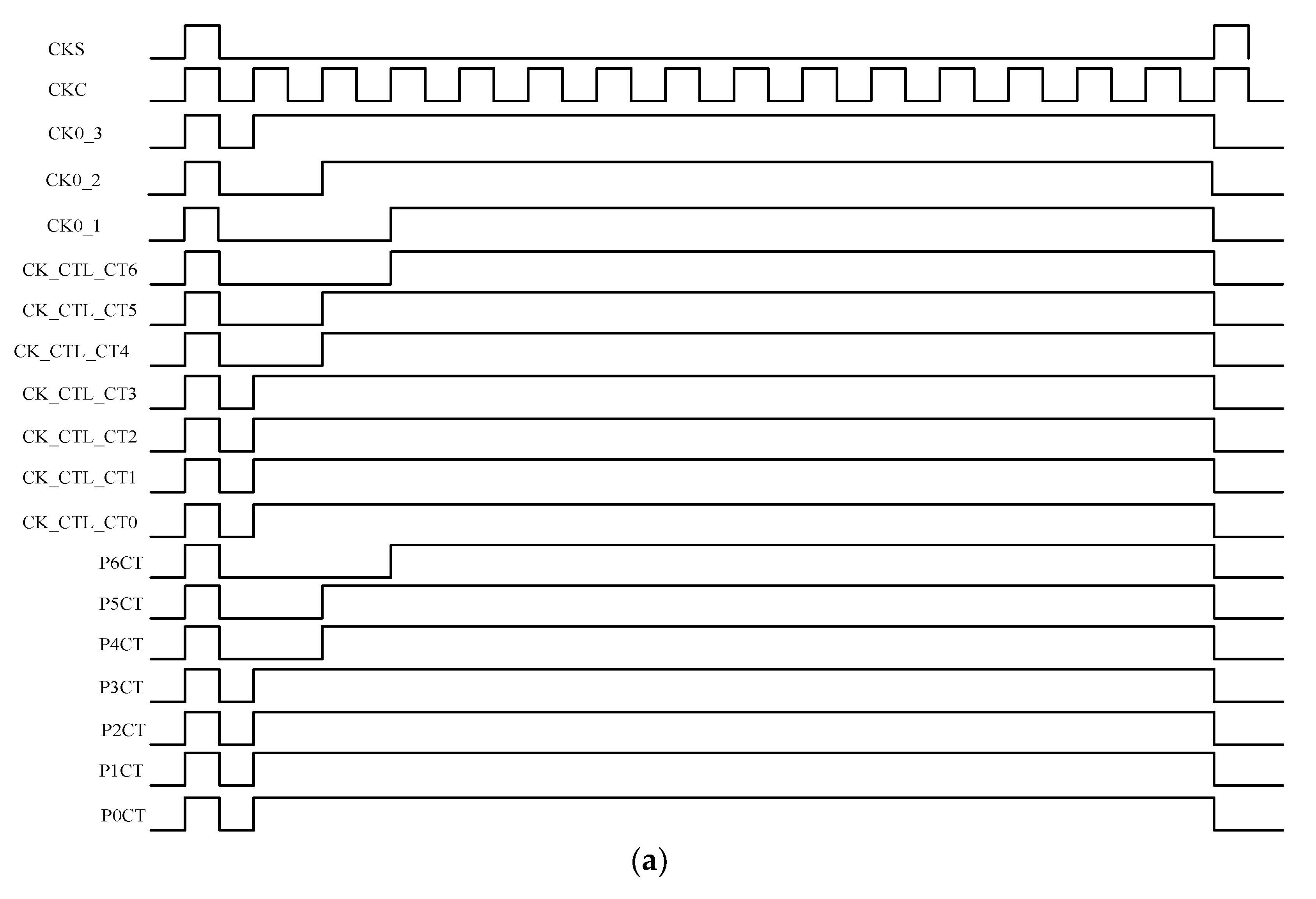

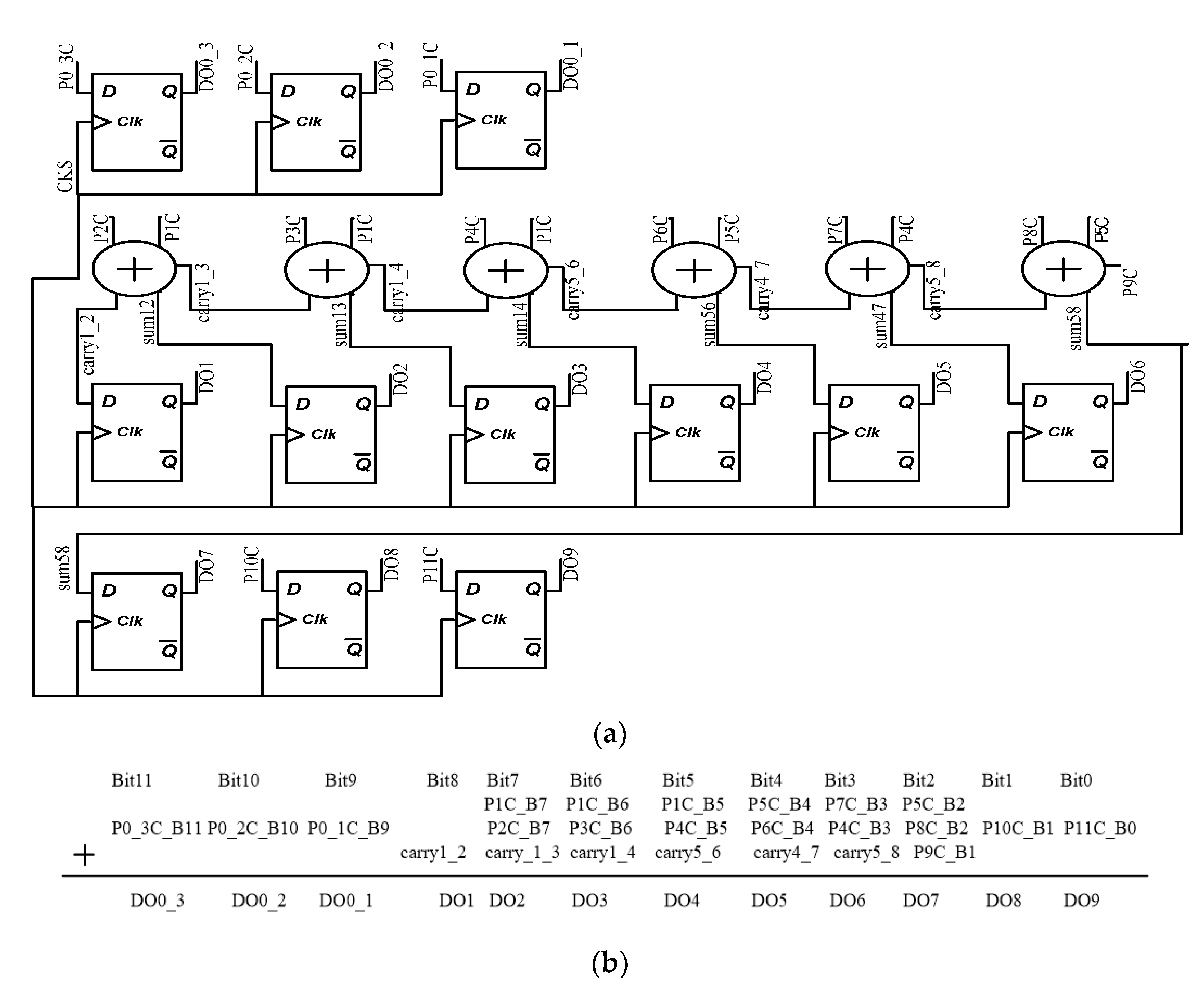

2.3. Fine Conversion Capacitive Digital-to-Analog Converter Control Logic, Reconfigurable Resolution (RR) Control Logic, Switch with NEG (SW-W-NEG), and the Input Signal Plus the Negative Voltage (VI + NEG) Voltage Generator

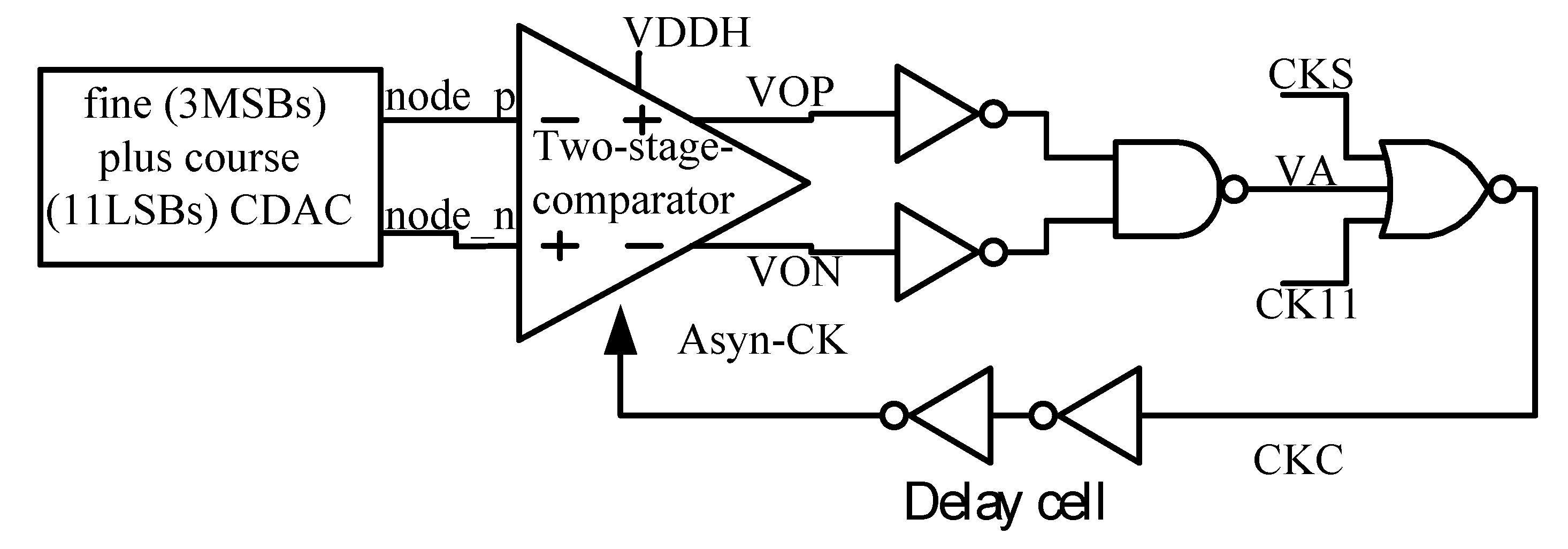

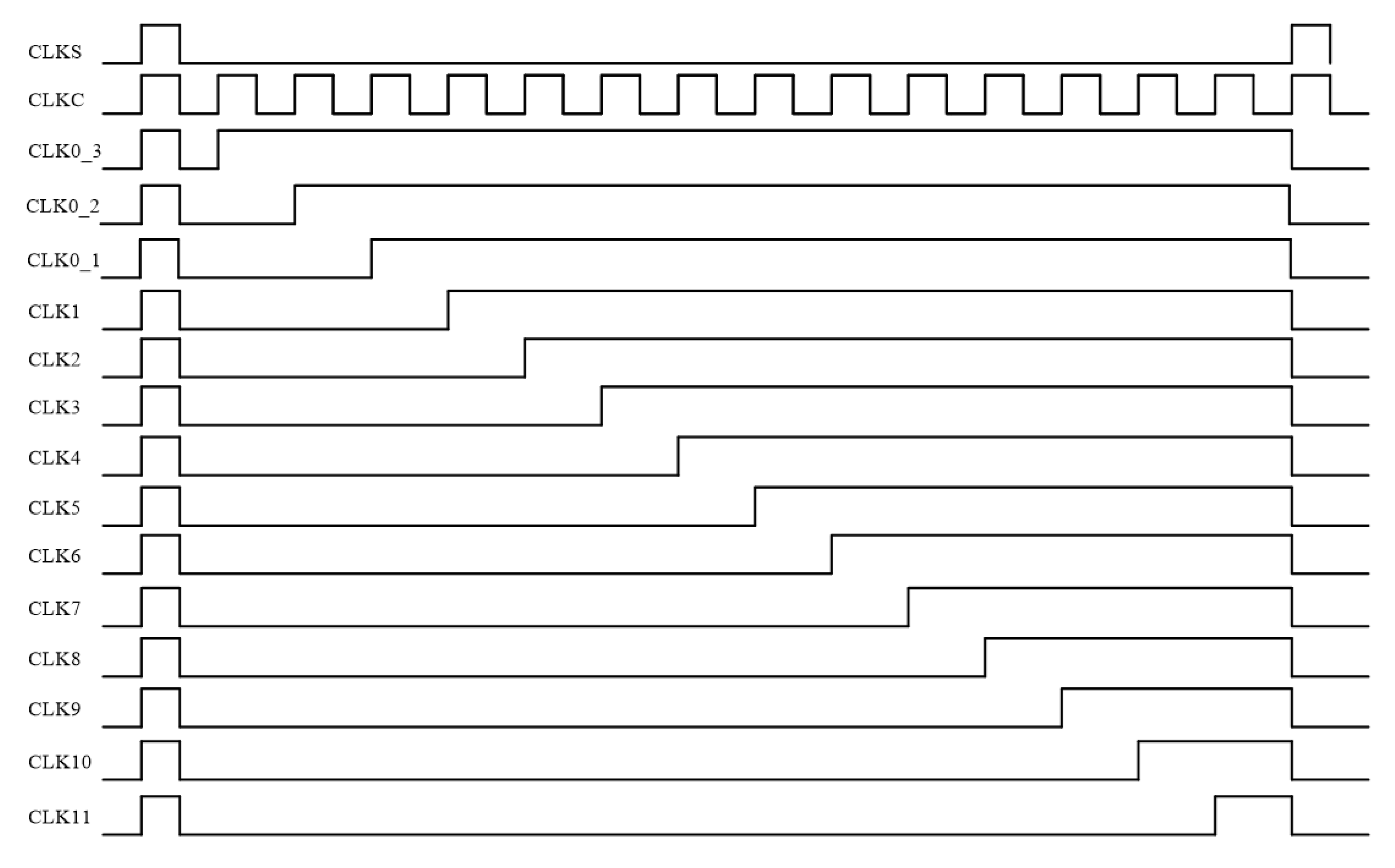

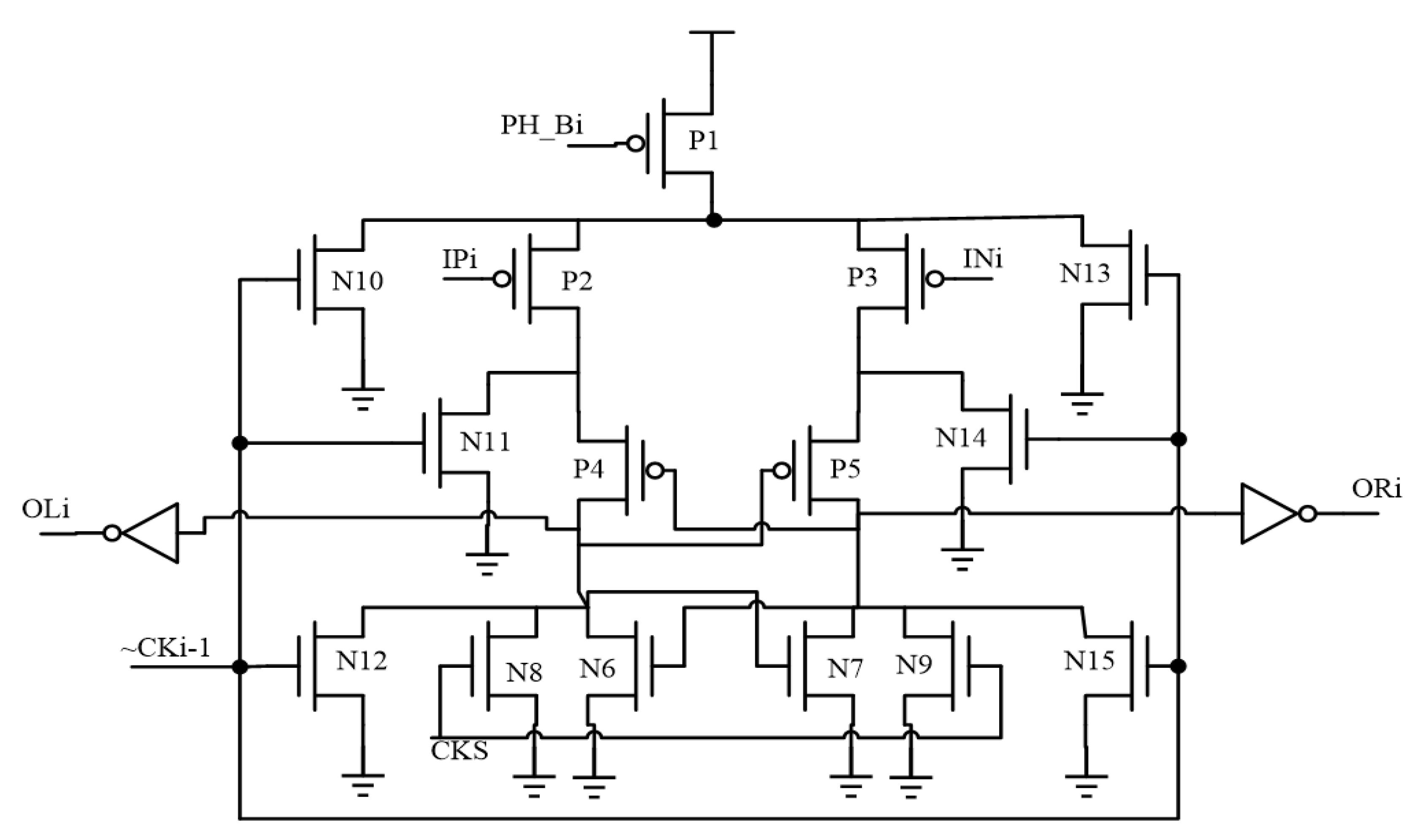

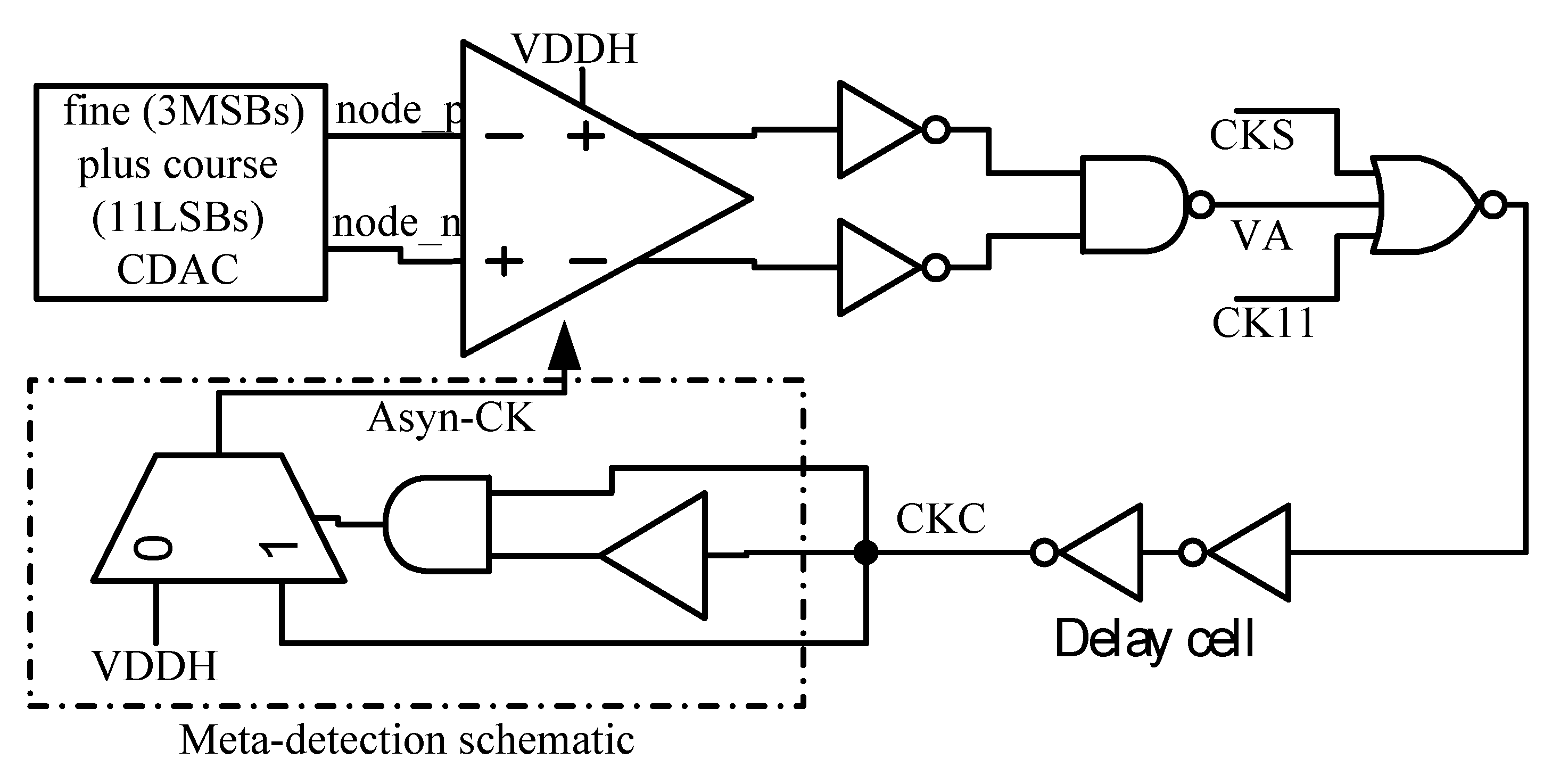

2.4. Internally Generated Clock, Multi-Phase Control Logic, Phase Control Logic, Fine Plus Course Conversion Switch Control Logic, Bit Control Logic, Meta-Detection, and Error Correction Schematic

2.5. Scalable Voltage Design

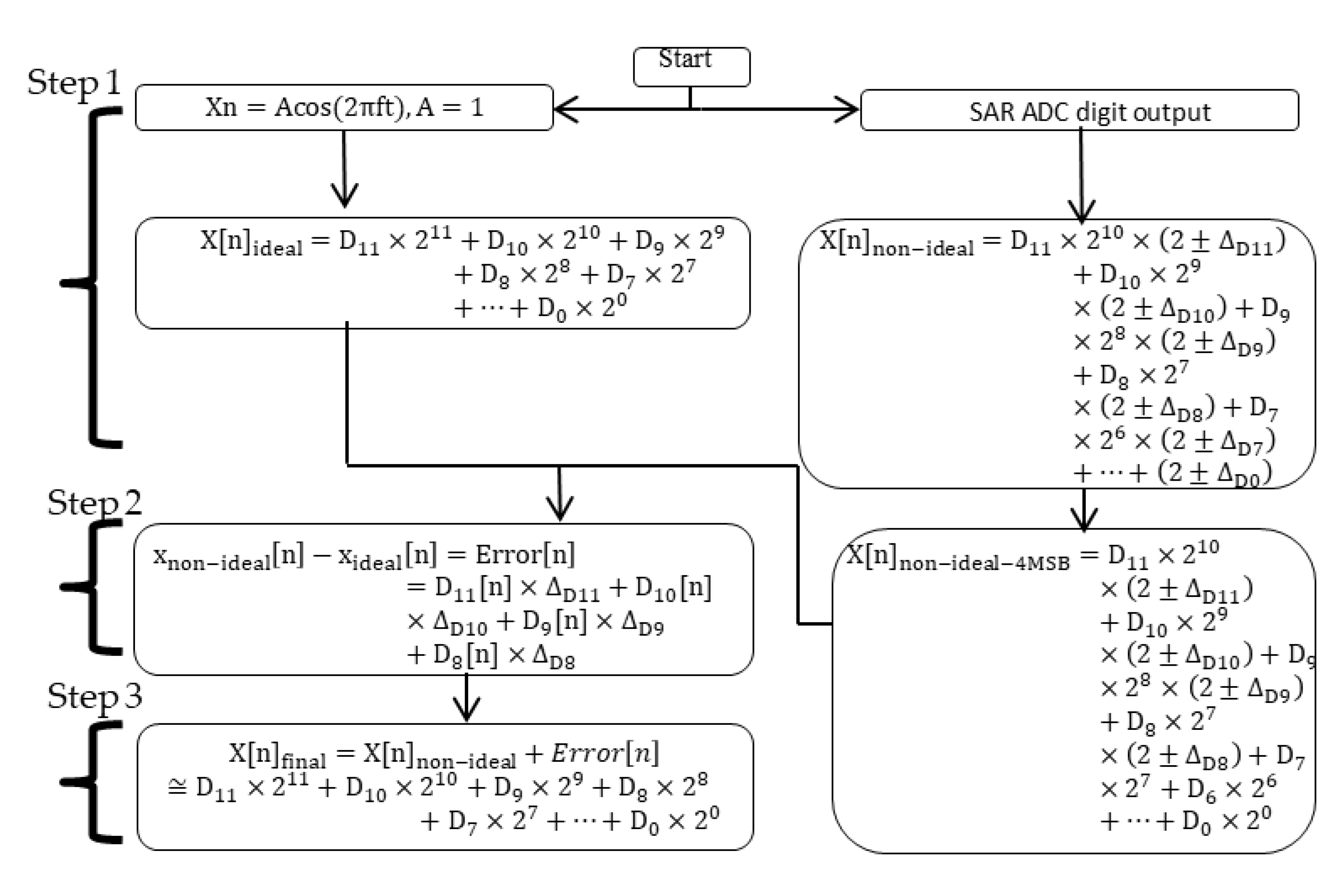

3. Discrete Fourier Transform-Based Calibration

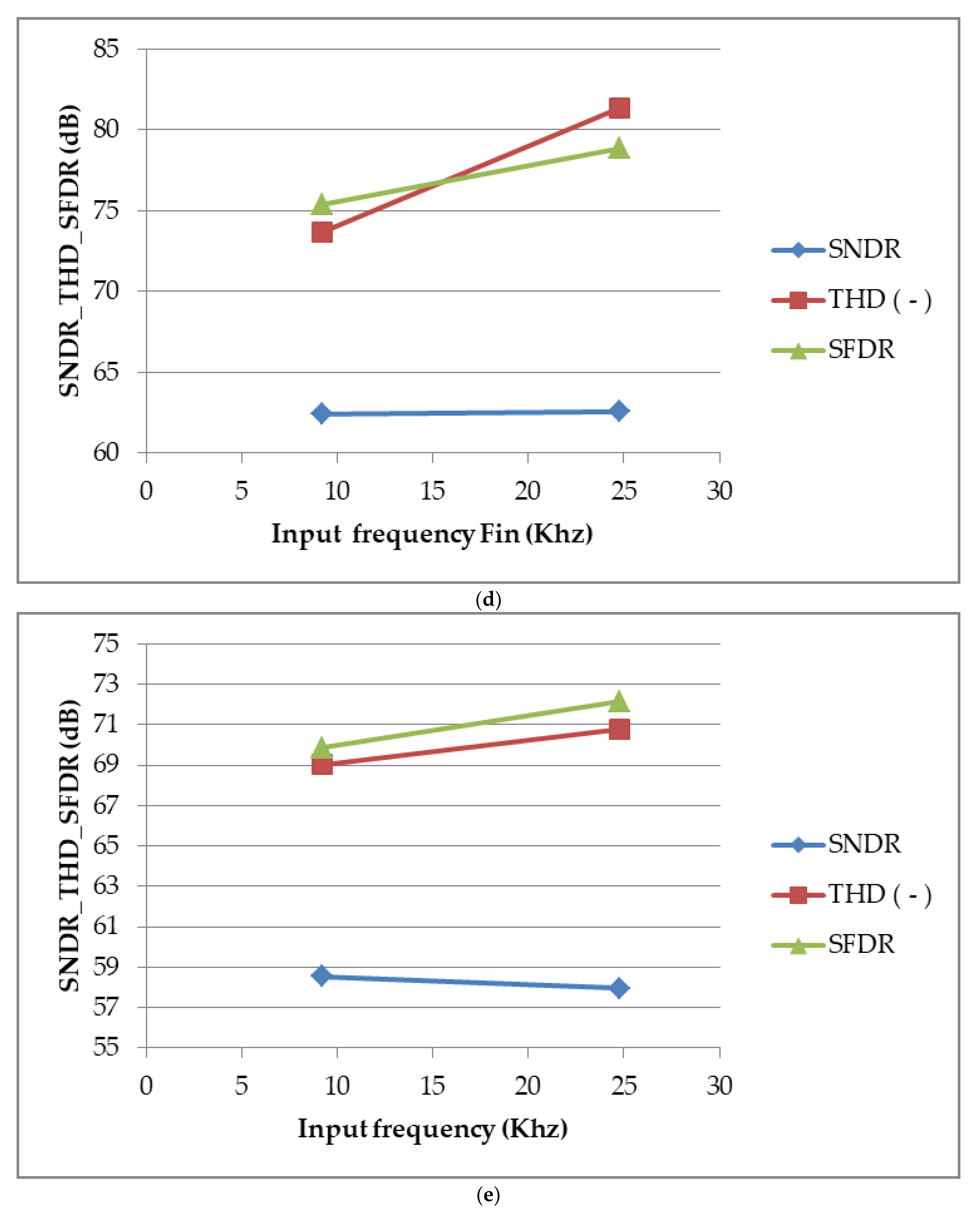

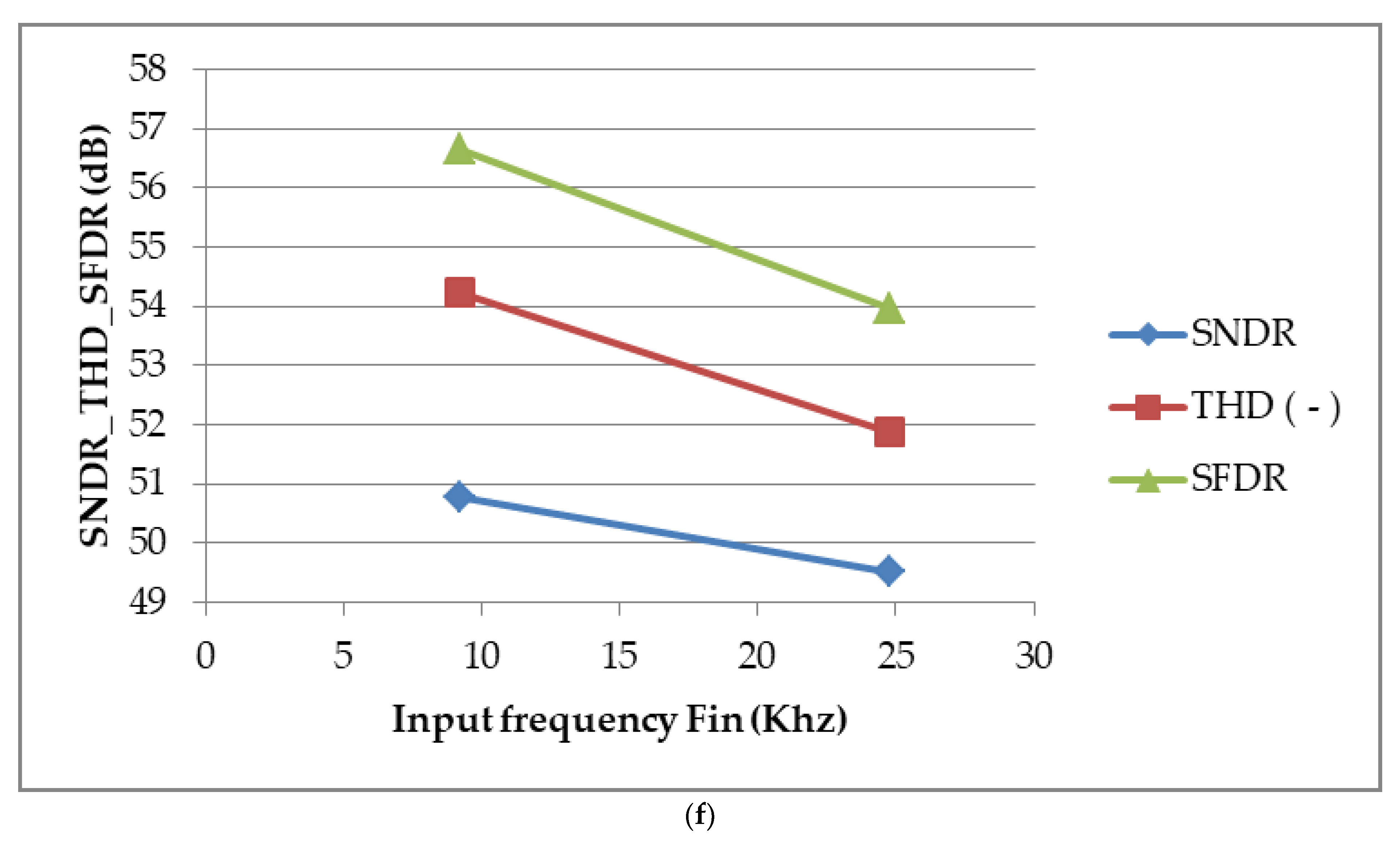

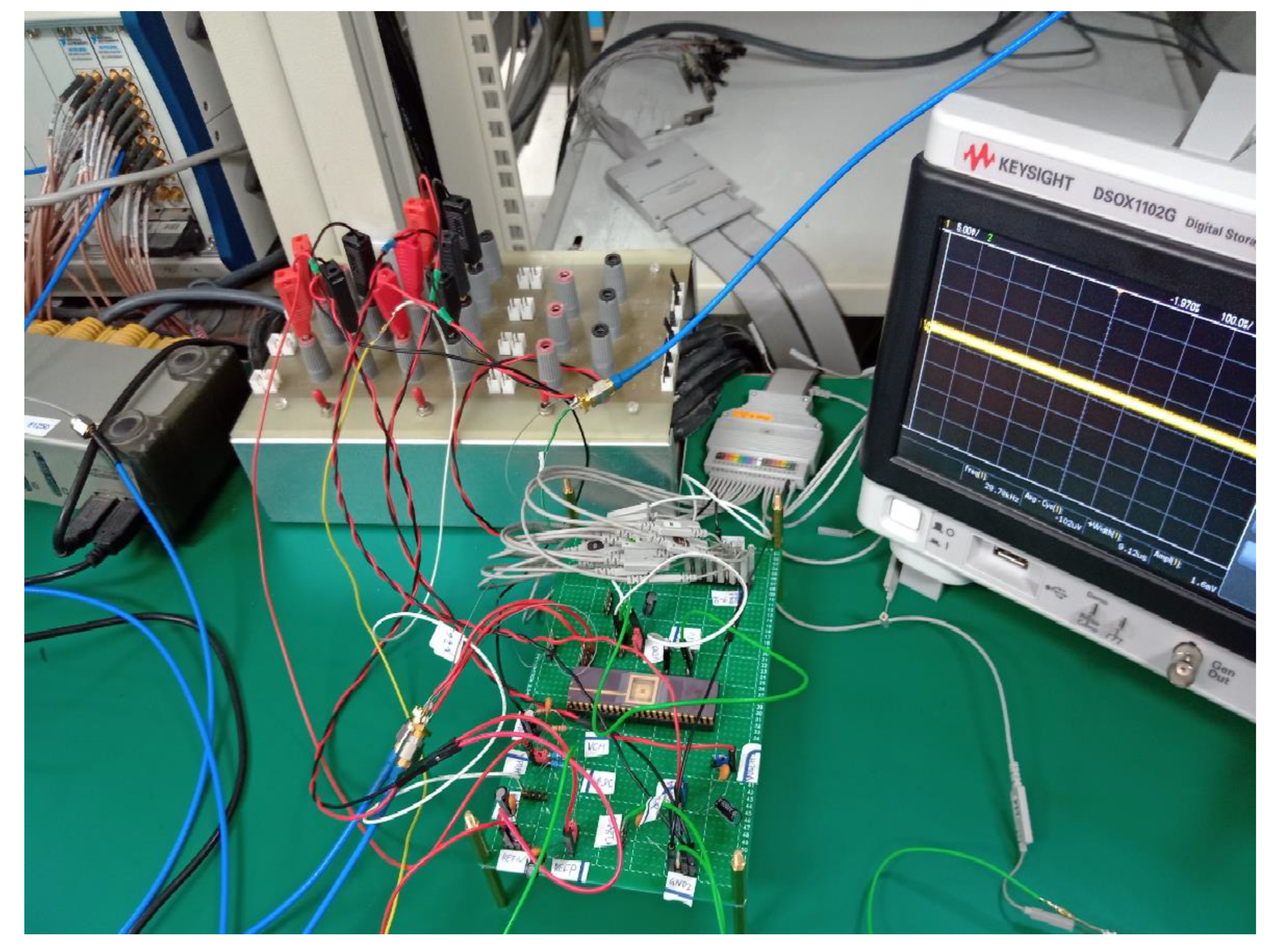

4. Measurement and Discussion

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Acknowledgments

Conflicts of Interest

References

- Aiello, O.; Crovetti, P.; Alioto, M. Fully Synthesizable Low-Area Analogue-to-Digital Converters with Minimal Design Effort Based on the Dyadic Digital Pulse Modulation. IEEE Access 2020, 8, 70890–70899. [Google Scholar] [CrossRef]

- Shehzad, K.; Verma, D.; Khan, D.; Ain, Q.U.; Basim, M.; Kim, S.J.; Pu, Y.; Hwang, K.C.; Yang, Y.; Lee, K.Y. Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator. Electronics 2020, 9, 872. [Google Scholar] [CrossRef]

- Dai, Z.; Svensson, C.; Alvandpour, A. Power Consumption Bounds for SAR ADCs. In Proceedings of the 2011 20th European Conference on Circuit Theory and Design, Linkoping, Sweden, 29–31 August 2011; pp. 556–559. [Google Scholar]

- Juan, Y.H.; Huang, H.Y.; Lai, S.C.; Juang, W.H.; Lee, S.Y.; Luo, C.H. A Distortion Cancelation Technique with the Recursive DFT Method for Successive Approximation Analog-to-Digital Converters. IEEE Trans. Circuits Syst. Express Briefs 2016, 63, 146–150. [Google Scholar] [CrossRef]

- Lin, H.M.; Lin, C.H.; Wen, K.A. A resolution-reconfigurable and power scalable SAR ADC with partial thermometer coded DAC. Adv. Sci. Technol. Eng. Syst. J. 2018, 3, 89–96. [Google Scholar] [CrossRef]

- Lin, H.M.; Wen, K.A. A Low Power Reconfigurable SAR ADC for CMOS MEMS Sensor. In Proceedings of the SoC Design Conference, Seoul, Korea, 5–8 November 2017; pp. 7–8. [Google Scholar]

- McCreary, J.L.; Gray, P.R. All-MOS charge redistribution analog-to-digital conversion techniques. IEEE J. Solid-State Circuits 1975, 10, 371–379. [Google Scholar] [CrossRef]

- Ginsburg, B.P.; Chandrakasan, A.P. An Energy-Efficient Charge Recycling Approach for a SAR Converter with Capacitive DAC. In Proceedings of the IEEE International Symposium on Circuits and Systems, Kobe, Japan, 23–26 May 2005; Volume 1, pp. 184–187. [Google Scholar]

- Lyu, Y.F. A Low Power 10-bit 500-KS/s Delta-Modulated Successive Approximation Register Analog-to-Digital Converter for Implantable Medical Devices. Master’s Thesis, Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, 2012. [Google Scholar]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Tsai, J.H.; Wang, H.H.; Yen, Y.C.; Lai, C.M.; Chen, Y.J.; Huang, P.C.; Chen, H.; Lee, C.C. A 0.003 mm2 10 b 240 MS/s 0.7 mW SAR ADC in 28 nm CMOS with digital error correction and correlated-reversed switching. IEEE J. Solid-State Circuits 2015, 50, 1382–1398. [Google Scholar] [CrossRef]

- Haenzsche, S.; Schüffny, R. Analysis of a Charge Redistribution SAR ADC with Partial Thermometer Coded DAC. In Proceedings of the European Conference on Circuit Theory and Design, Dresden, Germany, 8–12 September 2013; pp. 1–4. [Google Scholar]

- Tran, C.Q.; Kawaguchi, H.; Sakurai, T. Low-Power High-Speed Level Shifter Design for Block-Level Dynamic Voltage Scaling Environment. In Proceedings of the 2005 International Conference on Integrated Circuit Design and Technology, Austin, TX, USA, 9–11 May 2005; pp. 229–232. [Google Scholar]

- Wang, S.; Dehollain, C. Design of a Rail-to-Rail 460 kS/s 10-bit SAR ADC for Capacitive Sensor Interface. In Proceedings of the IEEE 20th International Conference on Electronics, Circuits, and Systems, Abu Dhabi, UAE, 8–11 December 2013; pp. 453–456. [Google Scholar]

- Van Elzakker, M.; van Tuijl, E.; Geraedts, P.; Schinkel, D.; Klumperink, E.A.M.; Nauta, B. A 10-bit Charge-Redistribution ADC Consuming 1.9 μW at 1 MS/s. IEEE J. Solid-State Circuits 2010, 45, 1007–1015. [Google Scholar] [CrossRef]

- Yip, M.; Chandrakasan, A.P. A resolution-reconfigurable 5- to -10-bit 0.4- to -1 V power scalable SAR ADC for sensor applications. IEEE J. Solid-State Circuits 2013, 48, 1453–1464. [Google Scholar] [CrossRef]

- Lee, S.Y.; Liang, M.C.; Hsieh, C.H. FFT-based calibration method for 1.5 bit/stage pipelined ADCs. Int. J. Circuit Theory Appl. 2015, 43, 455–469. [Google Scholar] [CrossRef]

| [3] | [4] | [5] | [1] | [2] | SAR-ADC-WFC-CDA | ||

|---|---|---|---|---|---|---|---|

| Resolution | 10 bits | 12 bits | 12 bits | 6.4 bits | 6.7 bits | 12 bits | 9/10/11/12 bits |

| Process | 0.13 μm | 0.18 μm | 0.18 μm | 0.04 μm | 0.04 μm | 0.055 μm | 0.18 μm |

| Analog, digital | 1.0 V, 0.4 V | 1.8 V, - | 1.8 V, 0.9 V | -, 1.0 V | -, 0.6 V | 1 V, 1 V | 1.5 V, 0.9 V |

| Layout zone | 0.19 mm2 | 2.38 mm2 | 0.35 mm2 | 3000 μm2 | 4970 μm2 | 0.039 mm2 | 0.052 mm2 |

| Fs | 1 KS/s | 200 KS/s | 50 KS/s | 2.8 KS/s | 2.2 KS/s | 1 MS/s | 50 KS/s |

| SNDR | 56.54 dB | 69.6 dB | 68.6 dB | 40.4 dB | 42.1 dB | 59.3 dB | 50.78/58.53/62.42/66.51 dB |

| Power | 0.05 μW | 41.5 μW | 9.7 μW | 7.3 uW | 0.94 uW | 108uW | –/–/–/2.7 μW |

| FoM | 94.5 fJ/conversion | 84.6 fJ/conversion | 88.4 fJ/conversion | 30,900 fJ/conversion | 4110 fJ/conversion | 17.8/conversion | –/–/–/30.5 fJ/conversion |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, C.-H.; Wen, K.-A. An Innovative Successive Approximation Register Analog-to-Digital Converter for a Nine-Axis Sensing System. J. Low Power Electron. Appl. 2021, 11, 3. https://doi.org/10.3390/jlpea11010003

Lin C-H, Wen K-A. An Innovative Successive Approximation Register Analog-to-Digital Converter for a Nine-Axis Sensing System. Journal of Low Power Electronics and Applications. 2021; 11(1):3. https://doi.org/10.3390/jlpea11010003

Chicago/Turabian StyleLin, Chih-Hsuan, and Kuei-Ann Wen. 2021. "An Innovative Successive Approximation Register Analog-to-Digital Converter for a Nine-Axis Sensing System" Journal of Low Power Electronics and Applications 11, no. 1: 3. https://doi.org/10.3390/jlpea11010003

APA StyleLin, C.-H., & Wen, K.-A. (2021). An Innovative Successive Approximation Register Analog-to-Digital Converter for a Nine-Axis Sensing System. Journal of Low Power Electronics and Applications, 11(1), 3. https://doi.org/10.3390/jlpea11010003