Energy Efficient Supply Boosted Comparator Design

Abstract

:1. Introduction

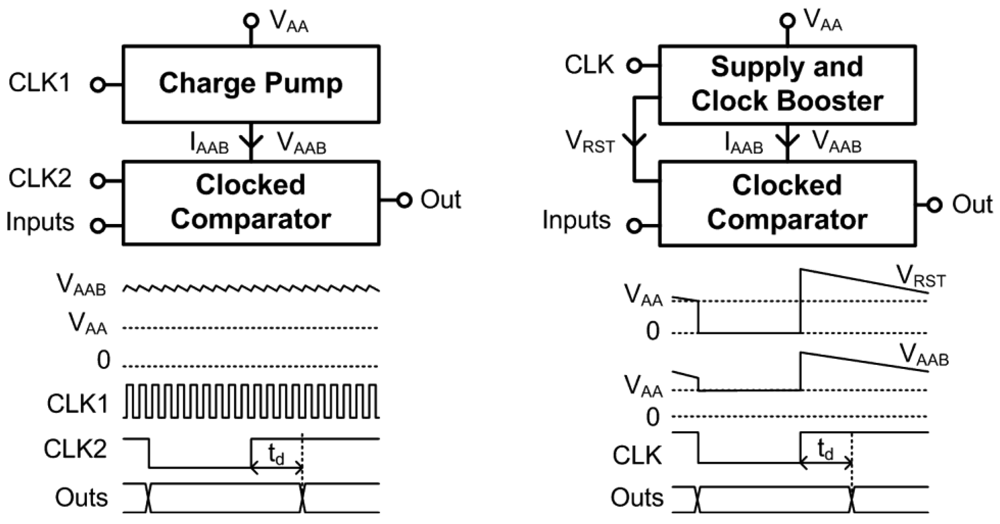

2. Supply Boosting Technique (SBT)

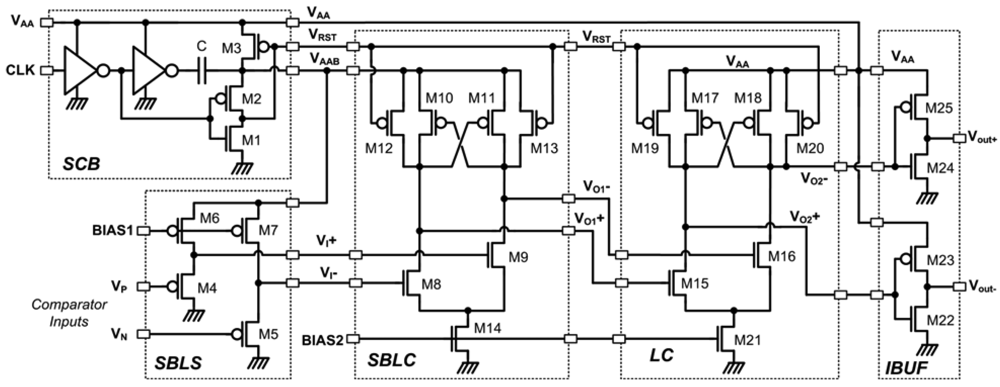

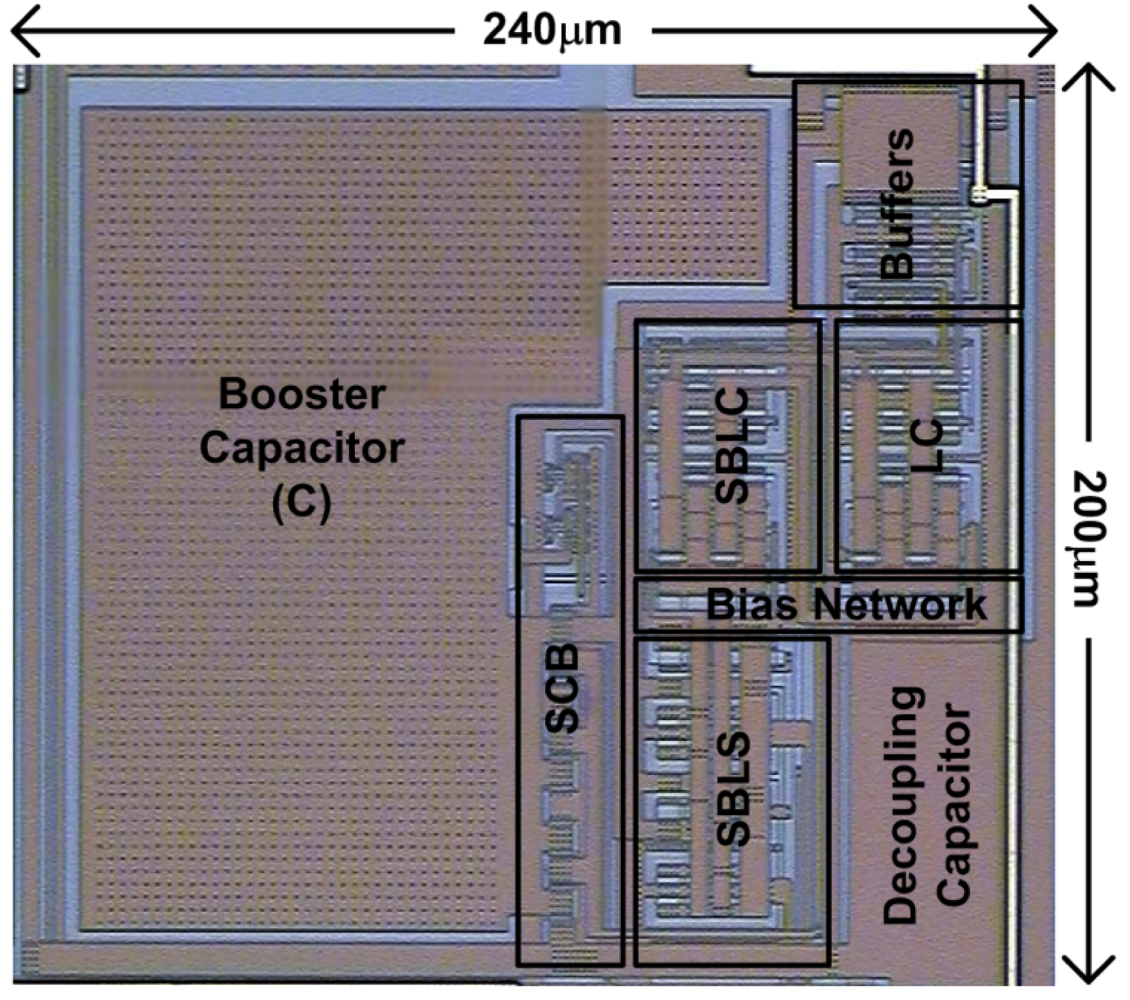

3. Supply Boosted Comparator (SBC) Design

3.1. Supply and Clock Booster (SCB) Circuit

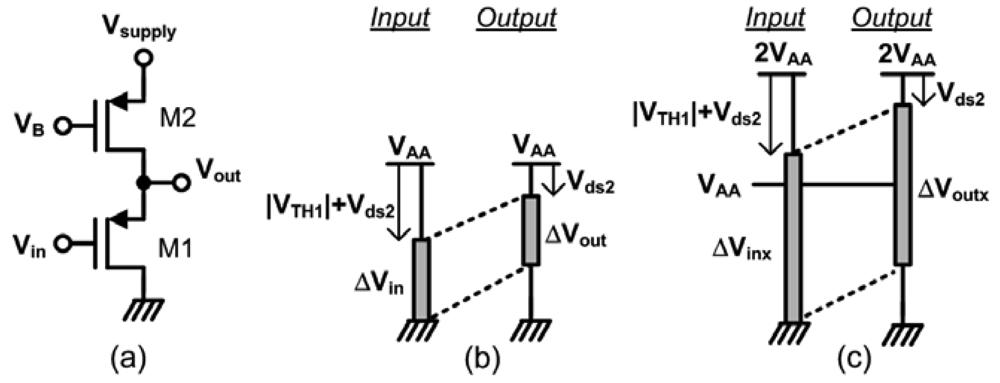

3.2. Supply Boosted Level Shifter (SBLS) Circuit

3.3. Latched Comparator (LC)

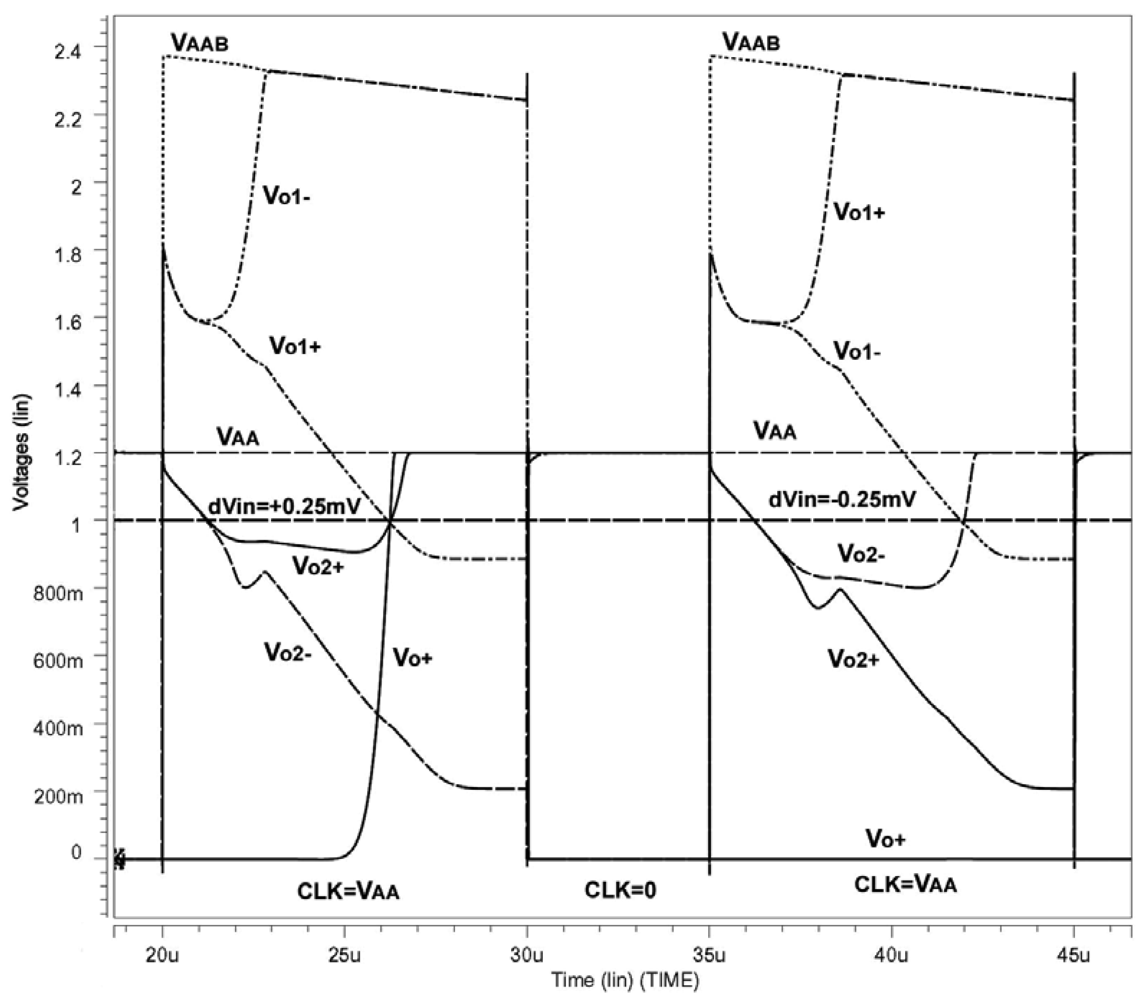

3.4. SBC Design and Simulation

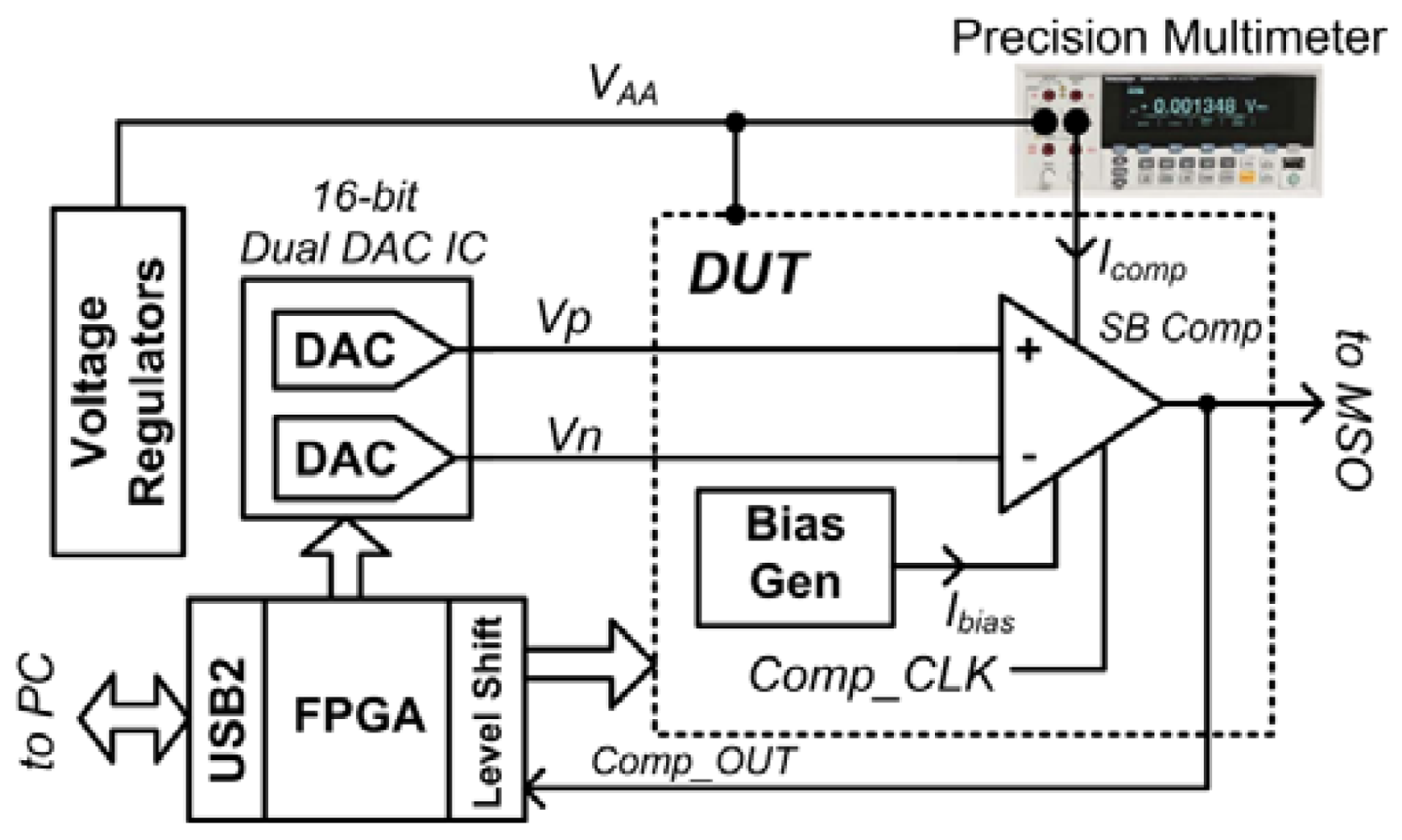

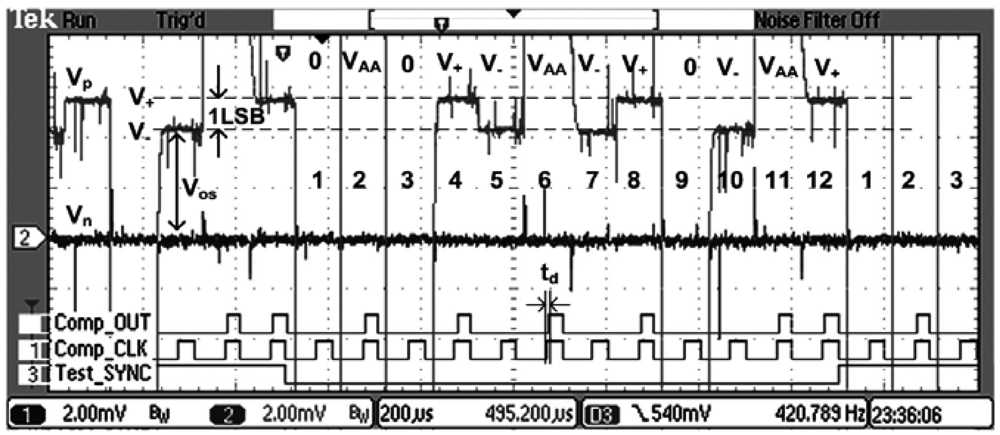

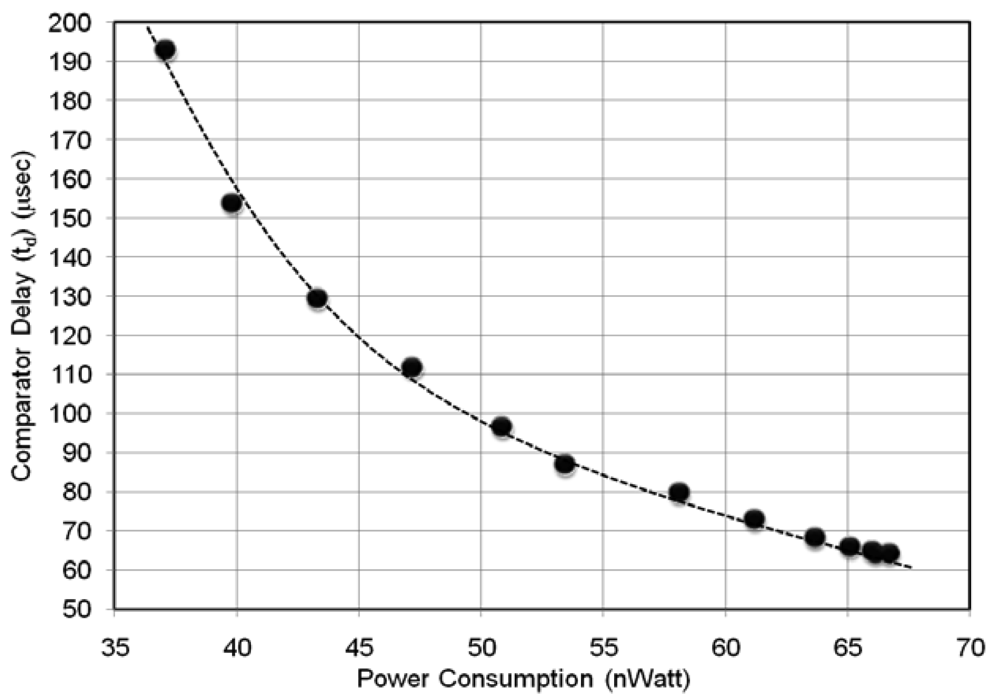

4. Measurement Results and Discussion

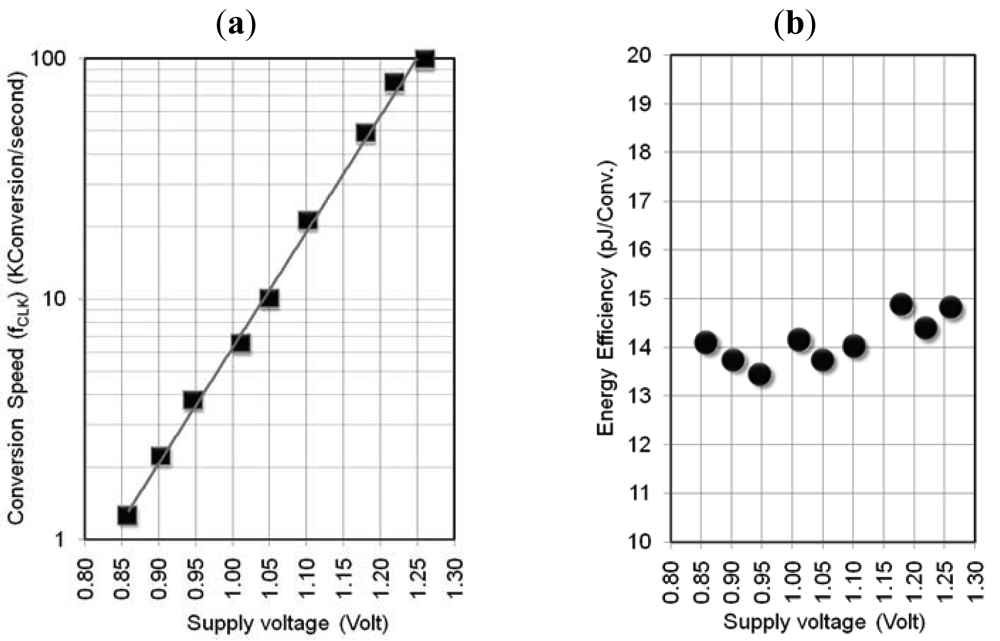

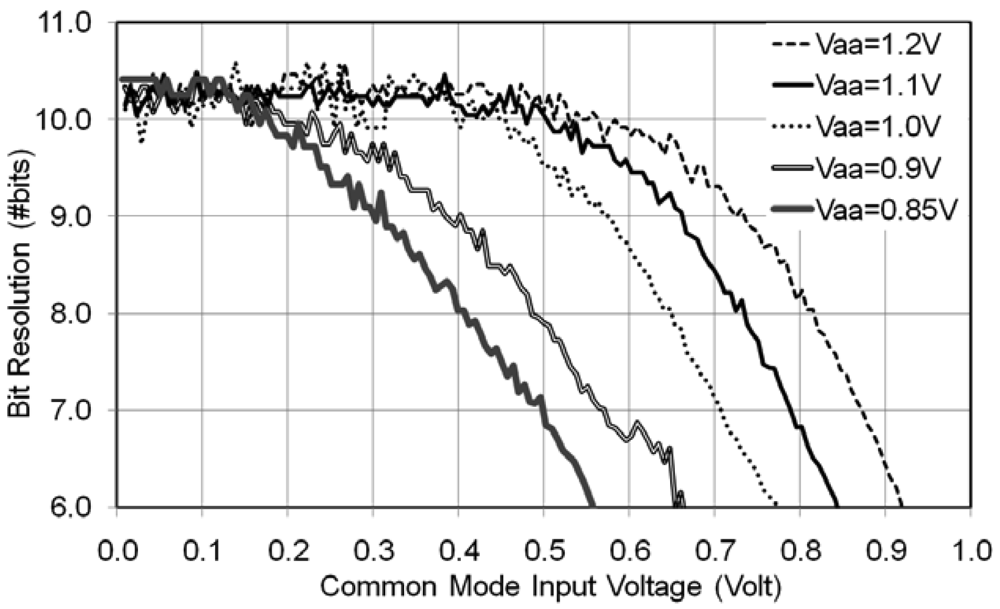

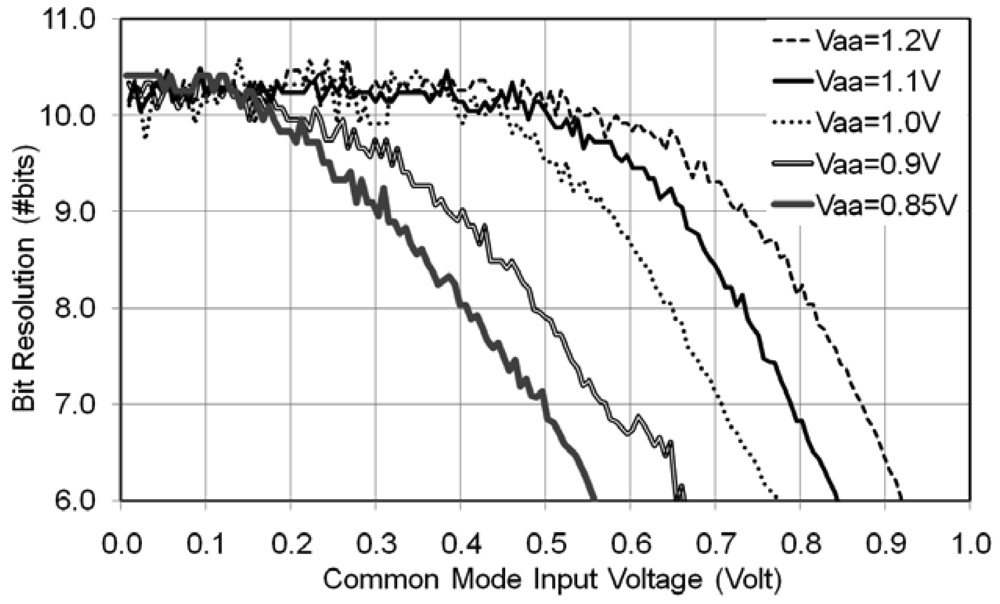

Measurement Results

5. Conclusion

| Device | Width (μm) | Length (μm) | M |

|---|---|---|---|

| M1 | 6.0 | 0.6 | 2 |

| M2–3 | 6.0 | 0.6 | 4 |

| M4–5,10–11,17–18 | 6.0 | 1.2 | 8 |

| M6–7,14,21 | 6.0 | 3.0 | 2 |

| M8–9,15–16 | 6.0 | 1.5 | 8 |

| M23,25 | 6.0 | 0.9 | 8 |

| M22,24 | 6.0 | 1.2 | 4 |

| M12–13,19–20 | 6.0 | 0.6 | 1 |

| Parameters | this Work | Ref. [20] | Ref. [5] | Unit |

|---|---|---|---|---|

| CMOS Process Technology | 0.50 | 0.50 | 0.25 | μm |

| tdreshold voltage (N/P) | +0.8/−0.9 | +0.74/−0.85 | +0.48/−0.6 | Volt |

| Supply Voltage | 1.0 | 1.0 | 1.0 | Volt |

| Supply Voltage Range | >0.85 | >1.0 | >1.0 | Volt |

| Input Range (VCMI) | 0.75 | 1.0 | 1.0 | Volt |

| Conversion Speed | 6.5 | 250 | 1000 a | KC/s |

| Power Consumption | 0.09 | 5.0 | 21.0 | μWatt |

| Energy Efficiency | 14.0 | 20.0 | 21.0 | pJ/C |

| Layout Area (LA) | 0.048 | 0.037 | 0.024 | mm2 |

| Normalized Area b | 133,300 c | 147,200 | 384,000 | - |

Acknowledgments

References

- Bechen, B.; Boom, T.V.D.; Weiler, D.; Hosticka, B.J. Theoretical and Practical Minimum of the Power Consumption of 3 ADCs in SC Technique. Proceedings of the 18th European Conference on Circuit Theory and Design, Sevilla, Spain, 27–30 August 2007; pp. 444–447.

- Wang, A.; Calhoun, B.H.; Chandrakasan, A.P. Sub-Threshold Design for Ultra Low-Power Systems; Springer: New York, NY, USA, 2006. [Google Scholar]

- Chang, L.; Frank, D.J.; Montoye, R.K.; Koester, S.J.; Ji, B.J.; Coteus, P.W.; Dennard, R.H.; Haensch, W. Practical strategies for power-efficient computing technologies. Proc. IEEE 2010, 98, 215–236. [Google Scholar]

- Hung, Y.C.; Liu, B.D. A low-voltage wide-input CMOS comparator for sensor application using back-gate technique. Biosens. Bioelectron. 2004, 20, 53–59. [Google Scholar]

- Baschirotto, A.; Castello, R. A 1-V 1.8-MHz CMOS switched-opamp SC filter with rail-to-rail output swing. IEEE J. Solid-State Circuits 1997, 32, 1979–1986. [Google Scholar]

- Huang, C.J.; Huang, H.Y. A Low-Voltage CMOS Rail-to Rail Operational Amplifier Using Double P-Channel Differential Input Pairs. Proceedings of the 2004 IEEE International Symposium on Circuits and Systems (ISCAS), Vancouver, Canada, 23–26 May 2004; 1, pp. 673–676.

- Abo, A.; Gray, P. A 1.5-V, 10-bit, 14-MS/s CMOS pipeline analog-to-digital converter. IEEE J. Solid-State Circuits 1999, 34, 599–606. [Google Scholar]

- Mortezapour, S.; Lee, E.K.F. A 1-V 8-bit successive approximation ADC in standard CMOS process. IEEE J. Solid-State Circuits 2000, 35, 642–646. [Google Scholar]

- Duisters, T.A.F.; Dijkmans, E.C. A-90-dB THD rail-to-rail input OPAMP using a new local charge pump in CMOS. IEEE J. Solid-State Circuits 1998, 33, 947–955. [Google Scholar]

- Pierre, R.S. Low-power BiCMOS op amp with integrated current mode charge pump. IEEE J. Solid State Circuits 2000, 35, 1046–1050. [Google Scholar]

- Lotfi, R.; Taherzadeh-Sani, M.; Azizi, M.Y.; Shoaei, O. A 1-V MOSFET-Only Fully-Differential Dynamic Comparator for Use in Low-Voltage Pipelined A/D Converters. Proceedings of the 2003 International Symposium on Signals, Circuits and Systems (SCS), Lasi, Romania, 10–11 July 2003; 2, pp. 377–380.

- Lee, S.C.; Park, D.S.; Song, J.H.; Choi, M.W.; Lee, S.H. A Low-Ripple Switched-Capacitor DC-DC up Converter for Low-Voltage Applications. Proceedings of the Second IEEE Asia Pacific Conference on ASICs, Cheju, South Korea, 28–30 August 2000; pp. 13–16.

- Mesgarani, A.; Alam, M.N.; Nelson, F.Z.; Ay, S.U. Supply Boosting Technique for Designing Very Low-Voltage Mixed-Signal Circuits in Standard CMOS. Proceedings of the 2010 IEEE Midwest Symposium on Circuits and Systems (MWSCAS), Seattle, WA, USA, 1–4 August 2010; pp. 893–896.

- Ay, S.U. A sub-1Volt 10-bit Supply Boosted SAR ADC Design in Standard CMOS. Int. J. Analog Integr. Circuits Signal Process. 2010, 66, 213–221. [Google Scholar]

- Ay, S.U. A 1.32 pW/frame pixel 1.2 V CMOS Energy Harvesting and Imaging (EHI) APS Imager. Proceedings of the 2011 IEEE International Solid- State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 116–117.

- Senderowicz, D.; Nicollini, G.; Pernici, S.; Nagari, A.; Confalonieri, P.; Davalle, C. Low-Voltage Double-Sampled ΣΔ Converters Applications. Proceedings of the 1997 IEEE International Solid- State Circuits Conference, San Francisco, CA, USA, 6–8 February 1997; pp. 210–211.

- Figueiredo, P.M.; Vital, J.C. Kickback noise reduction techniques for CMOS latched comparators. IEEE Trans. Circuits Syst. II 2006, 53, 541–545. [Google Scholar]

- Cho, T.; Gray, P. A 10 b, 20 M sample/s, 35 mW pipeline A/D converter. IEEE J. Solid-State Circuits 1995, 30, 166–172. [Google Scholar]

- MOSIS Homepage. Available online: http://www.mosis.com (accessed on 23 June 2011).

- Fayomi, C.J.B.; Roberts, G.W.; Sawan, M. Low Power/Low Voltage High Speed CMOS Differential Track and Latch Comparator with Rail-to-Rail Input. Proceedings of the 2000 IEEE International Symposium on Circuits and Systems, Geneva, Switzerland, 28–31 May 2000; 5, pp. 653–656.

© 2011 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Ay, S.U. Energy Efficient Supply Boosted Comparator Design. J. Low Power Electron. Appl. 2011, 1, 247-260. https://doi.org/10.3390/jlpea1020247

Ay SU. Energy Efficient Supply Boosted Comparator Design. Journal of Low Power Electronics and Applications. 2011; 1(2):247-260. https://doi.org/10.3390/jlpea1020247

Chicago/Turabian StyleAy, Suat U. 2011. "Energy Efficient Supply Boosted Comparator Design" Journal of Low Power Electronics and Applications 1, no. 2: 247-260. https://doi.org/10.3390/jlpea1020247

APA StyleAy, S. U. (2011). Energy Efficient Supply Boosted Comparator Design. Journal of Low Power Electronics and Applications, 1(2), 247-260. https://doi.org/10.3390/jlpea1020247