TCAD Simulation of the Doping-Less TFET with Ge/SiGe/Si Hetero-Junction and Hetero-Gate Dielectric for the Enhancement of Device Performance

Abstract

1. Introduction

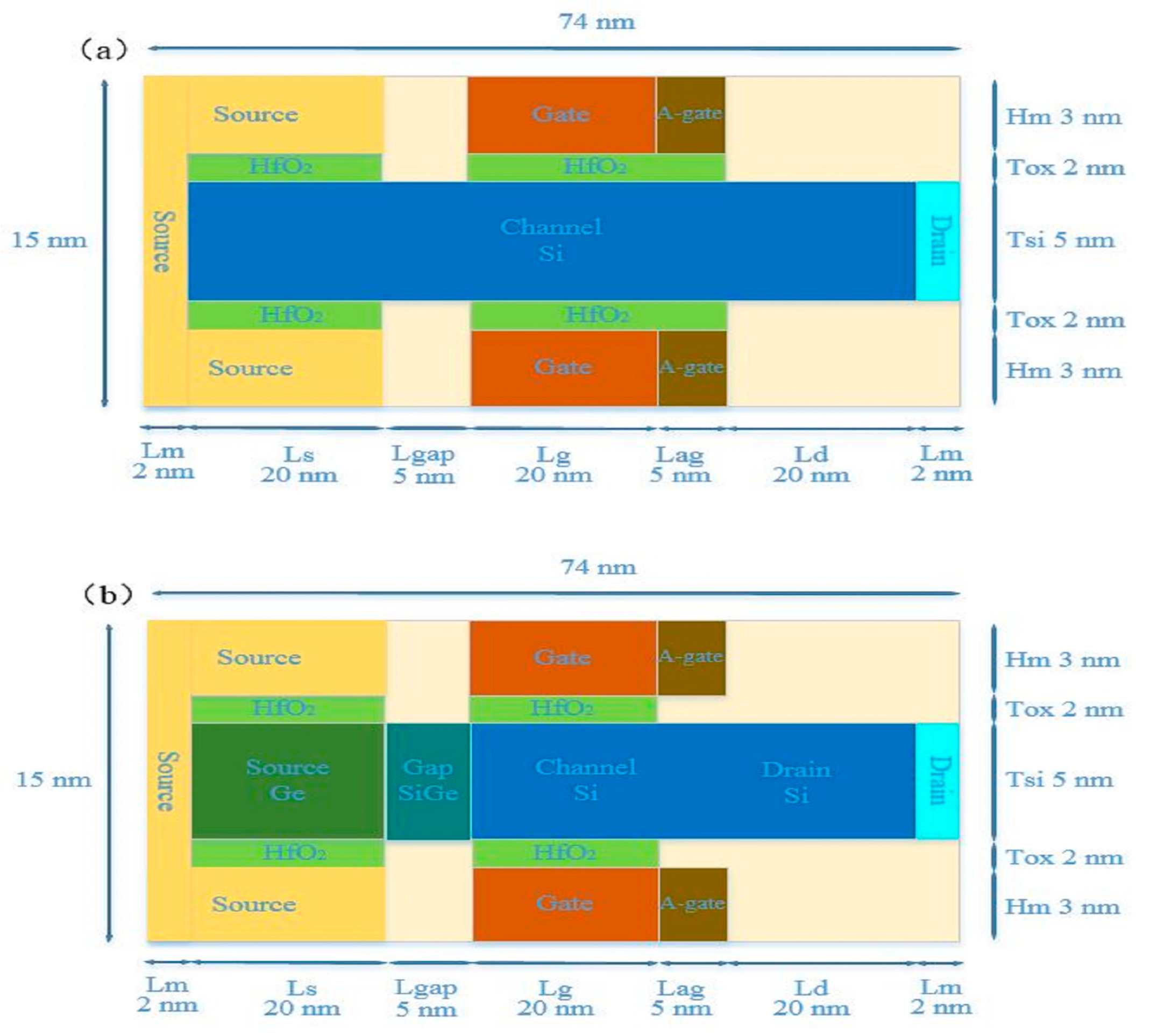

2. The Device Structure of DLTFET and H-DLTFET

3. Discussion of Simulation Results

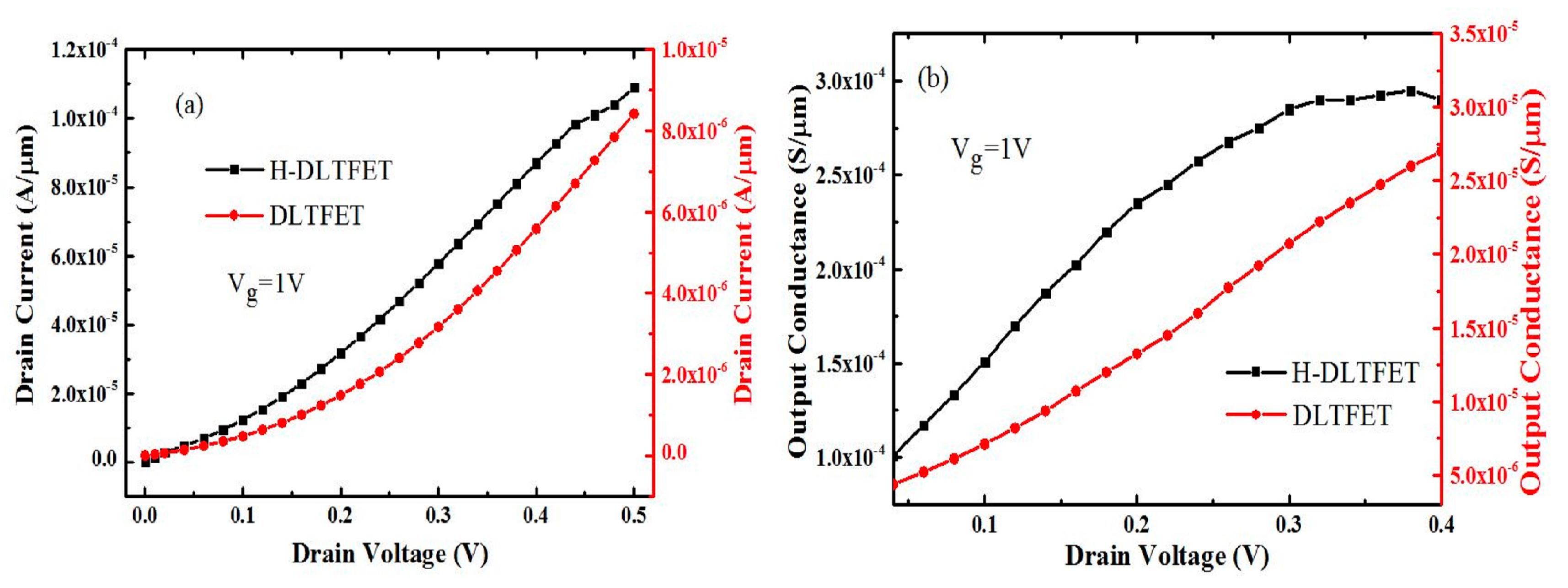

3.1. The Transfer and Output Characteristics Analysis

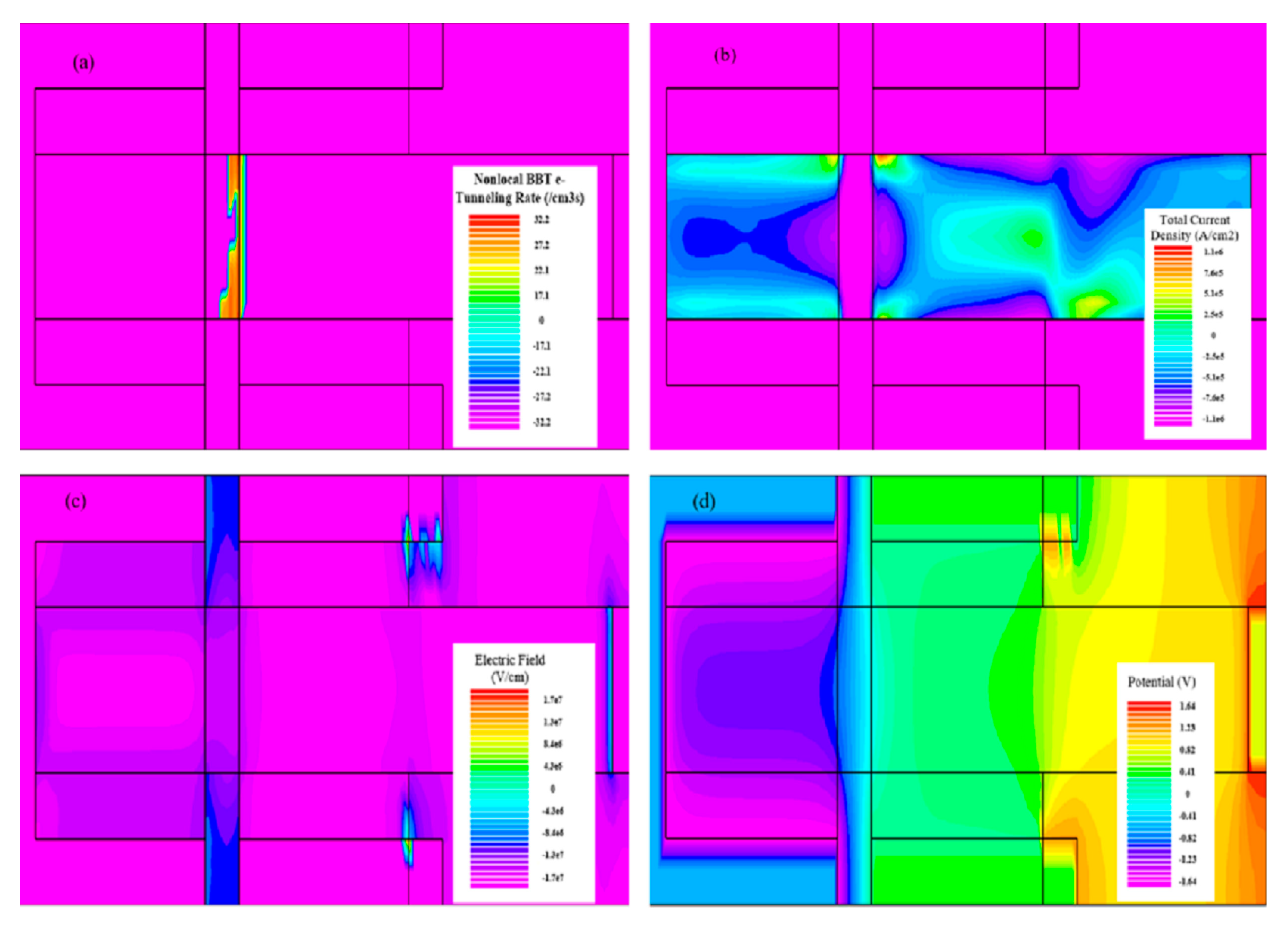

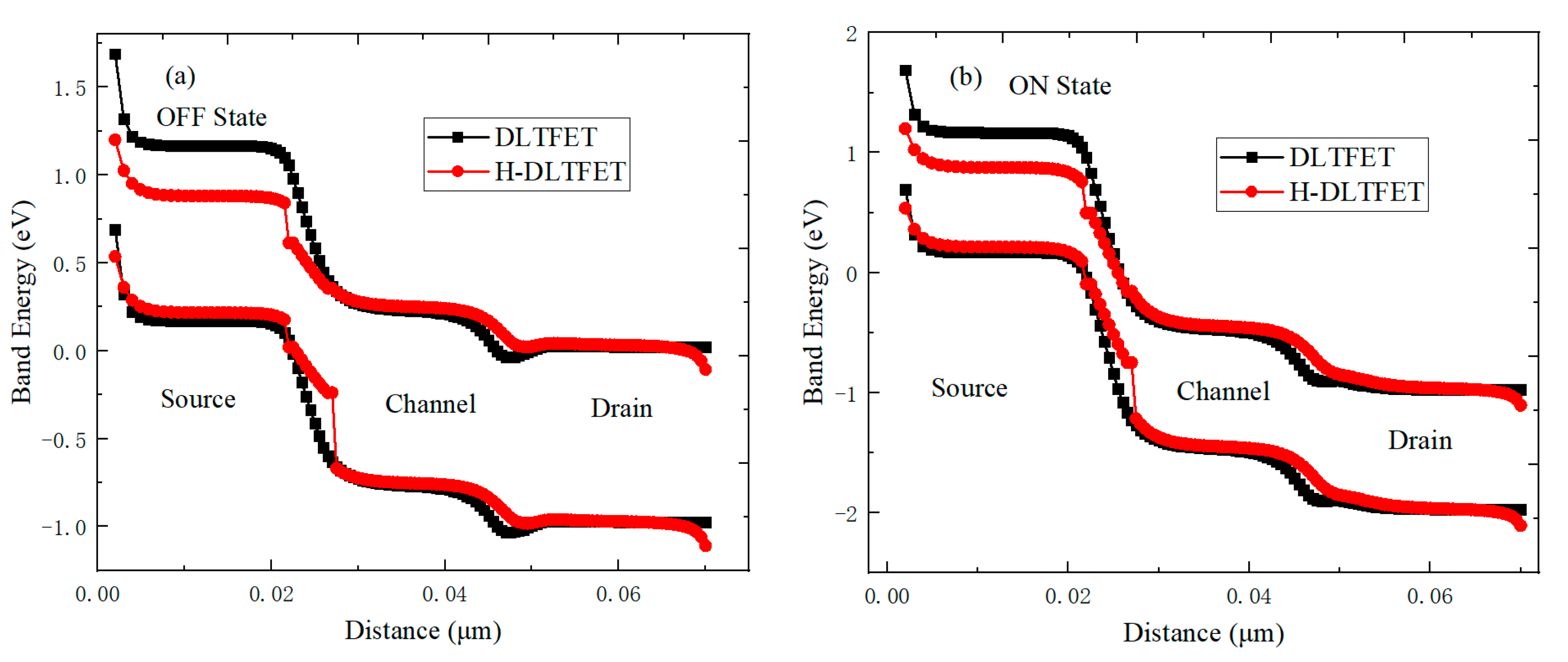

3.2. The Operating Mechanism of H-DLTFET

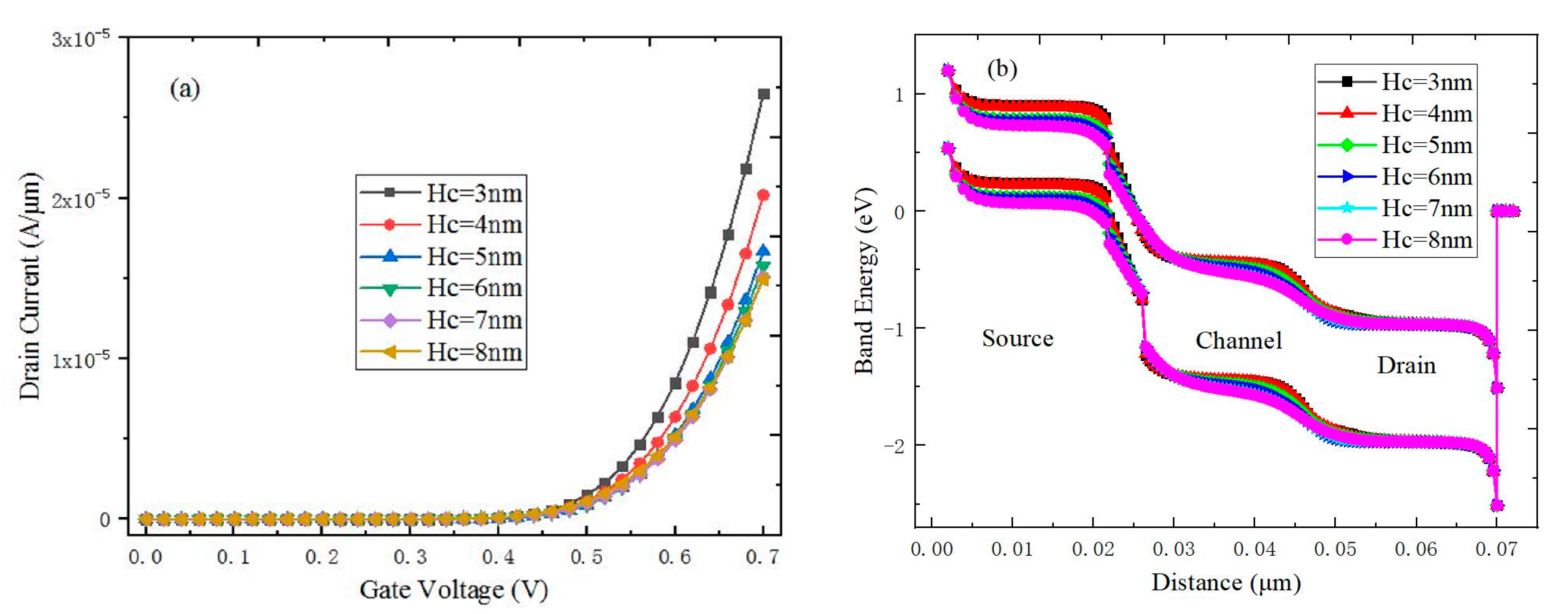

3.3. Effect of Device Parameters on The Electrical Performance

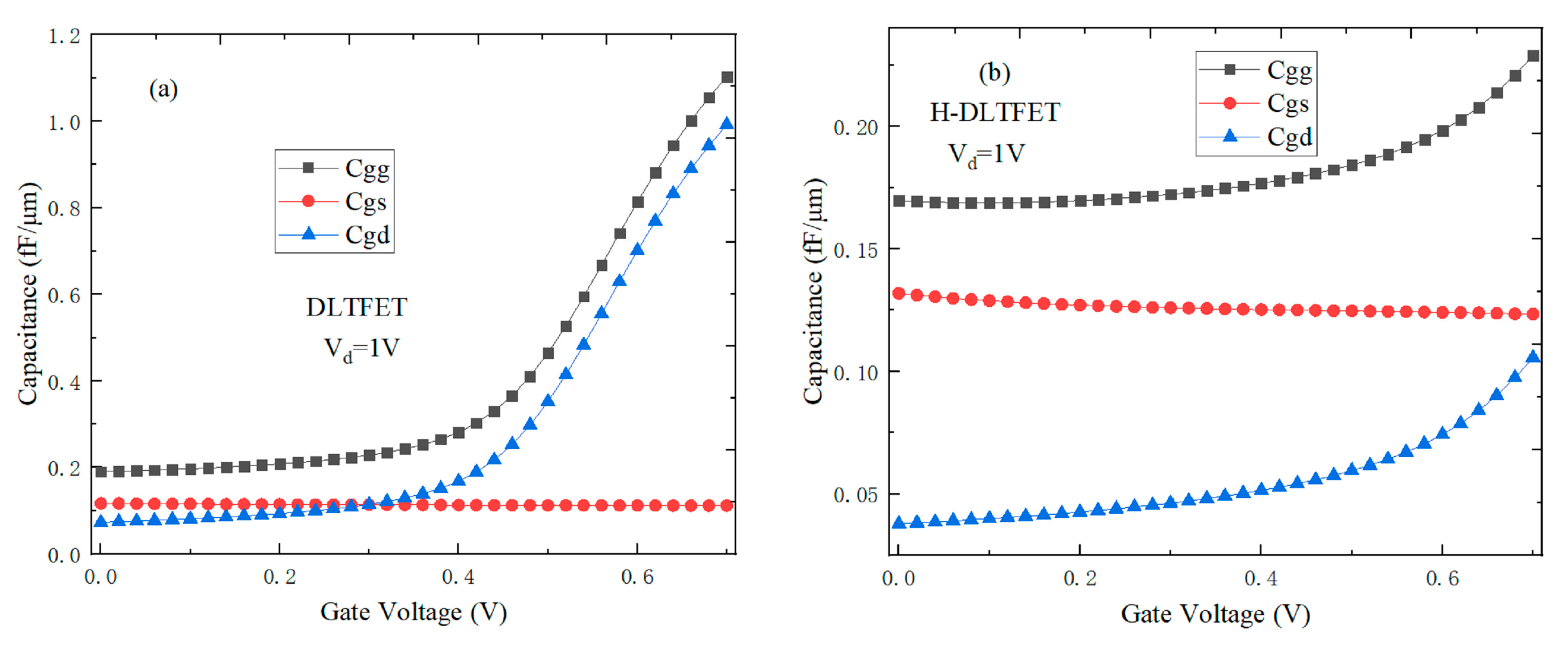

3.4. The C-V Characteristics

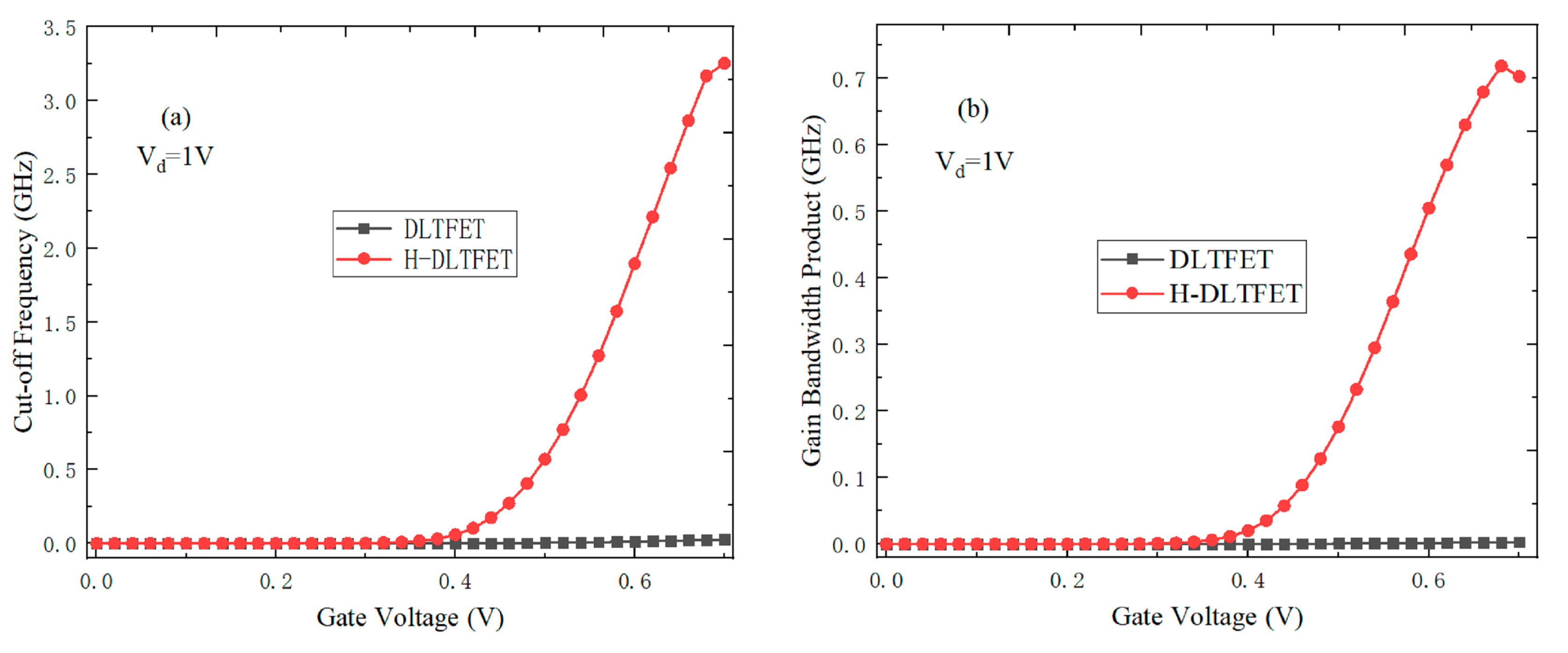

3.5. The Frequency Characteristics

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kim, S.W.; Kim, J.H.; Liu, T.J.K.; Choi, W.Y.; Park, B.G. Demonstration of L-shaped tunnel field-effect transistors. IEEE Trans. Electron Devices 2016, 63, 1774–1778. [Google Scholar] [CrossRef]

- Wang, W.; Wang, P.; Zhang, C.; Lin, X.; Liu, X.; Sun, Q.; Zhou, P.; Zhang, D.W. Design of U-Shape Channel Tunnel FETs with SiGe Source Regions. IEEE Trans. Electron Devices 2014, 61, 193–197. [Google Scholar] [CrossRef]

- Rahi, S.B.; Asthana, P.; Gupta, S. Heterogate junctionless tunnel field-effect transistor: Future of low-power devices. J. Comput. Electron. 2016, 16, 33–38. [Google Scholar] [CrossRef]

- Lee, H.; Park, S.; Lee, Y.; Nam, H.; Shin, C. Random variation analysis and variation-aware design of symmetric tunnel field-effect transistor. IEEE Trans. Electron Devices 2015, 62, 1778–1783. [Google Scholar]

- Li, W.; Liu, H.; Wang, S.; Chen, S. Reduced Miller capacitance in U-shaped channel tunneling FET by introducing heterogeneous gate dielectric. IEEE Trans. Electron Devices 2017, 38, 403–406. [Google Scholar] [CrossRef]

- Raushan, M.A.; Alam, N.; Akram, M.W.; Siddiqui, M.J. Impact of asymmetric dual-k spacers on tunnel field effect transistors. J. Comput. Electron. 2018, 17, 756–765. [Google Scholar] [CrossRef]

- Cao, J.; Logoteta, D.; Özkaya, S.; Biel, B.; Cresti, A.; Pala, M.G.; Esseni, D. Operation and Design of van der Waals Tunnel Transistors: A 3-D Quantum Transport Study. IEEE Trans. Electron Devices 2016, 63, 4388–4394. [Google Scholar] [CrossRef]

- Wadhwa, G.; Raj, B. Label Free Detection of Biomolecules Using Charge-Plasma-Based Gate Underlap Dielectric Modulated Junctionless TFET. J. Electron. Mater. 2018, 47, 4683–4693. [Google Scholar] [CrossRef]

- Rahi, S.B.; Ghosh, B.; Bishnoi, B. Temperature effect on hetero structure junctionless tunnel FET. J. Semicond. 2015, 36, 034002. [Google Scholar] [CrossRef]

- Singh, G.; Amin, S.I.; Anand, S.; Sarin, R.K. Design of Si0.5Ge0.5 based tunnel field effect transistor and its performance evaluation. Superlattices Microstruct. 2016, 92, 143–156. [Google Scholar] [CrossRef]

- Dash, S.; Mishra, G.P. A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET). Superlattices Microstruct. 2015, 86, 211–220. [Google Scholar] [CrossRef]

- Chauhan, S.S.; Sharma, N. Impact of Spacer-Gate Engineered Workfunction on the Performance of Dopingless TFET. J. Nanoelectron. Optoelectron. 2018, 13, 1200–1203. [Google Scholar] [CrossRef]

- Damrongplasit, N.; Kim, S.H.; Liu, T.J.K. Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. IEEE Electron Device Lett. 2013, 34, 184–186. [Google Scholar] [CrossRef]

- Raad, B.R.; Nigam, K.; Sharma, D.; Kondekar, P.N. Performance investigation of bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. Superlattices Microstruct. 2016, 94, 138–146. [Google Scholar] [CrossRef]

- Anand, S.; Sarin, R.K. Gate misalignment effects on analog/RF performance of charge plasma-based doping-less tunnel FET. Appl. Phys. A 2017, 123, 413. [Google Scholar] [CrossRef]

- Cecil, K.; Singh, J. Influence of Germanium source on dopingless tunnel-FET for improved analog/RF performance. Superlattices Microstruct. 2017, 101, 244–252. [Google Scholar] [CrossRef]

- Revelant, A.; Villalon, A.; Wu, Y.; Zaslavsky, A.; Le Royer, C.; Iwai, H.; Cristoloveanu, S. Electron-hole bilayer TFET: Experiments and comments. IEEE Trans. Electron Devices 2014, 61, 2674–2681. [Google Scholar]

- Aslam, M.; Sharma, D.; Yadav, S.; Soni, D.; Sharma, N.; Gedam, A. A comparative investigation of low work-function metal implantation in the oxide region for improving electrostatic characteristics of charge plasma TFET. Micro. Nano. Lett. 2019, 14, 123–128. [Google Scholar] [CrossRef]

- Lahgere, A.; Panchore, M.; Singh, J. Dopingless ferroelectric tunnel FET architecture for the improvement of performance of dopingless n-channel tunnel FETs. Superlattices Microstruct. 2016, 96, 16–25. [Google Scholar]

- Anand, S.; Sarin, R.K. An analysis on ambipolar reduction techniques for charge plasma based tunnel field effect transistors. J. Nanoelectron. Optoelectron. 2016, 11, 543–550. [Google Scholar] [CrossRef]

- Tirkey, S.; Nigam, K.; Pandey, S.; Sharma, D.; Kondekar, P. Investigation of gate material engineering in junctionless TFET to overcome the trade-off between ambipolarity and RF/linearity metrics. Superlattices Microstruct. 2017, 109, 307–315. [Google Scholar]

- Han, T.; Liu, H.; Chen, S.; Wang, S.; Li, W. A Doping-Less Tunnel Field-Effect Transistor with Si0.6Ge0.4 Heterojunction for the Improvement of the On–Off Current Ratio and Analog/RF Performance. Electronics 2019, 8, 574. [Google Scholar] [CrossRef]

- Bagga, N.; Sarkar, S.K. An analytical model for tunnel barrier modulation in triple metal double gate TFET. IEEE Trans. Electron Devices 2015, 62, 2136–2142. [Google Scholar] [CrossRef]

- Singh, D.; Pandey, S.; Nigam, K.; Sharma, D.; Yadav, D.S.; Kondekar, P. A charge-plasma-based dielectric-modulated junctionless TFET for biosensor label-free detection. IEEE Trans. Electron Devices 2017, 64, 271–278. [Google Scholar] [CrossRef]

- Leung, G.; Chui, C.O. Variability Impact of Random Dopant Fluctuation on Nanoscale Junctionless FinFETs. IEEE Electron Device Lett. 2012, 33, 767–769. [Google Scholar] [CrossRef]

- Lattanzio, L.; De Michielis, L.; lonescu, A.M. The electron–hole bilayer tunnel FET. Solid-State Electron. 2012, 74, 85–90. [Google Scholar] [CrossRef]

- Padilla, J.L.; Alper, C.; Medina-Bailón, C.; Gámiz, F.; lonescu, A.M. Assessment of pseudo-bilayer structures in the heterogate germanium electron-hole bilayer tunnel field-effect transistor. Appl. Phys. Lett. 2015, 106, 262102. [Google Scholar] [CrossRef]

- Ghosh, B.; Akram, M.W. Junctionless tunnel field effect transistor. IEEE Electron Device Lett. 2013, 34, 584–586. [Google Scholar] [CrossRef]

- Kao, K.H.; Verhulst, A.S.; Vandenberghe, W.G.; Sorée, B.; Magnus, W.; Leonelli, D.; Groeseneken, G.; De Meyer, K. Optimization of gate-on-source-only tunnel fets with counter-doped pockets. IEEE Trans. Electron Devices 2012, 59, 2070–2077. [Google Scholar] [CrossRef]

- Asthana, P.K.; Goswami, Y.; Basak, S.; Rahi, S.B.; Ghosh, B. Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. RSC Adv. 2015, 5, 48779–48785. [Google Scholar] [CrossRef]

- Biswas, A.; Luong, G.V.; Chowdhury, M.F.; Alper, C.; Zhao, Q.; Udrea, F. Benchmarking of Homojunction Strained-Si NW Tunnel FETs for Basic Analog Functions. IEEE Trans. Electron Devices 2017, 64, 1441–1448. [Google Scholar] [CrossRef]

- Sze, S.M.; Kwok, K.N.G. Physics of Semiconductor Devices, 3rd ed.; XI’AN JIAOTONG UNIVERSITY PRESS: Xi’an, China, 2008; pp. 130–246. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, T.; Liu, H.; Chen, S.; Wang, S.; Xie, H. TCAD Simulation of the Doping-Less TFET with Ge/SiGe/Si Hetero-Junction and Hetero-Gate Dielectric for the Enhancement of Device Performance. Coatings 2020, 10, 278. https://doi.org/10.3390/coatings10030278

Han T, Liu H, Chen S, Wang S, Xie H. TCAD Simulation of the Doping-Less TFET with Ge/SiGe/Si Hetero-Junction and Hetero-Gate Dielectric for the Enhancement of Device Performance. Coatings. 2020; 10(3):278. https://doi.org/10.3390/coatings10030278

Chicago/Turabian StyleHan, Tao, Hongxia Liu, Shupeng Chen, Shulong Wang, and Haiwu Xie. 2020. "TCAD Simulation of the Doping-Less TFET with Ge/SiGe/Si Hetero-Junction and Hetero-Gate Dielectric for the Enhancement of Device Performance" Coatings 10, no. 3: 278. https://doi.org/10.3390/coatings10030278

APA StyleHan, T., Liu, H., Chen, S., Wang, S., & Xie, H. (2020). TCAD Simulation of the Doping-Less TFET with Ge/SiGe/Si Hetero-Junction and Hetero-Gate Dielectric for the Enhancement of Device Performance. Coatings, 10(3), 278. https://doi.org/10.3390/coatings10030278