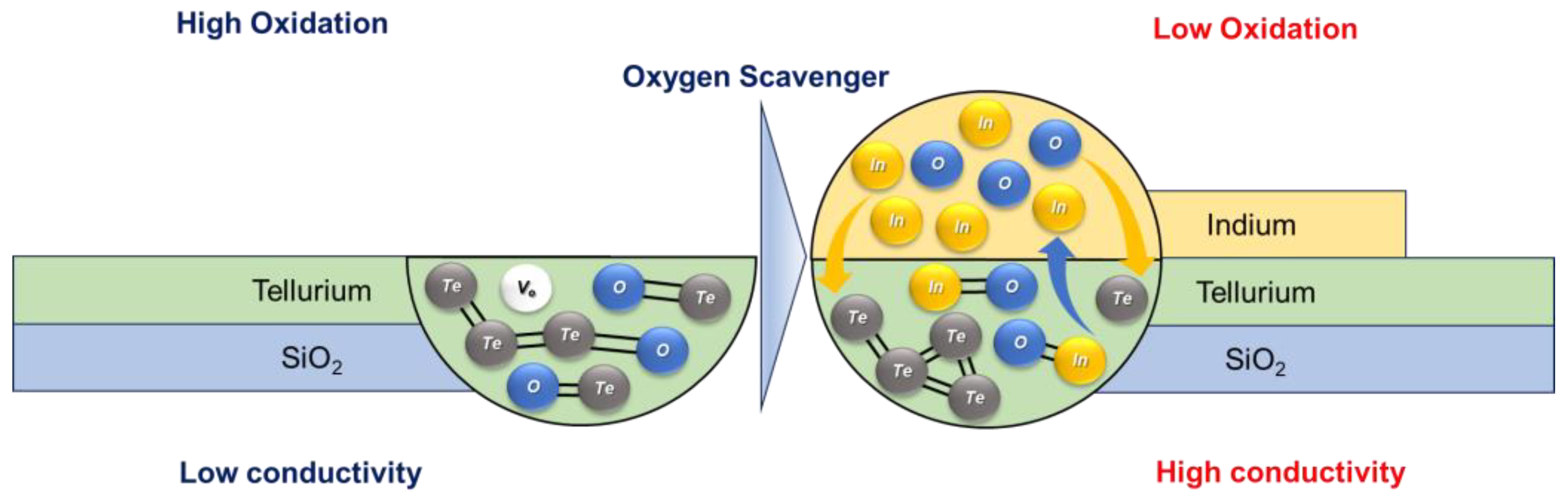

High-Mobility Tellurium Thin-Film Transistor: Oxygen Scavenger Effect Induced by a Metal-Capping Layer

Abstract

1. Introduction

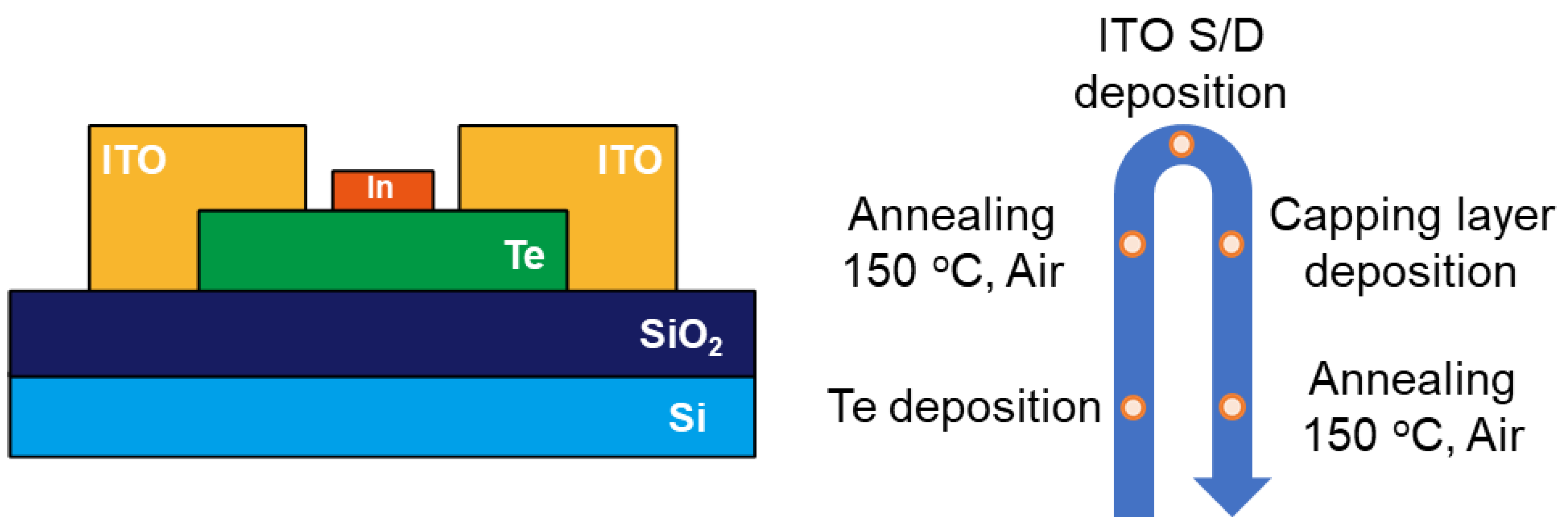

2. Materials and Methods

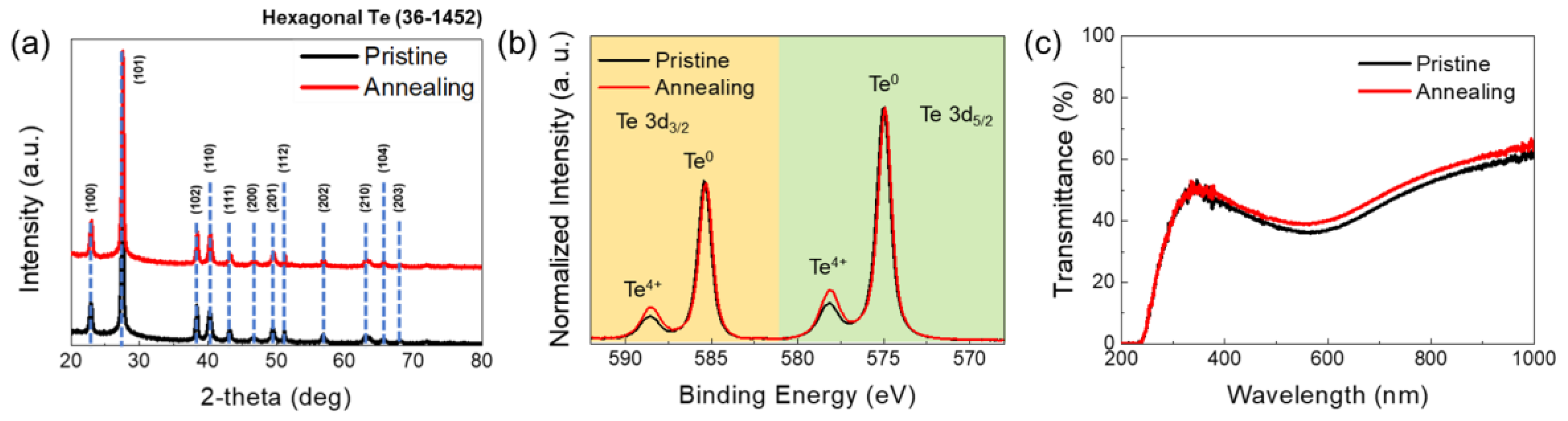

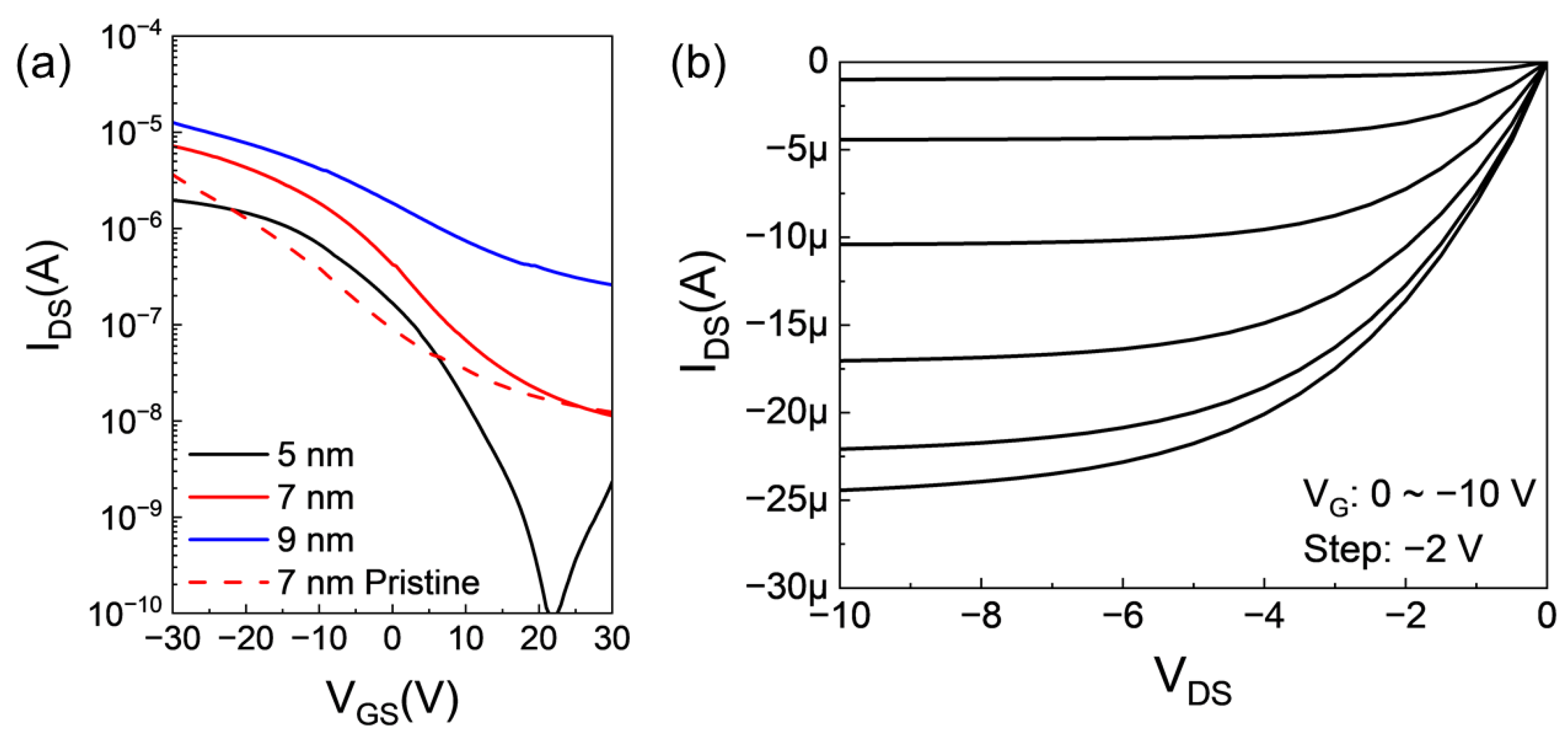

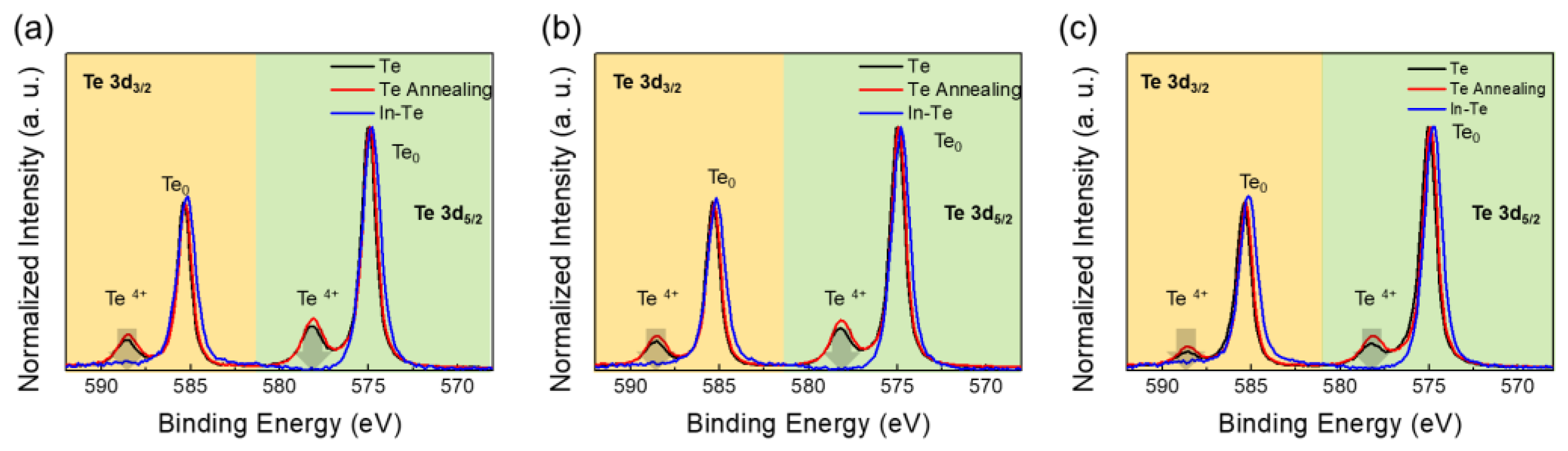

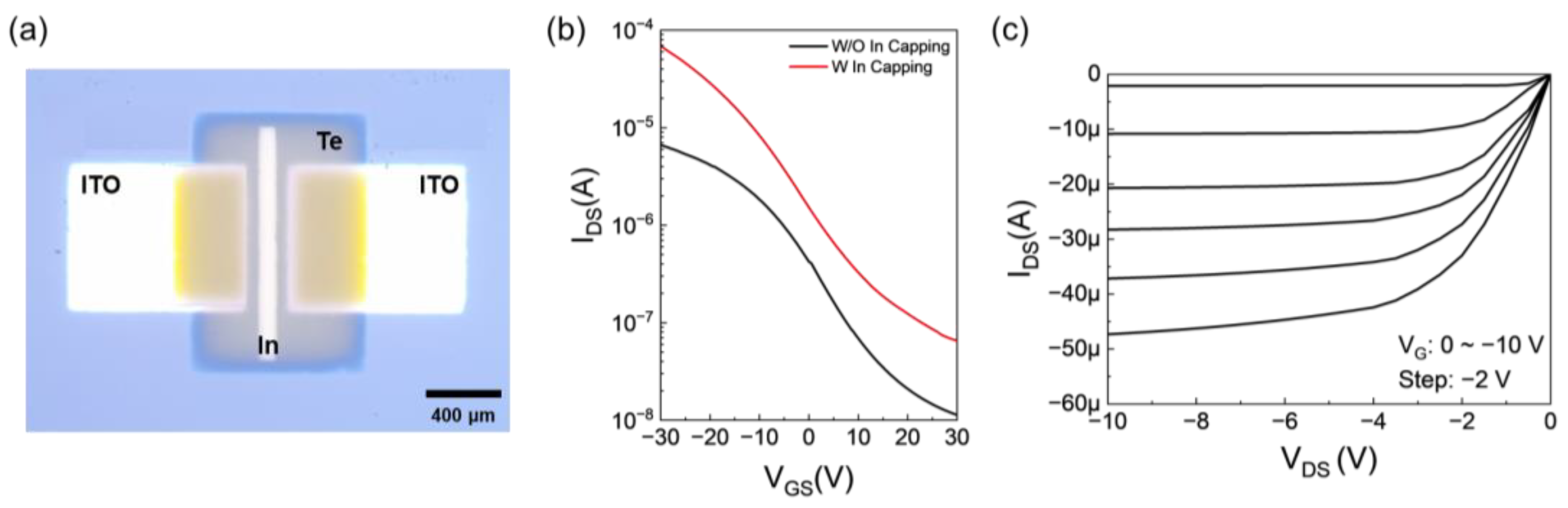

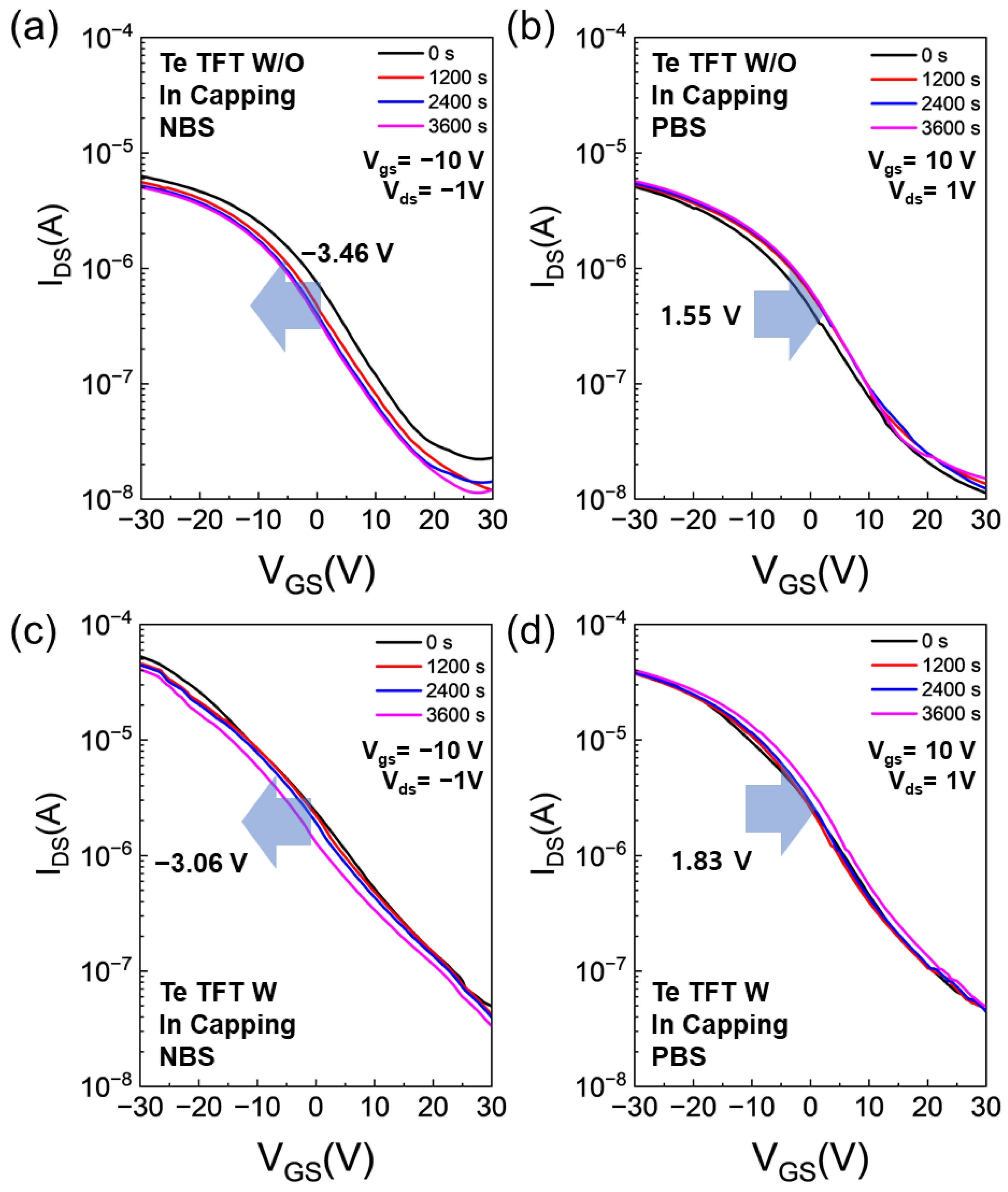

3. Results and Discussion

4. Conclusions

Supplementary Materials

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Choi, J.; Lee, C.; Lee, C.; Park, H.; Lee, S.M.; Kim, C.-H.; Yoo, H.; Im, S.G. Vertically stacked, low-voltage organic ternary logic circuits including nonvolatile floating-gate memory transistors. Nat. Commun. 2022, 13, 2305. [Google Scholar] [CrossRef]

- Kim, J.; Jeong, S.M.; Jeong, J. Scaling characteristics of depletion type, fully transparent amorphous indium–gallium–zinc-oxide thin-film transistors and inverters following Ar plasma treatment. Jpn. J. Appl. Phys. 2015, 54, 114102. [Google Scholar] [CrossRef]

- Zhang, J.; Wang, W.; Zhu, J.; Wang, J.; Zhao, C.; Zhu, T.; Ren, Q.; Liu, Q.; Qiu, R.; Zhang, M. Ultra-Flexible Monolithic 3D Complementary Metal-Oxide-Semiconductor Electronics. Adv. Funct. Mater. 2023, 33, 2305379. [Google Scholar] [CrossRef]

- Guo, E.; Xing, S.; Dollinger, F.; Hübner, R.; Wang, S.-J.; Wu, Z.; Leo, K.; Kleemann, H. Integrated complementary inverters and ring oscillators based on vertical-channel dual-base organic thin-film transistors. Nat. Electron. 2021, 4, 588–594. [Google Scholar] [CrossRef]

- Jeong, K.; Shin, D.y.; Park, J.M.; Yi, D.J.; Hong, H.; Kim, H.S.; Chung, K.B. Noncontact Monitoring and Imaging of the Operation and Performance of Thin-Film Field-Effect Transistors. Adv. Sci. 2024, 12, 2407923. [Google Scholar] [CrossRef] [PubMed]

- Hong, S.; Mativenga, M.; Jang, J. Extreme bending test of IGZO TFT. In Proceedings of the 2014 21st International Workshop on Active-Matrix Flatpanel Displays and Devices (AM-FPD), Kyoto, Japan, 2–4 July 2014; pp. 125–127. [Google Scholar]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef]

- Byeon, G.; Jang, S.C.; Roh, T.; Park, J.-M.; Kim, H.-S.; Noh, Y.-Y. Recent progress in the development of backplane thin film transistors for information displays. J. Inf. Disp. 2023, 24, 159–168. [Google Scholar] [CrossRef]

- Lee, G.; Jang, S.C.; Lee, J.H.; Park, J.M.; Noh, B.; Choi, H.; Kweon, H.; Kim, D.H.; Kim, H.Y.; Kim, H.S. Intrinsically Photopatternable High-k Polymer Dielectric for Flexible Electronics. Adv. Funct. Mater. 2024, 34, 2405530. [Google Scholar] [CrossRef]

- Shang, Z.-W.; Hsu, H.-H.; Zheng, Z.-W.; Cheng, C.-H. Progress and challenges in p-type oxide-based thin film transistors. Nanotechnol. Rev. 2019, 8, 422–443. [Google Scholar] [CrossRef]

- Yang, J.; Wang, B.; Zhang, Y.; Ding, X.; Zhang, J. Low-temperature combustion synthesis and UV treatment processed p-type Li: NiO x active semiconductors for high-performance electronics. J. Mater. Chem. C 2018, 6, 12584–12591. [Google Scholar] [CrossRef]

- Maeng, W.; Lee, S.-H.; Kwon, J.-D.; Park, J.; Park, J.-S. Atomic layer deposited p-type copper oxide thin films and the associated thin film transistor properties. Ceram. Int. 2016, 42, 5517–5522. [Google Scholar] [CrossRef]

- Yen, T.J.; Chin, A.; Gritsenko, V. Exceedingly high performance top-gate p-type SnO thin film transistor with a nanometer scale channel layer. Nanomaterials 2021, 11, 92. [Google Scholar] [CrossRef]

- Cheng, Q.; Pang, J.; Sun, D.; Wang, J.; Zhang, S.; Liu, F.; Chen, Y.; Yang, R.; Liang, N.; Lu, X. WSe2 2D p-type semiconductor-based electronic devices for information technology: Design, preparation, and applications. InfoMat 2020, 2, 656–697. [Google Scholar] [CrossRef]

- Huang, H.; Zha, J.; Xu, S.; Yang, P.; Xia, Y.; Wang, H.; Dong, D.; Zheng, L.; Yao, Y.; Zhang, Y. Precursor-Confined Chemical Vapor Deposition of 2D Single-Crystalline Se x Te1–x Nanosheets for p-Type Transistors and Inverters. ACS Nano 2024, 18, 17293–17303. [Google Scholar] [CrossRef] [PubMed]

- Ding, X.; Zhang, S.; Zhao, M.; Xiang, Y.; Zhang, K.H.; Zu, X.; Li, S.; Qiao, L. NbS2: A promising p-type ohmic contact for two-dimensional materials. Phys. Rev. Appl. 2019, 12, 064061. [Google Scholar] [CrossRef]

- Sata, Y.; Moriya, R.; Masubuchi, S.; Watanabe, K.; Taniguchi, T.; Machida, T. N-and p-type carrier injections into WSe2 with van der Waals contacts of two-dimensional materials. Jpn. J. Appl. Phys. 2017, 56, 04CK09. [Google Scholar] [CrossRef]

- Zhao, C.; Batiz, H.; Yasar, B.; Kim, H.; Ji, W.; Scott, M.C.; Chrzan, D.C.; Javey, A. Tellurium Single-Crystal Arrays by Low-Temperature Evaporation and Crystallization. Adv. Mater. 2021, 33, 2100860. [Google Scholar] [CrossRef]

- Shi, Z.; Cao, R.; Khan, K.; Tareen, A.K.; Liu, X.; Liang, W.; Zhang, Y.; Ma, C.; Guo, Z.; Luo, X. Two-dimensional tellurium: Progress, challenges, and prospects. Nano-Micro Lett. 2020, 12, 99. [Google Scholar] [CrossRef]

- Wang, Q.; Safdar, M.; Xu, K.; Mirza, M.; Wang, Z.; He, J. Van der Waals epitaxy and photoresponse of hexagonal tellurium nanoplates on flexible mica sheets. ACS Nano 2014, 8, 7497–7505. [Google Scholar] [CrossRef]

- Lim, S.-H.; Kim, T.I.; Park, I.-J.; Kwon, H.-I. Synthesis of a Tellurium Semiconductor with an Organic–Inorganic Hybrid Passivation Layer for High-Performance p-Type Thin Film Transistors. ACS Appl. Electron. Mater. 2023, 5, 4816–4825. [Google Scholar] [CrossRef]

- Lee, S.M.; Park, J.-M.; Ahn, S.; Jang, S.C.; Kim, H.; Kim, H.-S. Inorganic p-Type Tellurium-Based Synaptic Transistors: Complementary Synaptic Pairs with n-Type Devices for Energy-Efficient Operation. ACS Appl. Electron. Mater. 2024, 6, 5371–5378. [Google Scholar] [CrossRef]

- Zhao, C.; Tan, C.; Lien, D.-H.; Song, X.; Amani, M.; Hettick, M.; Nyein, H.Y.Y.; Yuan, Z.; Li, L.; Scott, M.C. Evaporated tellurium thin films for p-type field-effect transistors and circuits. Nat. Nanotechnol. 2020, 15, 53–58. [Google Scholar] [CrossRef]

- Zhou, G.; Addou, R.; Wang, Q.; Honari, S.; Cormier, C.R.; Cheng, L.; Yue, R.; Smyth, C.M.; Laturia, A.; Kim, J. High-mobility helical tellurium field-effect transistors enabled by transfer-free, low-temperature direct growth. Adv. Mater. 2018, 30, 1803109. [Google Scholar] [CrossRef] [PubMed]

- Zhao, C.; Batiz, H.; Yasar, B.; Ji, W.; Scott, M.C.; Chrzan, D.C.; Javey, A. Orientated Growth of Ultrathin Tellurium by van der Waals Epitaxy. Adv. Mater. Interfaces 2022, 9, 2101540. [Google Scholar] [CrossRef]

- Kim, T.; Choi, C.H.; Byeon, P.; Lee, M.; Song, A.; Chung, K.-B.; Han, S.; Chung, S.-Y.; Park, K.-S.; Jeong, J.K. Growth of high-quality semiconducting tellurium films for high-performance p-channel field-effect transistors with wafer-scale uniformity. NPJ 2d Mater. Appl. 2022, 6, 4. [Google Scholar] [CrossRef]

- Lu, J.; He, Y.; Ma, C.; Ye, Q.; Yi, H.; Zheng, Z.; Yao, J.; Yang, G. Ultrabroadband imaging based on wafer-scale tellurene. Adv. Mater. 2023, 35, 2211562. [Google Scholar] [CrossRef]

- Liu, A.; Kim, Y.-S.; Kim, M.G.; Reo, Y.; Zou, T.; Choi, T.; Bai, S.; Zhu, H.; Noh, Y.-Y. Selenium alloyed tellurium oxide for amorphous p-channel transistors. Nature 2024, 629, 798–802. [Google Scholar] [CrossRef]

- Choi, K.; Nam, S.; Kim, Y.-H.; Oh, H.; Kim, I.; Lee, K.; Cho, S.H. Promotion of Processability in a p-Type Thin-Film Transistor Using a Se–Te Alloying Channel Layer. ACS Appl. Mater. Interfaces 2024, 16, 23459–23466. [Google Scholar]

- Kim, H.-D.; Naqi, M.; Jang, S.C.; Park, J.-M.; Park, Y.C.; Park, K.; Nahm, H.-H.; Kim, S.; Kim, H.-S. Nonvolatile high-speed switching Zn-ON thin-film transistors with a bilayer structure. ACS Appl. Mater. Interfaces 2022, 14, 13490–13498. [Google Scholar] [CrossRef]

- Shin, Y.; Kim, S.T.; Kim, K.; Kim, M.Y.; Oh, S.; Jeong, J.K. The mobility enhancement of indium gallium zinc oxide transistors via low-temperature crystallization using a tantalum catalytic layer. Sci. Rep. 2017, 7, 10885. [Google Scholar] [CrossRef]

- Lee, S.H.; Lee, S.; Jang, S.C.; On, N.; Kim, H.-S.; Jeong, J.K. Mobility enhancement of indium-gallium oxide via oxygen diffusion induced by a metal catalytic layer. J. Alloys Compd. 2021, 862, 158009. [Google Scholar] [CrossRef]

- Reese, M.O.; Perkins, C.L.; Burst, J.M.; Farrell, S.; Barnes, T.M.; Johnston, S.W.; Kuciauskas, D.; Gessert, T.A.; Metzger, W.K. Intrinsic surface passivation of CdTe. J. Appl. Phys. 2015, 118, 155305. [Google Scholar] [CrossRef]

- Miranda La Hera, V.; Wu, X.; Mena, J.; Barzegar, H.R.; Ashok, A.; Koroidov, S.; Wågberg, T.; Gracia-Espino, E. Controlled Synthesis of Tellurium Nanowires. Nanomaterials 2022, 12, 4137. [Google Scholar] [CrossRef]

- Majzlan, J.; Notz, S.; Haase, P.; Kamitsos, E.I.; Tagiara, N.S.; Dachs, E. Thermodynamic properties of tellurite (β-TeO2), paratellurite (α-TeO2), TeO2 glass, and Te (IV) phases with stoichiometry M2Te3O8, MTe6O13, MTe2O5 (M2+= Co, Cu, Mg, Mn, Ni, Zn). Geochemistry 2022, 82, 125915. [Google Scholar] [CrossRef]

- Aspiala, M.; Sukhomlinov, D.; Taskinen, P. Standard Gibbs energy of formation of tellurium dioxide measurement by a solid-oxide electrolyte EMF technique. Thermochim. Acta 2013, 573, 95–100. [Google Scholar] [CrossRef]

- Oh, J.-S.; Kim, T.I.; Kwon, H.-I.; Park, I.-J. Strain modulation effects on two-dimensional tellurium for advanced p-type transistor applications. Appl. Surf. Sci. 2024, 651, 159288. [Google Scholar] [CrossRef]

- Wang, X.; Li, H. A steep-slope tellurium transistor with a native voltage amplifying threshold switch. Appl. Phys. Lett. 2022, 120, 223502. [Google Scholar] [CrossRef]

- Kim, G.H.; Kang, S.-H.; Lee, J.M.; Son, M.; Lee, J.; Lee, H.; Chung, I.; Kim, J.; Kim, Y.-H.; Ahn, K. Room temperature-grown highly oriented p-type nanocrystalline tellurium thin-films transistors for large-scale CMOS circuits. Appl. Surf. Sci. 2023, 636, 157801. [Google Scholar] [CrossRef]

- Kim, T.; Choi, C.H.; Kim, S.E.; Kim, J.-K.; Jang, J.; Choi, S.; Noh, J.; Park, K.-S.; Kim, J.; Yoon, S. High-performance hexagonal tellurium thin-film transistor using tellurium oxide as a crystallization retarder. IEEE Electron Device Lett. 2022, 44, 269–272. [Google Scholar] [CrossRef]

| Thickness | µFE (cm2/Vs) | S.S. (V/dec) | Von (V) | ION/IOFF |

|---|---|---|---|---|

| 5 nm | 0.58 | 2.70 | 0.03 | 2.24 × 104 |

| 7 nm | 2.68 | 10.46 | −0.88 | 6.36 × 102 |

| 7 nm Pristine | 2.16 | 14.03 | −3.11 | 2.95 × 102 |

| 7 nm with In Capping | 33.54 | 12.52 | −2.21 | 1.05 × 103 |

| 9 nm | 3.92 | 22.84 | 9.42 | 4.86 × 101 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.-M.; Jang, S.C.; Park, J.-M.; Park, J.; Choi, N.; Chung, K.-B.; Lee, J.W.; Kim, H.-S. High-Mobility Tellurium Thin-Film Transistor: Oxygen Scavenger Effect Induced by a Metal-Capping Layer. Nanomaterials 2025, 15, 418. https://doi.org/10.3390/nano15060418

Lee S-M, Jang SC, Park J-M, Park J, Choi N, Chung K-B, Lee JW, Kim H-S. High-Mobility Tellurium Thin-Film Transistor: Oxygen Scavenger Effect Induced by a Metal-Capping Layer. Nanomaterials. 2025; 15(6):418. https://doi.org/10.3390/nano15060418

Chicago/Turabian StyleLee, Seung-Min, Seong Cheol Jang, Ji-Min Park, Jaewon Park, Nayoung Choi, Kwun-Bum Chung, Jung Woo Lee, and Hyun-Suk Kim. 2025. "High-Mobility Tellurium Thin-Film Transistor: Oxygen Scavenger Effect Induced by a Metal-Capping Layer" Nanomaterials 15, no. 6: 418. https://doi.org/10.3390/nano15060418

APA StyleLee, S.-M., Jang, S. C., Park, J.-M., Park, J., Choi, N., Chung, K.-B., Lee, J. W., & Kim, H.-S. (2025). High-Mobility Tellurium Thin-Film Transistor: Oxygen Scavenger Effect Induced by a Metal-Capping Layer. Nanomaterials, 15(6), 418. https://doi.org/10.3390/nano15060418