An Analytic Compact Model for P-Type Quasi-Ballistic/Ballistic Nanowire GAA MOSFETs Incorporating DIBL Effect

Abstract

1. Introduction

2. Modeling Ballistic Current

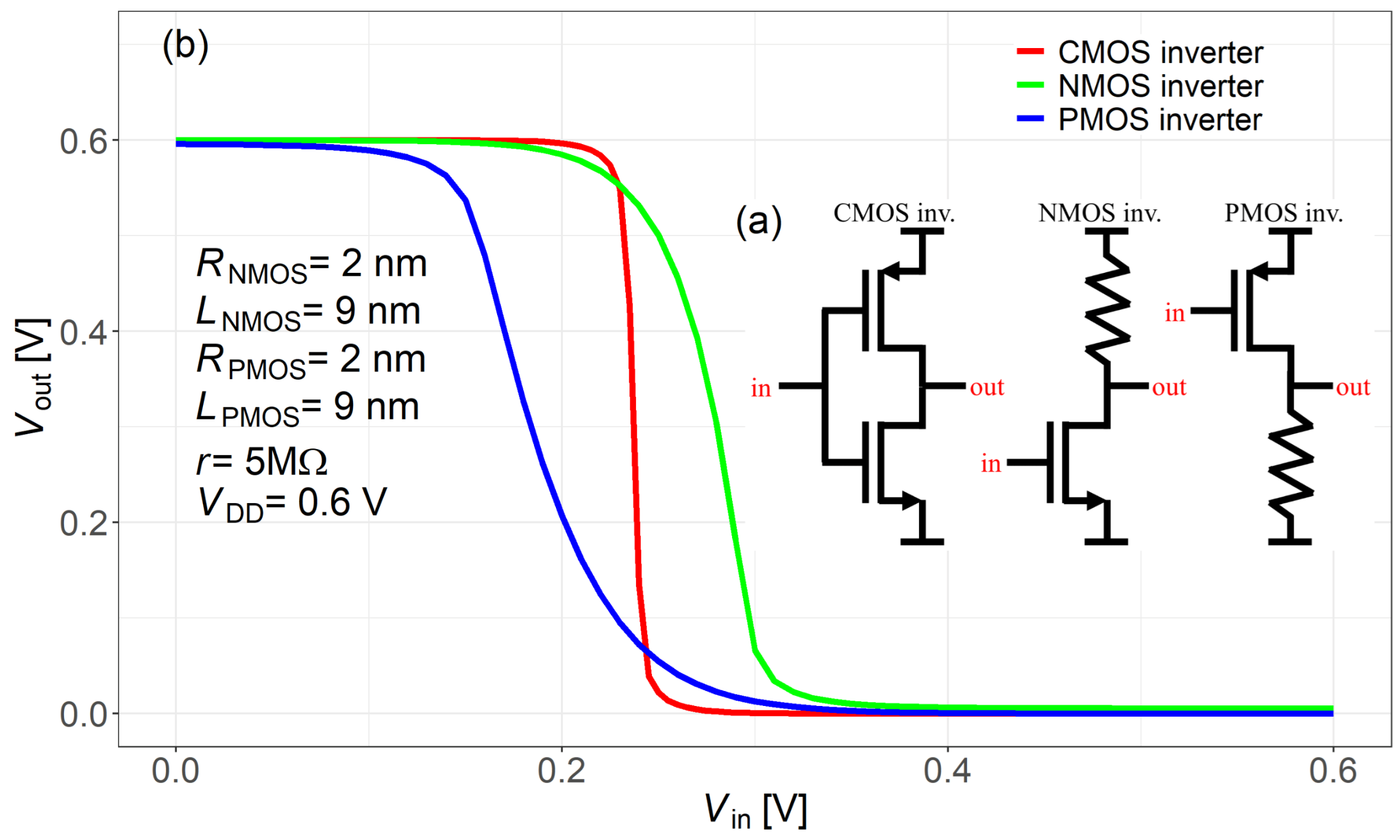

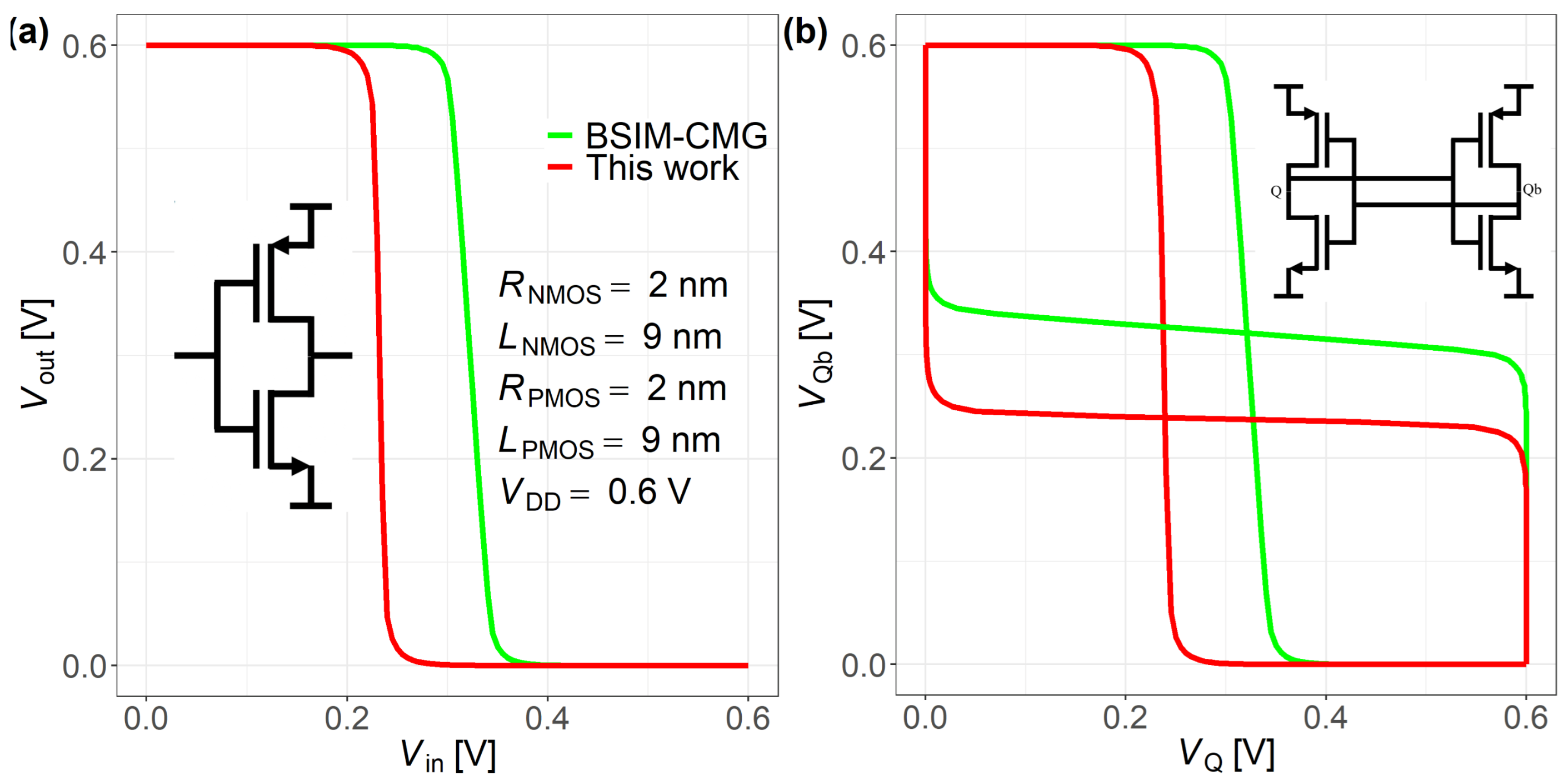

2.1. Model Structure and Coordinates

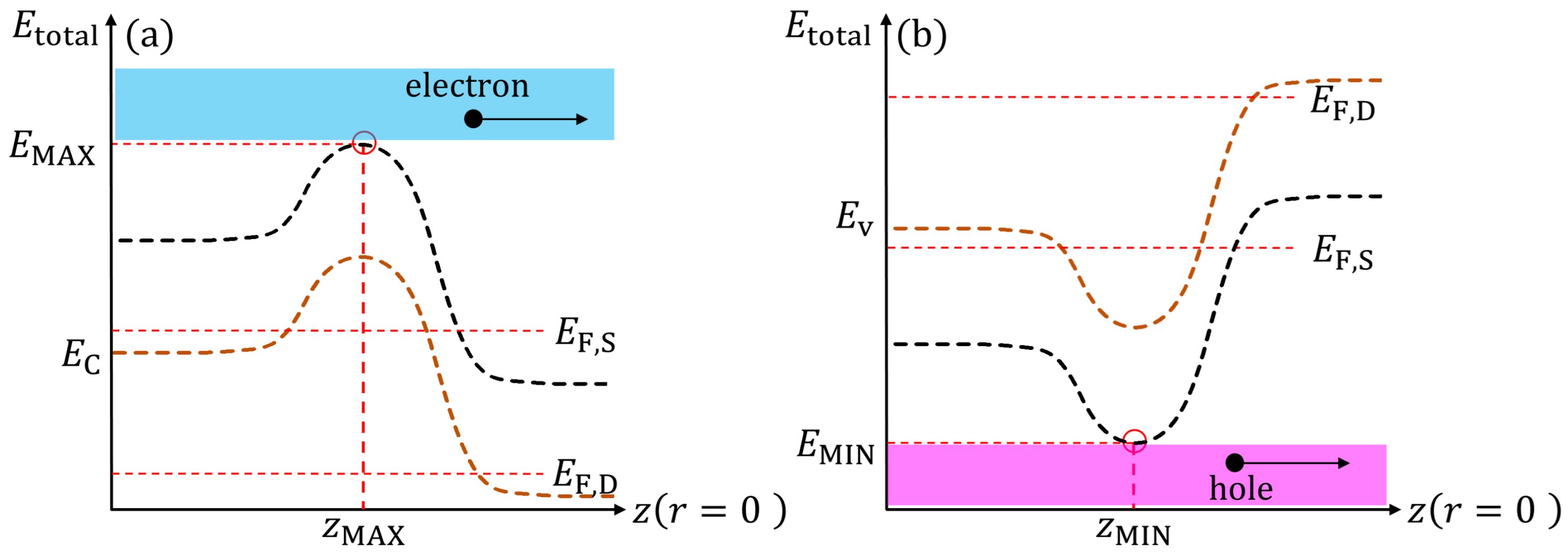

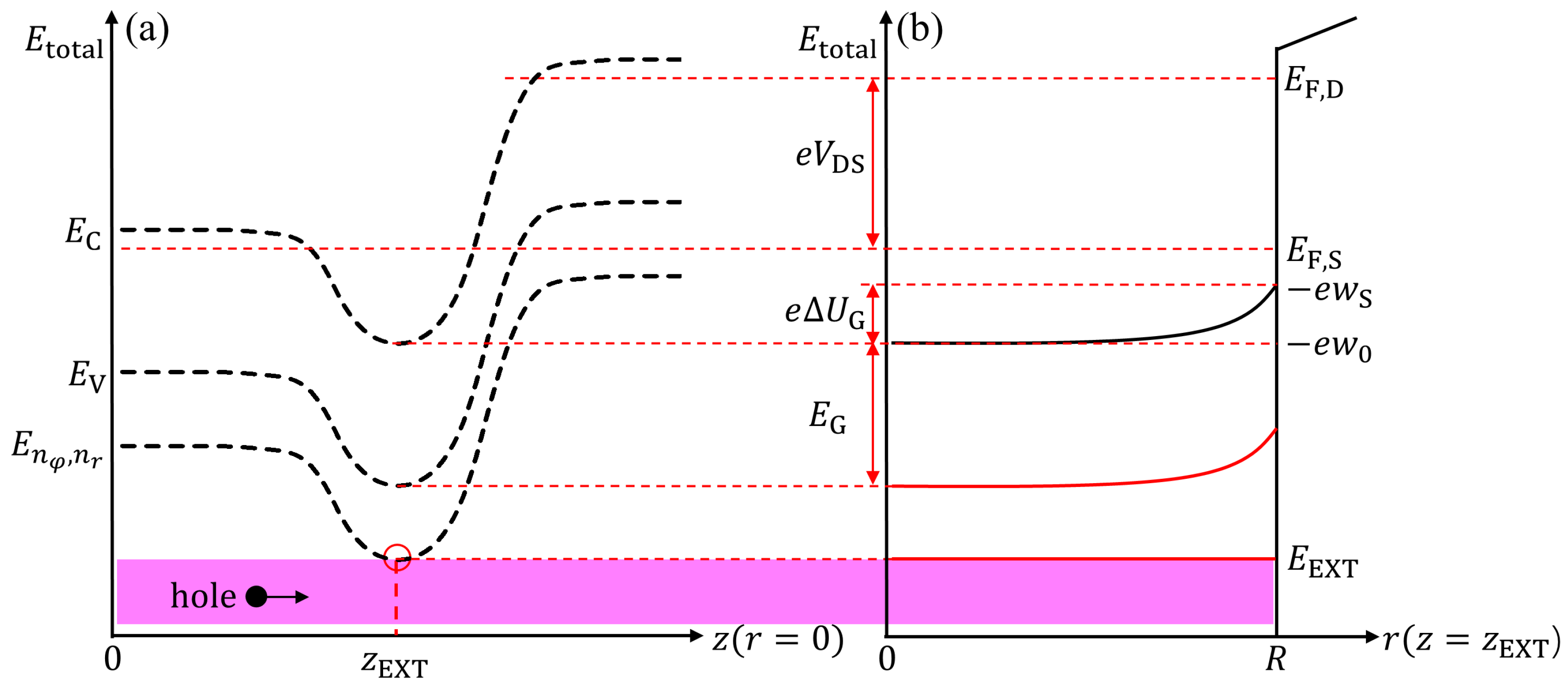

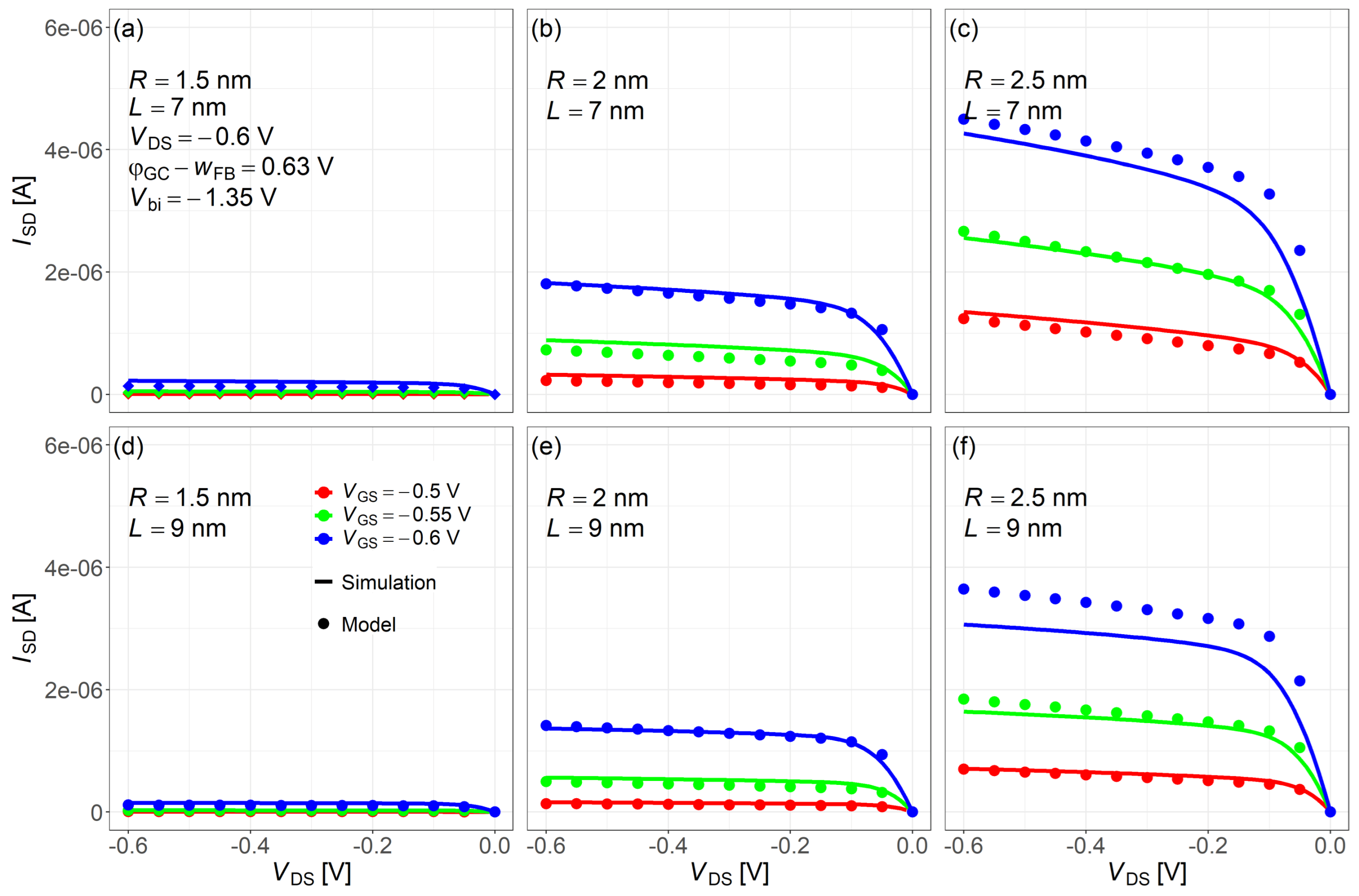

2.2. Quasi-Ballistic Current Derivation

3. Potential Profile Formulation

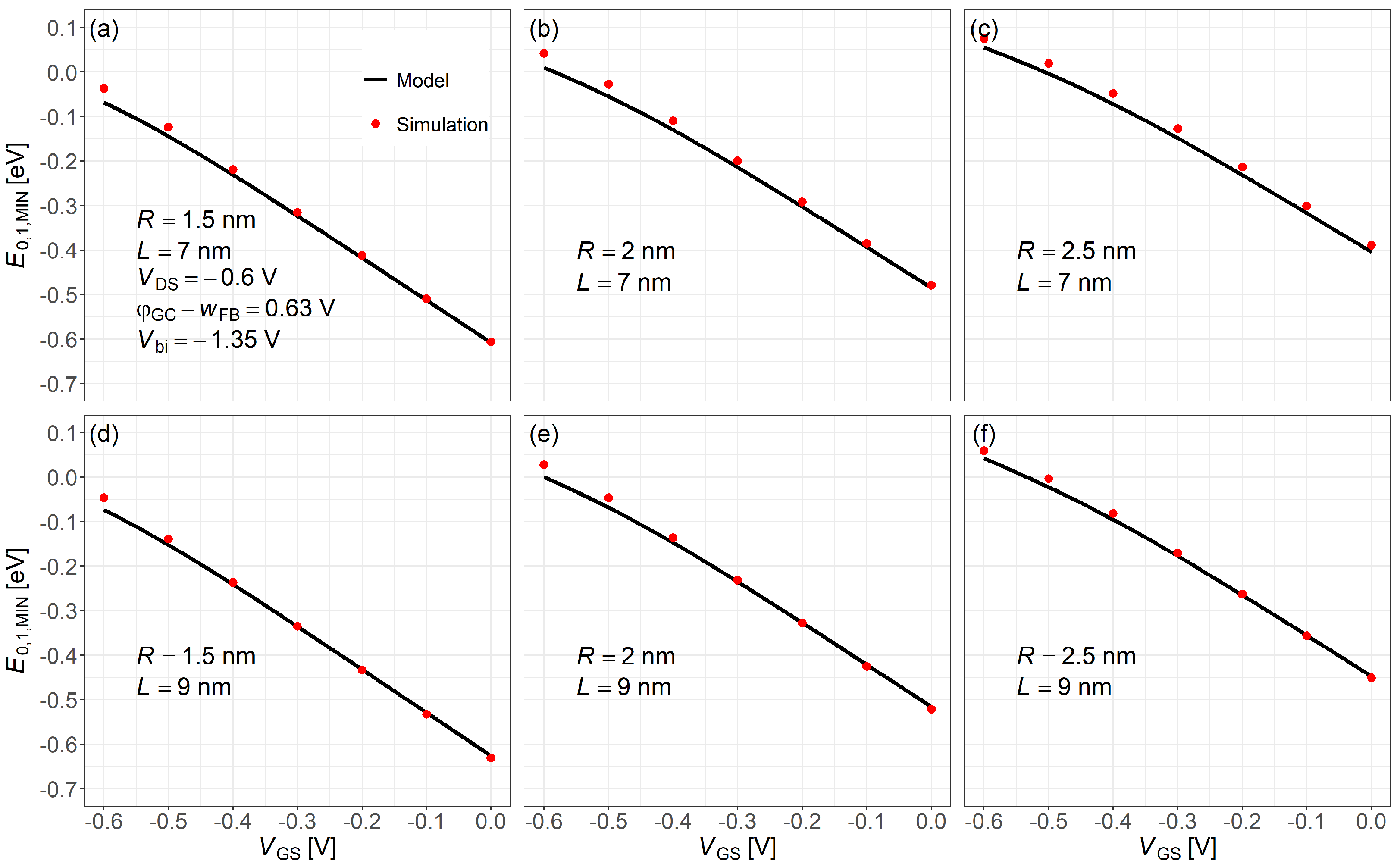

3.1. Subband Energy Profile and Definition of

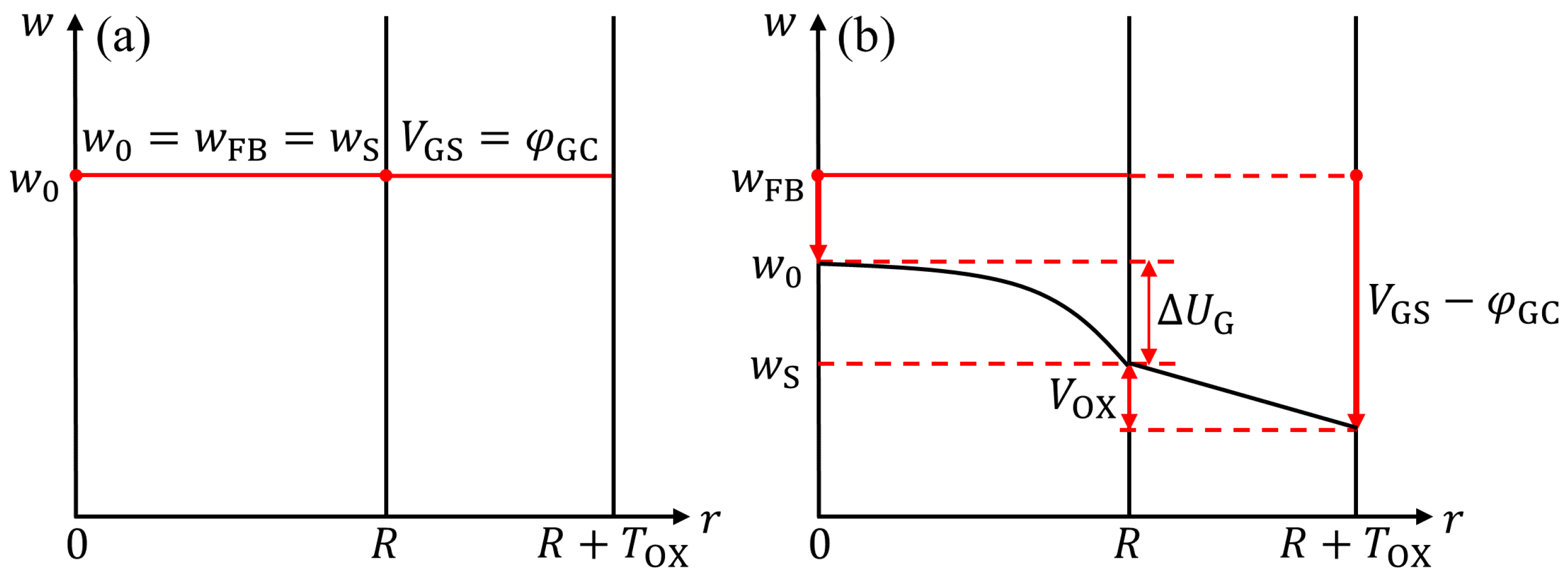

3.2. Analytical Solution for Channel Potential

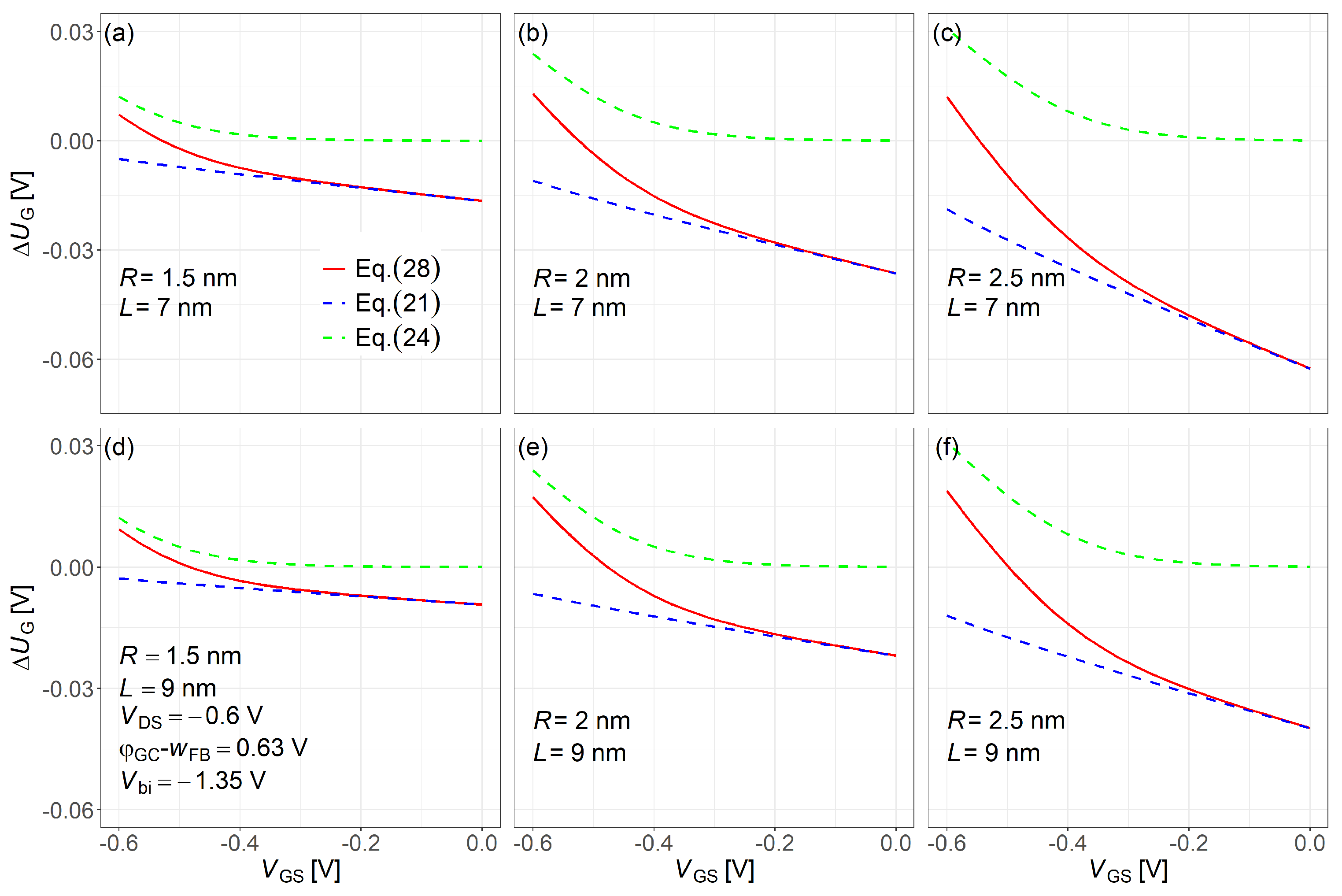

3.3. for All Operation Regions

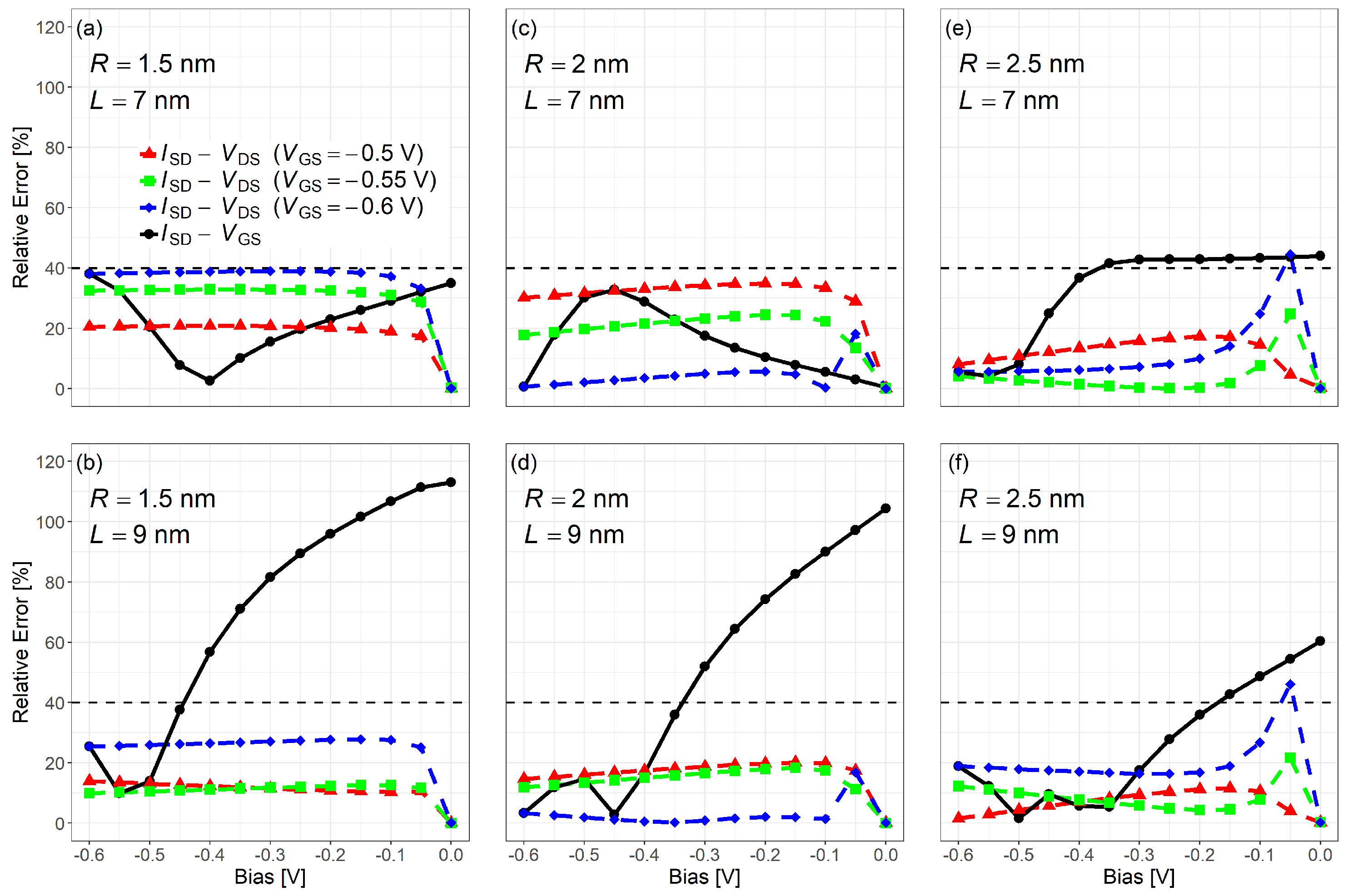

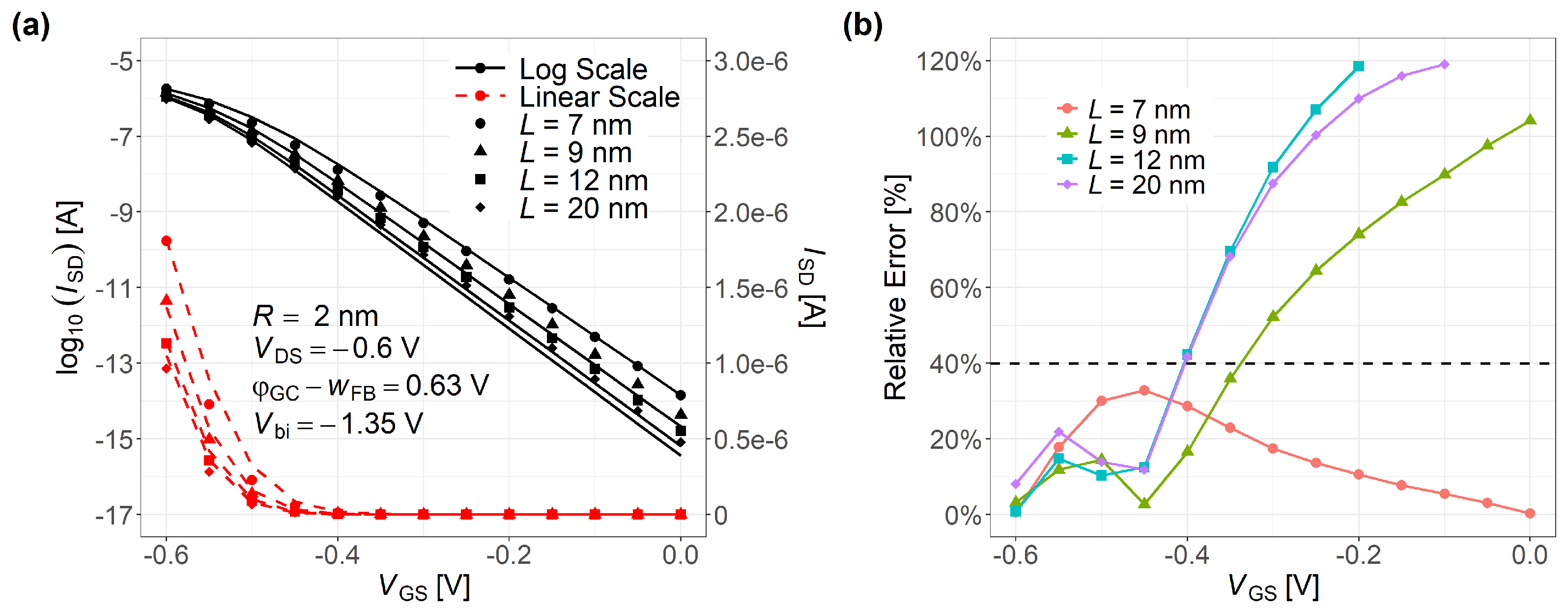

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Rathee, D.S.; Yadav, R.; Ahuja, K. Reduction of drain induced barrier lowering by optimization Trimetal-GAA-Si-NW MOSFET in multimedia tools. Multimed. Tools Appl. 2022, 81, 19849–19862. [Google Scholar] [CrossRef]

- Bhol, K.; Nanda, U. Nanowire Array-based MOSFET for Future CMOS Technology to Attain the Ultimate Scaling Limit. Silicon 2021, 14, 1169–1177. [Google Scholar] [CrossRef]

- Kumar, R.; Bala, S.; Kumar, A. Study and Analysis of Advanced 3D Multi-Gate Junctionless Transistors. Silicon 2021, 14, 1053–1067. [Google Scholar] [CrossRef]

- Lee, Y.; Park, G.-H.; Choi, B.; Yoon, J.; Kim, H.-J.; Kim, D.H.; Kim, D.M.; Kang, M.-H.; Choi, S.-J. Design study of the gate-all-around silicon nanosheet MOSFETs. Semicond. Sci. Technol. 2020, 35, 03LT01. [Google Scholar] [CrossRef]

- IEEE International Roadmap for Devices and Systems: 2022 Edition, Executive Summary. 2022. Available online: https://irds.ieee.org/editions/2022/executive-summary (accessed on 16 October 2025). [CrossRef]

- Manabe, K.; Uejima, K.; Ota, H.; Morita, Y.; Irisawa, T.; Hayashi, Y. Comprehensive analysis of determining factors of the effective work function of TiAlC/TiN metal gates for advanced gate-all-around CMOS integration. Jpn. J. Appl. Phys. 2025, 64, 01SP28. [Google Scholar] [CrossRef]

- Yin, Y.H.; Zhang, Z.F.; Zhong, H.X.; Shao, C.; Wan, X.H.; Zhang, C.; Robertson, J.; Guo, Y.Z. Tellurium Nanowire Gate-All-Around MOSFETs for Sub-5 nm Applications. ACS Appl. Mater. Interfaces 2021, 13, 3387–3396. [Google Scholar] [CrossRef] [PubMed]

- Ramesh, R.; Pon, A.; Babu, P.D.; Carmel, S.; Bhattacharyya, A. Optimization of Gate all-around Junctionless Transistor Using Response Surface Methodology. Silicon 2022, 14, 2499–2508. [Google Scholar] [CrossRef]

- Liu, S.-Q.; Li, Q.-H.; Yang, C.; Yang, J.; Xu, L.; Xu, L.-Q.; Ma, J.-C.; Li, Y.; Fang, S.-B.; Wu, B.-C.; et al. Performance Limit of Gate-All-Around Si Nanowire Field-Effect Transistors: An Ab Initio Quantum Transport Simulation. Phys. Rev. Appl. 2022, 18, 054089. [Google Scholar] [CrossRef]

- Han, M.-H.; Chang, C.-Y.; Jhan, Y.-R.; Wu, J.-J.; Chen, H.-B.; Cheng, Y.-C.; Wu, Y.-C. Characteristic of p-Type Junctionless Gate-All-Around Nanowire Transistor and Sensitivity Analysis. IEEE Electron Device Lett. 2013, 34, 157–159. [Google Scholar] [CrossRef]

- Lin, Y.W.; Lin, S.W.; Chen, B.A.; Sun, C.J.; Yan, S.C.; Luo, G.L.; Wu, Y.C.; Hou, F.J. 3-D Self-Aligned Stacked Ge Nanowire pGAAFET on Si nFinFET of Single Gate CFET. IEEE J. Electron Devices Soc. 2023, 11, 480–484. [Google Scholar] [CrossRef]

- Gautam, R.; Saxena, M.; Gupta, R.S.; Gupta, M. Gate-All-Around Nanowire MOSFET With Catalytic Metal Gate For Gas Sensing Applications. IEEE Trans. Nanotechnol. 2013, 12, 939–944. [Google Scholar] [CrossRef]

- Won, H.; Kang, M. Analysis of Circuit Simulation Considering Total Ionizing Dose Effects on FinFET and Nanowire FET. Appl. Sci. 2021, 11, 894. [Google Scholar] [CrossRef]

- Ma, J.; Nissimagoudar, A.S.; Li, W. First-principles study of electron and hole mobilities of Si and GaAs. Phys. Rev. B 2018, 97, 045201. [Google Scholar] [CrossRef]

- Ridley, K. Hybrid Phonons in Nanostructures; Oxford University Press: Oxford, UK, 2017. [Google Scholar] [CrossRef]

- Zakhleniuk, N.A.; Bennett, C.R.; Stavrou, V.N.; Babiker, M.; Ridley, B.K. Quantum capture of injected electrons in GaN-based laser heterostructures. Phys. Status Solidi A 1999, 176, 79–83. [Google Scholar] [CrossRef]

- Neophytos, N.; Oskar, B.; Zlatan, S.; Hans, K. Bandstructure and mobility variations in p-type silicon nanowires under electrostatic gate field. Solid-State Electron. 2013, 90, 44–50. [Google Scholar] [CrossRef]

- Khaliq, A.; Ali, M.; Mateen, M.; Huang, S.-H. Channel engineering for optimizing the electro-thermal characteristics in p-type GAA nanosheet transistors. Int. J. Numer. Model. Devices Fields 2024, 37, e3225. [Google Scholar] [CrossRef]

- Zhang, Y.N.; Han, K.; Li, J.W. A Simulation Study of a Gate-All-Around Nanowire Transistor with a Core–Insulator. Micromachines 2020, 11, 223. [Google Scholar] [CrossRef] [PubMed]

- Vashishtha, V.; Clark, L.T. Comparing bulk-Si FinFET and gate-all-around FETs for the 5 nm technology node. Microelectron. J. 2021, 107, 104942. [Google Scholar] [CrossRef]

- Yilmaz, K.; Darbandy, G.; Reimbold, G.; Iniguez, B.; Lime, F.; Kloes, A. Equivalent DG Dimensions Concept for Compact Modeling of Short-Channel and Thin Body GAA MOSFETs Including Quantum Confinement. IEEE Trans. Electron Devices 2020, 67, 5381–5387. [Google Scholar] [CrossRef]

- Yilmaz, K.; Iniguez, B.; Lime, F.; Kloes, A. Quasi-Compact Model of Direct Source-to-Drain Tunneling Current in Ultrashort-Channel Nanosheet MOSFETs by Wavelet Transform. IEEE Trans. Electron Devices 2022, 69, 17–24. [Google Scholar] [CrossRef]

- Lin, Y.K.; Duarte, J.P.; Kushwaha, P.; Agarwal, H.; Chang, H.L.; Sachid, A.; Salahuddin, S.; Hu, C.M. Compact Modeling Source-to-Drain Tunneling in Sub-10-nm GAA FinFET With Industry Standard Model. IEEE Trans. Electron Devices 2017, 64, 3576–3581. [Google Scholar] [CrossRef]

- Ganapati, R.; Samoju, V.R.; Jammu, B.R. Analytical Modeling of Threshold Voltage for Dual-Metal Double-Gate Gate-All-Around (DM-DG-GAA) MOSFET. Silicon 2021, 13, 2869–2880. [Google Scholar] [CrossRef]

- Cheng, H.; Uno, S.; Nakazato, K. Analytic compact model of ballistic and quasi-ballistic transport for cylindrical gate-all-around MOSFET including drain-induced barrier lowering effect. J. Comput. Electron 2014, 14, 321–328. [Google Scholar] [CrossRef]

- Cheng, H.; Liu, T.F.; Zhang, C.; Liu, Z.F.; Yang, Z.J.; Nakazato, K.; Zhang, Z.P. Nanowire gate-all-around MOSFETs modeling: Ballistic transport incorporating the source-to-drain tunneling. Jpn. J. Appl. Phys. 2020, 59, 074002. [Google Scholar] [CrossRef]

- Cheng, H.; Yang, Z.J.; Zhang, C.; Xie, C.; Liu, T.F.; Wang, J.; Zhang, Z.P. New Approach to Modeling Ultrashort Channel Ballistic Nanowire GAA MOSFETs. Nanomaterials 2022, 12, 3401. [Google Scholar] [CrossRef]

- Venugopal, R.; Ren, Z.B.; Lundstrom, M.S. Simulating quantum transport in nanoscale MOSFETs: Ballistic hole transport, subband engineering and boundary conditions. IEEE Trans. Nanotechnol. 2003, 2, 135–143. [Google Scholar] [CrossRef]

- Natori, K. Ballistic/quasi-ballistic transport in nanoscale transistor. Appl. Surf. Sci. 2008, 254, 6194–6198. [Google Scholar] [CrossRef]

- Natori, K.; Kimura, Y.; Shimizu, T. Characteristics of a carbon nanotube field-effect transistor analyzed as a ballistic nanowire field-effect transistor. J. Appl. Phys. 2005, 97, 034306. [Google Scholar] [CrossRef]

- Lundstrom, M. Fundamentals of Carrier Transport; Cambridge University Press: Cambridge, UK, 2000. [Google Scholar]

- Lundstrom, M.; Ren, Z.B. Essential Physics of Carrier Transport in Nanoscale MOSFETs. IEEE Trans. Electron Devices 2002, 49, 133–141. [Google Scholar] [CrossRef]

- Neamen, D.A. Semiconductor Physics and Devices: Basic Principles, 4th ed.; McGraw-Hill: New York, NY, USA, 2013. [Google Scholar]

- Cheng, H.; Uno, S.; Numata, T.; Nakazato, K. Analytic Compact Model of Ballistic and Quasi-Ballistic Cylindrical Gate-All-Around Metal-Oxide-Semiconductor Field Effect Transistors Including Two Subbands. Jpn. J. Appl. Phys 2013, 52, 04CN03. [Google Scholar] [CrossRef]

- Cheng, H.; Yang, Z.-J.; Zhang, C.; Zhang, Z.-P. A novel numerical modeling for p-type nanowire ballistic gate-all-around metal-oxide-semiconductor field-effect transistor. In Proceedings of the 2025 4th International Symposium on Semiconductor and Electronic Technology (ISSET), Xi’an, China, 25–27 July 2025; pp. 539–542. [Google Scholar] [CrossRef]

- Cheng, H.; Yang, Z.-J.; Cui, S.-P.; Zhang, Z.-P. An analytic model for p-type nanowire ballistic GAA MOSFET. In Proceedings of the 2025 4th International Symposium on Semiconductor and Electronic Technology (ISSET), Xi’an, China, 25–27 July 2025; pp. 534–538. [Google Scholar] [CrossRef]

- Numata, T.; Uno, S.; Nakazato, K.; Kamakura, Y.; Mori, N. Analytical Compact Model of Ballistic Cylindrical Nanowire Metal–Oxide–Semiconductor Field-Effect Transistor. Jpn. J. Appl. Phys. 2010, 49, 04DN05. [Google Scholar] [CrossRef]

- Silvaco International. Quantum Effect Simulation. In Electronic Archive: Atlas User’s Manual; Silvaco, Inc.: Santa Clara, CA, USA, 2016; Chapter 13; pp. 754–795. Available online: www.silvaco.com (accessed on 25 September 2022).

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheng, H.; Yang, Z.; Zhang, C.; Zhang, Z. An Analytic Compact Model for P-Type Quasi-Ballistic/Ballistic Nanowire GAA MOSFETs Incorporating DIBL Effect. Nanomaterials 2025, 15, 1734. https://doi.org/10.3390/nano15221734

Cheng H, Yang Z, Zhang C, Zhang Z. An Analytic Compact Model for P-Type Quasi-Ballistic/Ballistic Nanowire GAA MOSFETs Incorporating DIBL Effect. Nanomaterials. 2025; 15(22):1734. https://doi.org/10.3390/nano15221734

Chicago/Turabian StyleCheng, He, Zhijia Yang, Chao Zhang, and Zhipeng Zhang. 2025. "An Analytic Compact Model for P-Type Quasi-Ballistic/Ballistic Nanowire GAA MOSFETs Incorporating DIBL Effect" Nanomaterials 15, no. 22: 1734. https://doi.org/10.3390/nano15221734

APA StyleCheng, H., Yang, Z., Zhang, C., & Zhang, Z. (2025). An Analytic Compact Model for P-Type Quasi-Ballistic/Ballistic Nanowire GAA MOSFETs Incorporating DIBL Effect. Nanomaterials, 15(22), 1734. https://doi.org/10.3390/nano15221734