Wafer-Level Fabrication of Radiofrequency Devices Featuring 2D Materials Integration

Abstract

1. Introduction

2. Methodology

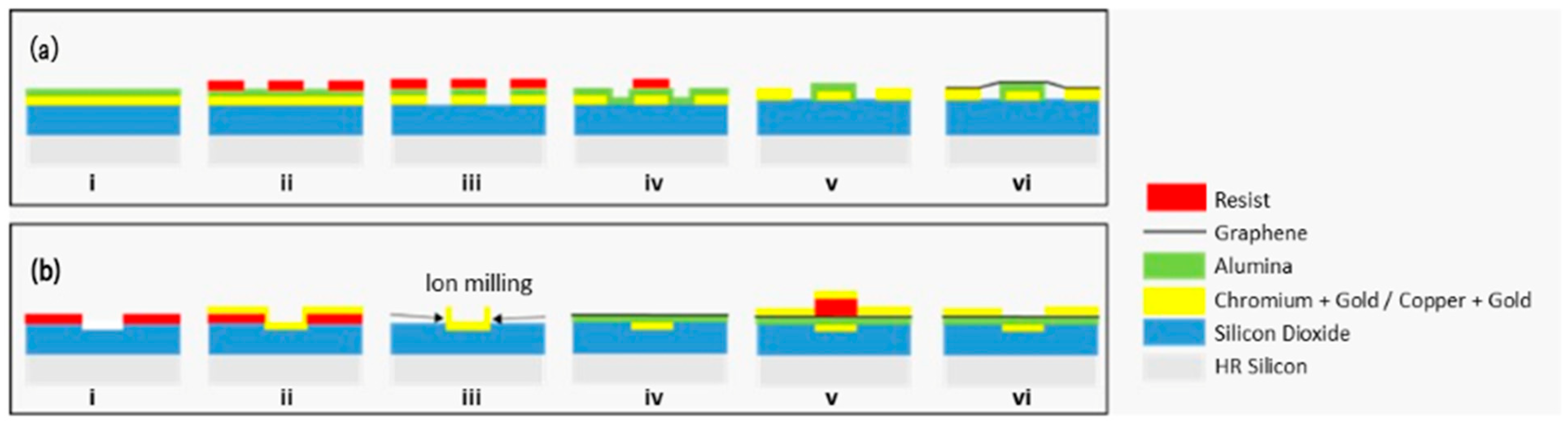

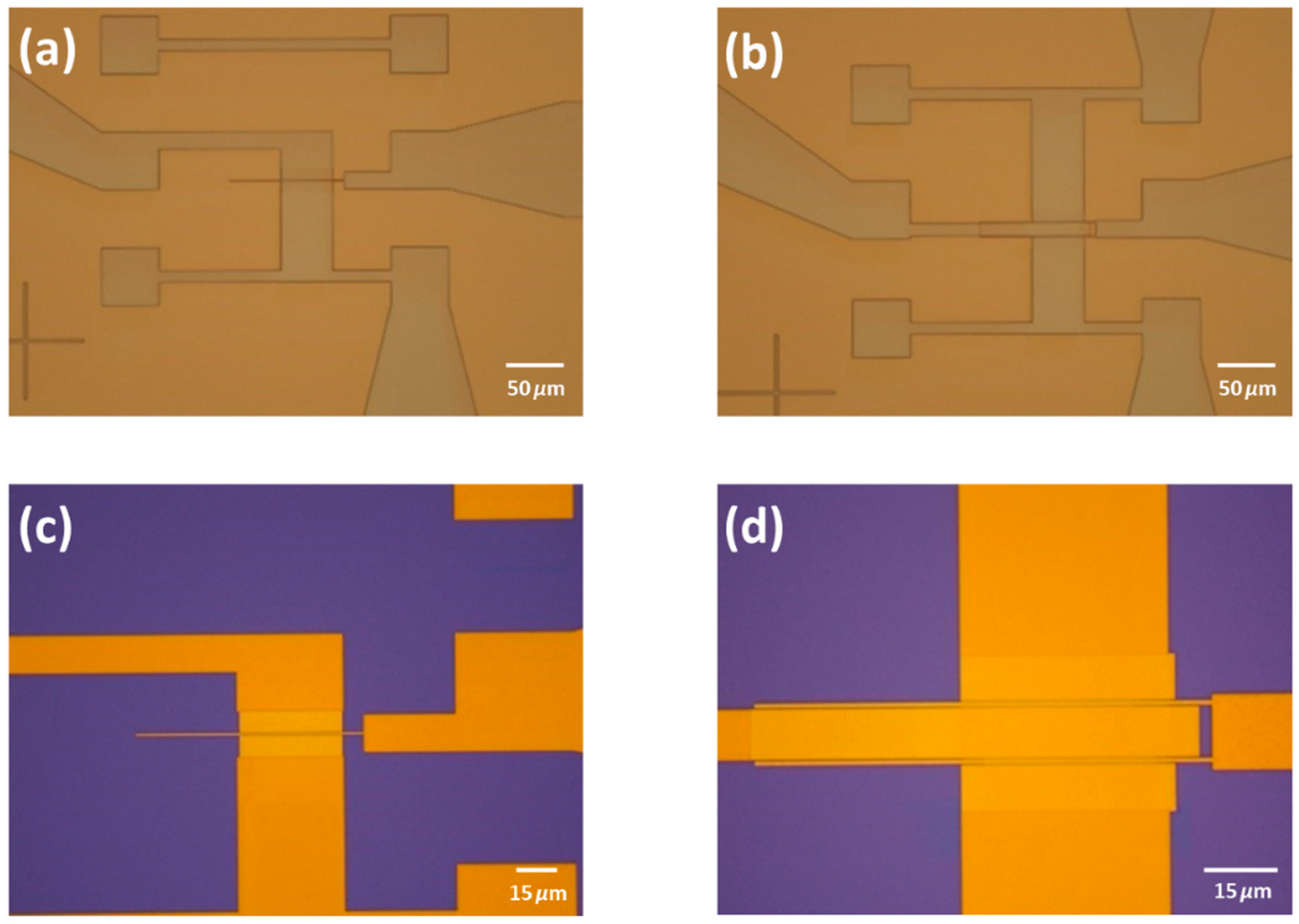

2.1. Graphene Device Fabrication Process with CPD

2.2. Graphene Device Fabrication Process with Surface Planarization

3. Performance Assessment of the Proposed Wafer-Level Fabrication

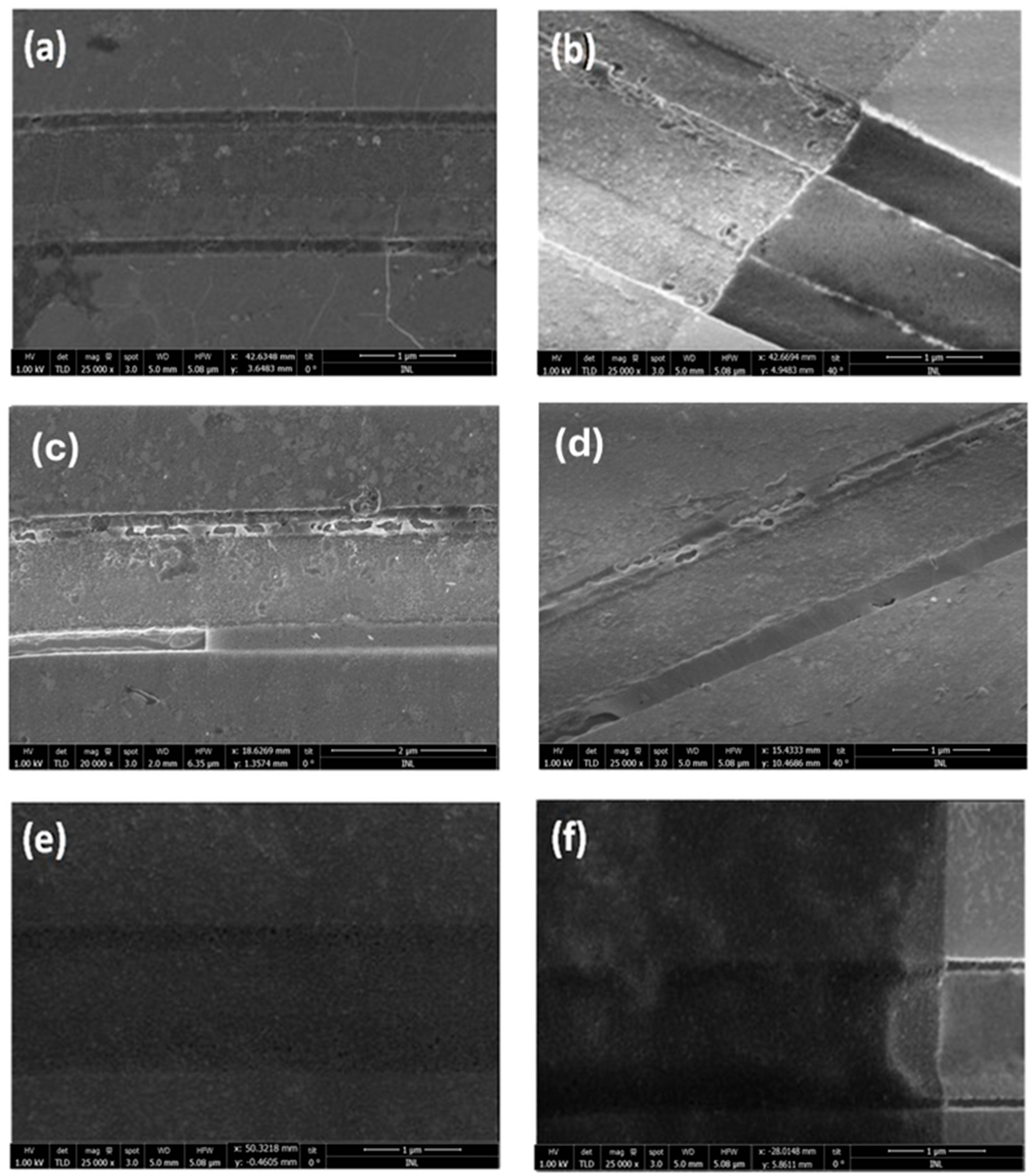

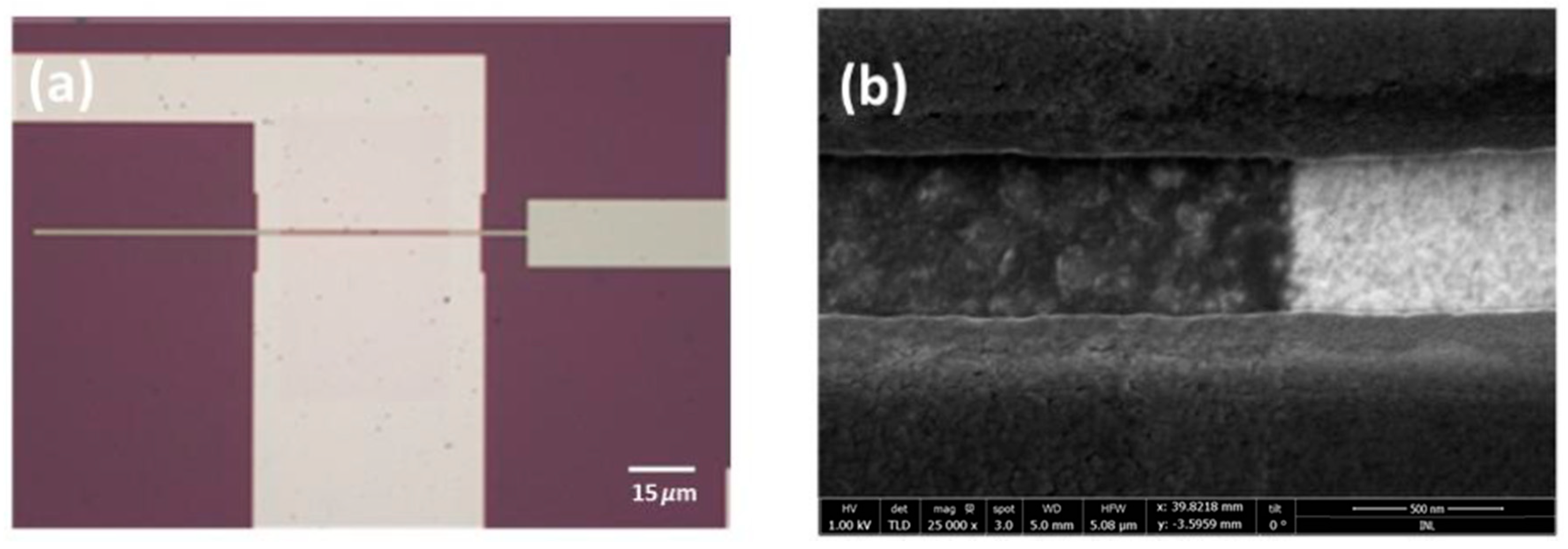

3.1. Graphene Quality Assessment

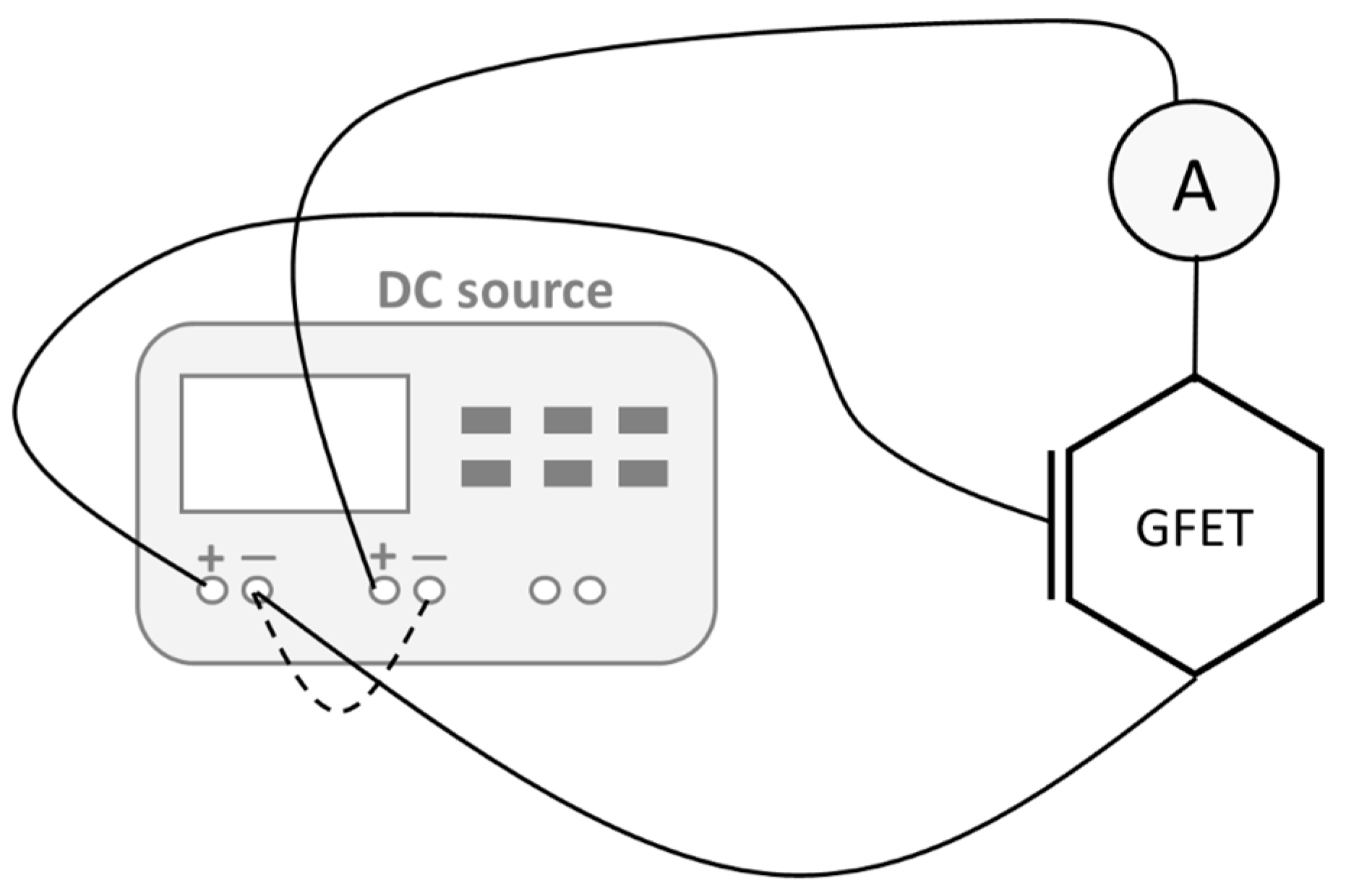

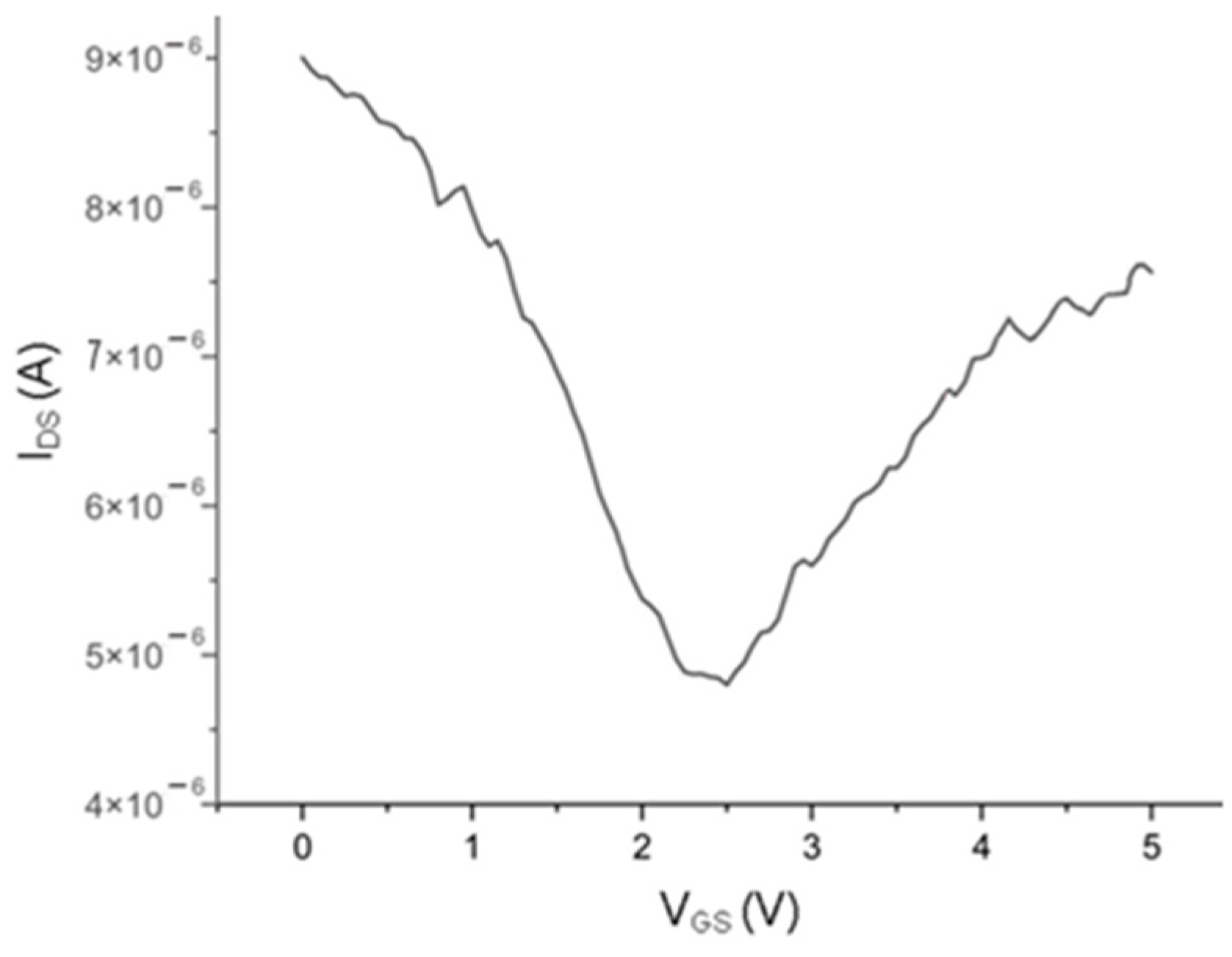

3.2. Low-Frequency Electrical Performance

3.2.1. Graphene Device Fabrication Process Without Surface Planarization (CPD)

3.2.2. Planar Buried Bottom-Gate Topology Improved

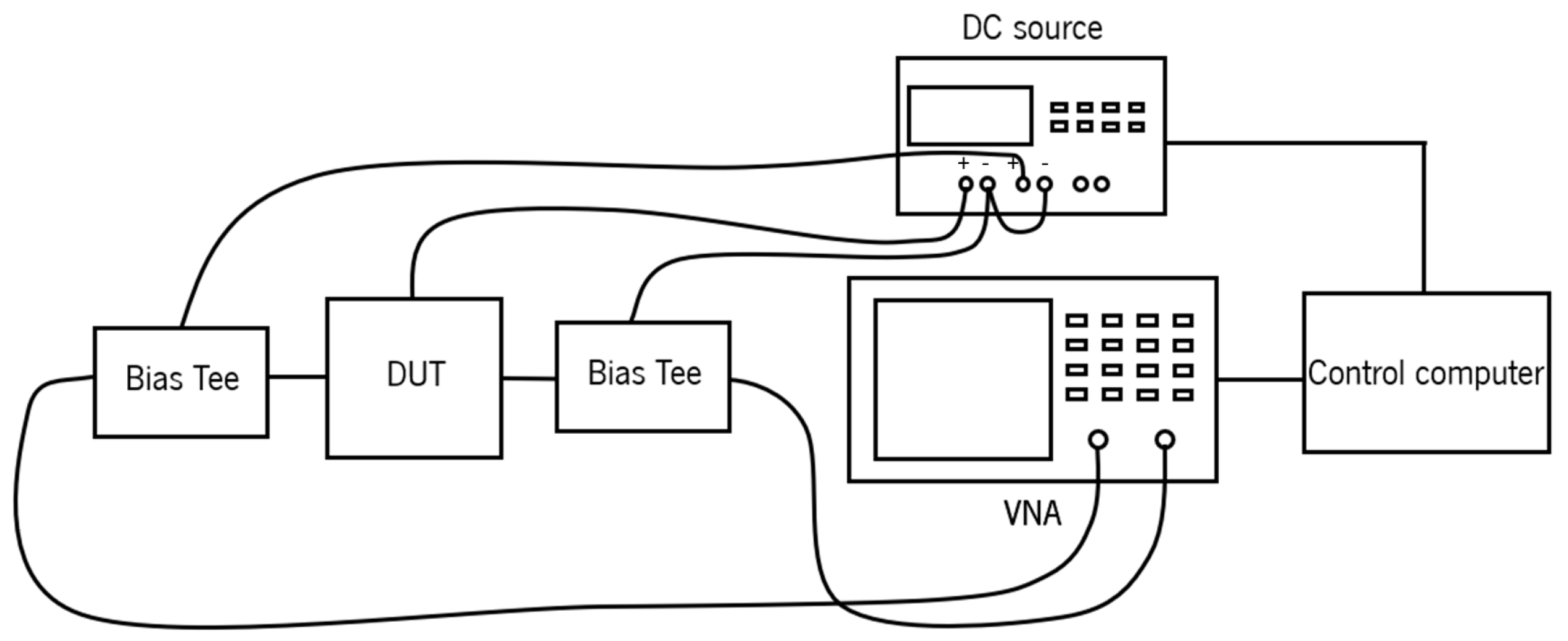

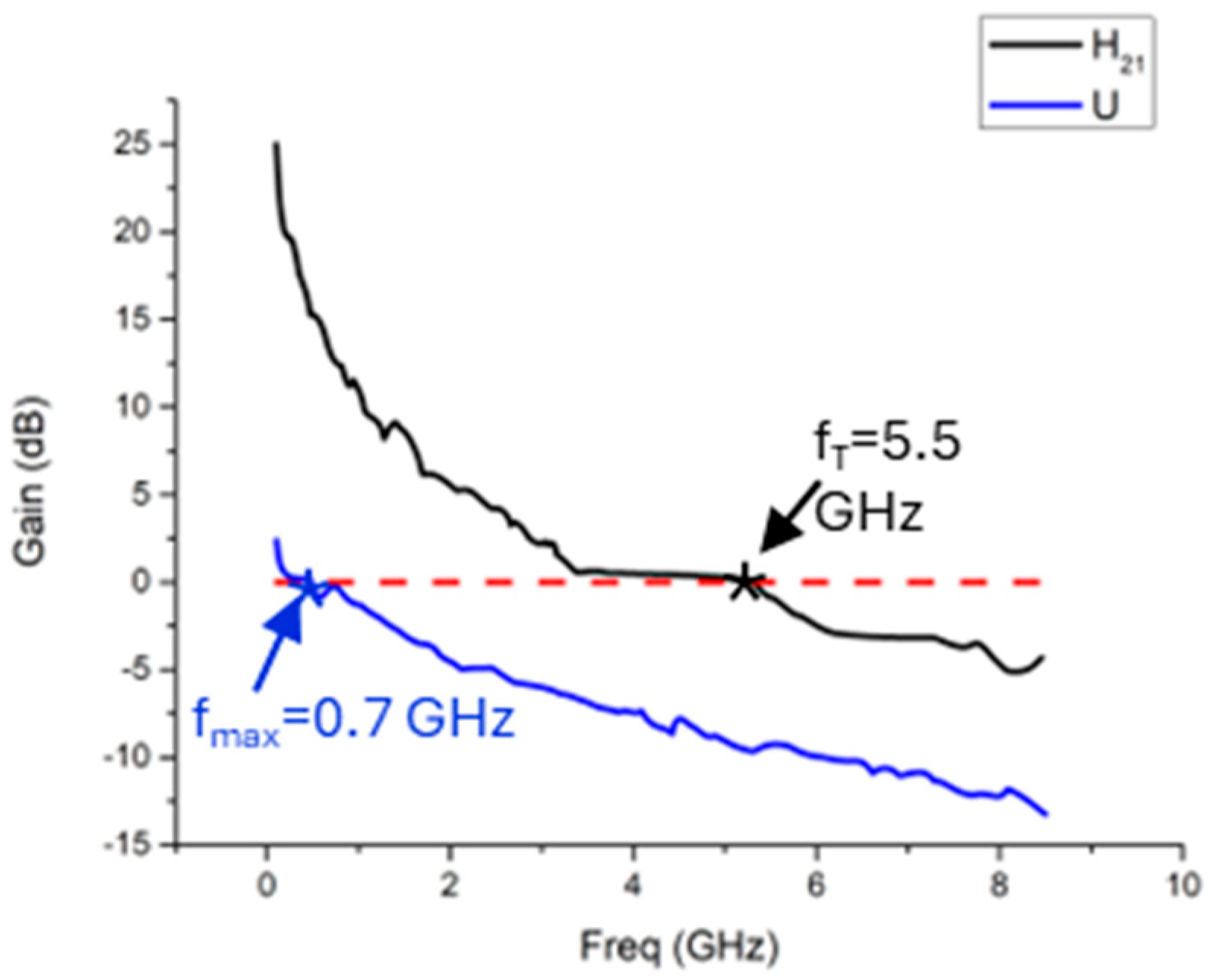

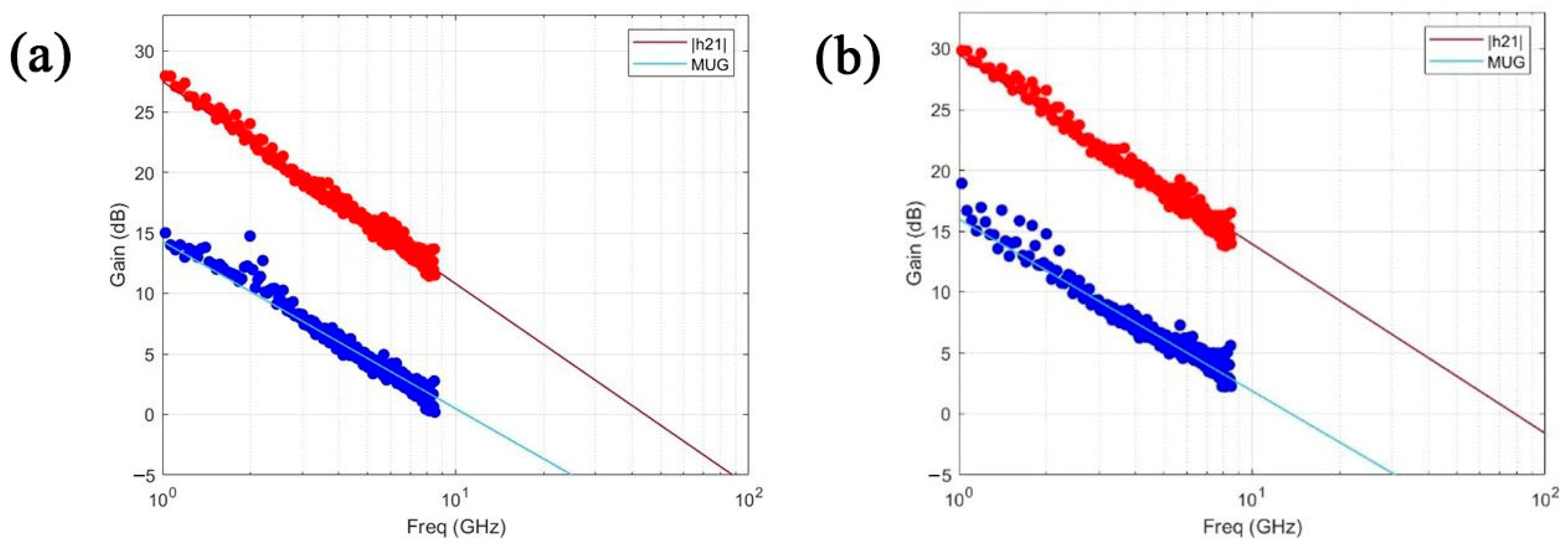

3.3. High-Frequency Electrical Performance

3.3.1. Graphene Device Fabrication Process with CPD

3.3.2. Planar Buried Bottom-Gate Topology

4. Performance Assessment of Fabricated RF Building Blocks

4.1. Performance Assessment of Fabricated Active Devices

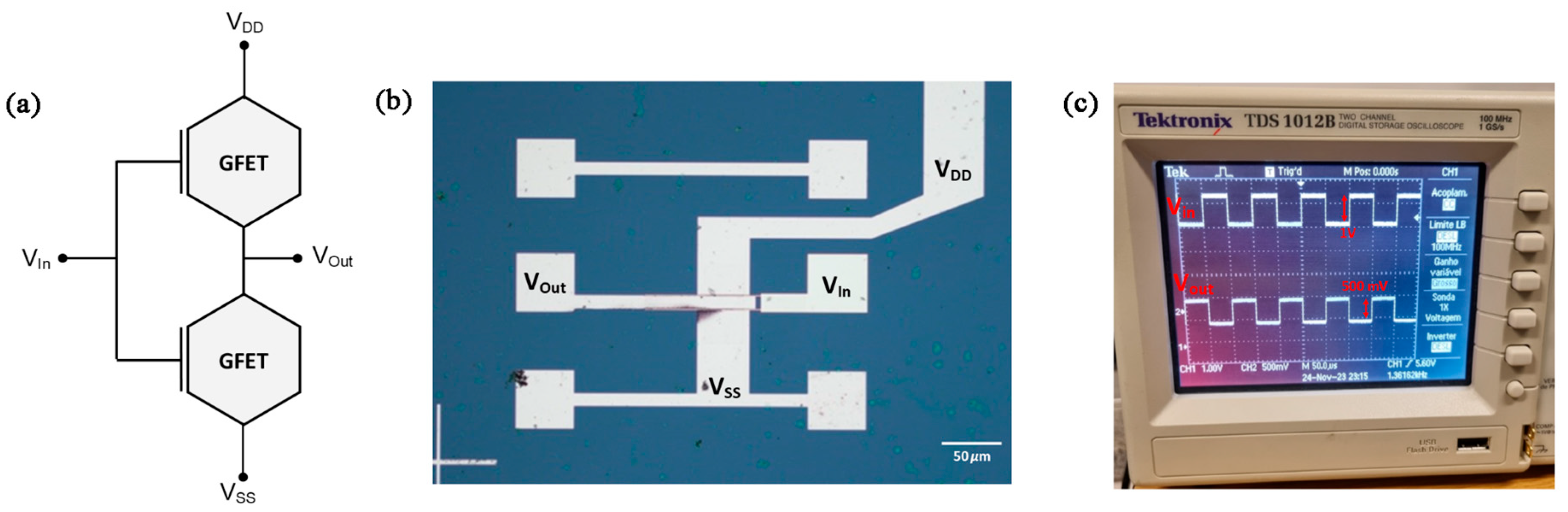

4.1.1. Transistor Integrated to Perform Digital Operations

4.1.2. Transistor Integrated to Perform Analog Operations

4.2. Performance Assessment of Fabricated Passive Devices

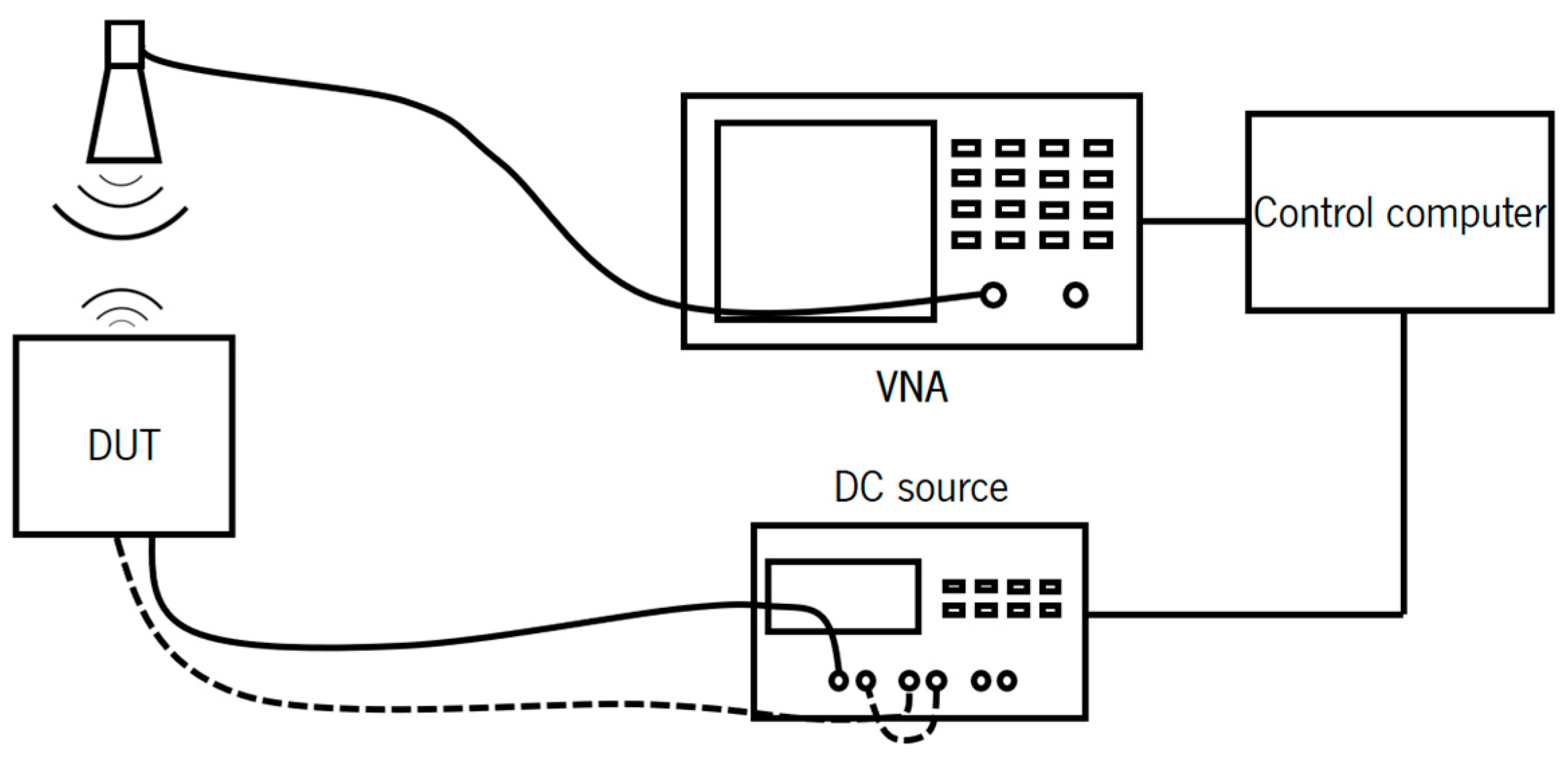

4.2.1. Wireless Sensing Readout Working Principle

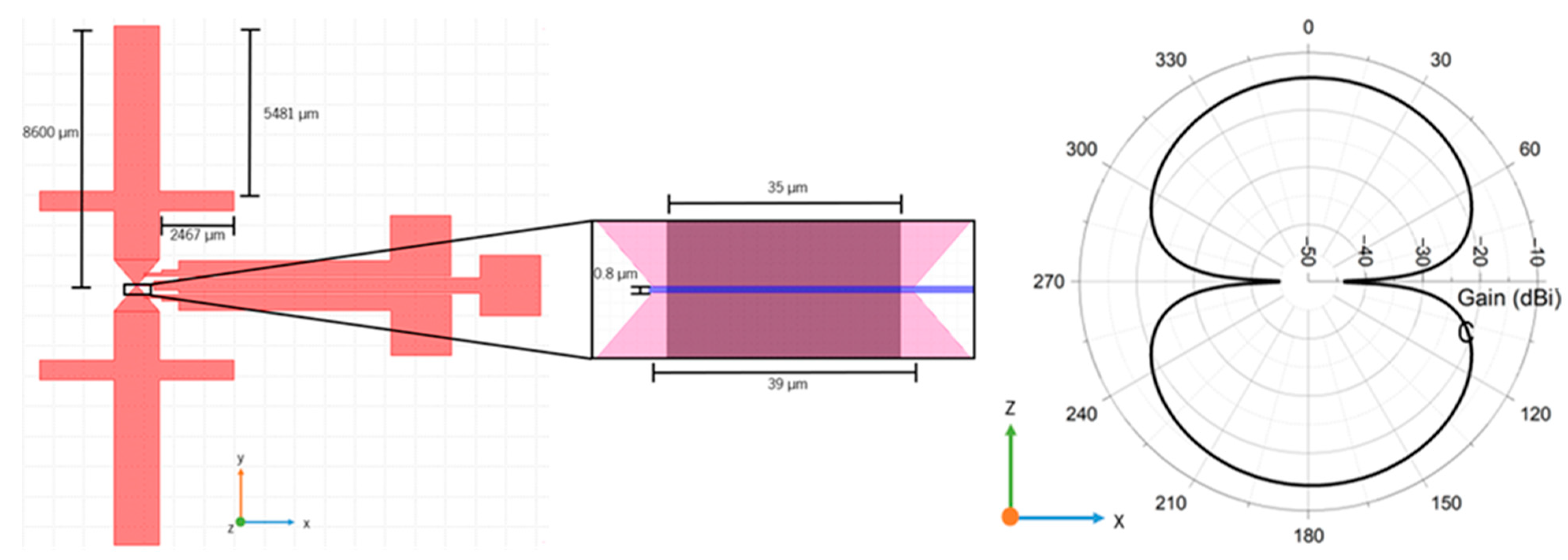

4.2.2. Sensing Antenna Design

4.2.3. Backscattering Antenna Readout

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Lee, S.; Zhong, Z. Nanoelectronic Circuits Based on Two-Dimensional Atomic Layer Crystals. Nanoscale 2014, 6, 13283–13300. [Google Scholar] [CrossRef] [PubMed]

- Zhu, W.; Perebeinos, V.; Freitag, M.; Avouris, P. Carrier Scattering, Mobilities, and Electrostatic Potential in Monolayer, Bilayer, and Trilayer Graphene. Phys. Rev. B Condens. Matter Mater Phys. 2009, 80, 235402. [Google Scholar] [CrossRef]

- Wu, Y.Q.; Farmer, D.B.; Valdes-Garcia, A.; Zhu, W.J.; Jenkins, K.; Dimitrakopoulos, C.; Avouris, P.; Lin, Y.-M. Record High RF Performance for Epitaxial Graphene Transistors. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; Volume 11, pp. 3690–3693. [Google Scholar]

- Peng, M.; Cheng, J.; Zheng, X.; Ma, J.; Feng, Z.; Sun, X. 2D-Materials-Integrated Optoelectromechanics: Recent Progress and Future Perspectives. Rep. Prog. Phys. 2023, 86, 026402. [Google Scholar] [CrossRef] [PubMed]

- Xue, H.; Gao, W.; Gao, J.; Schneider, G.F.; Wang, C.; Fu, W. Radiofrequency Sensing Systems Based on Emerging Two-Dimensional Materials and Devices. Int. J. Extrem. Manuf. 2023, 5, 032010. [Google Scholar] [CrossRef]

- Colmiais, I.; Silva, V.; Borme, J.; Alpuim, P.; Mendes, P.M. Towards RF Graphene Devices: A Review. FlatChem 2022, 35, 100409. [Google Scholar] [CrossRef]

- Cheng, R.; Bai, J.; Liao, L.; Zhou, H.; Chen, Y.; Liu, L.; Lin, Y.C.; Jiang, S.; Huang, Y.; Duan, X. High-Frequency Self-Aligned Graphene Transistors with Transferred Gate Stacks. Proc. Natl. Acad. Sci. USA 2012, 109, 11588–11592. [Google Scholar] [CrossRef] [PubMed]

- Gao, Q.; Xiong, X.; Li, X.; Wu, Y. High Performance Double-Gate Graphene Radio-Frequency Transistors. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018. [Google Scholar]

- Badmaev, A.; Che, Y.; Li, Z.; Wang, C.; Zhou, C. Self-Aligned Fabrication of Graphene Rf Transistors with t-Shaped Gate. ACS Nano 2012, 6, 3371–3376. [Google Scholar] [CrossRef] [PubMed]

- Liao, C.-D.; Capasso, A.; Queirós, T.; Domingues, T.; Cerqueira, F.; Nicoara, N.; Borme, J.; Freitas, P.; Alpuim, P. Optimizing PMMA Solutions to Suppress Contamination in the Transfer of CVD Graphene for Batch Production. Beilstein J. Nanotechnol. 2022, 13, 796–806. [Google Scholar] [CrossRef] [PubMed]

- Park, D.-W.; Mikael, S.; Chang, T.-H.; Gong, S.; Ma, Z. Bottom-Gate Coplanar Graphene Transistors with Enhanced Graphene Adhesion on Atomic Layer Deposition Al2O3. Appl. Phys. Lett. 2015, 106, 102106. [Google Scholar] [CrossRef]

- Heydrich, S.; Hirmer, M.; Preis, C.; Korn, T.; Eroms, J.; Weiss, D.; Schuller, C. Scanning Raman Spectroscopy of Graphene Antidot Lattices: Evidence for Systematic p-Type Doping. Appl. Phys. Lett. 2010, 97, 43113. [Google Scholar] [CrossRef]

- Levesque, P.L.; Sabri, S.S.; Aguirre, C.M.; Guillemette, J.; Siaj, M.; Desjardins, P.; Szkopek, T.; Martel, R. Probing Charge Transfer at Surfaces Using Graphene Transistors. Nano Lett. 2011, 11, 132–137. [Google Scholar] [CrossRef] [PubMed]

- Vieira, N.C.S.; Borme, J.; Machado, G.; Cerqueira, F.; Freitas, P.P.; Zucolotto, V.; Peres, N.M.R.; Alpuim, P. Graphene Field-Effect Transistor Array with Integrated Electrolytic Gates Scaled to 200 Mm. J. Phys. Condens. Matter 2016, 28, 085302. [Google Scholar] [CrossRef] [PubMed]

- Bianchi, M.; Guerriero, E.; Fiocco, M.; Alberti, R.; Polloni, L.; Behnam, A.; Carrion, E.A.; Pop, E.; Sordan, R. Scaling of Graphene Integrated Circuits. Nanoscale 2015, 7, 8076–8083. [Google Scholar] [CrossRef] [PubMed]

- Cabral, P.D.; Domingues, T.; Machado, G.; Chicharo, A.; Cerqueira, F.; Fernandes, E.; Athayde, E.; Alpuim, P.; Borme, J. Clean-Room Lithographical Processes for the Fabrication of Graphene Biosensors. Materials 2020, 13, 5728. [Google Scholar] [CrossRef] [PubMed]

- Abrantes, M.; Rodrigues, D.; Domingues, T.; Nemala, S.S.; Monteiro, P.; Borme, J.; Alpuim, P.; Jacinto, L. Ultrasensitive Dopamine Detection with Graphene Aptasensor Multitransistor Arrays. J. Nanobiotechnol. 2022, 20, 495. [Google Scholar] [CrossRef] [PubMed]

- Palacio, I.; Moreno, M.; Náñez, A.; Purwidyantri, A.; Domingues, T.; Cabral, P.D.; Borme, J.; Marciello, M.; Mendieta-Moreno, J.I.; Torres-Vázquez, B.; et al. Attomolar Detection of Hepatitis C Virus Core Protein Powered by Molecular Antenna-like Effect in a Graphene Field-Effect Aptasensor. Biosens. Bioelectron. 2023, 222, 115006. [Google Scholar] [CrossRef] [PubMed]

- Dinis, H.; Colmiais, I.; Mendes, P.M. A Multiantenna Approach to Maximize Wireless Power Transfered to Implantable Devices. In Proceedings of the 2017 International Applied Computational Electromagnetics Society Symposium-Italy (ACES), Firenze, Italy, 26–30 March 2017. [Google Scholar] [CrossRef]

- Colmiais, I.; Dinis, H.; Mendes, P.M. WPT System for Implantable Devices Using a Phased Array and Tracking Algorithm for Freely Moving Rats. In Proceedings of the 2019 IEEE 6th Portuguese Meeting on Bioengineering (ENBENG), Lisbon, Portugal, 22–23 February 2019; IEEE: Los Alamitos, CA, USA, 2019; pp. 1–4. [Google Scholar]

- Dinis, H.; Colmiais, I.; Mendes, P.M. Extending the Limits of Wireless Power Transfer to Miniaturized Implantable Electronic Devices. Micromachines 2017, 8, 359. [Google Scholar] [CrossRef] [PubMed]

- Dinis, H.; Colmiais, I.; Mendes, P.M. Design and Validation of a Six-Antenna WPT System with Tracking Capabilites for Biomedical Devices. In Proceedings of the 2019 17th IEEE International New Circuits and Systems Conference (NEWCAS), Munich, Germany, 23–26 June 2019; pp. 1–4. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Silva, V.; Colmiais, I.; Dinis, H.; Borme, J.; Alpuim, P.; Mendes, P.M. Wafer-Level Fabrication of Radiofrequency Devices Featuring 2D Materials Integration. Nanomaterials 2025, 15, 1119. https://doi.org/10.3390/nano15141119

Silva V, Colmiais I, Dinis H, Borme J, Alpuim P, Mendes PM. Wafer-Level Fabrication of Radiofrequency Devices Featuring 2D Materials Integration. Nanomaterials. 2025; 15(14):1119. https://doi.org/10.3390/nano15141119

Chicago/Turabian StyleSilva, Vitor, Ivo Colmiais, Hugo Dinis, Jérôme Borme, Pedro Alpuim, and Paulo M. Mendes. 2025. "Wafer-Level Fabrication of Radiofrequency Devices Featuring 2D Materials Integration" Nanomaterials 15, no. 14: 1119. https://doi.org/10.3390/nano15141119

APA StyleSilva, V., Colmiais, I., Dinis, H., Borme, J., Alpuim, P., & Mendes, P. M. (2025). Wafer-Level Fabrication of Radiofrequency Devices Featuring 2D Materials Integration. Nanomaterials, 15(14), 1119. https://doi.org/10.3390/nano15141119