Interface-Driven Electrothermal Degradation in GaN-on-Diamond High Electron Mobility Transistors

Abstract

1. Introduction

2. Device Details and Simulation Methods

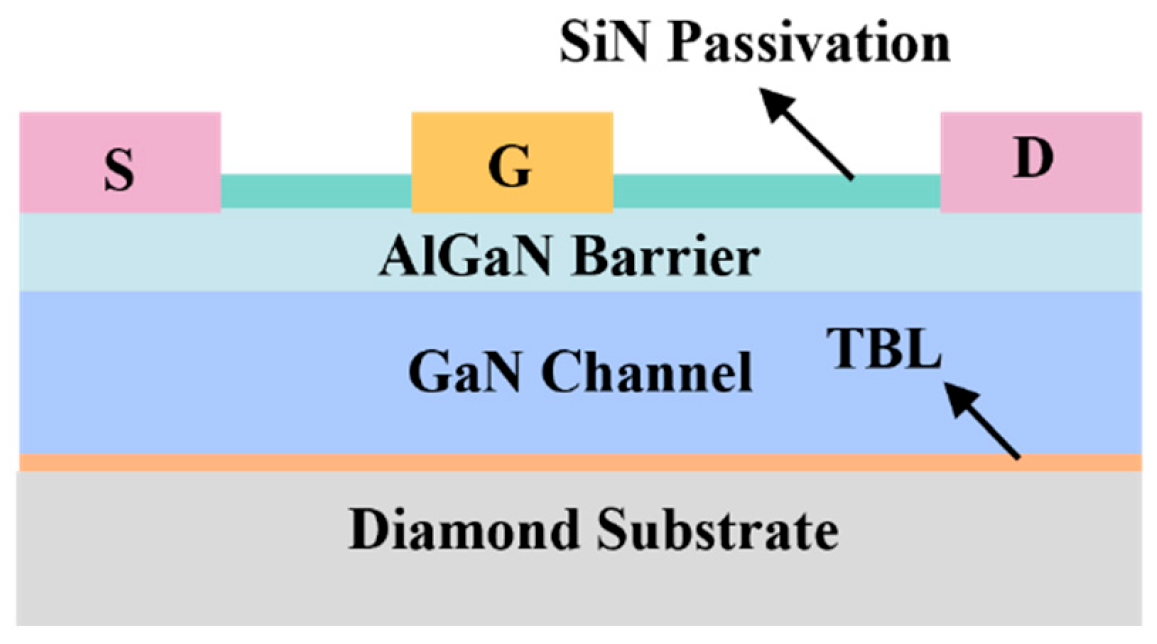

2.1. Device Model

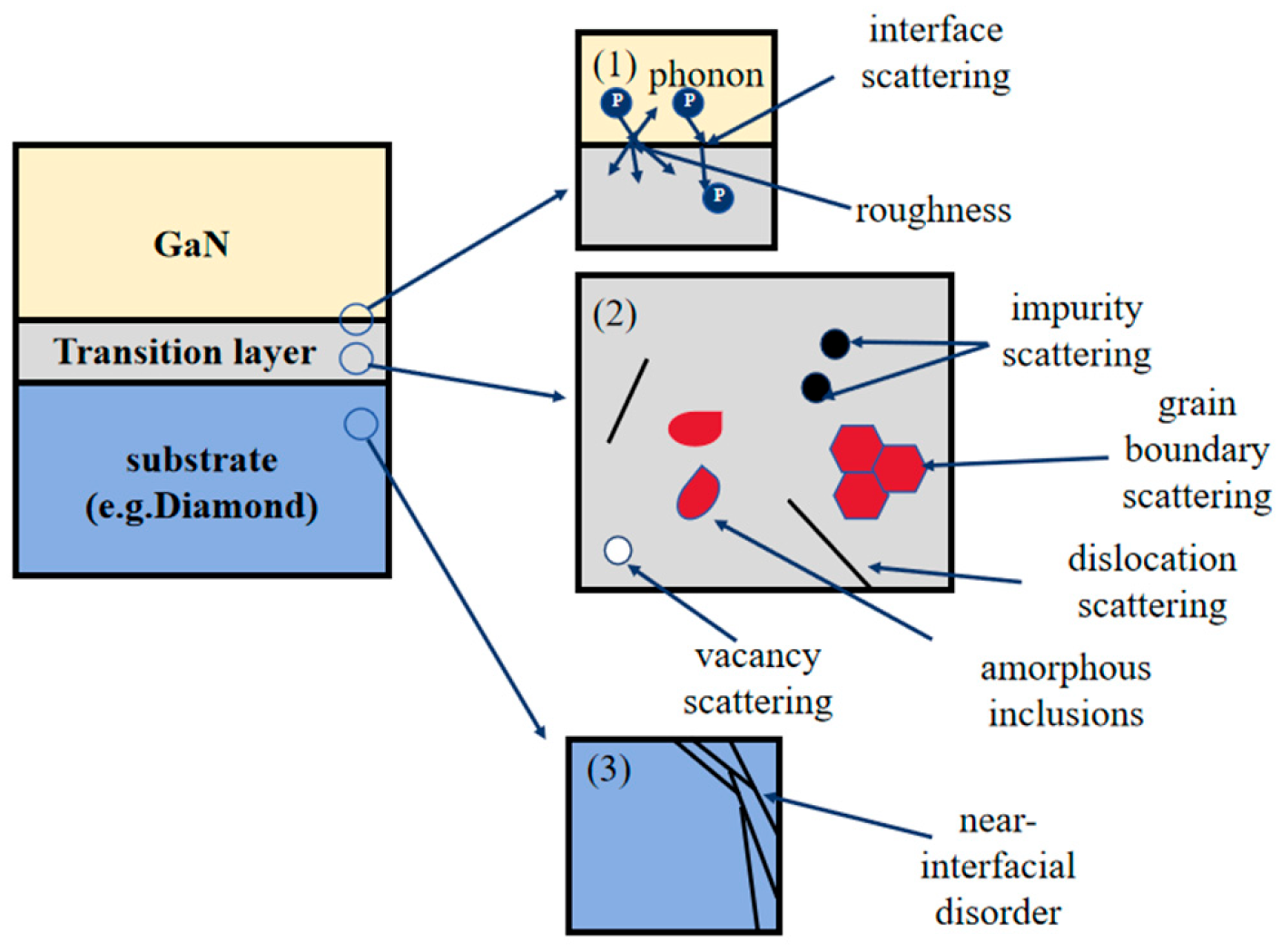

2.2. Simulation Methodologies

3. Simulation Results and Discussion

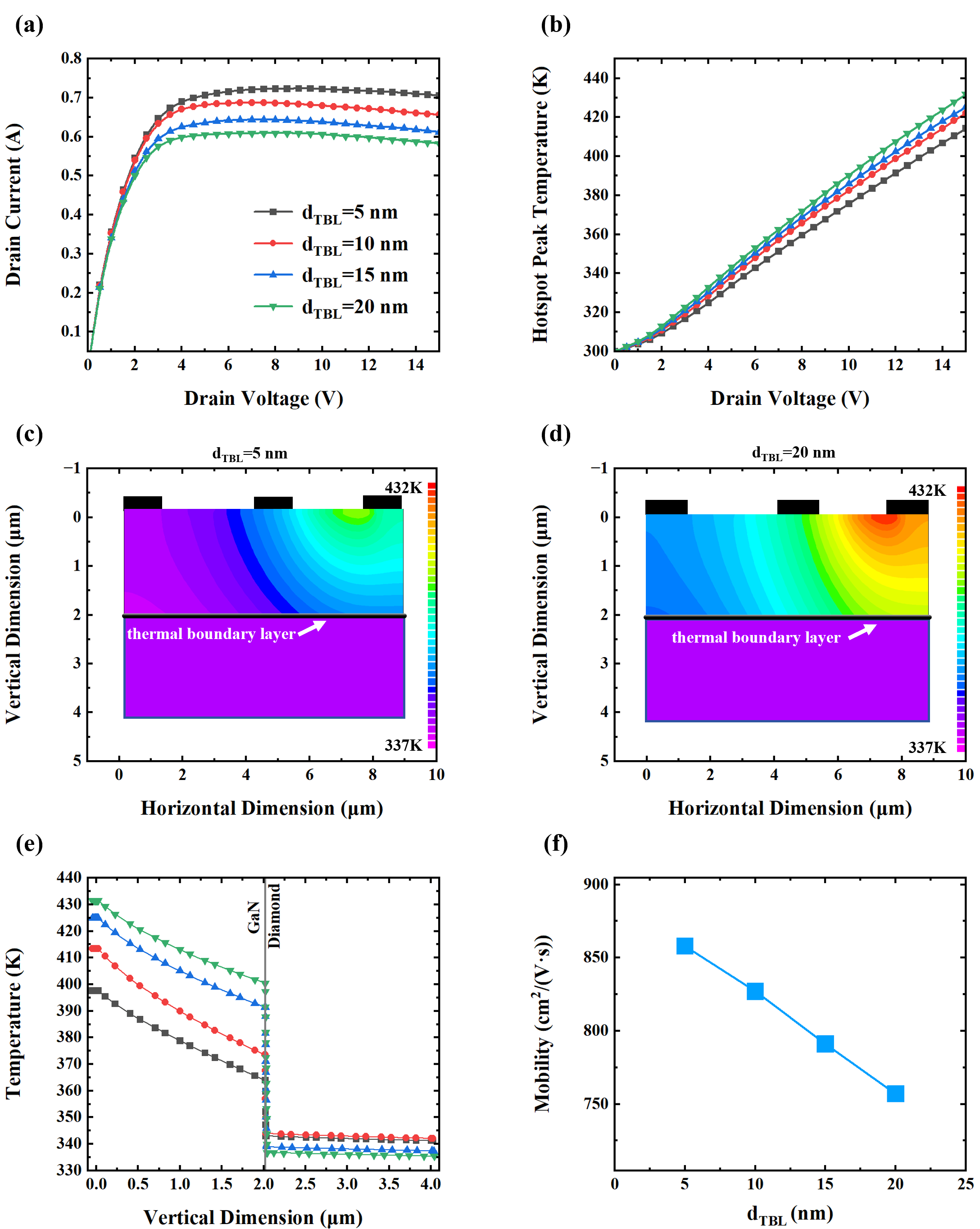

3.1. Effect of Thermal Boundary Layer Thickness

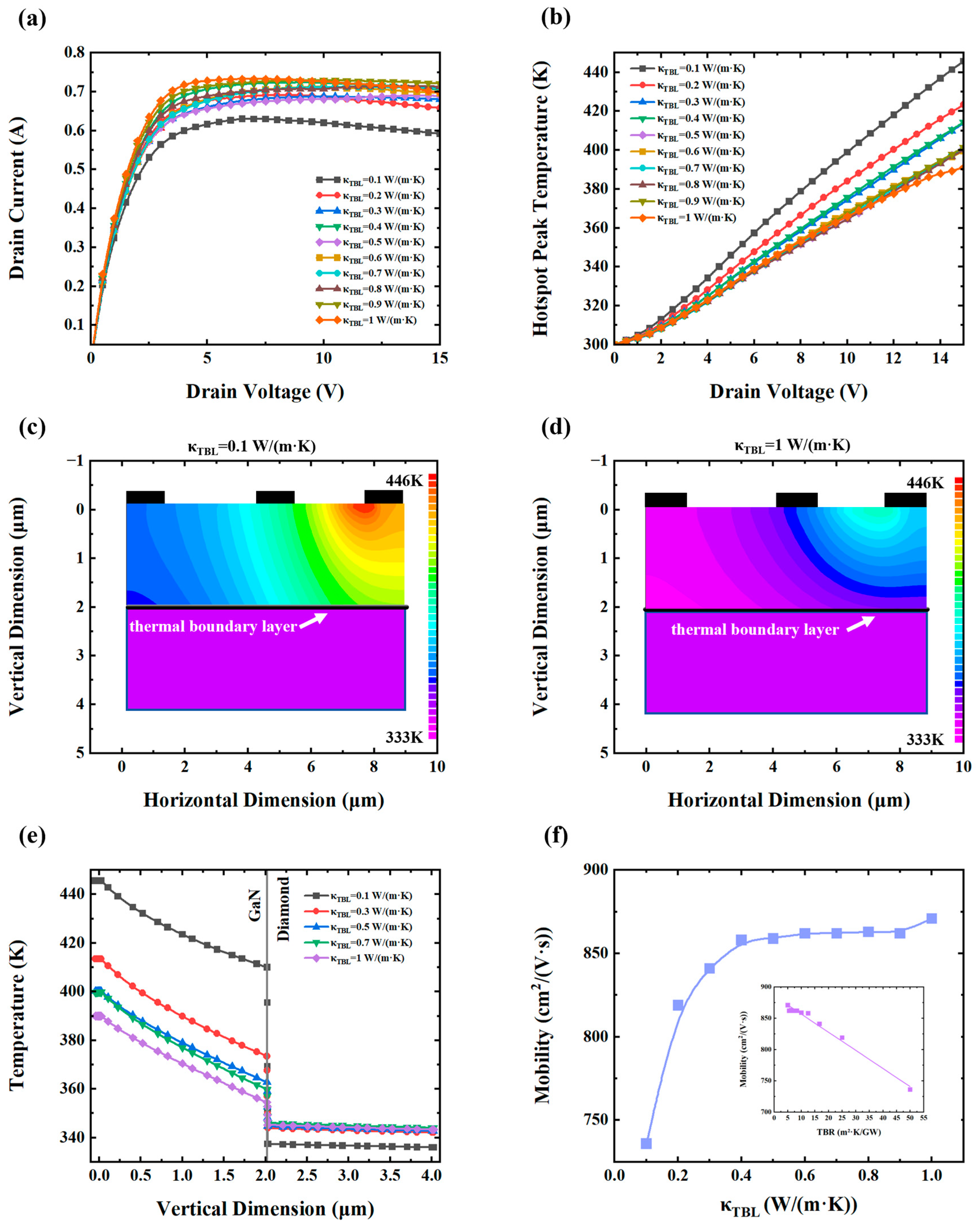

3.2. Effect of Thermal Boundary Layer Thermal Conductivity

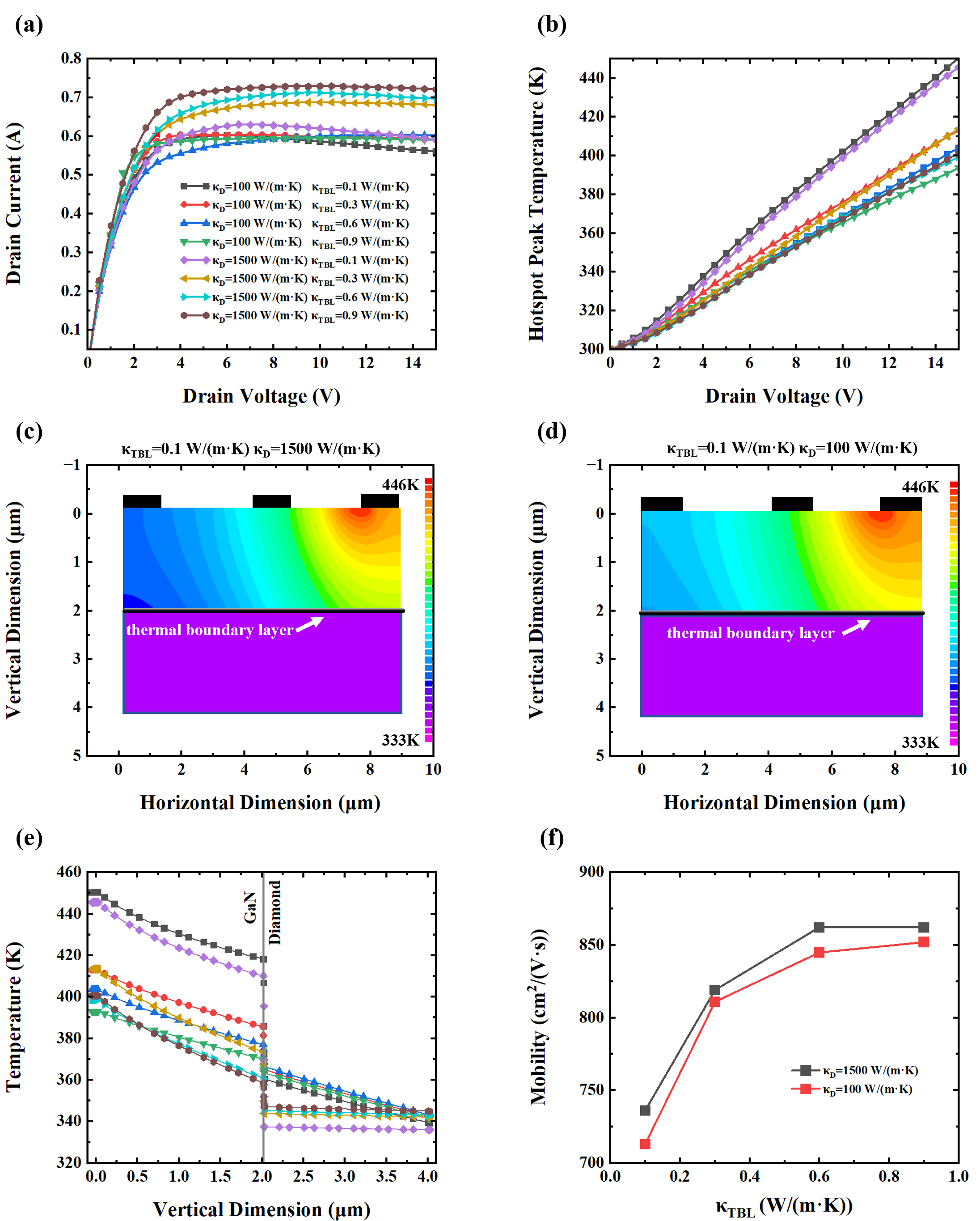

3.3. Effect Substrate and Thermal Boundary Layer Thermal Conductivity

4. Summary and Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chang, C.-Y.; Douglas, E.; Kim, J.; Lu, L.; Lo, C.-F.; Chu, B.-H.; Cheney, D.; Gila, B.P.; Ren, F.; Via, G.D.; et al. Electric-field-driven degradation in off-state step-stressed AlGaN/GaN high-electron mobility transistors. IEEE Trans. Device Mater. Reliab. 2011, 11, 187–193. [Google Scholar]

- Nigam, A.; Bhat, T.N.; Rajamani, S.; Dolmanan, S.B.; Tripathy, S.; Kumar, M. Effect of self-heating on electrical characteristics of AlGaN/GaN HEMT on Si (111) substrate. AIP Adv. 2017, 7, 085015. [Google Scholar] [CrossRef]

- Hu, B.; Wang, Z.; Xu, K.; Tang, D. Hotspot and nonequilibrium thermal transport in AlGaN/GaN FinFET: A coupled electron-phonon Monte Carlo simulation study. Int. J. Heat Mass Transf. 2025, 241, 126679. [Google Scholar] [CrossRef]

- Chang, Y.; Zhang, Y.; Zhang, Y.; Tong, K. A thermal model for static current characteristics of AlGaN/GaN high electron mobility transistors including self-heating effect. J. Appl. Phys. 2006, 99, 044501. [Google Scholar]

- Lee, S.; Vetury, R.; Brown, J.D.; Gibb, S.R.; Cai, W.Z.; Sun, J.; Green, D.S.; Shealy, J. Reliability assessment of AlGaN/GaN HEMT technology on SiC for 48V applications. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; pp. 446–449. [Google Scholar]

- Wang, A.; Tadjer, M.; Calle, F. Simulation of thermal management in AlGaN/GaN HEMTs with integrated diamond heat spreaders. Semicond. Sci. Technol. 2013, 28, 055010. [Google Scholar]

- Jeon, D.-Y.; Koh, Y.; Cho, C.-Y.; Park, K.-H. Impact of temperature-dependent series resistance on the operation of AlGaN/GaN high electron mobility transistors. AIP Adv. 2021, 11, 115203. [Google Scholar] [CrossRef]

- Liu, W.; Turin, V.; Balandin, A.; Chen, Y.; Wang, K. The ambient temperature effect on current-voltage characteristics of surface-passivated GaN-based field-effect transistors. MRS Internet J. Nitride Semicond. Res. 2004, 9, 7. [Google Scholar]

- Liu, C.; Chen, Y.; Xie, Y.; Liu, H.; Cai, Z. Electrical Properties and Reliability of AlGaN/GaN High Electron Mobility Transistor under RF Overdrive Stress at High Temperature. Micromachines 2024, 15, 1100. [Google Scholar] [CrossRef]

- Pomeroy, J.W.; Bernardoni, M.; Dumka, D.; Fanning, D.; Kuball, M. Low thermal resistance GaN-on-diamond transistors characterized by three-dimensional Raman thermography mapping. Appl. Phys. Lett. 2014, 104, 083513. [Google Scholar] [CrossRef]

- Tang, D.-S.; Cao, B.-Y. Phonon thermal transport and its tunability in GaN for near-junction thermal management of electronics: A review. Int. J. Heat Mass Transf. 2023, 200, 123497. [Google Scholar] [CrossRef]

- Francis, D.; Faili, F.; Babić, D.; Ejeckam, F.; Nurmikko, A.; Maris, H. Formation and characterization of 4-inch GaN-on-diamond substrates. Diam. Relat. Mater. 2010, 19, 229–233. [Google Scholar] [CrossRef]

- Yahya, N.; Nor, R.M.; Bakar, S.A.; Thandavan, T.M.; Rusop, M. Diamond: Synthesis, characterisation and applications. In Carbon and Oxide Nanostructures: Synthesis, Characterisation and Applications; Springer: Berlin/Heidelberg, Germany, 2011; pp. 195–217. [Google Scholar]

- Sun, H.; Simon, R.B.; Pomeroy, J.W.; Francis, D.; Faili, F.; Twitchen, D.J.; Kuball, M. Reducing GaN-on-diamond interfacial thermal resistance for high power transistor applications. Appl. Phys. Lett. 2015, 106, 111906. [Google Scholar] [CrossRef]

- Okamoto, N.; Minoura, Y.; Sato, M.; Ohki, T.; Ozaki, S.; Makiyama, K.; Yamada, A.; Kotani, J.; Joshin, K.; Nakamura, N. Thermal analysis of GaN-HEMT/SiC on diamond by surface activated bonding. Diamond 2018, 1, 75–78. [Google Scholar]

- Zhou, Y.; Anaya, J.; Pomeroy, J.; Sun, H.; Gu, X.; Xie, A.; Beam, E.; Becker, M.; Grotjohn, T.A.; Lee, C. Barrier-layer optimization for enhanced GaN-on-diamond device cooling. ACS Appl. Mater. Interfaces 2017, 9, 34416–34422. [Google Scholar]

- Won, Y.; Cho, J.; Agonafer, D.; Asheghi, M.; Goodson, K.E. Fundamental cooling limits for high power density gallium nitride electronics. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 737–744. [Google Scholar]

- Jia, X.; Wei, J.; Kong, Y.; Li, C.; Liu, J.; Chen, L.; Sun, F.; Wang, X. The influence of dielectric layer on the thermal boundary resistance of GaN-on-diamond substrate. Surf. Interface Anal. 2019, 51, 783–790. [Google Scholar] [CrossRef]

- Field, D.E.; Cuenca, J.A.; Smith, M.; Fairclough, S.M.; Massabuau, F.C.; Pomeroy, J.W.; Williams, O.; Oliver, R.A.; Thayne, I.; Kuball, M. Crystalline interlayers for reducing the effective thermal boundary resistance in GaN-on-diamond. ACS Appl. Mater. Interfaces 2020, 12, 54138–54145. [Google Scholar] [CrossRef]

- Mu, F.; He, R.; Suga, T. Room temperature GaN-diamond bonding for high-power GaN-on-diamond devices. Scr. Mater. 2018, 150, 148–151. [Google Scholar] [CrossRef]

- Cheng, Z.; Mu, F.; Yates, L.; Suga, T.; Graham, S. Interfacial thermal conductance across room-temperature-bonded GaN/diamond interfaces for GaN-on-diamond devices. ACS Appl. Mater. Interfaces 2020, 12, 8376–8384. [Google Scholar] [CrossRef]

- Zhang, J.; Hao, Y.; Zhang, J.; Ni, J. The mobility of two-dimensional electron gas in AlGaN/GaN heterostructures with varied Al content. Sci. China Ser. F Inf. Sci. 2008, 51, 780–789. [Google Scholar] [CrossRef]

- Miyoshi, M.; Egawa, T.; Ishikawa, H. Structural characterization of strained AlGaN layers in different Al content AlGaN/GaN heterostructures and its effect on two-dimensional electron transport properties. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 2005, 23, 1527–1531. [Google Scholar] [CrossRef]

- Hang, D.; Chen, C.; Chen, Y.; Jiang, H.; Lin, J. AlxGa1−xN/GaN band offsets determined by deep-level emission. J. Appl. Phys. 2001, 90, 1887–1890. [Google Scholar] [CrossRef]

- Hasegawa, H.; Akazawa, M. Current Transport, Fermi Level Pinning, and Transient Behavior\ofGroup-III Nitride Schottky Barriers. J. Korean Phys. Soc. 2009, 55, 1167–1179. [Google Scholar]

- Zhang, G.; Zhao, M.; Yan, C.; Sun, B.; Wu, Z.; Chang, H.; Jin, Z.; Sun, J.; Liu, H. Thermal analysis of AlGaN/GaN high-electron-mobility transistors with graphene. J. Nanosci. Nanotechnol. 2018, 18, 7578–7583. [Google Scholar]

- Selberherr, S. Analysis and Simulation of Semiconductor Devices; Springer Science & Business Media: Berlin, Germany, 2012. [Google Scholar]

- Meneghini, M.; Rossetto, I.; De Santi, C.; Rampazzo, F.; Tajalli, A.; Barbato, A.; Ruzzarin, M.; Borga, M.; Canato, E.; Zanoni, E. Reliability and failure analysis in power GaN-HEMTs: An overview. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 3B-2.1–3B-2.8. [Google Scholar]

- Piprek, J. Semiconductor Optoelectronic Devices: Introduction to Physics and Simulation; Elsevier: Amsterdam, The Netherlands, 2013. [Google Scholar]

- Mendes, J.C.; Liehr, M.; Li, C. Diamond/GaN HEMTs: Where from and where to? Materials 2022, 15, 415. [Google Scholar]

- Liu, D.; Fabes, S.; Li, B.-S.; Francis, D.; Ritchie, R.O.; Kuball, M. Characterization of the interfacial toughness in a novel “GaN-on-diamond” material for high-power RF devices. ACS Appl. Electron. Mater. 2019, 1, 354–369. [Google Scholar] [CrossRef]

- Das, S.K.; Putra, N.; Thiesen, P.; Roetzel, W. Temperature dependence of thermal conductivity enhancement for nanofluids. J. Heat Transf. 2003, 125, 567–574. [Google Scholar] [CrossRef]

- Zheng, Q.; Li, C.; Rai, A.; Leach, J.H.; Broido, D.A.; Cahill, D.G. Thermal conductivity of GaN, GaN 71, and SiC from 150 K to 850 K. Phys. Rev. Mater. 2019, 3, 014601. [Google Scholar] [CrossRef]

- Wang, K.; Hu, W.; Wu, S.; Wang, H.; Padhiar, M.A.; Ji, Y. Simulation investigation of effects of substrate and thermal boundary resistance on performances of AlGaN/GaN HEMTs. Phys. Scr. 2024, 99, 065554. [Google Scholar]

- Deng, X.; Zhang, B.; Li, Z. Electro-thermal analytical model and simulation of the self-heating effects in multi-finger 4H-SiC power MESFETs. Semicond. Sci. Technol. 2007, 22, 1339. [Google Scholar] [CrossRef]

- Li, S.S.; Thurber, W.R. The dopant density and temperature dependence of electron mobility and resistivity in n-type silicon. Solid-State Electron. 1977, 20, 609–616. [Google Scholar]

- Mahalingam, M. Thermal management in semiconductor device packaging. Proc. IEEE 1985, 73, 1396–1404. [Google Scholar]

- Adnan, K.Z.; Feng, T. Thermal boundary conductance and thermal conductivity strongly depend on nearby environment. Phys. Rev. B 2024, 109, 245302. [Google Scholar] [CrossRef]

- Xu, B.; Mu, F.; Liu, Y.; Guo, R.; Hu, S.; Shiomi, J. Record-Low thermal boundary resistance at bonded GaN/diamond interface by controlling ultrathin heterogeneous amorphous layer. Acta Mater. 2025, 282, 120458. [Google Scholar] [CrossRef]

- Yang, C.; Wang, J.; Ma, D.; Li, Z.; He, Z.; Liu, L.; Fu, Z.; Yang, J.-Y. Phonon transport across GaN-diamond interface: The nontrivial role of pre-interface vacancy-phonon scattering. Int. J. Heat Mass Transf. 2023, 214, 124433. [Google Scholar] [CrossRef]

- Zhang, C.; Liu, X.; Shao, C.; Sun, J.; Zhu, X.; Zhong, J.; Wang, S.; Liu, Q.; An, M.; Li, S. Self-Heating Aggravation in Mosfets Induced by Size-Dependent Lattice Thermal Conductivity of Semiconductors. Available online: https://ssrn.com/abstract=5151597 (accessed on 1 July 2025).

- Ko, T.-S.; Lin, D.-Y.; Lin, C.-F.; Chang, C.-W.; Zhang, J.-C.; Tu, S.-J. High-temperature carrier density and mobility enhancements in AlGaN/GaN HEMT using AlN spacer layer. J. Cryst. Growth 2017, 464, 175–179. [Google Scholar] [CrossRef]

- Neamen, D.A. Semiconductor Physics and Devices: Basic Principles; McGraw-hill: New York, NY, USA, 2003. [Google Scholar]

- Wang, Q.; Shao, C.; Xiong, Y.; Li, S.; Wang, R.; Sun, J.; Liu, Y.; Liu, X. Unlocking phonon dynamics at interfaces: Angle-resolved transmission, mode conversion, and thermal conductance engineering. Int. J. Heat Mass Transf. 2025, 250, 127318. [Google Scholar]

- Wang, Q.; Zhang, J.; Xiong, Y.; Li, S.; Chernysh, V.; Liu, X. Phonon dynamic behaviors induced by amorphous layers at heterointerfaces. Phys. Chem. Chem. Phys. 2024, 26, 8397–8407. [Google Scholar] [CrossRef]

- Liu, X.; Wang, Q.; Wang, R.; Wang, S.; Liu, X. Impact of interfacial compositional diffusion on interfacial phonon scattering and transmission in GaN/AlN heterostructure. J. Appl. Phys. 2023, 133, 095101. [Google Scholar] [CrossRef]

- Farahmand, M.; Garetto, C.; Bellotti, E.; Brennan, K.F.; Goano, M.; Ghillino, E.; Ghione, G.; Albrecht, J.D.; Ruden, P.P. Monte Carlo simulation of electron transport in the III-nitride wurtzite phase materials system: Binaries and ternaries. IEEE Trans. Electron Devices 2002, 48, 535–542. [Google Scholar] [CrossRef]

- Sheng, Y.; Zhu, H.; Xie, S.; Lv, Q.; Xie, H.; Wang, H.; Lv, R.; Bao, H. Electrically-driven reversible phonon transport manipulation in two-dimensional heterostructures. Nat. Commun. 2025, 16, 1970. [Google Scholar] [CrossRef] [PubMed]

- Soleimanzadeh, R.; Naamoun, M.; Floriduz, A.; Khadar, R.A.; van Erp, R.; Matioli, E. Seed dibbling method for the growth of high-quality diamond on GaN. ACS Appl. Mater. Interfaces 2021, 13, 43516–43523. [Google Scholar] [CrossRef] [PubMed]

- Tijent, F.Z.; Faqir, M.; Chouiyakh, H.; Essadiqi, E.H. Integration methods of GaN and diamond for thermal management optimization. ECS J. Solid State Sci. Technol. 2021, 10, 074003. [Google Scholar] [CrossRef]

- Zhou, Y.; Ramaneti, R.; Anaya, J.; Korneychuk, S.; Derluyn, J.; Sun, H.; Pomeroy, J.; Verbeeck, J.; Haenen, K.; Kuball, M. Thermal characterization of polycrystalline diamond thin film heat spreaders grown on GaN HEMTs. Appl. Phys. Lett. 2017, 111, 041901. [Google Scholar] [CrossRef]

- García, S.; Íñiguez-de-la-Torre, I.; Mateos, J.; González, T.; Pérez, S. Impact of substrate and thermal boundary resistance on the performance of AlGaN/GaN HEMTs analyzed by means of electro-thermal Monte Carlo simulations. Semicond. Sci. Technol. 2016, 31, 065005. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Al0.25Ga0.75N barrier layer thickness | 20 nm |

| GaN buffer layer thickness | 2 µm |

| Thermal boundary layer thickness | 5 nm (unless stated otherwise) |

| Diamond substrate thickness | 2 µm |

| SiN passivation thickness | 50 nm |

| Source length (Ls) | 1 µm |

| Gate length (Lg) | 1.4 µm |

| Drain length (Ld) | 1 µm |

| Source to gate channel length (Lsg) | 1 µm |

| Gate to drain channel length (Lgd) | 6 µm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, H.; Liu, Y.; Dong, X.; Ullah, A.; Sun, J.; Zhang, C.; Xiong, Y.; Gu, P.; Chen, G.; Liu, X. Interface-Driven Electrothermal Degradation in GaN-on-Diamond High Electron Mobility Transistors. Nanomaterials 2025, 15, 1114. https://doi.org/10.3390/nano15141114

Wang H, Liu Y, Dong X, Ullah A, Sun J, Zhang C, Xiong Y, Gu P, Chen G, Liu X. Interface-Driven Electrothermal Degradation in GaN-on-Diamond High Electron Mobility Transistors. Nanomaterials. 2025; 15(14):1114. https://doi.org/10.3390/nano15141114

Chicago/Turabian StyleWang, Huanran, Yifan Liu, Xiangming Dong, Abid Ullah, Jisheng Sun, Chuang Zhang, Yucheng Xiong, Peng Gu, Ge Chen, and Xiangjun Liu. 2025. "Interface-Driven Electrothermal Degradation in GaN-on-Diamond High Electron Mobility Transistors" Nanomaterials 15, no. 14: 1114. https://doi.org/10.3390/nano15141114

APA StyleWang, H., Liu, Y., Dong, X., Ullah, A., Sun, J., Zhang, C., Xiong, Y., Gu, P., Chen, G., & Liu, X. (2025). Interface-Driven Electrothermal Degradation in GaN-on-Diamond High Electron Mobility Transistors. Nanomaterials, 15(14), 1114. https://doi.org/10.3390/nano15141114