Abstract

In this study, we investigate the impact of rising time on alternating current (AC) stress-induced degradation in amorphous indium–tin–gallium–zinc oxide (a-ITGZO) TFTs through both experiments and simulations. When AC bias stresses with rising and falling times (tr-f) of 400 ns, 200 ns, and 100 ns were applied to the a-ITGZO TFTs, the threshold voltage (VTH) shifted positively by 0.97 V, 2.68 V, and 2.83 V, respectively. These experimental results align with a stretched exponential model, which attributes the VTH to electron trapping in bulk dielectric states or at interface traps. The simulation results further validate the stretched exponential model by illustrating the potential distribution across the dielectric and channel layers as a function of tr-f and the density of states in the a-ITGZO TFT.

1. Introduction

Recently, oxide thin-film transistors (TFTs) have been integrated into low-temperature polycrystalline silicon and oxide (LTPO) TFTs, which are emerging as a next-generation backplane technology for portable electronics utilizing active matrix organic light-emitting diode (AMOLED) displays [1,2,3,4,5,6,7]. These displays demand not only high resolution and brightness, but also low power consumption and a fast response time. LTPO technology is to combine the high mobility of poly-Si TFTS for driving and the low leakage characteristic and uniformity of oxide TFTs for pixel switching. To enable high-performance LTPO TFTs in pixel circuits, the reliability of oxide TFTs under alternating current (AC) stress is critical, as they are inevitably exposed to AC stress in integrated gate driver circuits. This AC instability is a major contributor to the performance degradation of LTPO TFTs.

To date, research on the degradation of electrical characteristics in oxide TFTs under AC bias stress has primarily focused on the interface between the channel and the gate dielectric [8,9,10,11]. However, performance degradation in TFTs is generally attributed to both bulk traps within the gate dielectric and interface traps at the dielectric/channel boundary [12,13]. Despite this, limited attention has been given to the role of bulk traps in the gate dielectric under AC bias conditions. In addition, most research has been conducted on the AC bias stress applied to the drain electrode, not to the gate electrode [14,15,16]. However, the AC bias stress applied to the gate electrode can profoundly affect the performance of TFTs, since the repetitive gate voltage pulse can accelerate trap generation and electron trapping within the gate dielectric and at the dielectric/channel interface.

In this study, we investigated the electrical characteristics of oxide TFTs under AC bias stress by considering both bulk traps within the gate dielectric and interface traps between the gate dielectric and the channel. Among the various AC parameters, the rising and falling times are fundamentally important for high-speed electronics [17]. In AMOLED driving circuits designed for high refresh rates, the gate electrodes of TFTs suffer from AC bias stress from high-frequency pulses. The rising edge of AC pulses brings about rapid changes in the potential across the gate dielectric and channel so that significant transient stress is applied to the TFTs. Thus, the rising edge of AC pulses is responsible for the performance degradation of TFTs. Hence, understanding the degradation mechanisms associated with AC bias stress under fast-rising conditions is essential for improving the reliability of TFTs in practical applications. Nevertheless, to date, there is little research on the degradation mechanisms in oxide TFTs from the rising edge of AC pulses. Therefore, we specifically examined the effect of rising time on AC stress-induced performance degradation in amorphous indium–tin–gallium–zinc oxide (a-ITGZO) TFTs through a combination of experimental analysis and simulation.

2. Materials and Methods

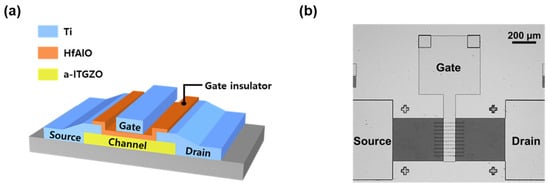

In this study, top-gate coplanar a-ITGZO TFTs with a split channel structure were fabricated on SiO2/p-type Si substrates. The split structure of the channel minimizes the parasitic series resistance so that it can enhance the field-effect mobility (μFE) and the on/off current ratio [18]. A 50 nm-thick a-ITGZO channel layer was deposited from an ITGZO target (In2O3:SnO2:Ga2O3:ZnO = 0.8:0.2:1:1 mol%, iTASCO, Korea) using radiofrequency (RF) magnetron sputtering (SCIEN Tech, Korea) under a gas mixture of Ar/O2 (47:30 sccm) at an RF power of 120 W and a working pressure of 1 mTorr. The channel length and width were 100 µm and 50 µm, respectively. The channel was formed by the ten split channels with a width of 5 μm, and the separation between the channels was 25 μm.

A 60 nm-thick HfAlO gate dielectric layer was deposited by atomic layer deposition (ALD) system (Lucida D100, NCD Technology, Korea) at 150 °C. During deposition, H2O was used as the oxidant, while tetrakis (ethylmethylamino) hafnium and trimethylaluminum served as the precursors for Hf and Al, respectively. The source, drain, and gate electrodes were formed via the thermal evaporation (SCIEN Tech, Korea) of Ti. Figure 1 presents a schematic (Figure 1a) and an optical microscope image (Figure 1b) of the fabricated a-ITGZO TFT.

Figure 1.

(a) Schematic and (b) optical microscope image of the fabricated a-ITGZO TFT.

The thicknesses of the a-ITGZO and HfAlO layers were measured using X-ray reflectometry (D8 Discover Plus, Bruker, MA, USA), and the capacitance of the gate dielectric was measured using an LCR meter (HP4285A, Agilent Technologies, Santa Clara, CA, USA). The I–V characteristics were evaluated using a semiconductor parameter analyzer (HP4155C, Agilent Technologies, Santa Clara, CA, USA), and AC bias stress was applied using an SMU/pulse generator (16440A, Agilent Technologies, Santa Clara, CA, USA). The electrical characteristics were measured under both DC and AC bias stress conditions in ambient air and inside a dark box.

A unipolar AC pulse (0 to 15 V) with a frequency of 500 kHz was applied to the gate electrode. The pulse had a duty ratio of 50% with equal rising and falling times. To examine the effect of the pulse rising–falling time (tr-f) on the electrical characteristics of a-ITGZO TFTs under AC bias stress, we applied AC pulses with tr-f values of 400, 200, and 100 ns. All simulations in this study were conducted using the Silvaco Victory TCAD device simulator (version 1.14.1.R).

3. Results and Discussions

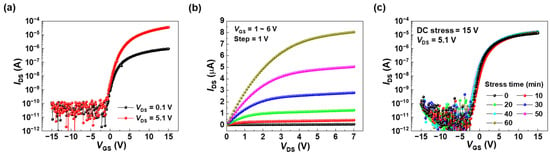

Figure 2 presents the transfer characteristics of the a-ITGZO TFT measured at drain-to-source voltages of 0.1 V and 5.1 V (Figure 2a), and its corresponding output characteristics (Figure 2b). The μFE in the linear region and the subthreshold swing (SS) are calculated using the following equations:

where IDS is the drain-to-source current, Cox (=119 nF/cm2) is the gate dielectric capacitance per unit area, W/L (50/100 μm) is the channel width-to-length ratio, and VTH is the threshold voltage. VTH was determined using the constant current method, using the VGS corresponding to an IDS of W/L × 10 nA at a VDS of 5.1 V. The μFE, SS, and VTH values of the a-ITGZO TFTs were 16.8 ± 3.4 cm2/V∙s, 447 ± 40 mV/decade, and –0.5 ± 0.3 V, respectively. Figure 2c shows the time evolution of the transfer curves for the a-ITGZO TFT under a DC bias stress of 15 V. The time evolution reveals that the on-current, SS, and threshold voltage shift (ΔVTH) are slightly changed even after the DC bias stress for 60 min; the on-current is changed from 13.0 μA to 16.6 μA, the SS from 670 mV/dec to 686 mV/dec, and the VTH from −0.6 V to −0.9 V. Considering that DC bias stress does not significantly change the performance of the a-ITGZO TFTs, this suggests that electron trapping rarely occurs under DC bias conditions.

Figure 2.

(a) Transfer and (b) output characteristics of the a-ITGZO TFT. (c) Time evolution of the transfer curves under a DC bias stress of 15 V.

On the other hand, the AC bias stress significantly affects the VTH of the a-ITGZO TFTs, depending on the tr-f of the AC pulse, as shown in Figure 3, which presents the time evolution of the transfer curves for tr-f values of 400 (Figure 3a), 200 (Figure 3b), and 100 ns (Figure 3c). Nevertheless, the on-current and SS of the a-ITGZO TFTs under AC bias stress showed only slight changes compared to those of the pristine devices. The degradation of the SS is expressed via ΔSS before and after applying AC bias stress. For tr-f values of 400 ns, 200 ns, and 100 ns, the ΔSS values are 28 mV/dec (from 398 mV/dec to 426 mV/dec), 51 mV/dec (from 550 mV/dec to 601 mV/dec), and 62 mV/dec (from 527 mV/dec to 589 mV/dec), respectively, indicating that the SS is significantly degraded as tr-f becomes shorter. Nevertheless, the AC bias stress has a considerable impact on ΔVTH, as shown in Figure 3d, rather than on the degradation of the SS. In addition, the AC bias stress has relatively little impact on the magnitude of the on-current. The on-current changes from 10.4 μA to 12.6 μA for a tr-f value of 400 ns, from 14.3 μA to 10.7 μA for a tr-f value of 200 ns, and from 11.3 μA to 12.5 μA for a tr-f value of 100 ns. On the contrary, the AC bias stress has a major impact on the SS and on-current rather than on ΔVTH when the AC bias has a low level of −20 V and a high level of 20 V [19,20]. In this study, the AC bias has a low level of 0 V and a high level of 15 V, which is close to the real-world situation in which the low level of a clock pulse is 0 V in display circuits. Under AC bias stresses with tr-f values of 400 ns, 200 ns, and 100 ns, the ΔVTH values are 0.97 V (from 0.57 V to 1.54 V), 2.68 V (from −0.44 V to 2.24 V), and 2.83 V (from −0.38 V to 2.45 V), respectively. This indicates that a larger ΔVTH is induced when AC pulses with faster tr-f are applied to the a-ITGZO TFTs. Figure 3d shows the time dependence of ΔVTH under AC bias stress with tr-f values of 100, 200, and 400 ns. Here, the scattered points and solid lines represent the experimental ΔVTH values and those calculated from a stretched exponential model, respectively. Considering the coefficient of determination (R2) that assesses how well a model fits the data, the data are well fitted with a stretched exponential equation; the values of R2 for 100 ns, 200 ns, and 400 ns are 0.98517, 0.99788, and 0.96733, respectively. The experimental ΔVTH values align well with the model, which explains ΔVTH as a result of electron trapping in the bulk states of the gate dielectric or at interface traps between the channel and dielectric layers [21,22].

Figure 3.

Transfer curves of the a-ITGZO TFTs under AC pulse conditions with tr-f of (a) 400 ns, (b) 200 ns, and (c) 100 ns. (d) Time dependence of ΔVTH under AC bias stress. Scattered points and solid lines represent the experimental ΔVTH values and the corresponding values calculated using the stretched exponential model, respectively.

The equation for the stretched exponential model is given as follows:

where VG is an applied gate bias, VTH0 is the initial threshold voltage, τ is the characteristic trapping time of carriers, and β is the stretched exponential exponent (in this study, β is 0.3) [23,24]. Furthermore, τ is expressed as τ = τ0 exp(Eτ/kT), where τ0 is the thermal prefactor for emission over the barrier, and Eτ is the average effective energy barrier that electrons in the channel must overcome to enter the insulator [25]. Thus, the τ value reflects the height of Eτ; a higher Eτ corresponds to a longer time required to overcome the barrier.

In this study, the τ values obtained from the stretched exponential equation are 6.1 × 105, 8.1 × 105, and 2.6 × 107 s for tr-f values of 100, 200, and 400 ns, respectively. The difference in τ values between 400 ns and 200 ns is significantly larger than that between 200 ns and 100 ns, indicating that the nonlinearity in ΔVTH is deeply concerned with the difference in τ values. As the rising time is faster, the Eτ for electron trapping is lower, so that the change in ΔVTH becomes greater. These τ values fall within the range reported in other studies on charge trapping mechanisms under bias stress [9,22,23,24,25]. The shorter trapping time observed at tr-f = 100 ns compared to 400 ns implies that Eτ is lower at faster rising times, resulting in a significantly larger ΔVTH, which agrees with our experimental findings.

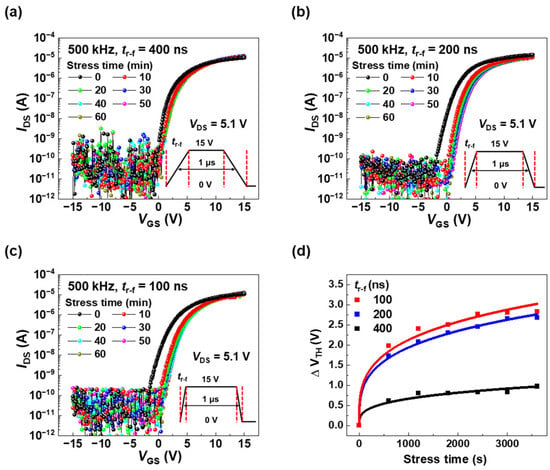

Among the AC bias conditions, the pulse frequency along with the rising time has been known to be one of key parameters in the performance degradation of TFTs [26,27]. Hence, we examined the effect of the pulse frequency on the electrical characteristics of a-ITGZO TFTs at tr-f of 100 ns, which was the rising time resulting in the most pronounced degradation in VTH, as shown in Figure 3. Figure 4 represents the transfer curves under AC stress with frequencies of 250 kHz (Figure 4a) and 125 kHz (Figure 4b), indicating that ΔVTH increases with the pulse frequency; 1.98 V at 125 kHz, 2.12 V at 250 kHz, and 2.83 V at 500 kHz (referred to Figure 3). The change in ΔVTH is deeply concerned with the number of AC pulses applied to the TFT. As the frequency is higher, the number of AC pulses applied to the TFT increases for a certain period. Thus, the gate dielectric and the interface between the channel and dielectric layers experience more frequent voltage transitions, increasing the probability of electron injection into bulk trap states within the gate dielectric or into interface trap states.

Figure 4.

Transfer curves of a-ITGZO TFTs under AC pulse conditions with frequencies of (a) 250 kHz and (b) 125 kHz.

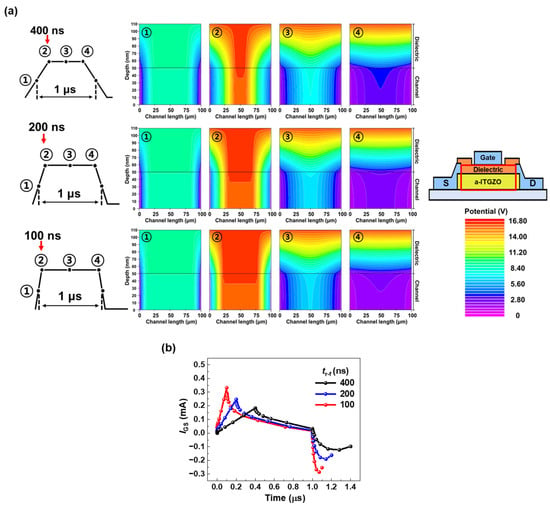

As mentioned above, according to the stretched exponential model, ΔVTH arises from electron trapping in the bulk states of the gate dielectric or at interface traps. However, most previous studies on ΔVTH have focused primarily on electron trapping at interface traps [28,29,30]. Therefore, in this study, to verify that electron trapping in the bulk dielectric is responsible for ΔVTH, we investigated the transient characteristics through the potential distribution across the dielectric and channel layers when applying AC bias stress. Figure 5a presents the potential contours extracted at four specific time points for tr-f values of 400 ns, 200 ns, and 100 ns; the point ① is the midpoint of the low level of the pulse, and the points ②, ③, and ④ are the beginning, midpoint, and end of the high-level duration, respectively. At the point ①, a relatively weak potential is formed across the channel and dielectric layers, and there is no significant difference in the potential distributions for tr-f values of 400 ns, 200 ns, and 100 ns. At point ② where the AC voltage reaches 15 V, a strong potential is formed across the dielectric and channel. When the AC voltage rapidly increases (tr-f is 100 ns), a wide and strong potential forms across the dielectric and channel layers, which is related to the current overshoot phenomenon during the pulse rising edge. This wide and strong potential at fast rising times allows more electrons to be injected into the dielectric. Consequently, a higher gate leakage current (IGS) is observed at a faster tr-f. On the other hand, at the points ③ and ④, the potential in the channel becomes weak regardless of the tr-f. Figure 5b shows the IGS during one cycle of an AC pulse with tr-f values of 400 ns, 200 ns, and 100 ns. Compared to IDS, which is commonly used to evaluate the electrical performance and degradation behavior of TFTs, IGS is an appropriate parameter to find out the cause of VTH degradation using the rising time of the AC bias. The extracted IGS values at the end of the rising edge are 0.18 mA, 0.24 mA, and 0.33 mA, respectively. The magnitude of the current overshoot increases as tr-f decreases. Because the current overshoot can cause significant degradation in electronic device performance [31,32], it is reasonable to attribute the increase in ΔVTH to the faster rising time. Therefore, at fast rising times, the wide and strong potential formed across the dielectric and channel layers leads to an increased ΔVTH.

Figure 5.

(a) Potential contours of the dielectric and channel layers when the AC pulse with tr-f of 400 ns, 200 ns, and 100 ns is applied. (b) Gate leakage current (IGS) over one cycle of AC pulses with tr-f of 400 ns, 200 ns, and 100 ns.

Additionally, this study reveals that IGS is a key parameter to analyze the current overshoot phenomenon occurring when the AC bias stress is applied to the gate electrode.

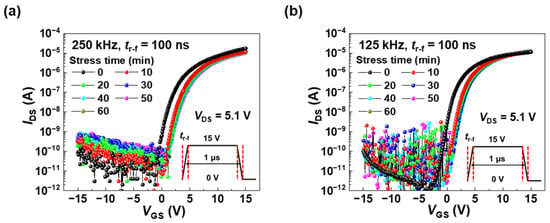

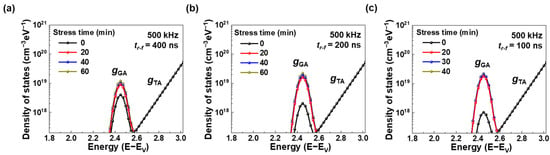

On the other hand, electron trapping at the interface traps was also examined by analyzing the density of states of a-ITGZO TFTs under AC bias stress with tr-f values of 400 ns (Figure 6a), 200 ns (Figure 6b), and 100 ns (Figure 6c), as shown in Figure 6.

Figure 6.

Density of states in the a-ITGZO TFTs under AC bias stress with tr-f of (a) 400 ns, (b) 200 ns, and (c) 100 ns.

The distributions of the sub-gap trap states for oxide semiconductors were calculated as follows:

where gTA(E), gTD(E), gGA(E), and gGD(E) represent the acceptor-like tail states, donor-like tail states, acceptor-like Gaussian states, and donor-like Gaussian states, respectively. The parameters NTD and NTA indicate the effective state densities at the valence band maximum (EV) and conduction band minimum (EC), while WTD and WTA correspond to the characteristic decay slopes of the tail states near the respective band edges. In addition, the parameters NGD and NGA refer to the total concentration of Gaussian-distributed donor-like and acceptor-like states, respectively. Their corresponding peak energies are denoted as EGD and EGA, while WGD and WGA represent the characteristic decay energy. There are no changes in gTD(E), gGD(E), or gTA(E), while gGA(E) increases after AC bias stress. Specifically, the increase in gGA(E) becomes more significant as the pulse tr-f becomes faster. The NGA standing for the interface trap density increases from 4.0 × 1018 cm−3eV−1 to 1.2 × 1019 cm−3eV−1 for tr-f = 400 ns, from 2.0 × 1018 cm−3eV−1 to 2.2 × 1019 cm−3eV−1 for tr-f = 200 ns, and from 1.0 × 1018 cm−3eV−1 to 2.2 × 1019 cm−3eV−1 for tr-f = 100 ns. The interface trap density significantly increases when the AC pulse has a short rise time. According to previous studies [33,34,35], weakly bonded oxygen ions are easily ionized under AC bias stress due to their low formation energy, forming oxygen interstitials that act as gGA(E) states at the interface between the channel and dielectric layers. Hence, an AC pulse with a faster tr-f accelerates the electron trapping of gGA(E) during bias stress, resulting in a larger ΔVTH. This is consistent with the stretched exponential model described above. In this study, it was revealed that AC stress-induced performance degradation in a-ITGZO TFTs is attributed to electron trapping both in the bulk states of the gate dielectric and at the interface traps between the channel and dielectric layers.

4. Conclusions

In this study, we investigated the effect of the pulse rising time on AC stress-induced performance degradation in a-ITGZO TFTs through both experiments and simulations. When AC bias stress was applied with tr-f values of 400 ns, 200 ns, and 100 ns, VTH was positively shifted by 0.97 V, 2.68 V, and 2.83 V, respectively. However, the on-current and SS of the a-ITGZO TFTs under AC bias stress showed little change compared to those of the pristine devices. Accordingly, a stretched exponential model was applied to describe ΔVTH. Based on the potential distribution formed across the dielectric and channel layers as a function of tr-f, it was confirmed that electron trapping in the bulk states of the gate dielectric contributes to the observed ΔVTH. Additionally, the larger ΔVTH under faster tr-f conditions was attributed to the electron trapping of gGA(E) interface states during bias stress. Overall, this study demonstrates that the degradation in ΔVTH of oxide TFTs under AC bias stress results from both electron trapping in the bulk states of the gate dielectric and trapping at the interface traps between the channel and dielectric layers.

Author Contributions

Conceptualization, M.K., K.C. and S.K.; Methodology, M.K., K.C. and S.K.; Validation, M.K. and K.C.; Formal Analysis, M.K.; Investigation, M.K. and K.C.; Writing—Original Draft Preparation, M.K.; Writing—Review and Editing, K.C. and S.K.; Visualization M.K., K.C. and S.K.; Supervision, S.K.; Funding Acquisition, S.K. All authors have read and agreed to the published version of the manuscript.

Funding

This work was partially funded by Samsung Display Co., Ltd., a grant from the National Research Foundation of Korea (NRF) supported by the Ministry of Science and ICT (MSIT) (RS-2023-00260876), and the Brain Korea 21 Plus Project.

Data Availability Statement

Data is contained within the article.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef] [PubMed]

- Dargar, S.K.; Srivastava, V.M. Design and analysis of IGZO thin film transistor for AMOLED pixel circuit using double-gate tri active layer channel. Heliyon 2019, 5, e01452. [Google Scholar] [CrossRef]

- Fan, C.-L.; Lin, W.-Y.; Chen, C.-Y. New low-frame-rate compensating pixel circuit based on low-temperature poly-Si and oxide TFTs for high-pixel-density portable AMOLED displays. Micromachines 2021, 12, 1514. [Google Scholar] [CrossRef]

- Yan, A.; Wang, C.; Yan, J.; Wang, Z.; Zhang, E.; Dong, Y.; Yan, Z.Y.; Lu, T.; Cui, T.; Li, D. Thin-Film Transistors for Integrated Circuits: Fundamentals and Recent Progress. Adv. Funct. Mater. 2024, 34, 2304409. [Google Scholar] [CrossRef]

- An, J.; Liao, C.; Zhu, Y.; Zheng, X.; Dai, C.; Zhang, X.; Zhang, S. Gate driver on array with multiple outputs and variable pulse widths for low-temperature polysilicon and oxide (LTPO) TFTs driven AMOLED displays. IEEE Trans. Circuits Syst. II Express Briefs 2022, 70, 934–938. [Google Scholar] [CrossRef]

- Kim, J.; Chen, Y.; Lee, S.; Jang, J. A novel gate driver working under depletion mode oxide TFTs using low-temperature poly-Si oxide TFTs. IEEE Electron. Device Lett. 2021, 42, 1619–1622. [Google Scholar] [CrossRef]

- Yu, E.K.-H.; Abe, K.; Kumomi, H.; Kanicki, J. AC bias-temperature stability of a-InGaZnO thin-film transistors with metal source/drain recessed electrodes. IEEE Trans. Electron. Devices 2014, 61, 806–812. [Google Scholar] [CrossRef]

- Priyadarshi, S.; Billah, M.M.; Lim, T.; Urmi, S.S.; Jang, J. Reduced dynamic gate pulse stress instability in dual gate a-InGaZnO thin film transistors. IEEE Electron. Device Lett. 2023, 44, 428–431. [Google Scholar] [CrossRef]

- Lee, S.; Jeon, K.; Park, J.-H.; Kim, S.; Kong, D.; Kim, D.M.; Kim, D.H.; Kim, S.; Kim, S.; Hur, J. Electrical stress-induced instability of amorphous indium-gallium-zinc oxide thin-film transistors under bipolar ac stress. Appl. Phys. Lett. 2009, 95, 132101. [Google Scholar] [CrossRef]

- Kim, H.; Kim, B.J.; Oh, J.; Choi, S.-Y.; Park, H. Bi-directional threshold voltage shift of amorphous InGaZnO thin film transistors under alternating bias stress. Semicond. Sci. Technol. 2024, 39, 025011. [Google Scholar] [CrossRef]

- Kim, S.-J.; Lee, S.-Y.; Lee, Y.W.; Kuk, S.-H.; Kwon, J.-Y.; Han, M.-K. Effect of charge trapping/detrapping on threshold voltage shift of IGZO TFTs under AC bias stress. Electrochem. Solid-State Lett. 2012, 15, H108. [Google Scholar] [CrossRef]

- Kim, E.; Kim, C.-K.; Lee, M.K.; Bang, T.; Choi, Y.-K.; Park, S.-H.K.; Choi, K.C. Influence of the charge trap density distribution in a gate insulator on the positive-bias stress instability of amorphous indium-gallium-zinc oxide thin-film transistors. Appl. Phys. Lett. 2016, 108, 182104. [Google Scholar] [CrossRef]

- Zhu, G.; Chen, Z.; Zhang, M.; Lu, L.; Deng, S.; Wong, M.; Kwok, H.-S. Reliability of indium-tin-zinc-oxide thin-film transistors under dynamic drain voltage stress. Appl. Phys. Lett. 2024, 125, 023505. [Google Scholar] [CrossRef]

- Park, S.; Ho, D.; Park, H.-B.; Park, S.K.; Kim, C. Bilayer channel structure to improve the stability of solution-processed metal oxide transistors under AC stress. Mater. Sci. Semicond. Process. 2024, 171, 108000. [Google Scholar] [CrossRef]

- Kim, J.; Kim, S.; Kim, H.; Kim, S.; Ho, D.; Kim, C. Enhancing AC stress stability in amorphous indium gallium zinc oxide thin-film transistors via controlled hydrogen diffusion. J. Mater. Chem. C 2025, 13, 3587. [Google Scholar] [CrossRef]

- Chen, Y.; Kim, H.; Lee, J.; Lee, S.; Do, Y.; Choi, M.; Jang, J. An 18.6-μm-pitch gate driver using a-IGZO TFTs for ultrahigh-definition AR/VR displays. IEEE Trans. Electron. Devices 2020, 67, 4929–4933. [Google Scholar] [CrossRef]

- Oh, H.; Cho, K.; Park, S.; Kim, S. Electrical characteristics of bendable a-IGZO thin-film transistors with split channels and top-gate structure. Microelectron. Eng. 2016, 159, 179–183. [Google Scholar] [CrossRef]

- Fujii, M.; Ishikawa, Y.; Horita, M.; Uraoka, Y. Unique phenomenon in degradation of amorphous In2O3–Ga2O3–ZnO thin-film transistors under dynamic stress. Appl. Phys. Express 2011, 4, 104103. [Google Scholar] [CrossRef]

- Takahashi, T.; Fujii, M.N.; Miyanaga, R.; Miyanaga, M.; Ishikawa, Y.; Uraoka, Y. Unique degradation under AC stress in high-mobility amorphous In–W–Zn–O thin-film transistors. Appl. Phys. Express 2020, 13, 054003. [Google Scholar] [CrossRef]

- Li, H.; Cai, L.; Xu, G.; Long, S. Positive-bias stress stability of solution-processed oxide semiconductor thin-film transistor. IEEE Trans. Electron. Devices 2022, 69, 3727–3731. [Google Scholar] [CrossRef]

- Park, S.; Cho, E.N.; Yun, I. Effects of alternating pulse bias stress on amorphous InGaZnO thin film transistors. ECS Trans. 2012, 45, 111. [Google Scholar] [CrossRef]

- Mativenga, M.; Choi, J.W.; Hur, J.H.; Kim, H.J.; Jang, J. Highly stable amorphous indium–gallium–zinc-oxide thin-film transistor using an etch-stopper and a via-hole structure. J. Inf. Disp. 2011, 12, 47–50. [Google Scholar] [CrossRef][Green Version]

- Park, S.; Cho, E.N.; Yun, I. Threshold voltage shift prediction for gate bias stress on amorphous InGaZnO thin film transistors. Microelectron. Reliab. 2012, 52, 2215–2219. [Google Scholar] [CrossRef]

- Lee, J.-M.; Cho, I.-T.; Lee, J.-H.; Kwon, H.-I. Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors. Appl. Phys. Lett. 2008, 93, 093504. [Google Scholar] [CrossRef]

- Cho, I.-T.; Lee, J.-M.; Lee, J.-H.; Kwon, H.-I. Charge trapping and detrapping characteristics in amorphous InGaZnO TFTs under static and dynamic stresses. Semicond. Sci. Technol. 2008, 24, 015013. [Google Scholar] [CrossRef]

- Wang, H.; Wang, M.; Shan, Q. Dynamic degradation of a-InGaZnO thin-film transistors under pulsed gate voltage stress. Appl. Phys. Lett. 2015, 106, 133506. [Google Scholar] [CrossRef]

- Zhou, X.; Shao, Y.; Zhang, L.; Lu, H.; He, H.; Han, D.; Wang, Y.; Zhang, S. Oxygen interstitial creation in a-IGZO thin-film transistors under positive gate-bias stress. IEEE Electron. Device Lett. 2017, 38, 1252–1255. [Google Scholar] [CrossRef]

- Dao, V.A.; Trinh, T.T.; Jang, K.; Ryu, K.; Yi, J. Trapping time characteristics of carriers in a-InGaZnO thin-film transistors fabricated at low temperatures for next-generation displays. J. Electron. Mater. 2013, 42, 711–715. [Google Scholar] [CrossRef]

- Fan, W.-T.; Liu, P.-T.; Kuo, P.-Y.; Chang, C.-M.; Liu, I.H.; Kuo, Y. Numerical analysis of oxygen-related defects in amorphous In-WO nanosheet thin-film transistor. Nanomaterials 2021, 11, 3070. [Google Scholar] [CrossRef]

- Song, J.; Lee, D.; Woo, J.; Koo, Y.; Cha, E.; Lee, S.; Park, J.; Moon, K.; Misha, S.H.; Prakash, A. Effects of RESET current overshoot and resistance state on reliability of RRAM. IEEE Electron. Device Lett. 2014, 35, 636–638. [Google Scholar]

- Lee, S.; Song, J.; Lee, D.; Woo, J.; Cha, E.; Hwang, H. Effect of AC pulse overshoot on nonlinearity and reliability of selectorless resistive random access memory in AC pulse operation. Solid-State Electron. 2015, 104, 70–74. [Google Scholar] [CrossRef]

- Zhu, Z.; Cao, W.; Huang, X.; Shi, Z.; Zhou, D.; Xu, W. Analysis of nitrogen-doping effect on sub-gap density of states in a-IGZO TFTs by TCAD simulation. Micromachines 2022, 13, 617. [Google Scholar] [CrossRef]

- Janotti, A.; Van de Walle, C.G. Native point defects in ZnO. Phys. Rev. B—Condens. Matter Mater. Phys. 2007, 76, 165202. [Google Scholar] [CrossRef]

- Chowdhury, M.D.H.; Migliorato, P.; Jang, J. Time-temperature dependence of positive gate bias stress and recovery in amorphous indium-gallium-zinc-oxide thin-film-transistors. Appl. Phys. Lett. 2011, 98, 153511. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).