Effects of Charge Trapping on Memory Characteristics for HfO2-Based Ferroelectric Field Effect Transistors

Abstract

:1. Introduction

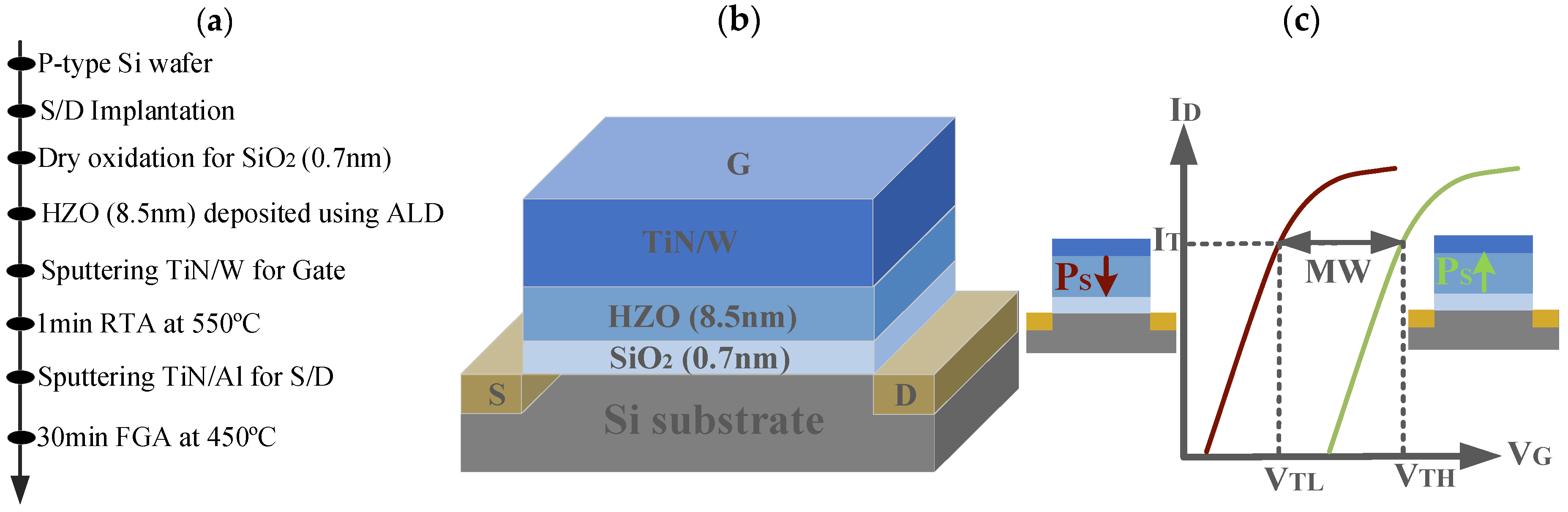

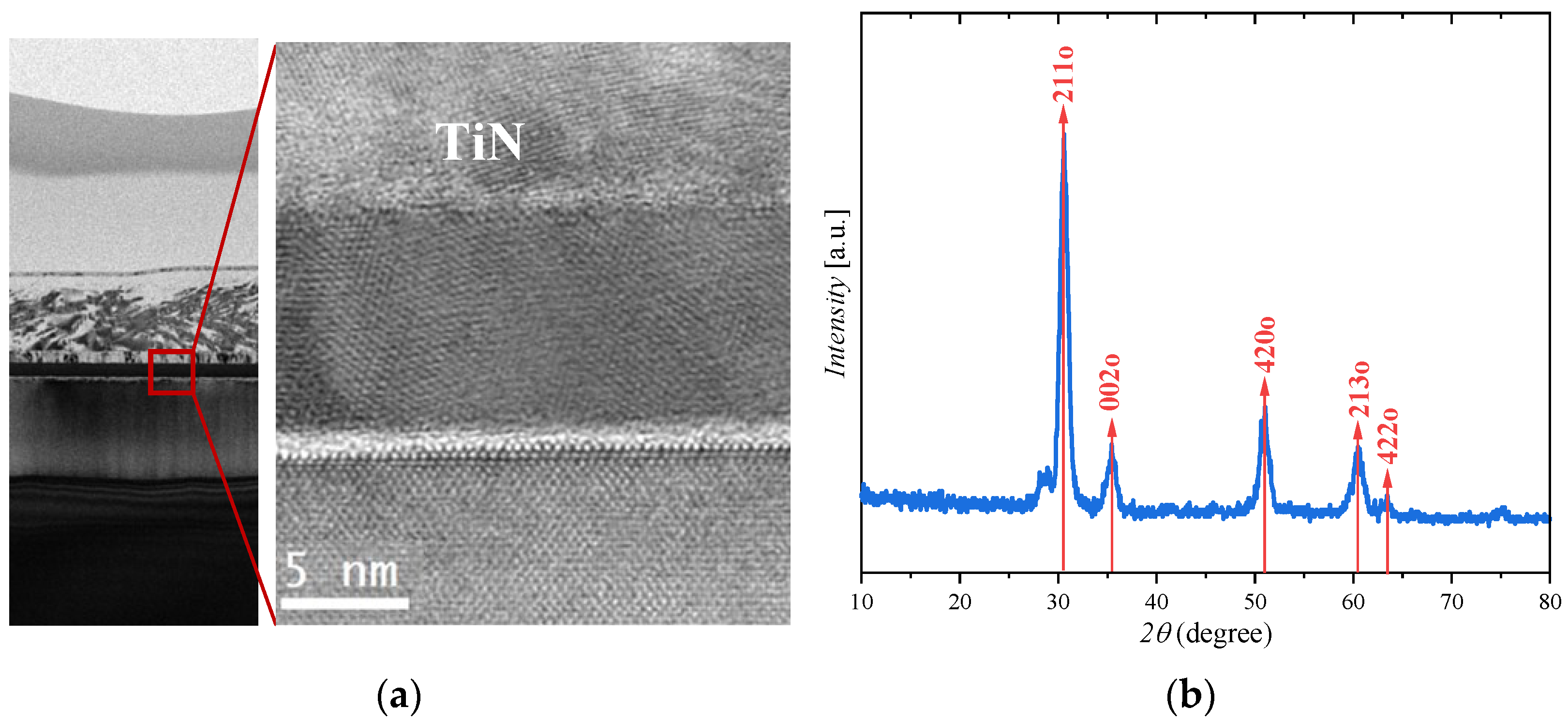

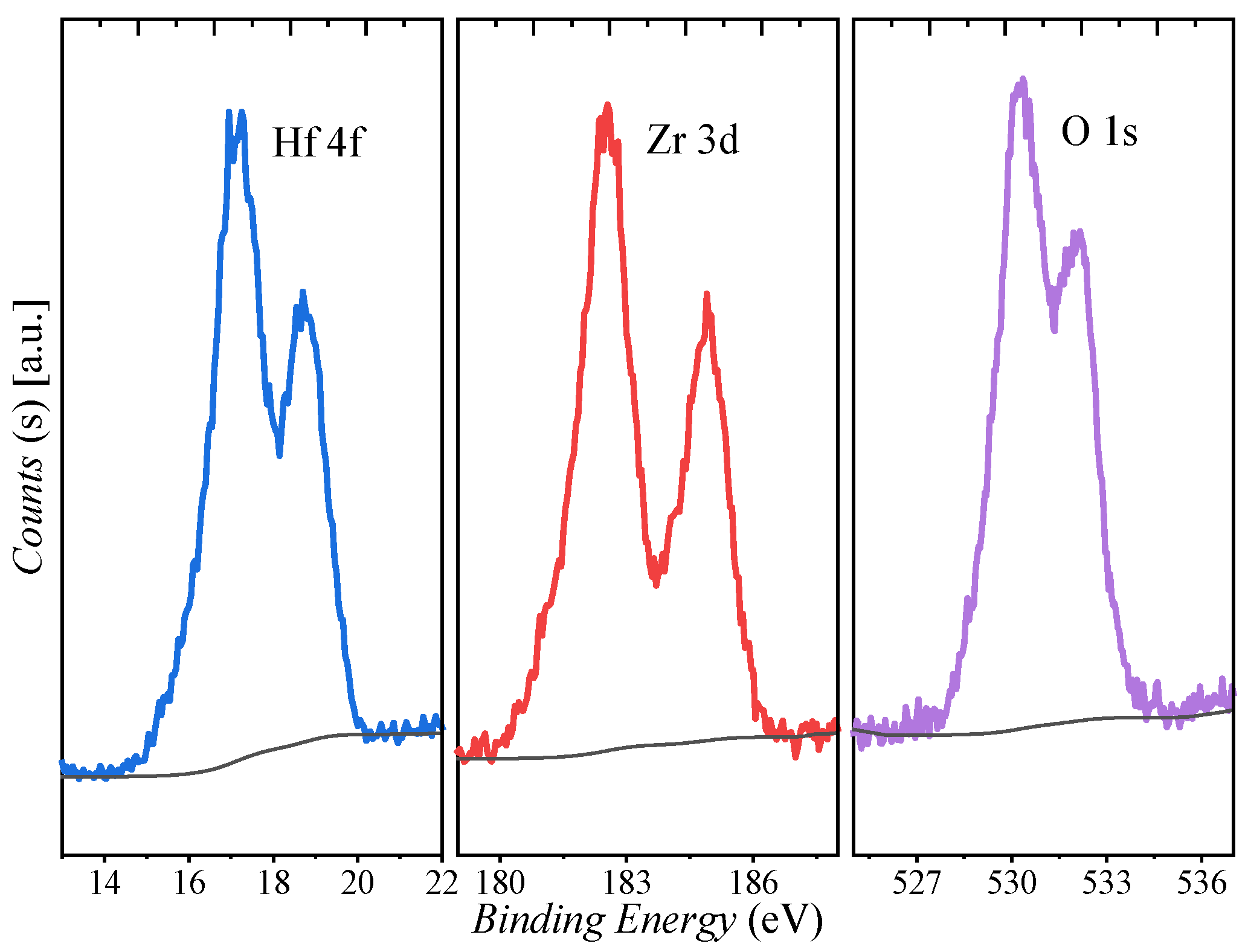

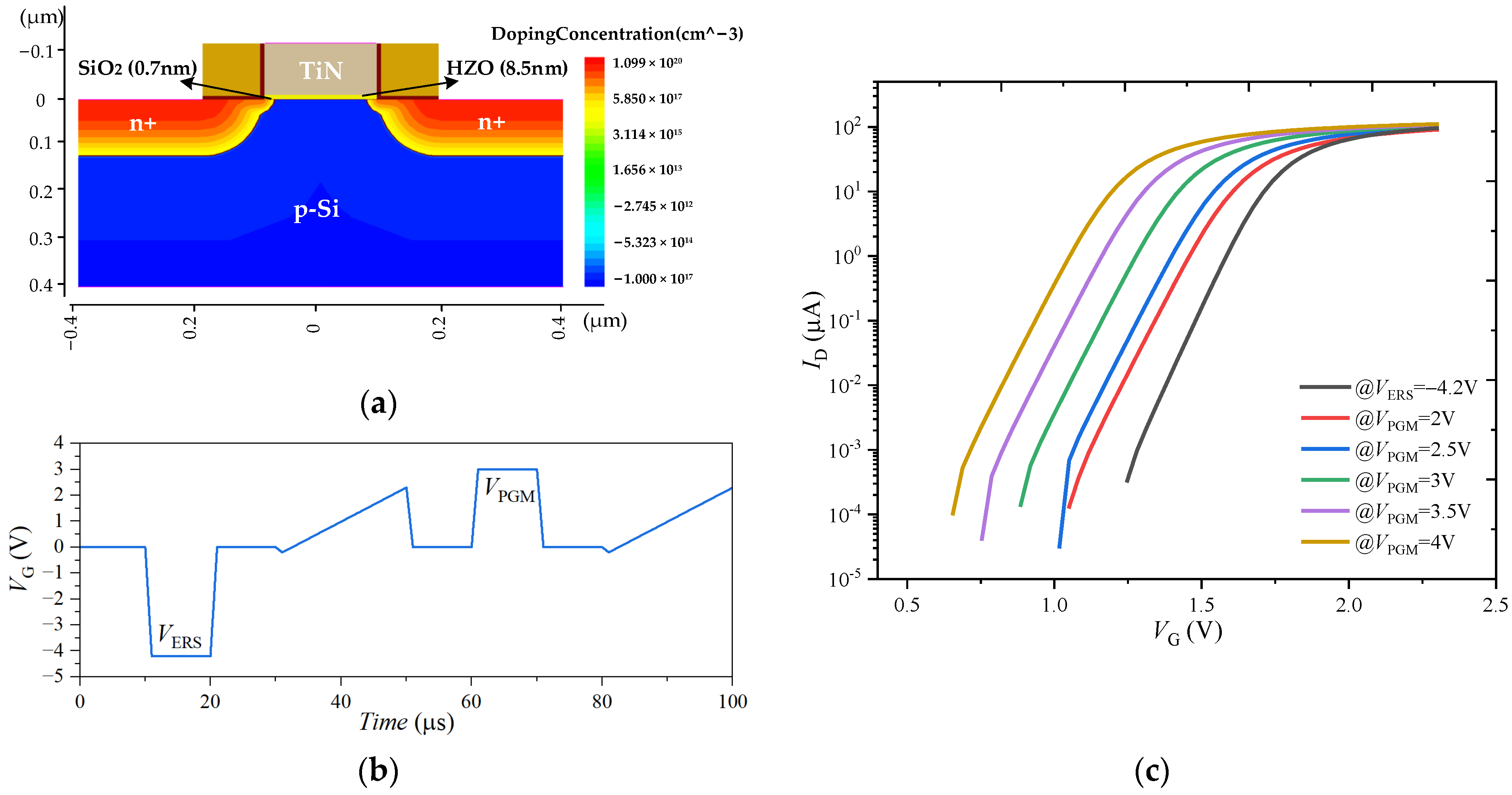

2. Devices and Methods

3. Experimental Results

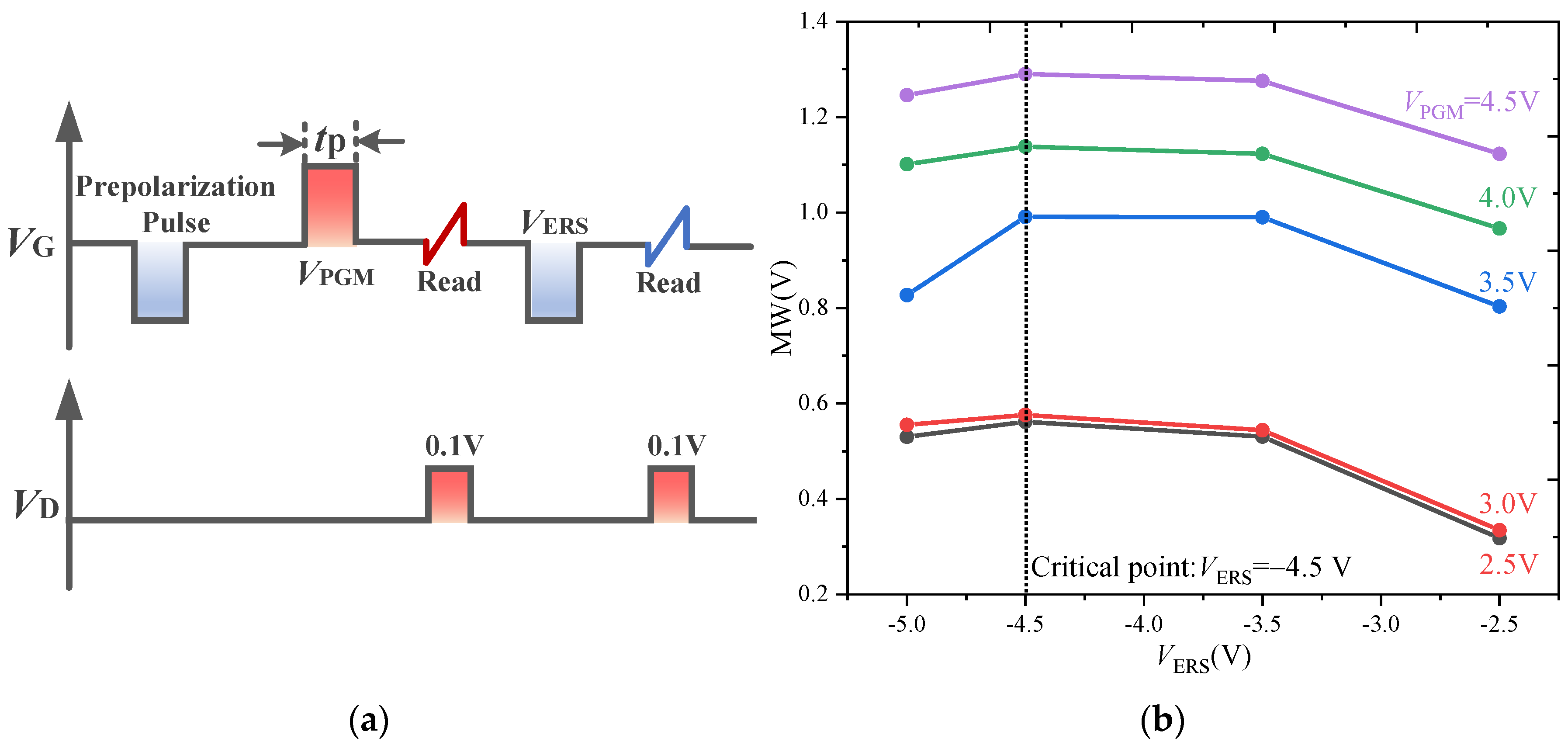

3.1. Memory Window

3.1.1. Memory Window under Various PGM and ERS Pulse Amplitudes

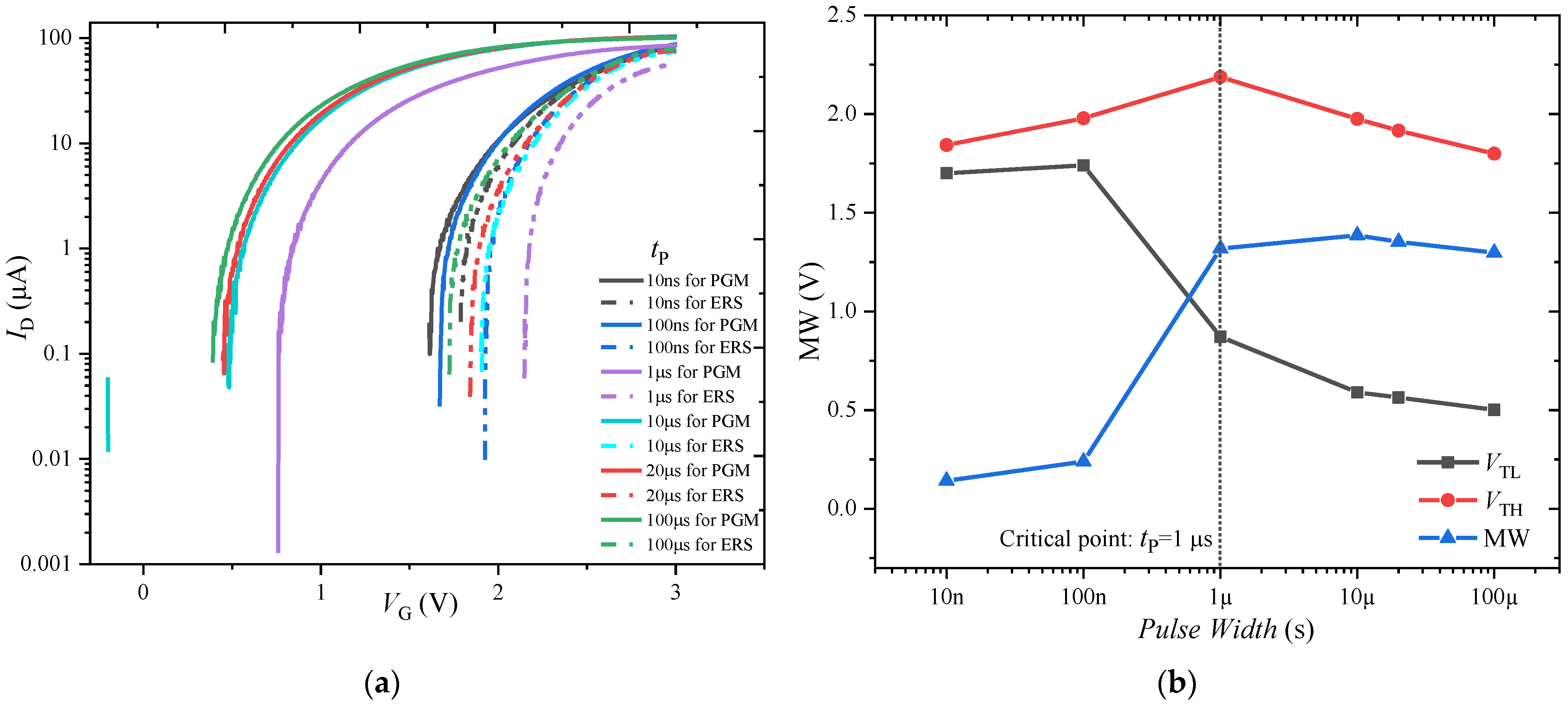

3.1.2. Memory Window under Various PGM and ERS Pulse Widths

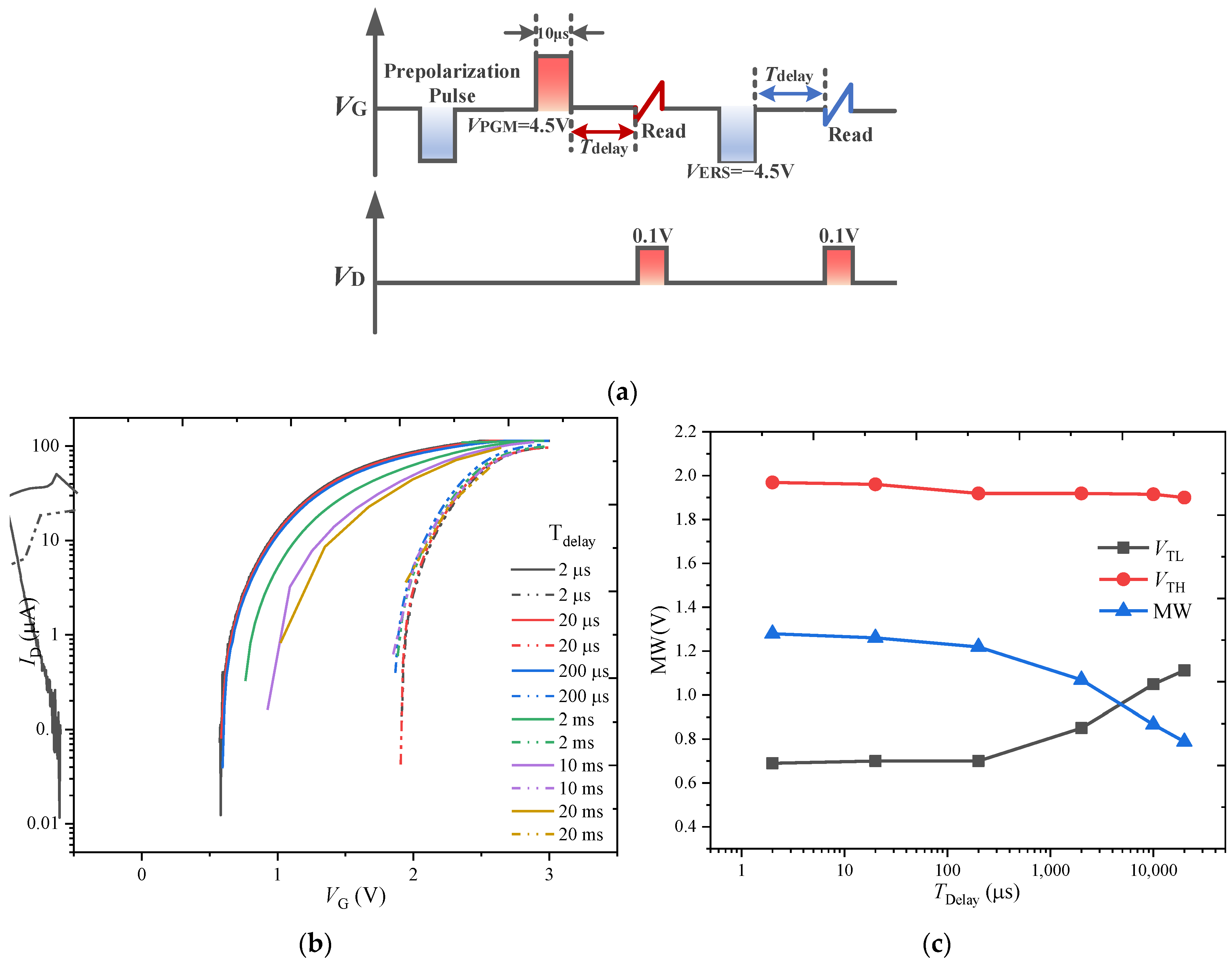

3.1.3. Memory Window under Various Read Delay Times

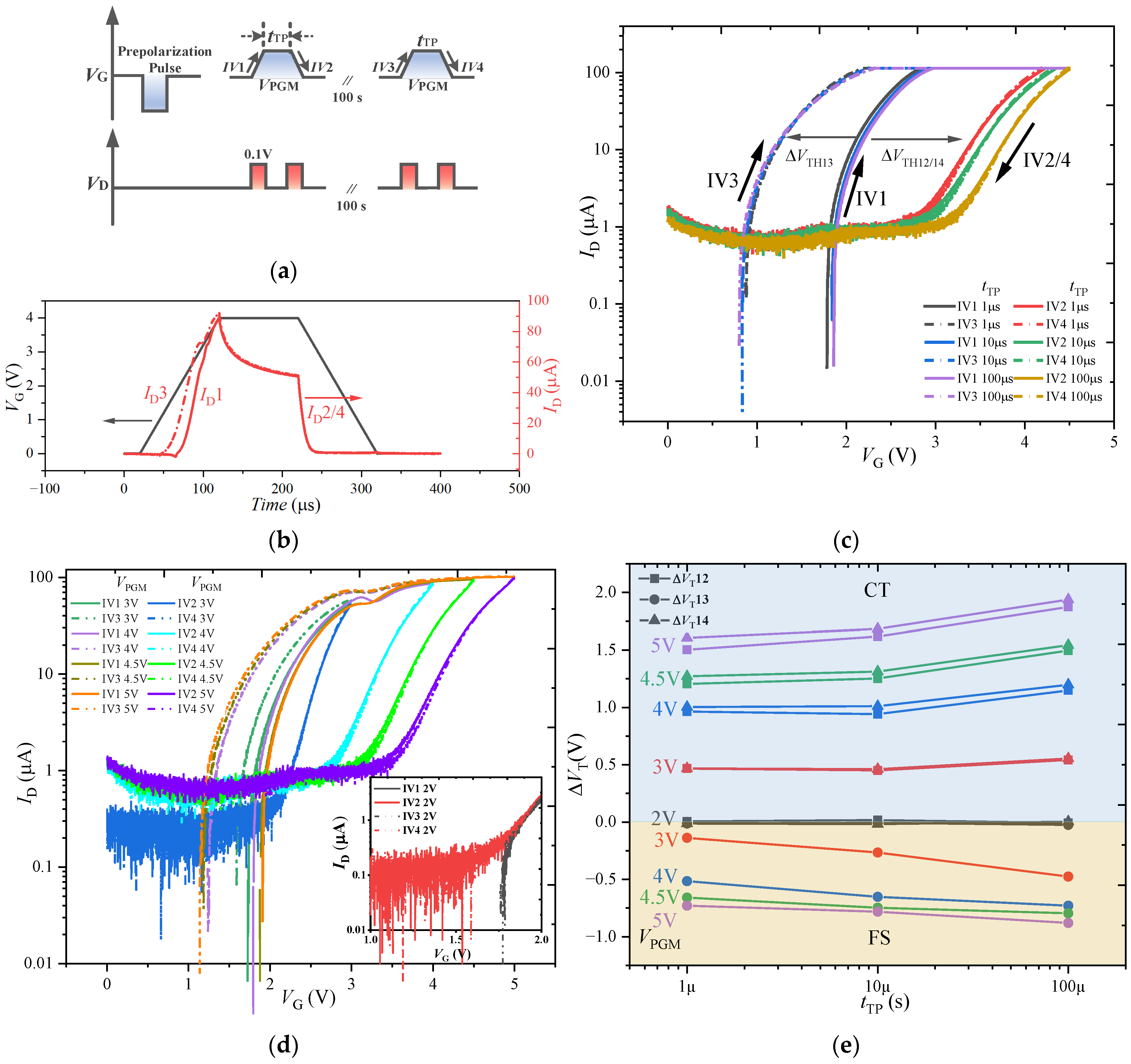

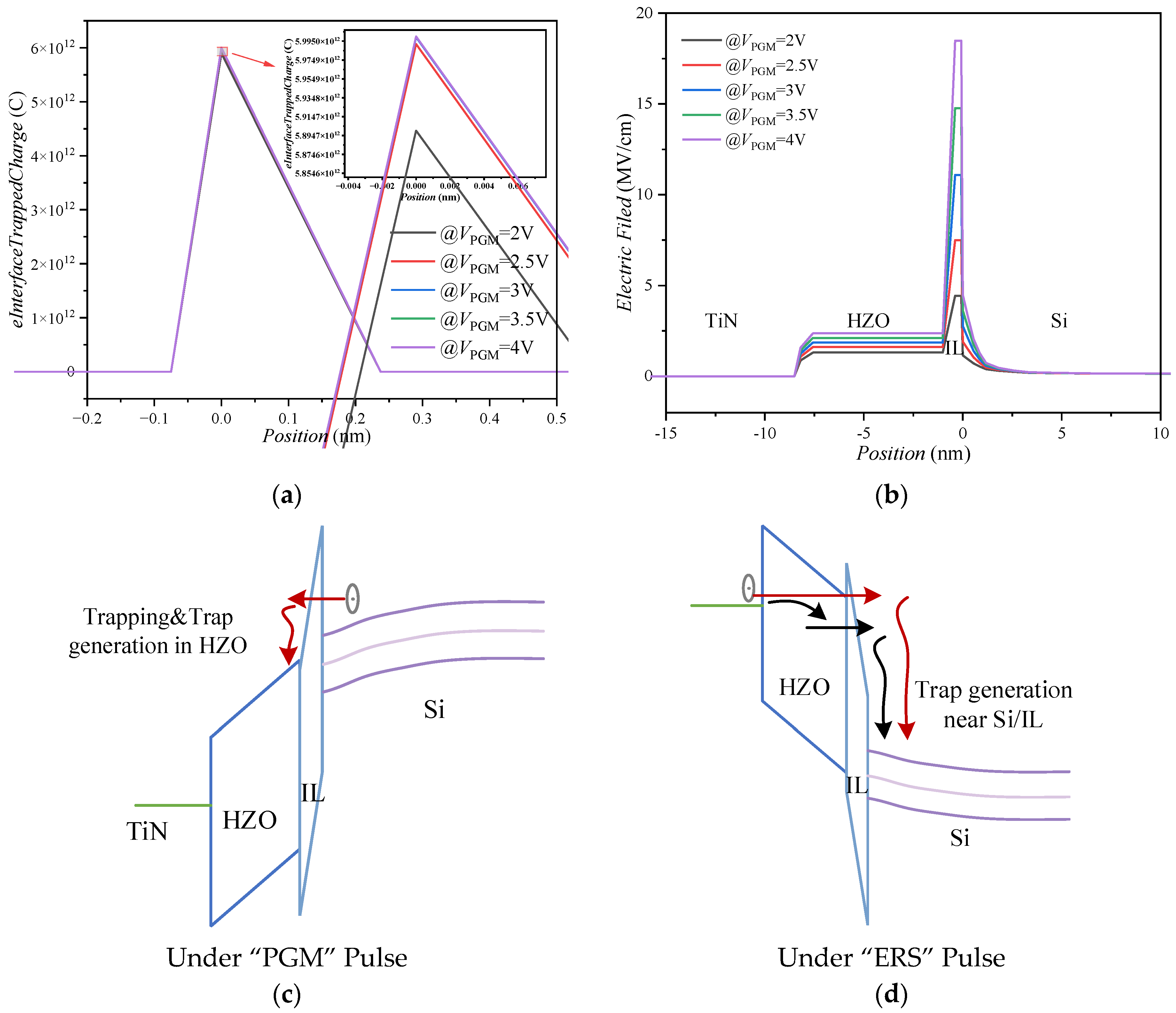

3.2. Charge Trapping and Ferroelectric Switching Effect

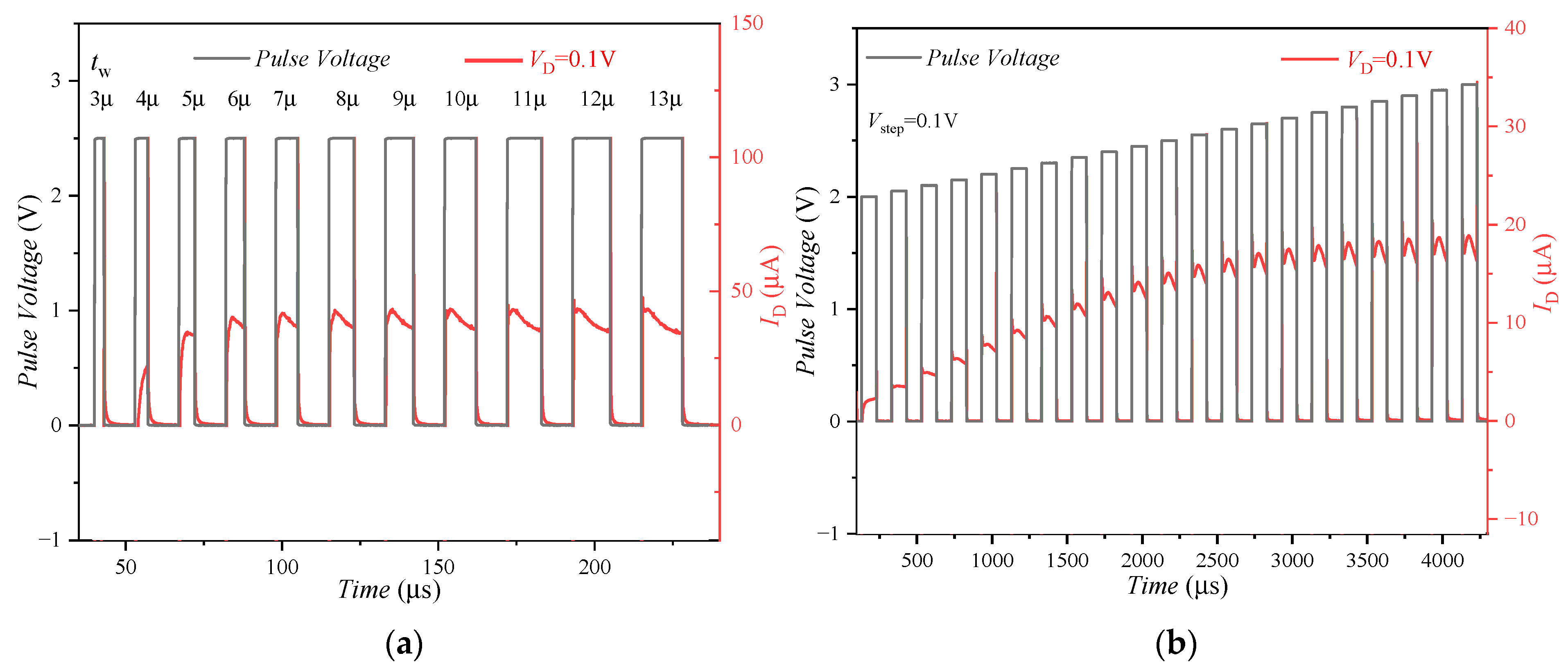

3.3. Conductance Modulation Characteristic Influenced by Charge Trapping Effect

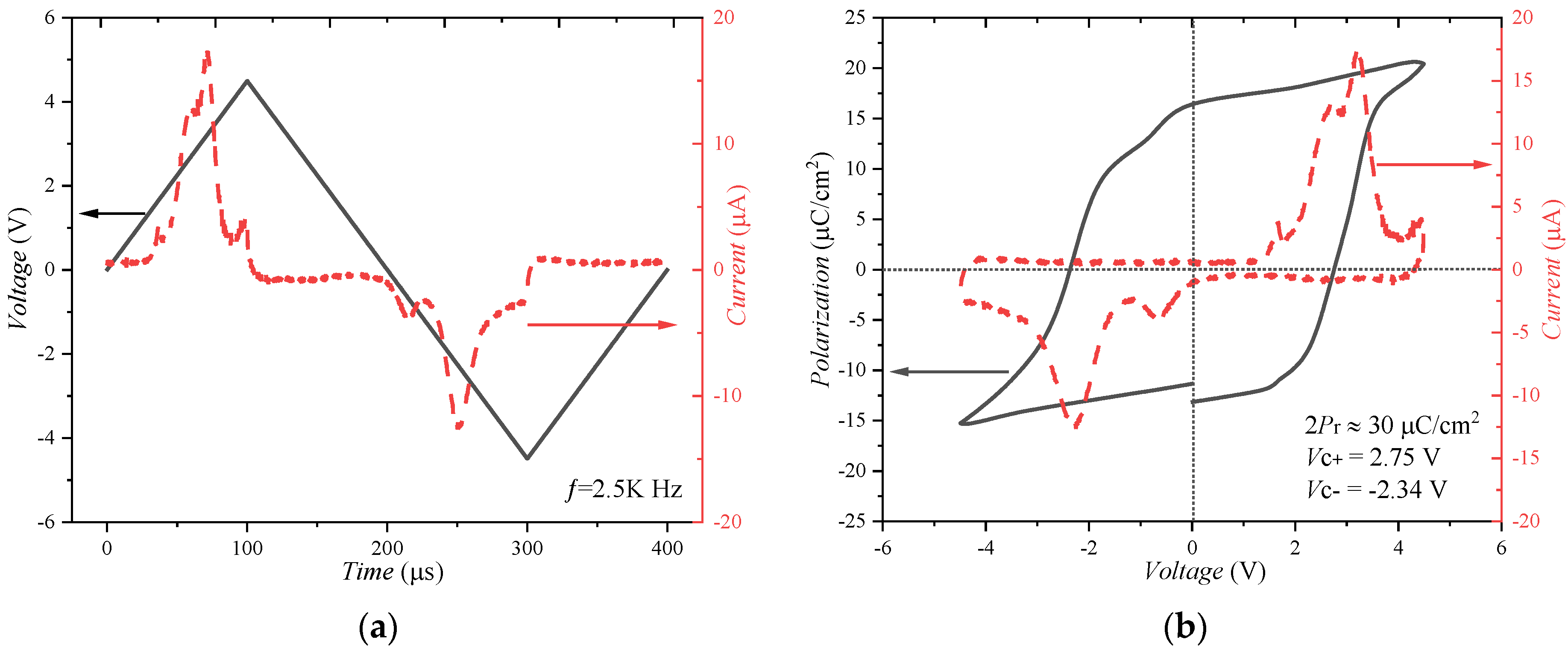

3.4. P-V Characteristics

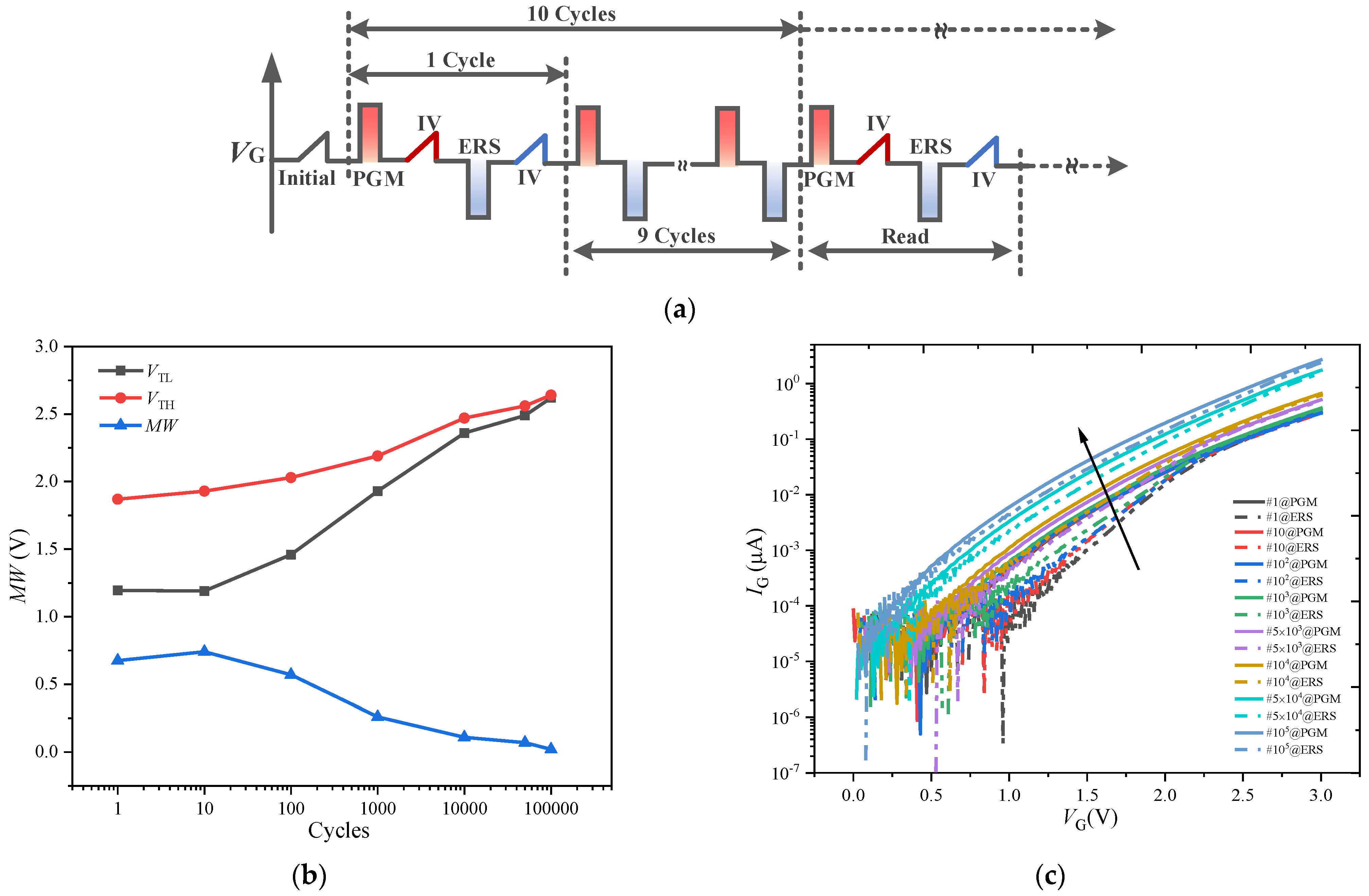

3.5. Endurance

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Boscke, T.; Muller, J.; Brauhaus, D.; Schroder, U.; Bottger, U. Ferroelectricity in Hafnium Oxide Thin Films. Appl. Phys. Lett. 2011, 99, 102903. [Google Scholar] [CrossRef]

- Wang, J.; Bi, J.; Liu, G.; Bai, H.; Xi, K.; Ji, L.; Li, B.; Majumdar, S. Simulations of Single Event Effects in 6T2C-based Ferroelectric Non-volatile SRAM. Semicond. Sci. Technol. 2020, 36, 015015. [Google Scholar] [CrossRef]

- Zhao, B.; Yan, Y.; Bi, J.; Xu, G.; Xu, Y.; Yang, X.; Fan, L.; Liu, M. Improved Ferroelectric Properties in Hf0.5Zr0.5O2 Thin Films by Microwave Annealing. Nanomaterials 2022, 12, 3001. [Google Scholar] [CrossRef]

- Van, J. 3D Memories and Ferroelectrics. In Proceedings of the 2017 IEEE International Memory Workshop (IMW), Monterey, CA, USA, 14–17 May 2017; pp. 1–3. [Google Scholar]

- Dunkel, S.; Trentzsch, M.; Richter, R.; Moll, P.; Fuchs, C.; Gehring, O.; Majer, M.; Wittek, S.; Müller, B.; Melde, T.; et al. A FeFET based Super-Low-Power Ultra-Fast Embedded NVM Technology for 22 nm FDSOI and Beyond. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 19.7.1–19.7.4. [Google Scholar]

- Florent, K.; Lavizzari, S.; Di Piazza, L.; Popovici, M.; Vecchio, E.; Potoms, G.; Groeseneken, G.; Van Houdt, J. First Demonstration of Vertically Stacked Ferroelectric Al Doped HfO2 Devices for NAND Applications. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Yang, X.; Xu, Y.; Bi, J.; Fan, L.; Ji, L.; Xu, G. Total Ionizing Dose Effects on Aluminum Oxide/Zirconium-Doped Hafnium Oxide Stack Ferroelectric Tunneling Junctions. Sci. China Inf. Sci. 2021, 64, 279–280. [Google Scholar] [CrossRef]

- Yang, X.; Bi, J.; Xu, Y.; Xi, K.; Ji, L. The Effects of Proton Radiation on Aluminum Oxide/Zirconium-Doped Hafnium Oxide Stacked Ferroelectric Tunneling Junctions. Appl. Phys. Express 2021, 14, 061001. [Google Scholar] [CrossRef]

- Yan, G.; Xu, G.; Bi, J.; Tian, G.; Xu, Q.; Yin, H.; Li, Y. Accumulative Total Ionizing Dose (TID) and Transient Dose Rate (TDR) Effects on Planar and Vertical Ferroelectric Tunneling-Field-Effect-Transistors (TFET). Microelectron. Reliab. 2020, 114, 113855. [Google Scholar] [CrossRef]

- Tian, G.; Bi, J.; Xu, G.; Xi, K.; Yang, X.; Yin, H.; Wang, W. Heavy Ion Induced Single-Event-Transient Effects in Nano-Scale Ferroelectricity Vertical Tunneling Transistors by TCAD Simulation. Semicond. Sci. Technol. 2020, 35, 105010. [Google Scholar] [CrossRef]

- Choe, G.; Yu, S. Variability Study of Ferroelectric Field-Effect Transistors Towards 7nm Technology Node. IEEE J. Electron. Dev. 2021, 9, 1131–1136. [Google Scholar] [CrossRef]

- Xiao, W.; Liu, C.; Peng, Y.; Zheng, S.; Feng, Q.; Zhang, C.; Zhang, J.; Hao, Y.; Liao, M.; Zhou, Y. Performance Improvement of Hf0.5Zr0.5O2 based Ferroelectric-Field-Effect Transistors with ZrO2 Seed Layers. IEEE Electron Device Lett. 2019, 40, 714–717. [Google Scholar] [CrossRef]

- Tian, G.; Bi, J.; Xu, G.; Xi, K.; Yang, X.; Majumdar, S.; Yin, H.; Xu, Q.; Wang, W. Single-Event-Transient Effects in Silicon-on-Insulator Ferroelectric Double-Gate Vertical Tunneling field Effect Transistors. Sci. China Inf. Sci. 2020, 63, 229403. [Google Scholar] [CrossRef]

- Breyer, E.; Mulaosmanovic, H.; Mikolajick, T.; Slesazeck, S. Reconfigurable NAND/NOR Logic Gates in 28 nm HKMG and 22 nm FD-SOI FeFET Technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 28.5.1–28.5.4. [Google Scholar]

- Deng, S.; Jiang, Z.; Dutta, S.; Ye, H.; Chakraborty, W.; Santosh, K.; Datta, S.; Ni, K. Examination of the Interplay between Polarization Switching and Charge Trapping in Ferroelectric FET. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 4.4.1–4.4.4. [Google Scholar]

- Deng, S.; Zhao, Z.; Sung, Y.; Duenkel, S.; MacMahon, D.; Tiwari, R.; Choudhury, N.; Beyer, S.; Gong, X.; Kurinec, S.; et al. Unraveling the Dynamics of Charge Trapping and De-Trapping in Ferroelectric FETs. IEEE Trans. Electron Devices 2022, 69, 1503–1511. [Google Scholar] [CrossRef]

- Toprasertpong, K.; Lin, Z.; Lee, T.; Takenaka, M.; Takagi, S. Asymmetric Polarization Response of Electrons and Holes in Si FeFETs Demonstration of Absolute Polarization Hysteresis Loop and Inversion Hole Density over 2 × 1013 cm2. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar]

- Izmailov, R.; Strand, J.; Larcher, L.; O’Sullivan, B.; Shluger, A.; Afanas’ev, V. Electron Trapping in Ferroelectric HfO2. Phys. Rev. Mater. 2021, 5, 034415. [Google Scholar] [CrossRef]

- Ali, T.; Polakowski, P.; Riedel, S.; Büttner, T.; Kämpfe, T.; Rudolph, M.; Pätzold, B.; Seidel, K.; Löhr, D.; Hoffmann, R.; et al. High Endurance Ferroelectric Hafnium Oxide-based FeFET Memory without Retention Penalty. IEEE Trans. Electron Devices 2018, 65, 3769–3774. [Google Scholar] [CrossRef]

- Hoffmann, M.; Tan, A.; Shanker, N.; Liao, Y.; Wang, L.; Bae, J.; Hu, C.; Salahuddin, S. Fast Read-After-Write and Depolarization Fields in High Endurance n-Type Ferroelectric FETs. IEEE Electron Device Lett. 2022, 43, 1–4. [Google Scholar] [CrossRef]

- Yurchuk, E.; Müller, J.; Müller, S.; Paul, J.; Peši’c, M.; Bentum, R.; Schroeder, U.; Mikolajick, T. Charge-Trapping Phenomena in HfO2-Based FeFET-Type Nonvolatile Memories. IEEE Trans. Electron Device 2016, 63, 3501–3507. [Google Scholar] [CrossRef]

- Gong, N.; Ma, T. A Study of Endurance Issues in HfO2-Based Ferroelectric Field Effect Transistors: Charge Trapping and Trap Generation. IEEE Electron Device Lett. 2018, 39, 15–18. [Google Scholar] [CrossRef]

- Higashi, Y.; Ronchi, N.; Kaczer, B.; Banerjee, K.; McMitchell, S.; O’Sullivan, B.; Clima, S.; Minj, A.; Celano, U.; Piazza, L.; et al. Impact of Charge Trapping on Imprint and its Recovery in HfO2 based FeFET. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 15.6.1–15.6.4. [Google Scholar]

- Zeng, B.; Xiao, W.; Liao, J.; Liu, H.; Liao, M.; Peng, Q.; Zheng, S.; Zhou, Y. Compatibility of HfN Metal Gate Electrodes with Hf0.5Zr0.5O2 Ferroelectric Thin Films for Ferroelectric Field-Effect Transistors. IEEE Electron Device Lett. 2018, 39, 1508–1511. [Google Scholar] [CrossRef]

- Mulaosmanovic, H.; Dunkel, S.; Muller, J.; Trentzsch, m.; Beyer, S.; Breyer, E.; Mikolajick, T.; Slesazeck, S. Impact of Read Operation on the Performance of HfO2-based Ferroelectric FETs. IEEE Electron Device Lett. 2020, 41, 1420–1423. [Google Scholar] [CrossRef]

- Sharath, S.; Bertaud, T.; Kurian, J.; Hildebrandt, E.; Walczyk, C.; Calka, P.; Zaumseil, P.; Sowinska, M.; Walczyk, D.; Gloskovskii, A.; et al. Towards Forming-free Resistive Switching in Oxygen Engineered HfO2−x. Appl. Phys. Lett. 2014, 104, 063502. [Google Scholar] [CrossRef]

- Hachemi, M.; Salem, B.; Consonni, V.; Roussel, H.; Garraud, A.; Lefevre1, G.; Labau, S.; Basrour, S.; Bsiesy, A. Study of Structural and Electrical Properties of Ferroelectric HZO Films Obtained by Single-Target Sputtering. AIP Adv. 2021, 11, 085004. [Google Scholar] [CrossRef]

- Tasneem, N.; Islam, M.; Wang, Z.; Zhao, Z.; Upadhyay, N.; Lombardo, S.; Chen, H.; Hur, J.; Triyoso, D.; Consiglio, S.; et al. Efficiency of Ferroelectric Field-Effect Transistors: An Experimental Study. IEEE Trans. Electron Device 2022, 69, 1568–1574. [Google Scholar] [CrossRef]

- Toprasertpong, K.; Tahara, K.; Fukui, T.; Lin, Z.; Watanabe, K.; Takenaka, M.; Takagi, S. Improved Ferroelectric/Semiconductor Interface Properties in Hf0.5Zr0.5O2 Ferroelectric FETs by Low-Temperature Annealing. IEEE Electron Device Lett. 2020, 41, 1588–1591. [Google Scholar] [CrossRef]

- Jerry, M.; Chen, P.; Zhang, J.; Sharma, P.; Ni, K.; Yu, S.; Datta, S. Ferroelectric FET Analog Synapse for Acceleration of Deep Neural Network Training. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 6.2.1–6.2.4. [Google Scholar]

- Liu, H.; Li, J.; Wang, G.; Chen, J.; Yu, X.; Liu, Y.; Jin, C.; Wang, S.; Hao, Y.; Han, G. Analog Synapses based on Nonvolatile FETs with Amorphous ZrO2 Dielectric for Spiking Neural Network Applications. IEEE Trans. Electron Device. 2022, 69, 1028–1033. [Google Scholar] [CrossRef]

- Jerry, M.; Dutta, S.; Kazemi, A.; Ni, K.; Zhang, J.; Chen, P.; Sharma, P.; Yu, S.; Hu, X.; Niemier, M.; et al. A Ferroelectric Field Effect Transistor based Synaptic Weight Cell. J. Phys. D Appl. Phys. 2018, 51, 434001. [Google Scholar] [CrossRef]

- Kim, M.; Lee, J. Ferroelectric Analog Synaptic Transistors. Nano Lett. 2019, 19, 2044–2050. [Google Scholar] [CrossRef] [PubMed]

- Nam, K.; Park, J.; Kwon, K.; Choi, B. Charge Pumping Technique to Measure Polarization Switching Charges of FeFETs. IEEE Electron Device Lett. 2022, 69, 5289–5296. [Google Scholar] [CrossRef]

- Toprasertpong, K.; Tahara, K.; Takenaka, M.; Takagi, S. Evaluation of Polarization Characteristics in Metal/Ferroelectric/Semiconductor Capacitors and Ferroelectric Field-Effect Transistors. Appl. Phys. Lett. 2020, 116, 242903. [Google Scholar] [CrossRef]

- Rani, K. Switchable Photovoltaic Properties in Ferroelectric PZT Thin Films. Ph.D. Thesis, University of Saclay, Paris, France, 21 March 2022. [Google Scholar]

- Ni, K.; Jerry, M.; Smith, J.; Datta, S. A Circuit Compatible Accurate Compact Model for Ferroelectric-Fets. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 131–132. [Google Scholar]

- Liu, Y.; Su, P. Comparison of 2-D MoS2 and Si Ferroelectric FET Nonvolatile Memories Considering the Trapped-Charge-Induced Variability. IEEE Trans. Electron Device 2022, 69, 2738–2740. [Google Scholar] [CrossRef]

| VPGM | ΔVT12 | ΔVT13 | Dominant Role |

|---|---|---|---|

| ≤2 V | - | - | - |

| >2 V and ≤4.5 V | ↑ | ↑ | CT and FS |

| >4.5 V | - | ↑ | CT |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, J.; Bi, J.; Xu, Y.; Niu, G.; Liu, M.; Stempitsky, V. Effects of Charge Trapping on Memory Characteristics for HfO2-Based Ferroelectric Field Effect Transistors. Nanomaterials 2023, 13, 638. https://doi.org/10.3390/nano13040638

Wang J, Bi J, Xu Y, Niu G, Liu M, Stempitsky V. Effects of Charge Trapping on Memory Characteristics for HfO2-Based Ferroelectric Field Effect Transistors. Nanomaterials. 2023; 13(4):638. https://doi.org/10.3390/nano13040638

Chicago/Turabian StyleWang, Jianjian, Jinshun Bi, Yannan Xu, Gang Niu, Mengxin Liu, and Viktor Stempitsky. 2023. "Effects of Charge Trapping on Memory Characteristics for HfO2-Based Ferroelectric Field Effect Transistors" Nanomaterials 13, no. 4: 638. https://doi.org/10.3390/nano13040638

APA StyleWang, J., Bi, J., Xu, Y., Niu, G., Liu, M., & Stempitsky, V. (2023). Effects of Charge Trapping on Memory Characteristics for HfO2-Based Ferroelectric Field Effect Transistors. Nanomaterials, 13(4), 638. https://doi.org/10.3390/nano13040638