Temperature-Dependent Carrier Transport in GaN Nanowire Wrap-Gate Transistor

Abstract

1. Introduction

2. Materials and Methods

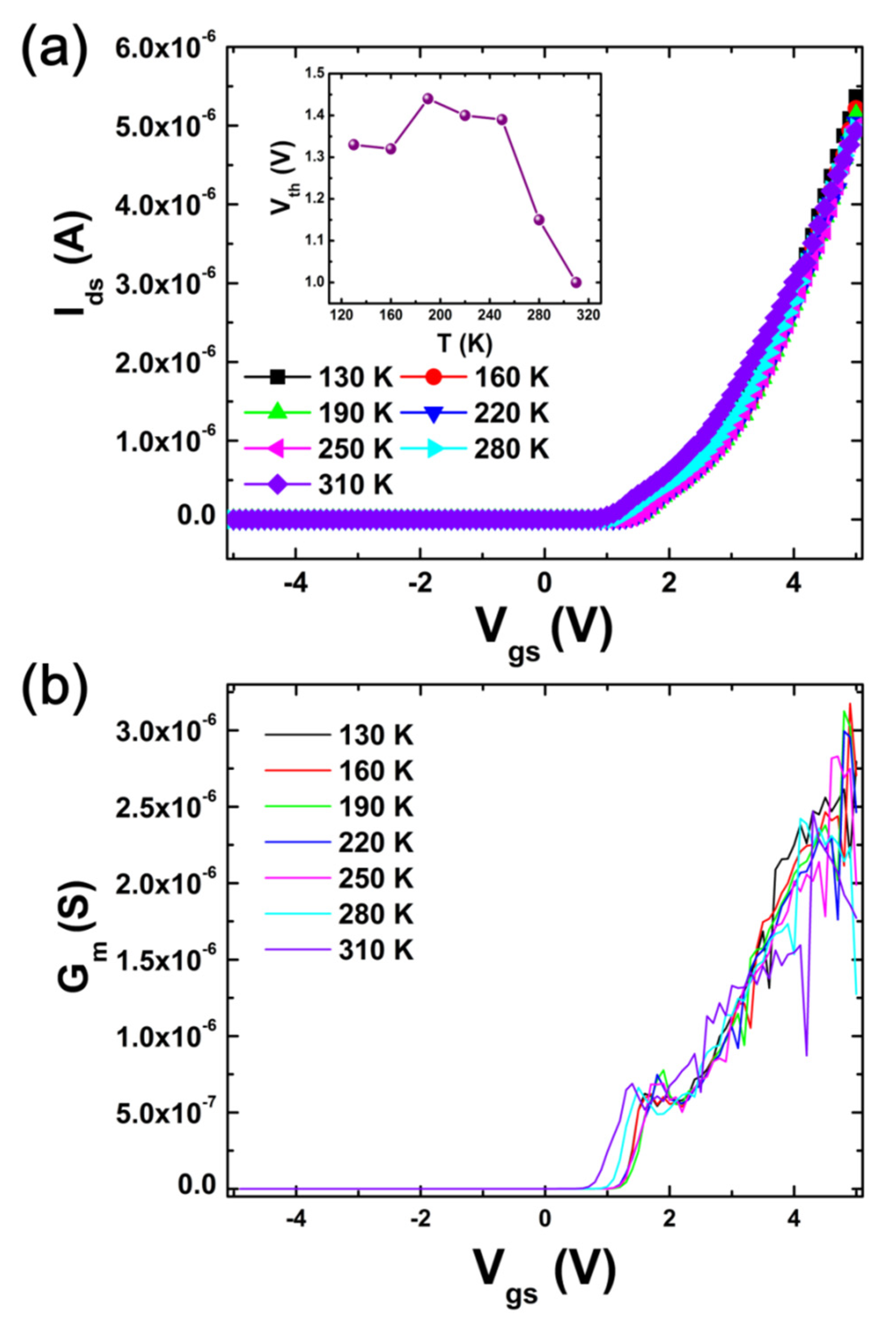

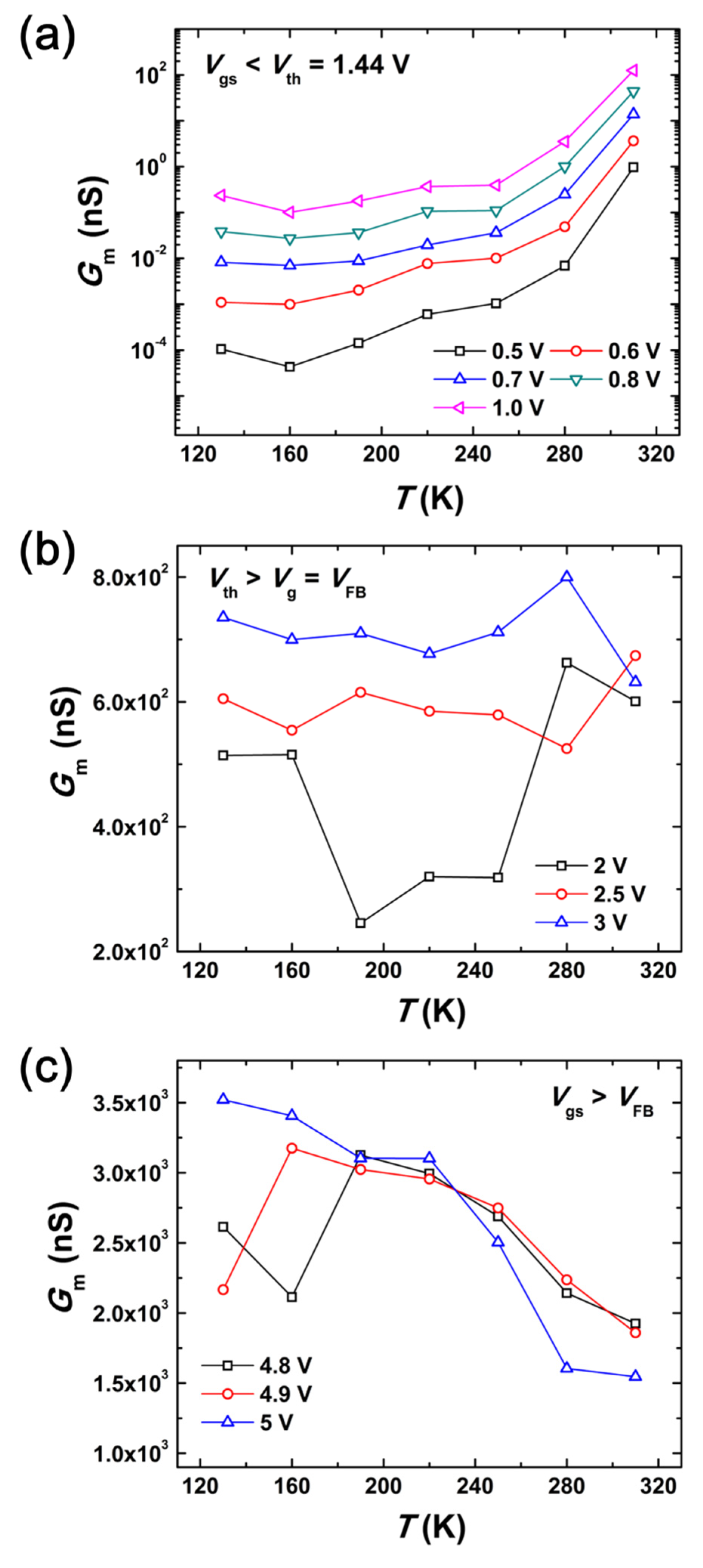

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lieber, C.M.; Wang, Z.L. Functional nanowires. MRS Bull. 2007, 32, 99–108. [Google Scholar] [CrossRef]

- Yang, P.; Yan, R.; Fardy, M. Semiconductor nanowire: What’s next? Nano. Lett. 2010, 10, 1529–1536. [Google Scholar] [CrossRef] [PubMed]

- Calarco, R.; Stoica, T.; Brandt, O.; Geelhaar, L. Surface-induced effects in GaN nanowires. J. Mater. Res. 2007, 26, 2157–2168. [Google Scholar] [CrossRef]

- Kumar, N.; Raman, A. Prospective sensing applications of novel heteromaterial based dopingless nanowire-TFET at low operating voltage. IEEE Trans. Nanotechnol. 2020, 19, 527–534. [Google Scholar] [CrossRef]

- Ranjan, R.; Kashyap, N.; Raman, A. High-performance dual-gate-charge-plasma-AlGaN/GaN MIS-HEMT. Appl. Phys. A 2020, 126, 169. [Google Scholar] [CrossRef]

- Raman, A.; Chattopadhayay, S.P.; Ranjan, R.; Kakkar, D.; Sharma, R. Design and investigation of dual dielectric recessed-gate AlGaN/GaN HEMT as gas sensor application. Trans. Electr. Electron. Mater. 2022, 23, 618–623. [Google Scholar] [CrossRef]

- He, T.; Zhang, X.; Ding, X.; Sun, C.; Zhao, Y.; Yu, Q.; Ning, J.; Wang, R.; Yu, G.; Lu, S.; et al. Broadband Ultraviolet Photodetector Based on Vertical Ga2O3/GaN Nanowire Array with High Responsivity. Adv. Opt. Mater. 2019, 7, 1801563. [Google Scholar] [CrossRef]

- Mozharov, A.M.; Kudryashov, D.A.; Bolshakov, A.D.; Tsyrlin, G.E.; Gudovskikh, A.S.; Mukhin, I.S. Numerical modeling of the characteristics of solar cells based on GaPNAs/Si heterostructures of GaN filamentous nanocrystals. Semicond. Phys. 2016, 50, 1543–1547. [Google Scholar]

- Zhao, D.; Huang, H.; Chen, S.; Li, Z.; Li, S.; Wang, M.; Zhu, H.; Chen, X. In situ growth of leakage-free direct-bridging GaN nanowires: Application to gas sensor of long term stability, low power consumption and sub-ppb detection limit. Nano Lett. 2019, 19, 3448–3456. [Google Scholar] [CrossRef]

- Shugurov, K.Y.; Reznik, R.R.; Mozharov, A.M.; Kotlyar, K.P.; Koval, O.Y.; Osipov, A.V.; Fedorov, V.V.; Shtrom, I.V.; Bolshakov, A.D.; Kukushkin, S.A.; et al. Study of SiC buffer layer thickness influence on photovoltaic properties of n-GaN NWs/SiC/p-Si heterostructure. Mater. Sci. Semicond. Process. 2019, 90, 20–25. [Google Scholar] [CrossRef]

- Shugurov, K.Y.; Mozharov, A.M.; Bolshakov, A.D.; Fedorov, V.V.; Sapunov, G.A.; Shtrom, I.V.; Uvarov, A.V.; Kudryashov, D.A.; Baranov, A.I.; Mikhailovskii, Y.V. Hydrogen passivation of the n-GaN nanowire/p-Si heterointerface. Nanotechnology 2020, 31, 244003. [Google Scholar] [CrossRef] [PubMed]

- Brubaker, M.D.; Genter, K.L.; Roshko, A.; Blanchard, P.T.; Spann, B.T.; Harvey, T.E.; Bertness, K.A. UV LEDs based on p–i–n core–shell AlGaN/GaN nanowire heterostructures grown by N-polar selective area epitaxy. Nanotechnology 2019, 30, 234001. [Google Scholar] [CrossRef] [PubMed]

- Im, K.-S. Impact of fin width on low-frequency noise in AlGaN/GaN finFETs: Evidence for bulk conduction. IEEE Access 2023, 11, 10384. [Google Scholar] [CrossRef]

- Doyle, B.S.; Boyanov, B.S.; Datta, S.M.; Doczy, M.L.; Hareland, S.; Jin, B.; Kavalieros, J.T.; Linton, T.M.; Rios, R.; Chau, R. Tri-gate fully-depleted CMOS transistors: Fabrication, design and layout. In Proceedings of the 2003 Symposium on VLSI Technology, Kyoto, Japan, 10–12 June 2003; Volume 133. [Google Scholar]

- Im, K.-S.; Sindhuri, V.; Jo, Y.-W.; Son, D.-H.; Lee, J.-H.; Cristoloveanu, S. Fabrication of AlGaN/GaN Ω-shaped nanowire fin-shaped FETs by a top-down approach. Appl. Phys. Express 2015, 8, 066501. [Google Scholar] [CrossRef]

- Im, K.-S.; Reddy, M.S.P.; Caulmione, R.; Theodorou, C.G.; Ghibaudo, G.; Cristoloveanu, S.; Lee, J.-H. Low-frequency noise characteristics of GaN nanowire gate-all-around transistors with/without 2-DEG channel. IEEE Trans. Electron Devices 2019, 66, 1243–1248. [Google Scholar] [CrossRef]

- Im, K.-S.; An, S.J.; Theodorou, C.G.; Ghibaudo, G.; Cristoloveanu, S.; Lee, J.-H. Effect of gate structure on the trapping behavior of GaN junctionless finFETs. IEEE Electron Device Lett. 2020, 41, 832–835. [Google Scholar] [CrossRef]

- Singh, N.; Lim, F.Y.; Wang, W.W.; Rustagi, S.C.; Bera, L.K.; Agarwal, A.; Tung, C.H.; Hoe, K.M.; Omampuliyur, S.; Tripathi, D.; et al. Ultra-narrow silicon gate-all-around CMOS devices: Impact of diameter, channel-orientation and low temperature on device performance. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Konar, A.; Mathew, J.; Nayak, K.; Bajaj, M.; Pandey, R.K.; Dhara, S.; Murali, K.V.R.M.; Deshmukh, M.M. Carrier transport in high mobility InAs nanowire junctionless transistors. Nano Lett. 2015, 15, 1684–1690. [Google Scholar] [CrossRef]

- Singh, S.; Raman, A. Design and dopingless GaN nanowire FET with low ‘Q’ for high switching and RF applications. Silicon 2022, 14, 1297–1307. [Google Scholar] [CrossRef]

- Kumari, N.; Raman, A.; Kakkar, D.; Sing, S.; Kumar, N. Noise distortion analysis of the designed heterodielectric dual-material gate dopingless nanowire FET. J. Electron. Mater. 2023, 52, 3253–3263. [Google Scholar] [CrossRef]

- Im, K.-S.; Won, C.-H.; Vodapally, S.; Caulmione, R.; Kim, Y.; Lee, J.-H.; Cristoloveanu, S. Fabrication of normally-off GaN nanowire gate-all-around FET with top-down approach. Appl. Phys. Lett. 2016, 109, 143106. [Google Scholar] [CrossRef]

- Reddy, M.S.P.; Im, K.-S.; Lee, J.-H.; Caulmione, R.; Cristoloveanu, S. Trap and 1/f-noise effects at the surface and core of GaN nanowire gate-all-around FET structure. Nano Res. 2019, 12, 809–814. [Google Scholar] [CrossRef]

- Mallem, S.P.R.; Thinguram, T.; Lee, J.-H.; Caulmilone, R.; Cristoloveanu, S. Gate architecture effects on the gate leakage characteristics of GaN wrap-gate nanowire transistors. Electron. Mater. Lett. 2020, 16, 433–440. [Google Scholar] [CrossRef]

- Dyakonova, N.; Dickens, A.; Shur, M.S.; Gaska, R.; Yang, J.W. Temperature dependence of impact ionization in AlGaN-GaN heterostructure field effect transistors. Appl. Phys. Lett. 1998, 72, 2562–2564. [Google Scholar] [CrossRef]

- Arulkumaran, S.; Egawa, T.; Ishikawa, H.; Jimbo, T. Temperature dependence of gate-leakage current in AlGaN/GaN high-electron-mobility transistors. Appl. Phys. Lett. 2003, 82, 3110–3112. [Google Scholar] [CrossRef]

- Son, D.-H.; Jo, Y.-W.; Seo, J.-H.; Won, C.-H.; Im, K.-S.; Lee, Y.-S.; Jang, H.-S.; Kim, D.-H.; Kang, I.-M.; Lee, J.-H. Low-voltage operation of GaN vertical nanowire MOSFET. Solid-State Electron. 2018, 145, 1–7. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mallem, S.P.R.; Puneetha, P.; Choi, Y.; Baek, S.M.; An, S.J.; Im, K.-S. Temperature-Dependent Carrier Transport in GaN Nanowire Wrap-Gate Transistor. Nanomaterials 2023, 13, 1629. https://doi.org/10.3390/nano13101629

Mallem SPR, Puneetha P, Choi Y, Baek SM, An SJ, Im K-S. Temperature-Dependent Carrier Transport in GaN Nanowire Wrap-Gate Transistor. Nanomaterials. 2023; 13(10):1629. https://doi.org/10.3390/nano13101629

Chicago/Turabian StyleMallem, Siva Pratap Reddy, Peddathimula Puneetha, Yeojin Choi, Seung Mun Baek, Sung Jin An, and Ki-Sik Im. 2023. "Temperature-Dependent Carrier Transport in GaN Nanowire Wrap-Gate Transistor" Nanomaterials 13, no. 10: 1629. https://doi.org/10.3390/nano13101629

APA StyleMallem, S. P. R., Puneetha, P., Choi, Y., Baek, S. M., An, S. J., & Im, K.-S. (2023). Temperature-Dependent Carrier Transport in GaN Nanowire Wrap-Gate Transistor. Nanomaterials, 13(10), 1629. https://doi.org/10.3390/nano13101629