Low-Temperature (≤500 °C) Complementary Schottky Source/Drain FinFETs for 3D Sequential Integration

Abstract

:1. Introduction

2. Device Fabrication

3. Results and Discussion

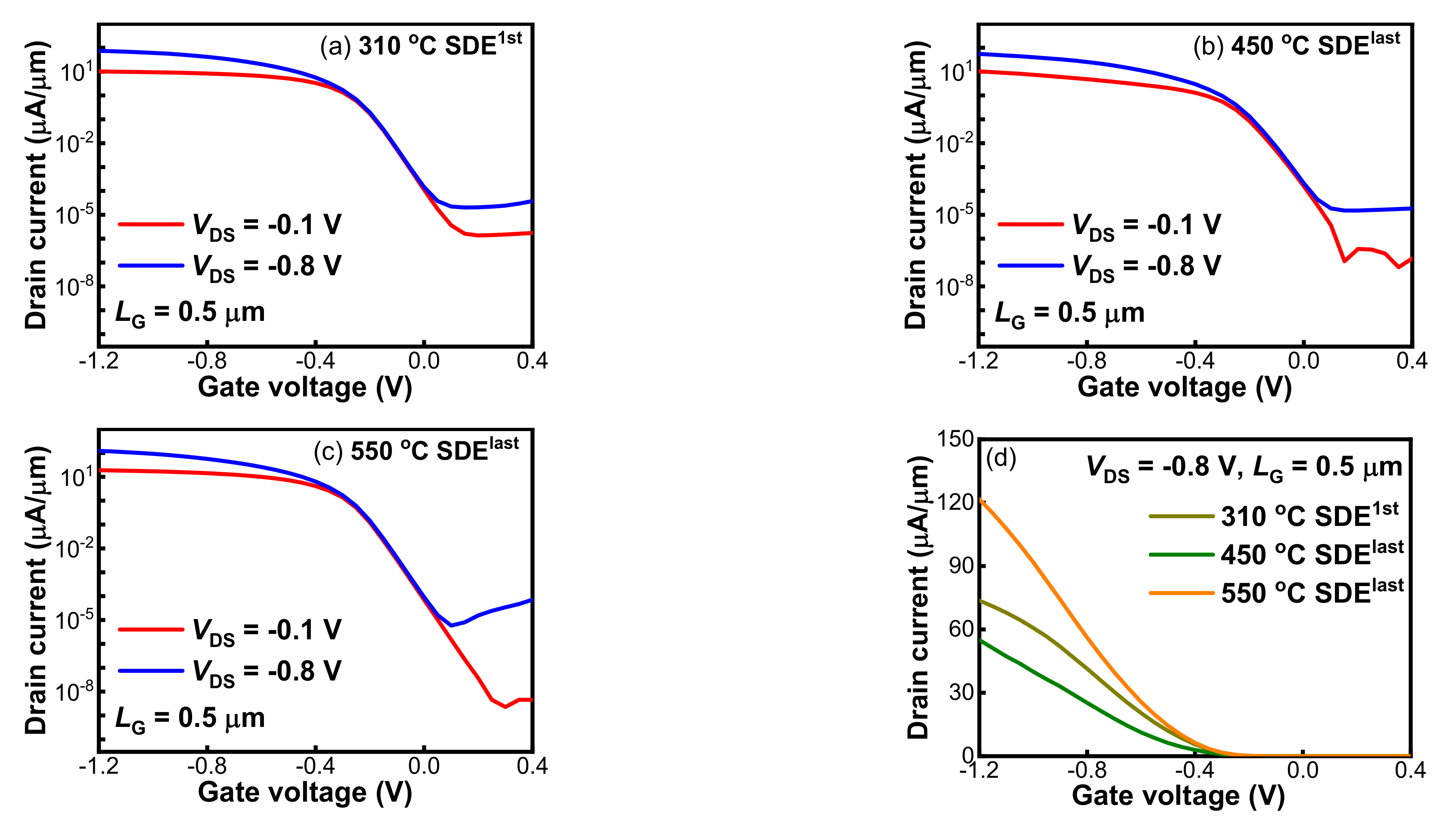

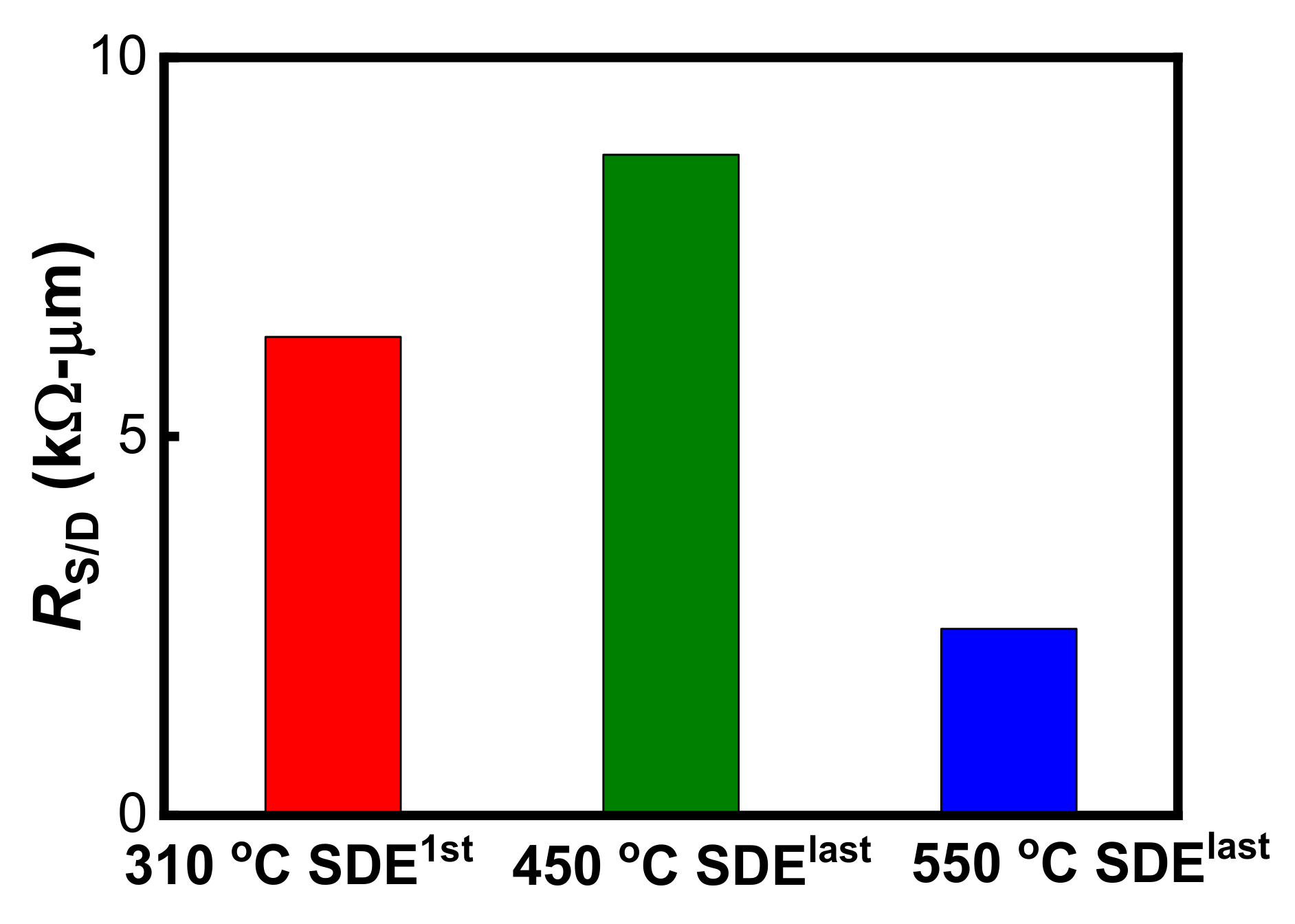

3.1. SDE Engineering

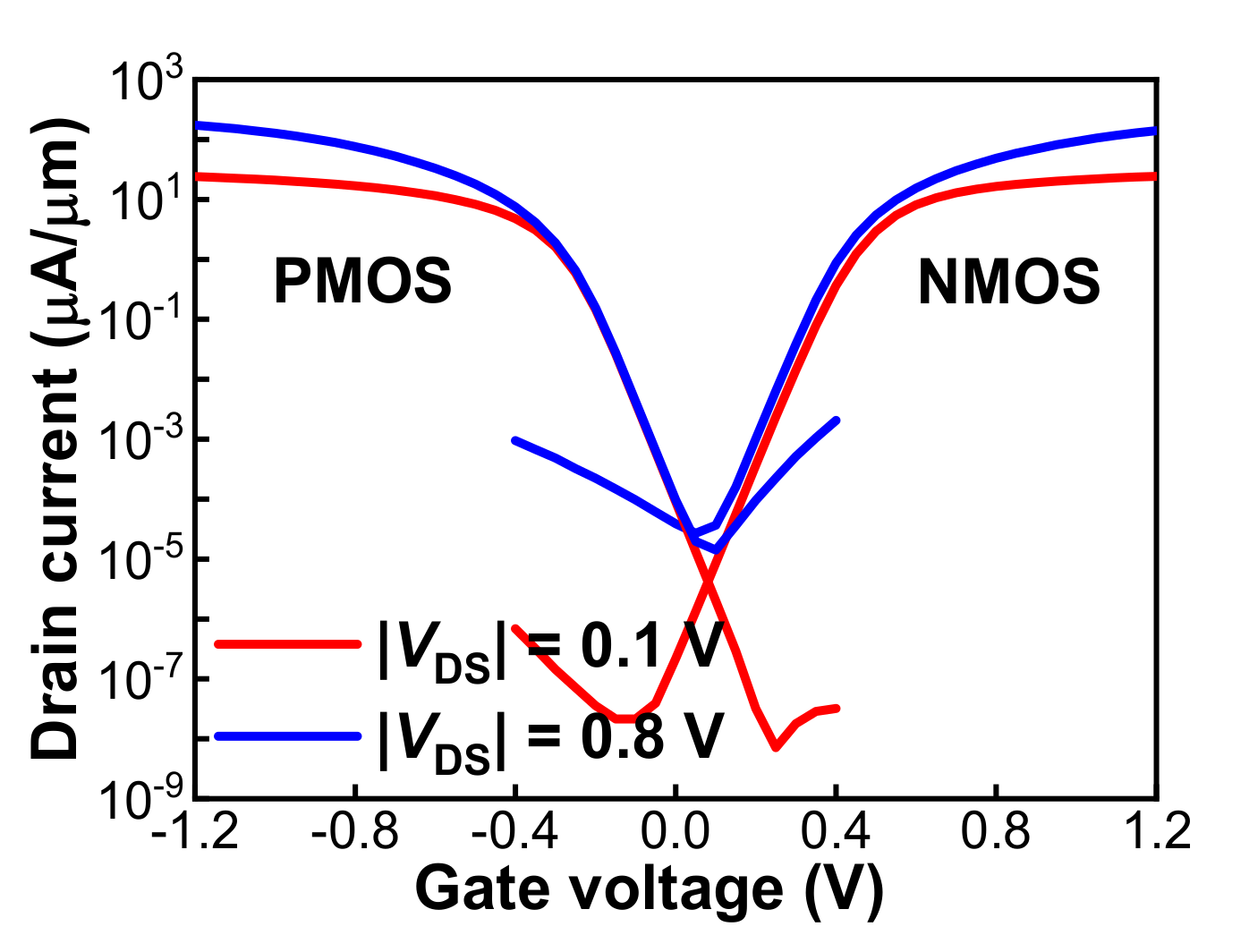

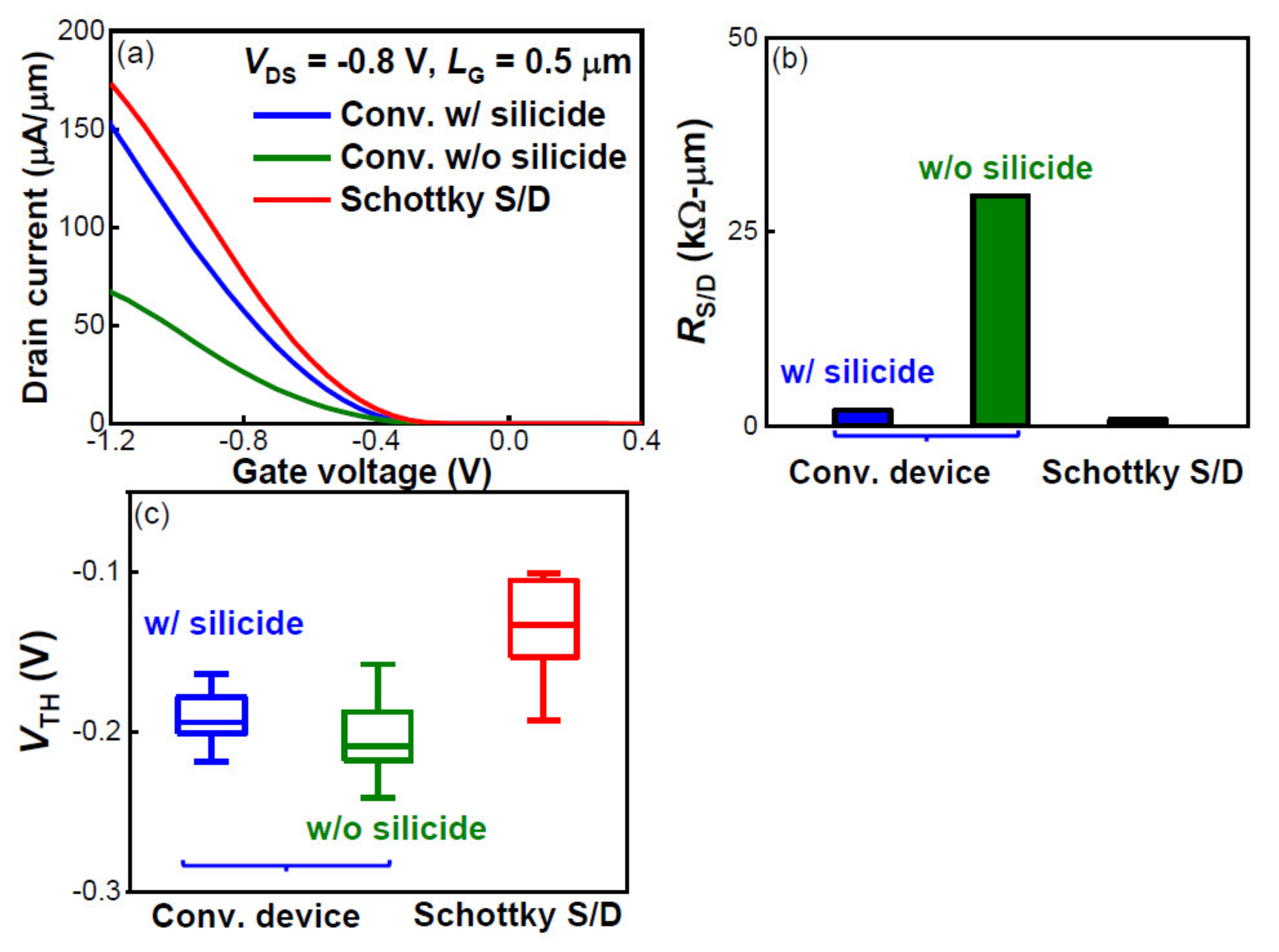

3.2. Low-Temperature Schottky S/D FinFETs vs. Conventional High-Temperature FinFETs

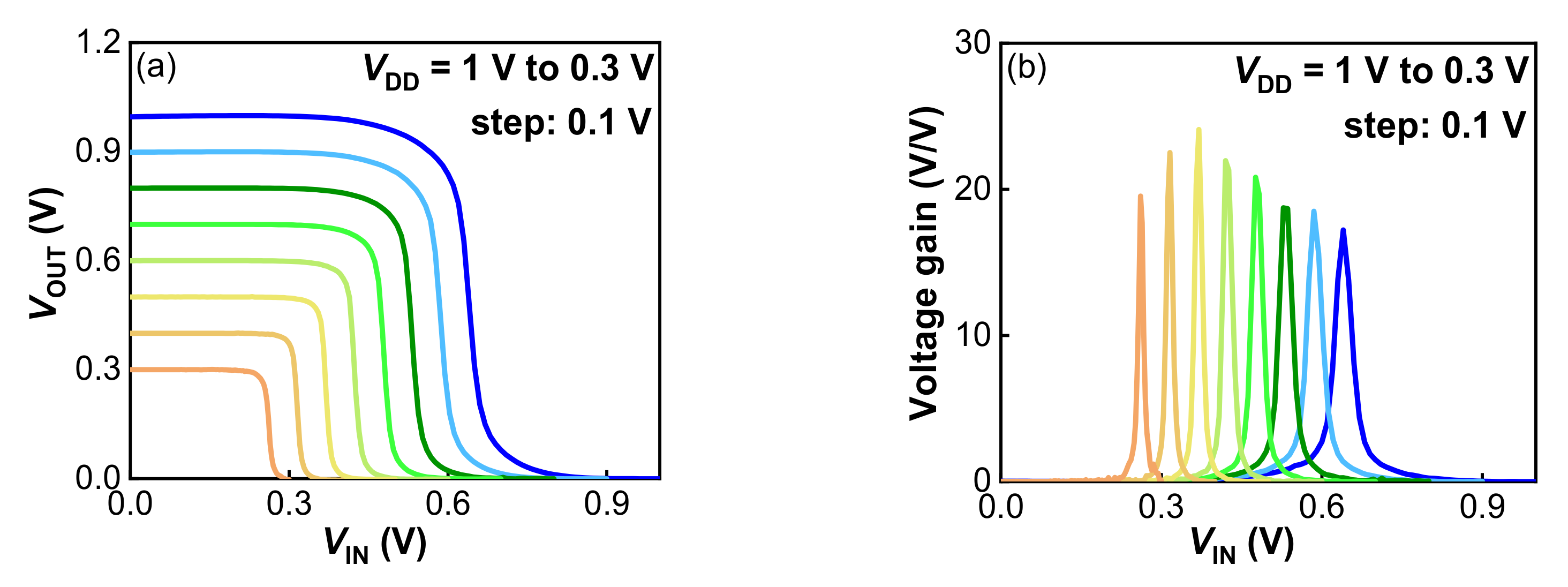

3.3. Inverter Characterization

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- International Technology Roadmap for Semiconductors. Available online: http://public.itrs.net/ (accessed on 9 February 2022).

- Vivet, P.; Thuriès, S.; Billoint, O.; Choisnet, S.; Lattard, D.; Beigné, E.; Batude, P. Monolithic 3D: An alternative to advanced CMOS scaling, technology perspectives and associated design methodology challenges. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; pp. 157–160. [Google Scholar]

- Lu, C.-M.; Deprat, F.; Fenouillet-Beranger, C.; Batude, P.; Garros, X.; Tsiara, A.; Leroux, C.; Gassilloud, R.; Nouguier, D.; Ney, D. Key process steps for high performance and reliable 3D Sequential Integration. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T226–T227. [Google Scholar]

- Vandooren, A.; Witters, L.; Franco, J.; Mallik, A.; Parvais, B.; Wu, Z.; Walke, A.; Deshpande, V.; Rosseel, E.; Hikavyy, A. Sequential 3D: Key integration challenges and opportunities for advanced semiconductor scaling. In Proceedings of the 2018 International Conference on IC Design & Technology (ICICDT), Otranto, Italy, 4–6 June 2018; pp. 145–148. [Google Scholar]

- Fenouillet-Beranger, C.; Brunet, L.; Batude, P.; Brevard, L.; Garros, X.; Casse, M.; Lacord, J.; Sklenard, B.; Acosta-Alba, P.; Kerdiles, S. A Review of Low Temperature Process Modules Leading Up to the First (≤500 °C) Planar FDSOI CMOS Devices for 3-D Sequential Integration. IEEE Trans. Electron Devices 2021, 68, 3142–3148. [Google Scholar] [CrossRef]

- Vandooren, A.; Wu, Z.; Parihar, N.; Franco, J.; Parvais, B.; Matagne, P.; Debruyn, H.; Mannaert, G.; Devriendt, K.; Teugels, L. 3D sequential low temperature top tier devices using dopant activation with excimer laser anneal and strained silicon as performance boosters. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar]

- Micout, J.; Lapras, V.; Batude, P.; Fenouillet-Beranger, C.; Lacord, J.; Sklenard, B.; Mathieu, B.; Rafhay, Q.; Mazzocchi, V.; Colinge, J.-P. High performance low temperature FinFET with DSPER, gate last and Self Aligned Contact for 3D sequential mtegration. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 32.32.31–32.32.34. [Google Scholar]

- Yang, C.-C.; Hsieh, T.-Y.; Huang, P.-T.; Chen, K.-N.; Wu, W.-C.; Chen, S.-W.; Chang, C.-H.; Shen, C.-H.; Shieh, J.-M.; Hu, C. Location-controlled-grain technique for monolithic 3D BEOL FinFET circuits. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 11.13.11–11.13.14. [Google Scholar]

- Hsieh, P.-Y.; Chang, Y.-J.; Chen, P.-J.; Chen, C.-L.; Yang, C.-C.; Huang, P.-T.; Chen, Y.-J.; Shen, C.-M.; Liu, Y.-W.; Huang, C.-C. Monolithic 3D BEOL FinFET switch arrays using location-controlled-grain technique in voltage regulator with better FOM than 2D regulators. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 3.1.1–3.1.4. [Google Scholar]

- Huang, C.-Y.; Dewey, G.; Mannebach, E.; Phan, A.; Morrow, P.; Rachmady, W.; Tung, I.-C.; Thomas, N.; Alaan, U.; Paul, R. 3-D self-aligned stacked NMOS-on-PMOS nanoribbon transistors for continued Moore’s law scaling. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 20.26.21–20.26.24. [Google Scholar]

- Liu, Y.-W.; Hu, H.-W.; Hsieh, P.-Y.; Chung, H.-T.; Chang, S.-J.; Liu, J.-H.; Huang, P.-T.; Yang, C.-C.; Shen, C.-H.; Shieh, J.-M. Single-Crystal Islands (SCI) for Monolithic 3-D and Back-End-of-Line FinFET Circuits. IEEE Trans. Electron Devices 2021, 68, 5257–5262. [Google Scholar] [CrossRef]

- Deshpande, V.; Djara, V.; O’Connor, E.; Hashemi, P.; Morf, T.; Balakrishnan, K.; Caimi, D.; Sousa, M.; Fompeyrine, J.; Czornomaz, L. Three-dimensional monolithic integration of III–V and Si (Ge) FETs for hybrid CMOS and beyond. Jpn. J. Appl. Phys. 2017, 56, 04CA05. [Google Scholar] [CrossRef] [Green Version]

- Deshpande, V.; Djara, V.; O’Connor, E.; Hashemi, P.; Balakrishnan, K.; Sousa, M.; Caimi, D.; Olziersky, A.; Czornomaz, L.; Fompeyrine, J. Advanced 3D monolithic hybrid CMOS with sub-50 nm gate inverters featuring replacement metal gate (RMG)-InGaAs nFETs on SiGe-OI fin pFETs. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 8.8.1–8.8.4. [Google Scholar]

- Chang, S.-W.; Lu, T.-H.; Yang, C.-Y.; Yeh, C.-J.; Huang, M.-K.; Meng, C.-F.; Chen, P.-J.; Chang, T.-H.; Chang, Y.-S.; Jhu, J.-W. First Demonstration of Heterogeneous IGZO/Si CFET Monolithic 3-D Integration With Dual Work Function Gate for Ultralow-Power SRAM and RF Applications. IEEE Trans. Electron Devices 2022, 69, 2101–2107. [Google Scholar] [CrossRef]

- Chakraborty, W.; Ye, H.; Grisafe, B.; Lightcap, I.; Datta, S. Low Thermal Budget (<250 °C) Dual-Gate Amorphous Indium Tungsten Oxide (IWO) Thin-Film Transistor for Monolithic 3-D Integration. IEEE Trans. Electron Devices 2020, 67, 5336–5342. [Google Scholar] [CrossRef]

- Vandooren, A.; Franco, J.; Parvais, B.; Wu, Z.; Witters, L.; Walke, A.; Li, W.; Peng, L.; Deshpande, V.; Bufler, F.M. 3-D sequential stacked planar devices featuring low-temperature replacement metal gate junctionless top devices with improved reliability. IEEE Trans. Electron Devices 2018, 65, 5165–5171. [Google Scholar] [CrossRef]

- Vandooren, A.; Franco, J.; Wu, Z.; Parvais, B.; Li, W.; Witters, L.; Walke, A.; Peng, L.; Deshpande, V.; Rassoul, N. First Demonstration of 3D stacked Finfets at a 45 nm fin pitch and 110 nm gate pitch technology on 300 mm wafers. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 7.1.1–7.1.4. [Google Scholar]

- Lepselter, M.; Sze, S. SB-IGFET: An insulated-gate field-effect transistor using Schottky barrier contacts for source and drain. Proc. IEEE 1968, 56, 1400–1402. [Google Scholar] [CrossRef]

- Tsui, B.-Y.; Lin, C.-P. A novel 25-nm modified Schottky-barrier FinFET with high performance. IEEE Electron Device Lett. 2004, 25, 430–432. [Google Scholar] [CrossRef]

- Kaneko, A.; Yagishita, A.; Yahashi, K.; Kubota, T.; Omura, M.; Matsuo, K.; Mizushima, I.; Okano, K.; Kawasaki, H.; Izumida, T. High-performance FinFET with dopant-segregated Schottky source/drain. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

- Khater, M.H.; Zhang, Z.; Cai, J.; Lavoie, C.; D’Emic, C.; Yang, Q.; Yang, B.; Guillorn, M.; Klaus, D.; Ott, J.A. High-k/Metal-Gate Fully Depleted SOI CMOS with Single-Silicide Schottky Source/Drain with Sub-30-nm Gate Length. IEEE Electron Device Lett. 2010, 31, 275–277. [Google Scholar] [CrossRef]

- Ko, C.; Chen, H.; Wang, T.; Kuan, T.; Hsu, J.; Huang, C.; Ge, C.; Lai, L.; Lee, W. NiSi Schottky barrier process-strained Si (SB-PSS) CMOS technology for high performance applications. In Proceedings of the 2006 Symposium on VLSI Technology, Honolulu, HI, USA, 13–15 June 2006; pp. 80–81. [Google Scholar]

- Chin, Y.; Pey, K.; Singh, N.; Lo, G.; Tan, L.; Zhu, G.; Zhou, X.; Wang, X.; Zheng, H. Excimer laser-annealed dopant segregated Schottky (ELA-DSS) Si nanowire gate-all-around (GAA) pFET with near zero effective Schottky barrier height (SBH). In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–9 December 2009; pp. 1–4. [Google Scholar]

- Nishisaka, M.; Matsumoto, S.; Asano, T. Schottky source/drain SOI MOSFET with shallow doped extension. Jpn. J. Appl. Phys. 2003, 42, 2009. [Google Scholar] [CrossRef] [Green Version]

- Schroder, D.K. Semiconductor Material and Device Characterization; John Wiley & Sons: Hoboken, NJ, USA, 2015. [Google Scholar]

- Chen, L.J. Silicide Technology for Integrated Circuits; Iet: London, UK, 2004; Volume 5. [Google Scholar]

- Qiu, Z.; Zhang, Z.; Ostling, M.; Zhang, S.-L. A comparative study of two different schemes to dopant segregation at NiSi/Si and PtSi/Si interfaces for Schottky barrier height lowering. IEEE Trans. Electron Devices 2007, 55, 396–403. [Google Scholar] [CrossRef]

- Luo, J.; Qiu, Z.-J.; Zhang, Z.; Östling, M.; Zhang, S.-L. Interaction of NiSi with dopants for metallic source/drain applications. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Processing Meas. Phenom. 2010, 28, C1I1–C1I11. [Google Scholar] [CrossRef]

- Zhang, Z.; Qiu, Z.; Liu, R.; Ostling, M.; Zhang, S.-L. Schottky-barrier height tuning by means of ion implantation into preformed silicide films followed by drive-in anneal. IEEE Electron Device Lett. 2007, 28, 565–568. [Google Scholar] [CrossRef]

- Lu, J.; Miles, D.; Zhao, J.; Gurba, A.; Xu, Y.; Lin, C.; Hewson, M.; Ruan, J.; Tsung, L.; Kuan, R. A novel nickel SALICIDE process technology for CMOS devices with sub-40 nm physical gate length. In Proceedings of the Digest. International Electron Devices Meeting, San Francisco, CA, USA, 8–11 December 2002; pp. 371–374. [Google Scholar]

- Kim, J.; Park, T.; Lee, S.; Lee, S.; Kim, C.; Hyun, S.; Kim, Y.; Hwang, K.; Kim, H. Effect of Millisecond Annealing Temperature of Ni 1-x Pt. x Si Formation on Leakage Current Characteristics of Static Random-Access Memory Cells. IEEE Trans. Electron Devices 2018, 66, 389–394. [Google Scholar] [CrossRef]

| Item 1 | 310 °C SDE 1st | 450 °C SDE last | 550 °C SDE last |

|---|---|---|---|

| Silicidation annealing | 310 °C 60 s | 310 °C 60 s | 500 °C 30 s |

| Drive-in annealing | NA | 450 °C 60 s | 550 °C 60 s |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mao, S.; Gao, J.; He, X.; Liu, W.; Liu, J.; Wang, G.; Zhou, N.; Luo, Y.; Cao, L.; Zhang, R.; et al. Low-Temperature (≤500 °C) Complementary Schottky Source/Drain FinFETs for 3D Sequential Integration. Nanomaterials 2022, 12, 1218. https://doi.org/10.3390/nano12071218

Mao S, Gao J, He X, Liu W, Liu J, Wang G, Zhou N, Luo Y, Cao L, Zhang R, et al. Low-Temperature (≤500 °C) Complementary Schottky Source/Drain FinFETs for 3D Sequential Integration. Nanomaterials. 2022; 12(7):1218. https://doi.org/10.3390/nano12071218

Chicago/Turabian StyleMao, Shujuan, Jianfeng Gao, Xiaobin He, Weibing Liu, Jinbiao Liu, Guilei Wang, Na Zhou, Yanna Luo, Lei Cao, Ran Zhang, and et al. 2022. "Low-Temperature (≤500 °C) Complementary Schottky Source/Drain FinFETs for 3D Sequential Integration" Nanomaterials 12, no. 7: 1218. https://doi.org/10.3390/nano12071218

APA StyleMao, S., Gao, J., He, X., Liu, W., Liu, J., Wang, G., Zhou, N., Luo, Y., Cao, L., Zhang, R., Liu, H., Li, X., Li, Y., Wu, Z., Li, J., Luo, J., Zhao, C., Wang, W., & Yin, H. (2022). Low-Temperature (≤500 °C) Complementary Schottky Source/Drain FinFETs for 3D Sequential Integration. Nanomaterials, 12(7), 1218. https://doi.org/10.3390/nano12071218