4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

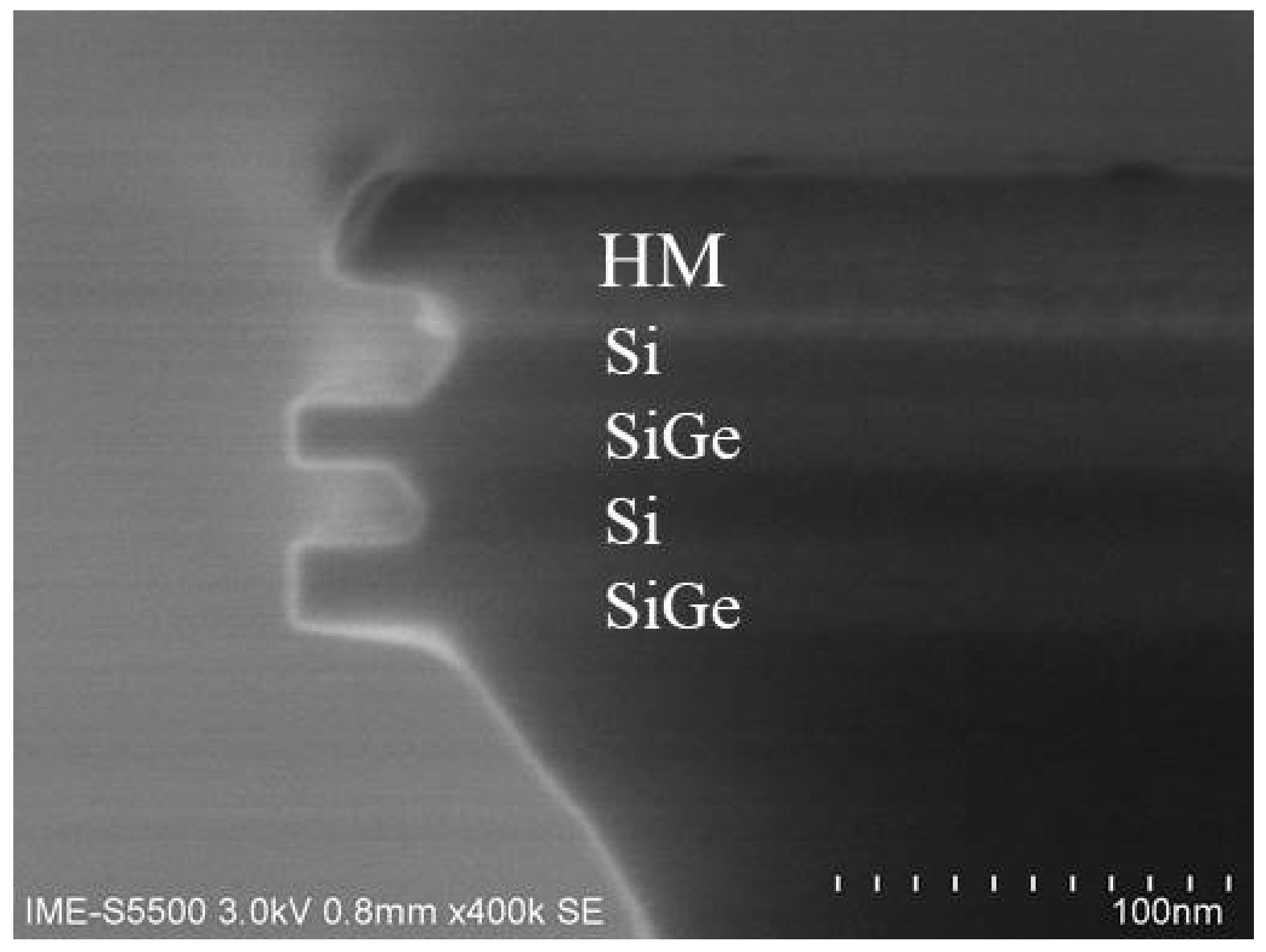

3.1. High-Quality Stacked Si0.7Ge0.3/Si Fin Formation

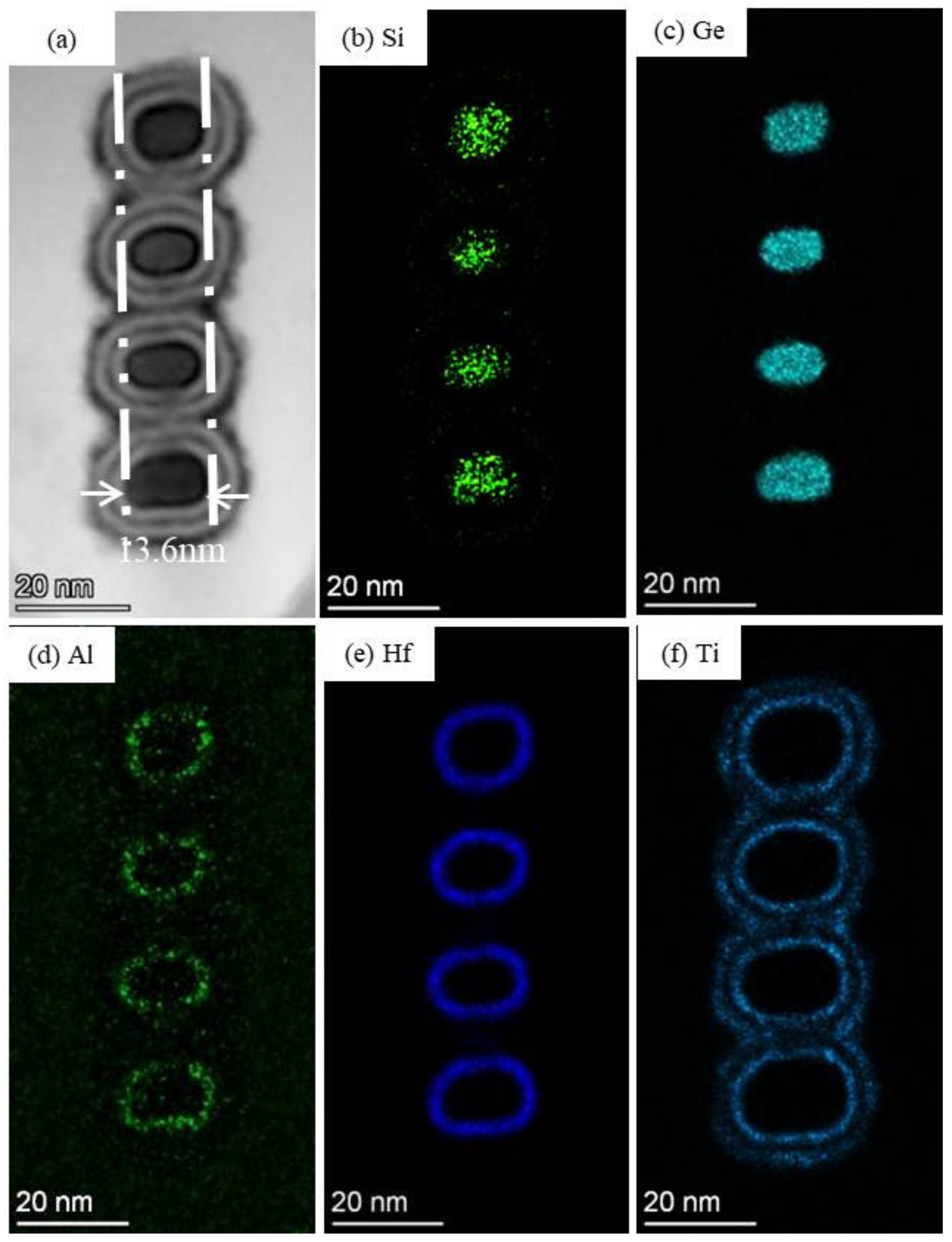

3.2. Si0.7Ge0.3 NW Channel Release

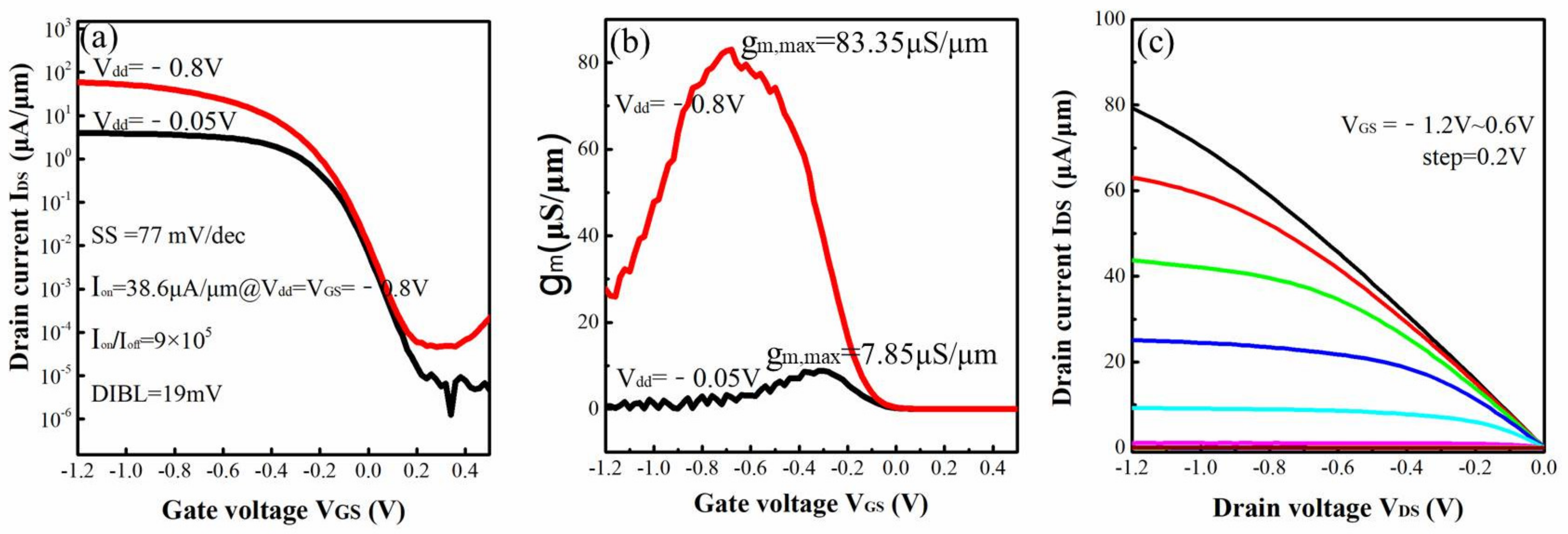

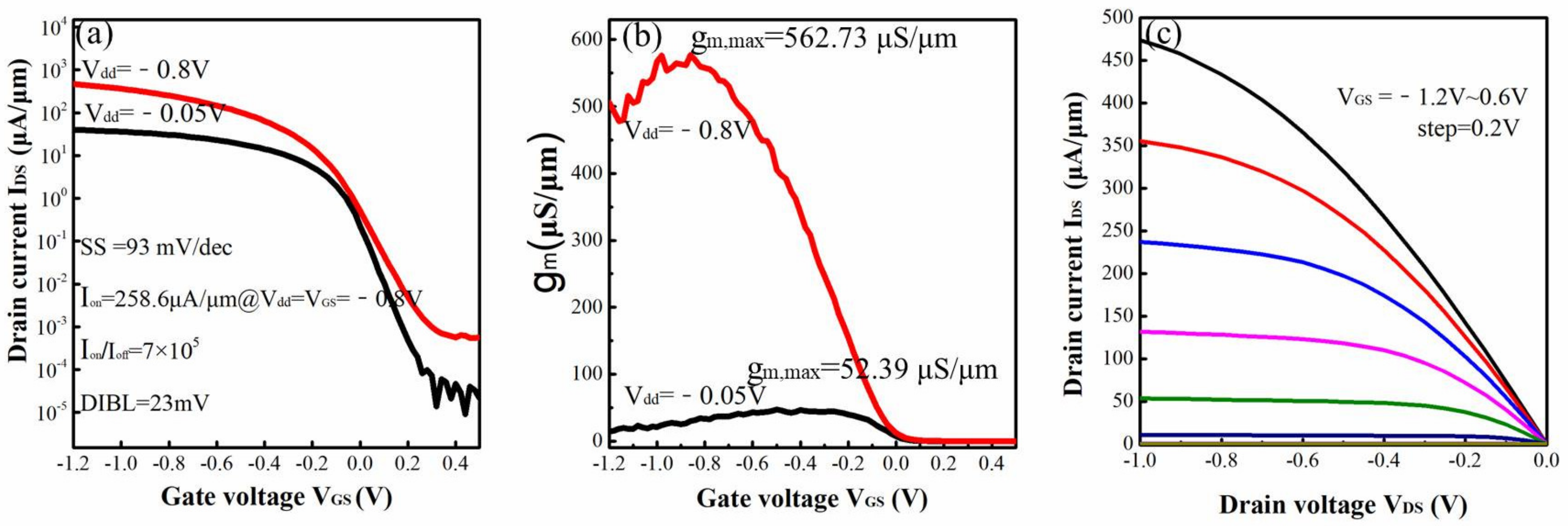

3.3. 4-Levels Vertically Stacked Si0.7Ge0.3 NW GAA Device

3.4. Electrial Perforemance Optimization

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Fang, W.W.; Singh, N.; Bera, L.K.; Nguyen, H.S.; Rustagi, S.C.; Lo, G.Q.; Balasubramanian, N.; Kwong, D. Vertically Stacked SiGe Nanowire Array Channel CMOS Transistors. IEEE Electron. Device Lett. 2007, 28, 211–213. [Google Scholar] [CrossRef]

- Veloso, A.; Eneman, G.; Huynh-Bao, T.; Chasin, A.; Simoen, E.; Vecchio, E.; Devriendt, K.; Brus, S.; Rosseel, E.; Hikavyy, A.; et al. Vertical Nanowire and Nanosheet FETs: Device Features, Novel Schemes for Improved Process Control and Enhanced Mobility, Potential for Faster & More Energy Efficient Circuits. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.1.1–11.1.4. [Google Scholar]

- Bender, H.; Bosch, E.G.T.; Richard, O.; Mendez, D.; Favia, P.; Lazić, I. 3D characterization of nanowire devices with STEM based modes. Semicond. Sci. Technol. 2019, 34, 114001. [Google Scholar] [CrossRef]

- Liu, X.-Y.; Hao, J.-L.; You, N.-N.; Bai, Y.; Tang, Y.-D.; Yang, C.-Y.; Wang, S.-K. High-mobility SiC MOSFET with low density of interface traps using high pressure microwave plasma oxidation. Chin. Phys. B 2020, 29, 037301. [Google Scholar] [CrossRef]

- Pavlidis, G.; Hilton, A.M.; Brown, J.L.; Heller, E.R.; Graham, S. Monitoring the Joule heating profile of GaN/SiC high electron mobility transistors via cross-sectional thermal imaging. J. Appl. Phys. 2020, 128, 075705. [Google Scholar] [CrossRef]

- Akarvardar, K.; Wang, M.; Bao, R.; Burns, S.; Chan, V.; Cheng, K.; Demarest, J.; Fronheiser, J.; Hashemi, P.; Kelly, J.; et al. FINFET Technology Featuring High Mobility SiGe Channel for 10 nm and Beyond. In Proceedings of the IEEE Symposium on VLSI Technology (VLSI), Honolulu, HI, USA, 13–16 January 2016. [Google Scholar]

- Ando, T.; Hashemi, P.; Bruley, J.; Rozen, J.; Ogawa, Y.; Koswatta, S.; Chan, K.K.; Cartier, E.A.; Mo, R.; Narayanan, V. High Mobility High-Ge-Content SiGe PMOSFETs Using Al2O3/HfO2 Stacks with In-Situ O3 Treatment. IEEE Electron. Device Lett. 2017, 38, 303–305. [Google Scholar] [CrossRef]

- Franco, J.; Kaczer, B.; Roussel, P.J.; Mitard, J.; Cho, M.; Witters, L.; Grasser, T.; Groeseneken, G. SiGe channel technology: Superior reliability toward ultrathin EOT devices—Part I: NBTI. IEEE Trans. Electron. Devices 2013, 60, 396. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Zan, Y.; Li, J.; Zhang, Q.; Wu, Z.; Luo, J.; Wang, W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials 2021, 11, 1689. [Google Scholar] [CrossRef] [PubMed]

- Lee, C.H.; Southwick, R.G.; Mochizuki, S.; Li, J.; Miao, X.; Wang, M.; Bao, R.; Ok, I.; Ando, T.; Hashemi, P.; et al. Toward High Performance SiGe Channel CMOS: Design of High Electron Mobility in SiGe nFinFETs Outperforming Si. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.1.1–35.1.4. [Google Scholar]

- Li, Y.; Cheng, X.; Zhong, Z.; Zhang, Q.; Wang, G.; Li, Y.; Li, J.; Ma, X.; Wang, X.; Yang, H.; et al. Key Process Technologies for Stacked Double Si0.7Ge0.3 Channel Nanowires Fabrication. ECS J. Solid State Sci. Technol. 2020, 9, 064009. [Google Scholar] [CrossRef]

- Wieser, U.; Iamundo, D.; Kunze, U.; Hackbarth, T.; König, U. Nanoscale patterning of Si/SiGe heterostructures by electron-beam lithography and selective wet-chemical etching. Semicond. Sci. Technol. 2000, 15, 862–867. [Google Scholar] [CrossRef]

- Cheng, X.; Li, Y.; Liu, H.; Zan, Y.; Lu, Y.; Zhang, Q.; Li, J.; Du, A.; Wu, Z.; Luo, J.; et al. Selective wet etching in fabricating SiGe nanowires with TMAH solution for gate-all-around MOSFETs. J. Mater. Sci. Mater. Electron. 2020, 31, 22478–22486. [Google Scholar] [CrossRef]

- Barraud, S.; Lapras, V.; Samson, M.P.; Gaben, L.; Grenouillet, L.; Maffini-Alvaro, V.; Morand, Y.; Daranlot, J.; Rambal, N.; Previtalli, B.; et al. Vertically stacked-NanoWires MOSFETs in a replacement metal gate process with inner spacer and SiGe source/drain. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 17.6.1–17.6.4. [Google Scholar]

- Hikavyy, A.; Vanherle, W.; Witters, L.; Vincent, B.; Dekoster, J.; Loo, R. High Ge Content SiGe Selective Processes for Source/Drain in Manufacturing the Next Generations of pMOS Transistors. ECS J. Solid State Sci. Technol. 2013, 2, 282–286. [Google Scholar] [CrossRef]

- Zhao, Z.; Cheng, X.; Li, Y.; Zan, Y.; Liu, H.; Wang, G.; Du, A.; Li, J.; Zhang, Q.; Xu, G.; et al. Investigation on the formation technique of SiGe Fin for the high mobility channel FinFET device. J. Mater. Sci. Mater. Electron. 2019, 31, 5854–5860. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Wang, W. Integration of Si0.7Ge0.3 fin onto a bulk-Si substrate and its P-type FinFET device fabrication. Semicond. Sci. Technol. 2021, 36, 125001. [Google Scholar] [CrossRef]

- Ahles, C.F.; Choi, J.Y.; Wolf, S.; Kummel, A.C. Selective Etching of Silicon in Preference to Germanium and Si0.5Ge0.5. ACS Appl. Mater. Interfaces 2017, 9, 20947–20954. [Google Scholar] [CrossRef] [PubMed]

- Bidal, G.; Loubet, N.; Fenouillet-Beranger, C.; Denorme, S.; Perreau, P.; Fleury, D.; Clement, L.; Laviron, C.; Leverd, F.; Gouraud, P.; et al. Folded fully depleted FET using Silicon-On-Nothing technology as a highly W-scaled planar solution. Solid-State Electron. 2009, 53, 735–740. [Google Scholar] [CrossRef]

- Liu, H.; Li, Y.; Cheng, X.; Zan, Y.; Lu, Y.; Wang, G.; Li, J.; Kong, Z.; Ma, X.; Wang, X.; et al. Fabrication and selective wet etching of Si0.2Ge0.8/Ge multilayer for Si0.2Ge0.8 channel gate-all-around MOSFETs. Mater. Sci. Semicond. Process. 2021, 121, 105397. [Google Scholar] [CrossRef]

- Liu, W.D.; Lee, Y.C.; Sekiguchi, R.; Yoshida, Y.; Komori, K.; Wostyn, K.; Sebaai, F.; Holsteyns, F. Selective Wet Etching in Fabricating SiGe and Ge Nanowires for Gate-all-Around MOSFETs. Solid State Phenom. 2018, 282, 101–106. [Google Scholar] [CrossRef]

- Demeurisse, C.; Verheyen, P.; Opsomer, K.; Vrancken, C.; Absil, P.; Lauwers, A. Thermal stability of NiPt- and Pt-silicide cotacts on SiGe source/drain. Microelectron. Eng. 2007, 84, 2547–2551. [Google Scholar] [CrossRef]

- Kittl, J.A.; Lauwers, A.; Chamirian, O.; Pawlak, M.A.; Van Dal, M.; Akheyar, A.; De Potter, M.; Kottantharayil, A.; Pourtois, G.; Lindsay, R.; et al. Applications of Ni-based silicides to 45 nm CMOS and beyond. Mater. Res. Soc. Symp. Proc. 2004, 810, 31–42. [Google Scholar] [CrossRef]

| Samples | Ion (μA/μm) | SS (mV/dec) | gm,max (μS/μm) | DIBL (mV/V) | Ioff (μA/μm) | Ion/Ioff | RSD (Ω) |

|---|---|---|---|---|---|---|---|

| W/o silicide | 38.6 | 77 | 83.85 | 19 | 4.22 × 10−5 | 9 × 105 | 9.2 × 105 |

| W/silicide | 258.6 | 93 | 562.73 | 23 | 3.71 × 10−4 | 7 × 105 | 6.4 × 104 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cheng, X.; Li, Y.; Zhao, F.; Chen, A.; Liu, H.; Li, C.; Zhang, Q.; Yin, H.; Luo, J.; Wang, W. 4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process. Nanomaterials 2022, 12, 889. https://doi.org/10.3390/nano12050889

Cheng X, Li Y, Zhao F, Chen A, Liu H, Li C, Zhang Q, Yin H, Luo J, Wang W. 4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process. Nanomaterials. 2022; 12(5):889. https://doi.org/10.3390/nano12050889

Chicago/Turabian StyleCheng, Xiaohong, Yongliang Li, Fei Zhao, Anlan Chen, Haoyan Liu, Chun Li, Qingzhu Zhang, Huaxiang Yin, Jun Luo, and Wenwu Wang. 2022. "4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process" Nanomaterials 12, no. 5: 889. https://doi.org/10.3390/nano12050889

APA StyleCheng, X., Li, Y., Zhao, F., Chen, A., Liu, H., Li, C., Zhang, Q., Yin, H., Luo, J., & Wang, W. (2022). 4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process. Nanomaterials, 12(5), 889. https://doi.org/10.3390/nano12050889