# Article 4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process

Xiaohong Cheng <sup>(D)</sup>, Yongliang Li <sup>\*</sup><sup>(D)</sup>, Fei Zhao <sup>(D)</sup>, Anlan Chen, Haoyan Liu, Chun Li, Qingzhu Zhang <sup>(D)</sup>, Huaxiang Yin <sup>(D)</sup>, Jun Luo <sup>(D)</sup> and Wenwu Wang

\* Correspondence: liyongliang@ime.ac.cn

Citation: Cheng, X.; Li, Y.; Zhao, F.; Chen, A.; Liu, H.; Li, C.; Zhang, Q.; Yin, H.; Luo, J.; Wang, W. 4-Levels Vertically Stacked SiGe Channel Nanowires Gate-All-Around Transistor with Novel Channel Releasing and Source and Drain Silicide Process. *Nanomaterials* 2022, 12, 889. https://doi.org/10.3390/ nano12050889

Academic Editors: Chih-Yen Chen, Zong-Hong Lin, Hung-Wei (Homer) Yen, Der-Hsien Lien and Salvo Mirabella

Received: 13 January 2022 Accepted: 3 March 2022 Published: 7 March 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). Abstract: In this paper, the fabrication and electrical performance optimization of a four-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> channel nanowires gate-all-around transistor are explored in detail. First, a high crystalline quality and uniform stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si film is achieved by optimizing the epitaxial growth process and a vertical profile of stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin is attained by further optimizing the etching process under the HBr/He/O<sub>2</sub> plasma. Moreover, a novel ACT@SG-201 solution without any dilution at the temperature of 40  $^{\circ}$ C is chosen as the optimal etching solution for the release process of Si<sub>0.7</sub>Ge<sub>0.3</sub> channel. As a result, the selectivity of Si to Si<sub>0.7</sub>Ge<sub>0.3</sub> can reach 32.84 with a signature of "rectangular" Si<sub>0.7</sub>Ge<sub>0.3</sub> extremities after channel release. Based on these newly developed processes, a 4-levels vertically stacked Si0.7Ge0.3 nanowires gate-all-around device is prepared successfully. An excellent subthreshold slope of 77 mV/dec, drain induced barrierlowering of 19 mV/V,  $I_{on}/I_{off}$  ratio of 9  $\times$  10  $^5$  and maximum of transconductance of ~83.35  $\mu S/\mu m$ are demonstrated. However, its driven current is only  $\sim$  38.6  $\mu$ A/ $\mu$ m under V<sub>DS</sub> = V<sub>GS</sub> = -0.8 V due to its large resistance of source and drain (9.2  $\times$  10<sup>5</sup>  $\Omega$ ). Therefore, a source and drain silicide process is implemented and its driven current can increase to  $258.6 \ \mu\text{A}/\mu\text{m}$  (about 6.7 times) due to the decrease of resistance of source and drain to  $6.4 \times 10^4 \Omega$ . Meanwhile, it is found that a slight increase of leakage after the silicide process online results in a slight deterioration of the subthreshold slope and  $I_{on}/I_{off}$  ratio. Its leakage performance needs to be further improved through the co-optimization of source and drain implantation and silicide process in the future.

Keywords: SiGe channel; gate-all-around; release; silicide

# 1. Introduction

The vertically stacked horizontal gate-all-around (GAA) transistors are now established as the most promising candidate to the FinFETs in sub-5nm technology node, due to the excellent electrostatic and short channel control [1–3]. Moreover, to keep Moore's Law alive as long as possible, researchers are also looking for alternatives to silicon channel material, like SiC, GaN, SiGe and Ge [4–7]. Among them, SiGe materials, especially those with Ge concentration between 20% and 40%, have been considered as the channel material of GAA devices. This is because they have higher electron and hole mobility, better negative bias temperature instability (NBTI) reliability [8,9] than Si and are more compatible with present Si platform [9–11]. However, the fabrication of stacked SiGe nanowire/nanosheet (NW/NS) GAA devices still face many challenges, such as a high-quality stacked SiGe/Si fin structure preparation, high selectively SiGe NW/NS release, inner spacer, source/drain (S/D) epitaxial process, etc. [11–15]. These processes are critical for the preparation of

Integrated Circuit Advanced Process Center, Institute of Microelectronics, University of Chinese Academy of Sciences, Beijing 100029, China; chengxiaohong@ime.ac.cn (X.C.); zhaofei@ime.ac.cn (F.Z.); chenanlan@ime.ac.cn (A.C.); liuhaoyan@ime.ac.cn (H.L.); lichun@ime.ac.cn (C.L.); zhangqingzhu@ime.ac.cn (Q.Z.); yinhuaxiang@ime.ac.cn (H.Y.); luojun@ime.ac.cn (J.L.); wangwenwu@ime.ac.cn (W.W.)

the stacked SiGe channel NW/NS device. Prior to this work, there are several reports on the preparation of SiGe/Si fin in terms of the epitaxial growth and dry etching process of stacked SiGe/Si [11,12,16,17]. In addition, the releasing technologies of SiGe nanowire by highly selective removal of Si have been investigated in the last years using the dry etching with CF4-based plasma [18], in situ HCl gaseous thermal etching [19] and wet chemical etching [13,20]. However, the former two methods are normally conducted using specific tools to avoid damages or selectivity issues. Meanwhile, wet chemical etching is an easier strategy since it can achieve a high selective etching only by choosing an appropriate alkaline solution and optimizing its temperature. Moreover, the wet chemical etching can be implemented in a common wet bench or spin on single wafer tool. Recently, a new alkaline solution, ACT@SG-201, was proposed to remove Si sacrificial layer and inhibit the loss of SiGe layer [21]. Therefore, for a 4-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NW GAA device, a high crystalline quality epitaxial growth and vertical dry etching of stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si multilayer and a high selective release of stacked SiGe channels need to be further studied, as only a few studies have been reported so far.

In this paper, a 4-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA p-MOS device is demonstrated by developing the fabrication process of a high-quality stacked  $Si_{0.7}Ge_{0.3}/Si$ fin and developing the releasing process of the stacked  $Si_{0.7}Ge_{0.3}$  channels. Furthermore, its driven current can be further enhanced by introducing a process of nickel-based silicide at S/D regions.

#### 2. Materials and Methods

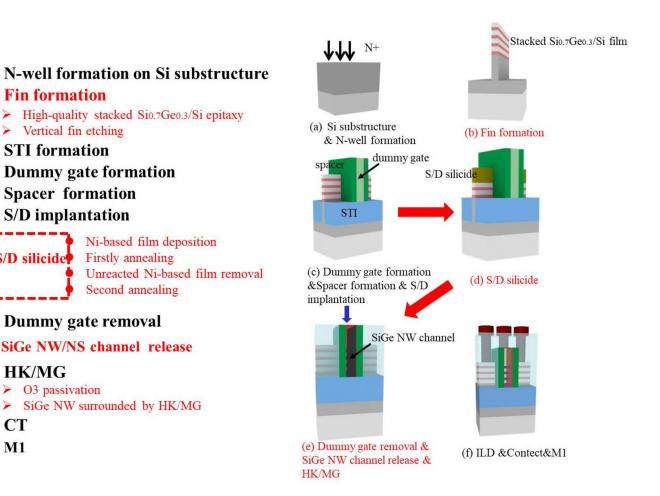

The process flow that was used for the fabrication of the stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA p-MOS transistor is illustrated in Figure 1. After the n-Well formation (Figure 1a), a vertical stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin was fabricated by developing a high-quality epitaxial growth and anisotropic dry etching process used the HBr-based plasma under the sidewall image transfer technique (Figure 1b). After that, the shallow trench isolation (STI), dummy gate and spacers were defined, and *p*-type BF<sub>2</sub> ions were implanted in Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fins to form S/D regions (Figure 1c). In addition, some samples employed a self-aligned S/D nickel-based silicide process [22,23] (Figure 1d). The stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs were subsequently released in the replacement metal gate (RMG) module by using an optimized ACT@SG-201 solution for the selective removal of Si sacrificial layers. Additionally, the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> bi-layer high-k (HK) dielectric and TiN-based/W metal gate (MG) stack were used as the HK/MG stack (Figure 1e). Finally, the four terminals were formed by the normal contact and metal connections process (Figure 1f).

The film quality and device structure were observed using high-resolution transmission electron microscopy (HRTEM) and the high angle annular dark field scanning transmission electron microscope (HAADF-STEM). The fin etch and selective etch profiles were performed by scanning electron microscopes (SEM). The Energy-dispersive X-ray spectroscopy (EDX) mapping analysis was employed to verify elements of the final stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device. The electrical characterization was performed using a Keithley 4200 semiconductor parameter analyzer. S/D silicide

HK/MG

CT **M1**

Figure 1. The process flow of stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA p-MOS device. (a) Si substructure & N-well formation; (b) fin formation; (c) dummy gate formation & spacer formation & S/D implantaton; (d) S/D formation; (e) dummy gate removal & SiGe NW channel release & HK/MG; (f) ILD & Contect & M1.

## 3. Results and Discussion

# 3.1. High-Quality Stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si Fin Formation

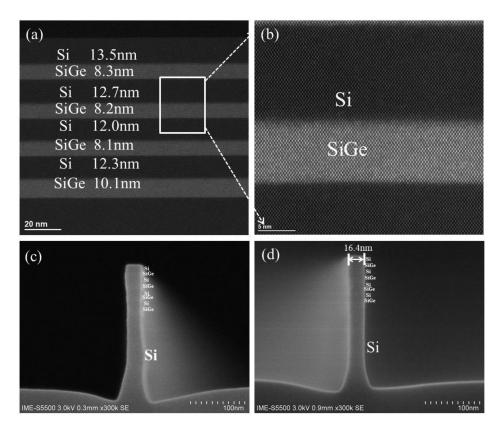

A vertical stacked  $Si_{0.7}Ge_{0.3}/Si$  fin with a high crystalline quality is one of key factors for the fabrication of a stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si NWs GAA device. As shown in Figure 2a,b, a high-quality epitaxial growth of stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si multilayer was verified using the HRTEM and HAADF-STEM analysis. No threading dislocation defects, as well as distinct and sharp interfaces between the Si<sub>0.7</sub>Ge<sub>0.3</sub> and Si, can be found. Meanwhile, the thickness of  $Si_{0.7}Ge_{0.3}$  from top to bottom is 8.3, 8.2, 8.1 and 10.1 nm under the same time of epitaxial growth. In other words, the thickness of bottom  $Si_{0.7}Ge_{0.3}$  is ~2 nm thicker than that of others. It is known that the epitaxial rate is strongly dependent on the crystallization of the under-layer, that is, the epitaxial rate might be decreased if multi-crystallization occurs in the under-layer [9]. At the same time, the thickness of Si is measured as 13.5, 12.7, 12.0 and 12.3 nm from top to bottom for the better release of  $Si_{0.7}Ge_{0.3}$  NW channel. Moreover, it can be seen that the thickness of top Si is ~1 nm thicker than that of others. Its purpose is to increase the process window for the following poly and spacer etching process.

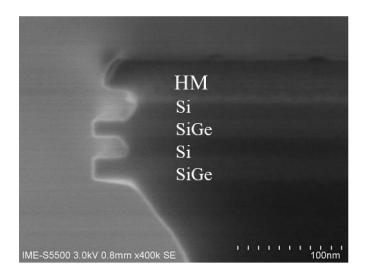

**Figure 2.** (a) HRTEM images of stacked  $Si_{0.7}Ge_{0.3}/Si$  multilayer; (b) its magnified images at the  $Si_{0.7}Ge_{0.3}/Si$  interfaces. (c) Four-period stacked SiGe/Si fin profile with HBr/O<sub>2</sub>/He plasma under bias voltage of -90 V, (d) under bias voltage of -100 V.

To get a uniform stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NW channel length and excellent gate control, a vertical profile of stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin is a critical process. Based on previous etching results of the SiGe fin and two period stacked SiGe/Si fin [11,17], the HBr/O<sub>2</sub>/He plasma was applied for four-period-stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin, as shown in Figure 2c. It is found that a not very vertical profile of stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin etching was fine-tuned from -90 V to -100 V. A vertical four-period stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin structure was attained by increasing ions bombarding, as shown in Figure 2d.

#### 3.2. Si<sub>0.7</sub>Ge<sub>0.3</sub> NW Channel Release

For a selective removal of Si to  $Si_{0.7}Ge_{0.3}$ , the wet etching approach using an alkaline solution is still a better choice. For example, the conventional TMAH solution, after the co-optimization of concentration and temperature, can be chosen to selectively remove the Si to  $Si_{0.7}Ge_{0.3}$  with a selectivity of ~17.3 [13]. To further enhance the selectivity of the wet etching process, a novel ACT@SG-201 solution is employed to verify the release process of four-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NW channel. This novel solution has effective Si surface modifier and SiGe corrosion inhibitor to achieve a relatively high selectivity [21].

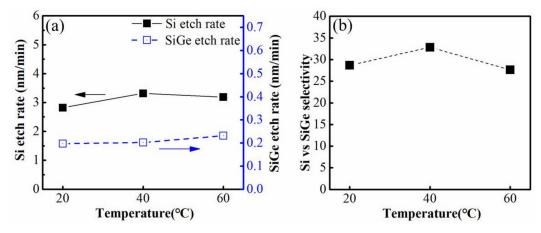

Firstly, the effect of temperature on the etching characteristics was verified for the ACT@SG-201. Figure 3a,b present the etching rates of Si, Si<sub>0.7</sub>Ge<sub>0.3</sub> and selectivity of Si to Si<sub>0.7</sub>Ge<sub>0.3</sub> under ACT@SG-201 solution at temperatures of 20 °C, 40 °C and 60 °C. The lateral etching rate of Si is calculated based on the tunnel depth divided by immersion time. Additionally, the vertical etching rate of Si<sub>0.7</sub>Ge<sub>0.3</sub> is calculated based on the thickness loss of Si<sub>0.7</sub>Ge<sub>0.3</sub> per side at the edge position divided by immersion time [13]. It can be found that the vertical etching rate of Si<sub>0.7</sub>Ge<sub>0.3</sub> layers increase with the increase of temperature, but the lateral etching rate of Si layers increases first and then decrease with the increase of temperature. Therefore, the selectivity of Si to Si<sub>0.7</sub>Ge<sub>0.3</sub> increases from 28.67 to 32.84

as the temperature of ACT@SG-201 solution increase from 20 to 40 °C and then decrease to 27.76 as the temperatures of ACT@SG-201 solution further increase to 60 °C. It can be concluded that ACT@SG-201 at 40 °C is the optimal temperature for the selective removal of Si to  $Si_{0.7}Ge_{0.3}$ .

**Figure 3.** (a) The lateral etching rate of Si and the vertical etching rate of Si<sub>0.7</sub>Ge<sub>0.3</sub>, (b) the etching selectivity of Si to Si<sub>0.7</sub>Ge<sub>0.3</sub> under ACT@SG-201 at different temperature.

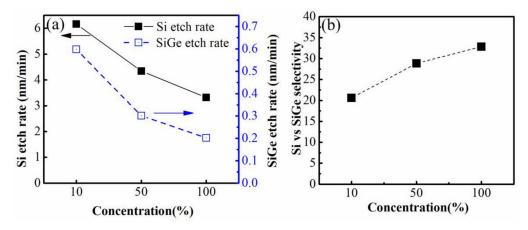

At the same time, the etching rate of Si,  $Si_{0.7}Ge_{0.3}$  and selectivity of Si to  $Si_{0.7}Ge_{0.3}$  with different concentration of ACT@SG-201 solution at 40 °C are presented in Figure 4a,b. As we can see that the etching rate of Si and  $Si_{0.7}Ge_{0.3}$  are decreasing with the increasing of the concentration of ACT@SG-201. However, the selectivity of Si to  $Si_{0.7}Ge_{0.3}$  increase from 20.67 to 32.84 because the etching rate of  $Si_{0.7}Ge_{0.3}$  decreases more than that of Si. Based on the above results, the ACT@SG-201 without any dilution at the temperature of 40 °C is chosen as the optimal etching solution for the selective etching of Si to  $Si_{0.7}Ge_{0.3}$ .

**Figure 4.** (a) The lateral etching rate of Si and the vertical etching rate of  $Si_{0.7}Ge_{0.3}$ , (b) the etching selectivity of Si to  $Si_{0.7}Ge_{0.3}$  under different concentration of ACT@ SG-201 at 40 °C.

Moreover, the selective etching profile of two periods  $Si_{0.7}Ge_{0.3}/Si$  multilayer by using the optimal ACT@SG-201 at 40 °C is presented in Figure 5. The  $Si_{0.7}Ge_{0.3}$  layers extremities are "rectangular" without significant  $Si_{0.7}Ge_{0.3}$  loss after etching for 10 min at 40 °C due to its high selectivity. This result further confirms that ACT@SG-201 without any dilution at the temperature of 40 °C is the optimal condition due to its high selectivity.

**Figure 5.** The SEM image of the selective etching of the  $Si_{0.7}Ge_{0.3}/Si$  multilayers stack utilizing the optimal ACT@ SG-201 solution at 40 °C for 10 min.

# 3.3. 4-Levels Vertically Stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NW GAA Device

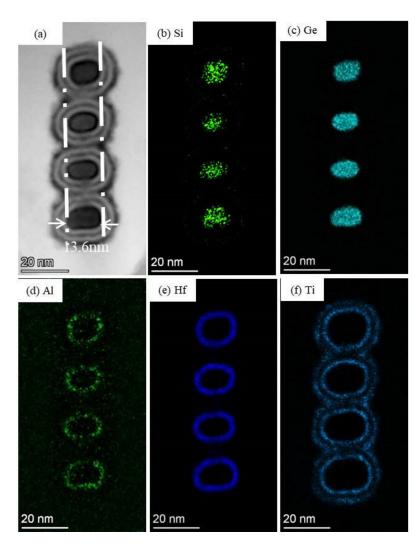

Based on above newly developed fabrication process of high-quality stacked Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin, and release process of  $Si_{0.7}Ge_{0.3}$  NW channel, a four-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA device is prepared successfully. Figure 6 shows the cross-sectional image of the  $Si_{0.7}Ge_{0.3}$  NW channels area under the HK/MG stack at the end of fabrication processing. It can be found that vertical and uniform four-levels stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> channels with almost the same width (~13.6 nm) were achieved. This result indicates that our newly developed fin formation and NWs release process are effective for the fabrication of vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device. In addition, the EDX mapping results of the four-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device under the HK/MG stack at the end of the fabrication processing are shown in Figure 6b–f. From Figure 6b,c, it can be seen that uniform Ge and Si elements are distributed in the channel area. Namely, the stacked channels are Si<sub>0.7</sub>Ge<sub>0.3</sub> layers and the Si sacrificial layers have been completely removed. These results further confirmed that our newly developed fin formation and NWs release process are effective for the fabrication of vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NW GAA device. Meanwhile, the stacked  $Si_{0.7}Ge_{0.3}$  NW channels were well surrounded by the ALD HK/MG stacks to form a GAA structure, as shown in Figure 6d–f, which could provide an excellent gate control ability for the four-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NW GAA device.

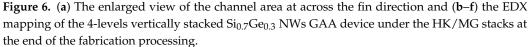

The typical I<sub>DS</sub>-V<sub>GS</sub>, g<sub>m</sub>-V<sub>GS</sub> and I<sub>DS</sub>-V<sub>DS</sub> characteristics of the four-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device are shown in Figure 7a–c, respectively. An excellent subtreshold slope (SS) of ~77 mV/dec, low drain induced barrier-lowering (DIBL) of ~19 mV/V, high I<sub>on</sub>/I<sub>off</sub> ratio of ~9 × 10<sup>5</sup> and the maximum of transconductance (g<sub>m,max</sub>) of ~83.35  $\mu$ S/ $\mu$ m were demonstrated using the above newly developed process. In particular, its excellent SS performance indicates that a good electrostatic control is obtained for the 4-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device. However, its driven current (I<sub>on</sub>) was only ~38.6  $\mu$ A/ $\mu$ m under V<sub>DS</sub> = V<sub>GS</sub> = -0.8 V due to its large resistance of source and drain (R<sub>SD</sub>). According to the I<sub>DS</sub>-V<sub>DS</sub> curves of different device widths at liner region, it can be calculated that the value of R<sub>SD</sub> can reach 9.2 × 10<sup>5</sup>  $\Omega$ . This is because the direct connect was formed between contact and Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si fin at S/D area without epitaxial or silicide process.

**Figure 7.** (a)  $I_{DS}$ - $V_{GS}$ , (b)  $g_m$ - $V_{GS}$  and (c)  $I_{DS}$ - $V_{DS}$  characteristics of the four-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device.

## 3.4. Electrial Perforemance Optimization

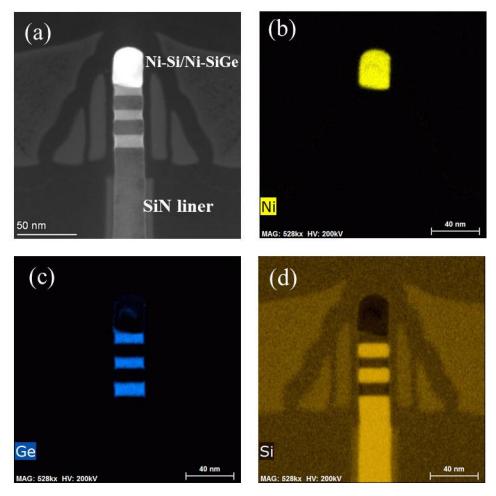

To further improve the drive current and reduce the  $R_{SD}$ , a S/D silicide process is proposed to fabricate the four-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA device. The HAADF-STEM and EDX mapping analysis were employed to check the S/D region of the four-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA device. The results are shown in Figure 8a–d. It is found that the top first period and partial second period  $Si_{0.7}Ge_{0.3}/Si$  fin at S/D area have been silicified with a uniform and smooth interface. Meanwhile, the EDX mapping results, as shown in Figure 8b–d, proved that the uniform Ni-Si or Ni-SiGe silicide was formed on the top of the  $Si_{0.7}Ge_{0.3}/Si$  fin at S/D area.

**Figure 8.** (a) The cross–sectional images of S/D region of 4-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA device at perpendicular to fin direction and its EDX mapping of Ni (b), Ge (c), and Si element (d) distribution.

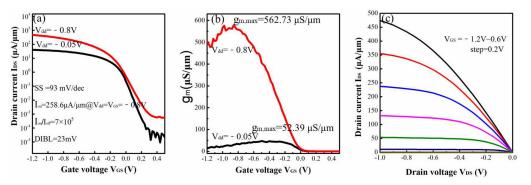

The I<sub>DS</sub>-V<sub>GS</sub>, g<sub>m</sub>-V<sub>GS</sub> and I<sub>DS</sub>-V<sub>DS</sub> characteristics of 4-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device with S/D silicide process are shown in Figure 9a–c, respectively. Compared with device without S/D silicide process, the I<sub>on</sub> can increase from 38.6 to ~258.6  $\mu$ A/ $\mu$ m (about 6.7 times), as well as the g<sub>m,max</sub> can increase from 83.35 to 562.73  $\mu$ S/ $\mu$ m (about 6.7 times), because its R<sub>SD</sub> can reduce from 9.2 × 10<sup>5</sup> to 6.4 × 10<sup>4</sup>  $\Omega$  by employing the S/D silicide process. These results verified that the S/D silicide process can improve the I<sub>on</sub> of the 4-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NW GAA device by reducing its R<sub>SD</sub>.

**Figure 9.** The (a)  $I_{DS}$ - $V_{GS}$ , (b)  $g_m$ - $V_{GS}$  (c)  $I_{DS}$ - $V_{DS}$  characteristics of 4-levels vertically stacked Si<sub>0.7</sub>Ge<sub>0.3</sub> NWs GAA device with S/D silicide process.

To check if this process has other side effects, the key electrical parameters of devices with or without S/D silicide are compared in detail. The results are summarized in Table 1. Although its I<sub>on</sub>, g<sub>m,max</sub> and R<sub>SD</sub> had obviously improvement, its other parameters, such as SS, DIBL, leakage (I<sub>off</sub>) and I<sub>on</sub>/I<sub>off</sub> ratio were slightly worse. For example, the leakage increased from  $4.22 \times 10^{-5}$  to  $3.71 \times 10^{-4} \,\mu\text{A}/\mu\text{m}$ , SS increased from 77 to 93 mV/dec, and its I<sub>on</sub>/I<sub>off</sub> ratio decreased from  $9 \times 10^5$  to  $7 \times 10^5$ . We believe that the slight deterioration of SS and I<sub>on</sub>/I<sub>off</sub> ratio is caused by the increase of I<sub>off</sub>. Its leakage performance needs to be further improved through the co-optimization of S/D implantation and silicide process in the future.

**Table 1.** The comparison of electrical characteristic parameters for the 4-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA devices with or without S/D silicide process.

| Samples                    | I <sub>on</sub> (μA/μm) | SS (mV/dec) | gm,max<br>(μS/μm) | DIBL<br>(mV/V) | I <sub>off</sub> (μA/μm)                  | I <sub>on</sub> /I <sub>off</sub>                     | R <sub>SD</sub> (Ω)                                         |

|----------------------------|-------------------------|-------------|-------------------|----------------|-------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|

| W/o silicide<br>W/silicide | 38.6<br>258.6           | 77<br>93    | 83.85<br>562.73   | 19<br>23       | $4.22 	imes 10^{-5} \ 3.71 	imes 10^{-4}$ | $\begin{array}{l}9\times10^5\\7\times10^5\end{array}$ | $\begin{array}{c} 9.2\times10^5\\ 6.4\times10^4\end{array}$ |

# 4. Conclusions

In a summary, a four-levels vertically stacked  $Si_{0.7}Ge_{0.3}$  NWs GAA device is successfully fabricated by developing a high-quality epitaxial growth and vertical fin etch of stacked SiGe/Si multilayer, and introducing the channel release process of stacked  $Si_{0.7}Ge_{0.3}$  NWs under the optimal ACT@SG-201 solution. Meanwhile, the Ni-based silicide process is also implemented to improve its driven current by decreasing the R<sub>SD</sub>. Moreover, its slightly poor leakage performance needs to be further improved through the co-optimization of S/D implantation and silicide process in the future.

**Author Contributions:** Methodology, Y.L. and Q.Z.; investigation, X.C., H.L., C.L. and Y.L.; data curation, X.C., F.Z. and A.C.; writing—original draft preparation, X.C. and Y.L.; writing—review and editing, H.Y., J.L. and W.W.; project administration, Y.L.; funding acquisition, Y.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work is supported in part by the Science and technology program of Beijing Municipal Science and Technology Commission (Grant no. Z201100004220001), in part by the CAS Pioneer Hundred Talents Program (Grant no. NA), in part by Beijing Municipal Natural Science Foundation (Grant no. 4202078).

Data Availability Statement: Not applicable.

Acknowledgments: We thank the Integrated Circuit Advanced Process Center (ICAC) at the Institute of Microelectronics of the Chinese Academy of Sciences for the devices fabricated on their advanced 200 mm CMOS platform.

Conflicts of Interest: The authors declare no conflict of interest.

# References

- Fang, W.W.; Singh, N.; Bera, L.K.; Nguyen, H.S.; Rustagi, S.C.; Lo, G.Q.; Balasubramanian, N.; Kwong, D. Vertically Stacked SiGe Nanowire Array Channel CMOS Transistors. *IEEE Electron. Device Lett.* 2007, 28, 211–213. [CrossRef]

- Veloso, A.; Eneman, G.; Huynh-Bao, T.; Chasin, A.; Simoen, E.; Vecchio, E.; Devriendt, K.; Brus, S.; Rosseel, E.; Hikavyy, A.; et al. Vertical Nanowire and Nanosheet FETs: Device Features, Novel Schemes for Improved Process Control and Enhanced Mobility, Potential for Faster & More Energy Efficient Circuits. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 11.1.1–11.1.4.

- 3. Bender, H.; Bosch, E.G.T.; Richard, O.; Mendez, D.; Favia, P.; Lazić, I. 3D characterization of nanowire devices with STEM based modes. *Semicond. Sci. Technol.* **2019**, *34*, 114001. [CrossRef]

- 4. Liu, X.-Y.; Hao, J.-L.; You, N.-N.; Bai, Y.; Tang, Y.-D.; Yang, C.-Y.; Wang, S.-K. High-mobility SiC MOSFET with low density of interface traps using high pressure microwave plasma oxidation. *Chin. Phys. B* **2020**, *29*, 037301. [CrossRef]

- 5. Pavlidis, G.; Hilton, A.M.; Brown, J.L.; Heller, E.R.; Graham, S. Monitoring the Joule heating profile of GaN/SiC high electron mobility transistors via cross-sectional thermal imaging. *J. Appl. Phys.* **2020**, *128*, 075705. [CrossRef]

- Akarvardar, K.; Wang, M.; Bao, R.; Burns, S.; Chan, V.; Cheng, K.; Demarest, J.; Fronheiser, J.; Hashemi, P.; Kelly, J.; et al. FINFET Technology Featuring High Mobility SiGe Channel for 10 nm and Beyond. In Proceedings of the IEEE Symposium on VLSI Technology (VLSI), Honolulu, HI, USA, 13–16 January 2016.

- Ando, T.; Hashemi, P.; Bruley, J.; Rozen, J.; Ogawa, Y.; Koswatta, S.; Chan, K.K.; Cartier, E.A.; Mo, R.; Narayanan, V. High Mobility High-Ge-Content SiGe PMOSFETs Using Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> Stacks with In-Situ O<sub>3</sub> Treatment. *IEEE Electron. Device Lett.* 2017, 38, 303–305. [CrossRef]

- 8. Franco, J.; Kaczer, B.; Roussel, P.J.; Mitard, J.; Cho, M.; Witters, L.; Grasser, T.; Groeseneken, G. SiGe channel technology: Superior reliability toward ultrathin EOT devices—Part I: NBTI. *IEEE Trans. Electron. Devices* **2013**, *60*, 396. [CrossRef]

- 9. Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Zan, Y.; Li, J.; Zhang, Q.; Wu, Z.; Luo, J.; Wang, W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. *Nanomaterials* **2021**, *11*, 1689. [CrossRef] [PubMed]

- Lee, C.H.; Southwick, R.G.; Mochizuki, S.; Li, J.; Miao, X.; Wang, M.; Bao, R.; Ok, I.; Ando, T.; Hashemi, P.; et al. Toward High Performance SiGe Channel CMOS: Design of High Electron Mobility in SiGe nFinFETs Outperforming Si. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.1.1–35.1.4.

- 11. Li, Y.; Cheng, X.; Zhong, Z.; Zhang, Q.; Wang, G.; Li, Y.; Li, J.; Ma, X.; Wang, X.; Yang, H.; et al. Key Process Technologies for Stacked Double Si<sub>0.7</sub>Ge<sub>0.3</sub> Channel Nanowires Fabrication. *ECS J. Solid State Sci. Technol.* **2020**, *9*, 064009. [CrossRef]

- 12. Wieser, U.; Iamundo, D.; Kunze, U.; Hackbarth, T.; König, U. Nanoscale patterning of Si/SiGe heterostructures by electron-beam lithography and selective wet-chemical etching. *Semicond. Sci. Technol.* **2000**, *15*, 862–867. [CrossRef]

- 13. Cheng, X.; Li, Y.; Liu, H.; Zan, Y.; Lu, Y.; Zhang, Q.; Li, J.; Du, A.; Wu, Z.; Luo, J.; et al. Selective wet etching in fabricating SiGe nanowires with TMAH solution for gate-all-around MOSFETs. *J. Mater. Sci. Mater. Electron.* **2020**, *31*, 22478–22486. [CrossRef]

- Barraud, S.; Lapras, V.; Samson, M.P.; Gaben, L.; Grenouillet, L.; Maffini-Alvaro, V.; Morand, Y.; Daranlot, J.; Rambal, N.; Previtalli, B.; et al. Vertically stacked-NanoWires MOSFETs in a replacement metal gate process with inner spacer and SiGe source/drain. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 17.6.1–17.6.4.

- 15. Hikavyy, A.; Vanherle, W.; Witters, L.; Vincent, B.; Dekoster, J.; Loo, R. High Ge Content SiGe Selective Processes for Source/Drain in Manufacturing the Next Generations of pMOS Transistors. *ECS J. Solid State Sci. Technol.* **2013**, *2*, 282–286. [CrossRef]

- 16. Zhao, Z.; Cheng, X.; Li, Y.; Zan, Y.; Liu, H.; Wang, G.; Du, A.; Li, J.; Zhang, Q.; Xu, G.; et al. Investigation on the formation technique of SiGe Fin for the high mobility channel FinFET device. *J. Mater. Sci. Mater. Electron.* **2019**, *31*, 5854–5860. [CrossRef]

- 17. Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Wang, W. Integration of Si<sub>0.7</sub>Ge<sub>0.3</sub> fin onto a bulk-Si substrate and its P-type FinFET device fabrication. *Semicond. Sci. Technol.* **2021**, *36*, 125001. [CrossRef]

- Ahles, C.F.; Choi, J.Y.; Wolf, S.; Kummel, A.C. Selective Etching of Silicon in Preference to Germanium and Si<sub>0.5</sub>Ge<sub>0.5</sub>. ACS Appl. Mater. Interfaces 2017, 9, 20947–20954. [CrossRef] [PubMed]

- Bidal, G.; Loubet, N.; Fenouillet-Beranger, C.; Denorme, S.; Perreau, P.; Fleury, D.; Clement, L.; Laviron, C.; Leverd, F.; Gouraud, P.; et al. Folded fully depleted FET using Silicon-On-Nothing technology as a highly W-scaled planar solution. *Solid-State Electron.* 2009, 53, 735–740. [CrossRef]

- Liu, H.; Li, Y.; Cheng, X.; Zan, Y.; Lu, Y.; Wang, G.; Li, J.; Kong, Z.; Ma, X.; Wang, X.; et al. Fabrication and selective wet etching of Si<sub>0.2</sub>Ge<sub>0.8</sub>/Ge multilayer for Si<sub>0.2</sub>Ge<sub>0.8</sub> channel gate-all-around MOSFETs. *Mater. Sci. Semicond. Process.* 2021, 121, 105397. [CrossRef]

- 21. Liu, W.D.; Lee, Y.C.; Sekiguchi, R.; Yoshida, Y.; Komori, K.; Wostyn, K.; Sebaai, F.; Holsteyns, F. Selective Wet Etching in Fabricating SiGe and Ge Nanowires for Gate-all-Around MOSFETs. *Solid State Phenom.* **2018**, *282*, 101–106. [CrossRef]

- 22. Demeurisse, C.; Verheyen, P.; Opsomer, K.; Vrancken, C.; Absil, P.; Lauwers, A. Thermal stability of NiPt- and Pt-silicide cotacts on SiGe source/drain. *Microelectron. Eng.* 2007, *84*, 2547–2551. [CrossRef]

- Kittl, J.A.; Lauwers, A.; Chamirian, O.; Pawlak, M.A.; Van Dal, M.; Akheyar, A.; De Potter, M.; Kottantharayil, A.; Pourtois, G.; Lindsay, R.; et al. Applications of Ni-based silicides to 45 nm CMOS and beyond. *Mater. Res. Soc. Symp. Proc.* 2004, 810, 31–42. [CrossRef]