Importance of Structural Relaxation on the Electrical Characteristics and Bias Stability of Solution-Processed ZnSnO Thin-Film Transistors

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

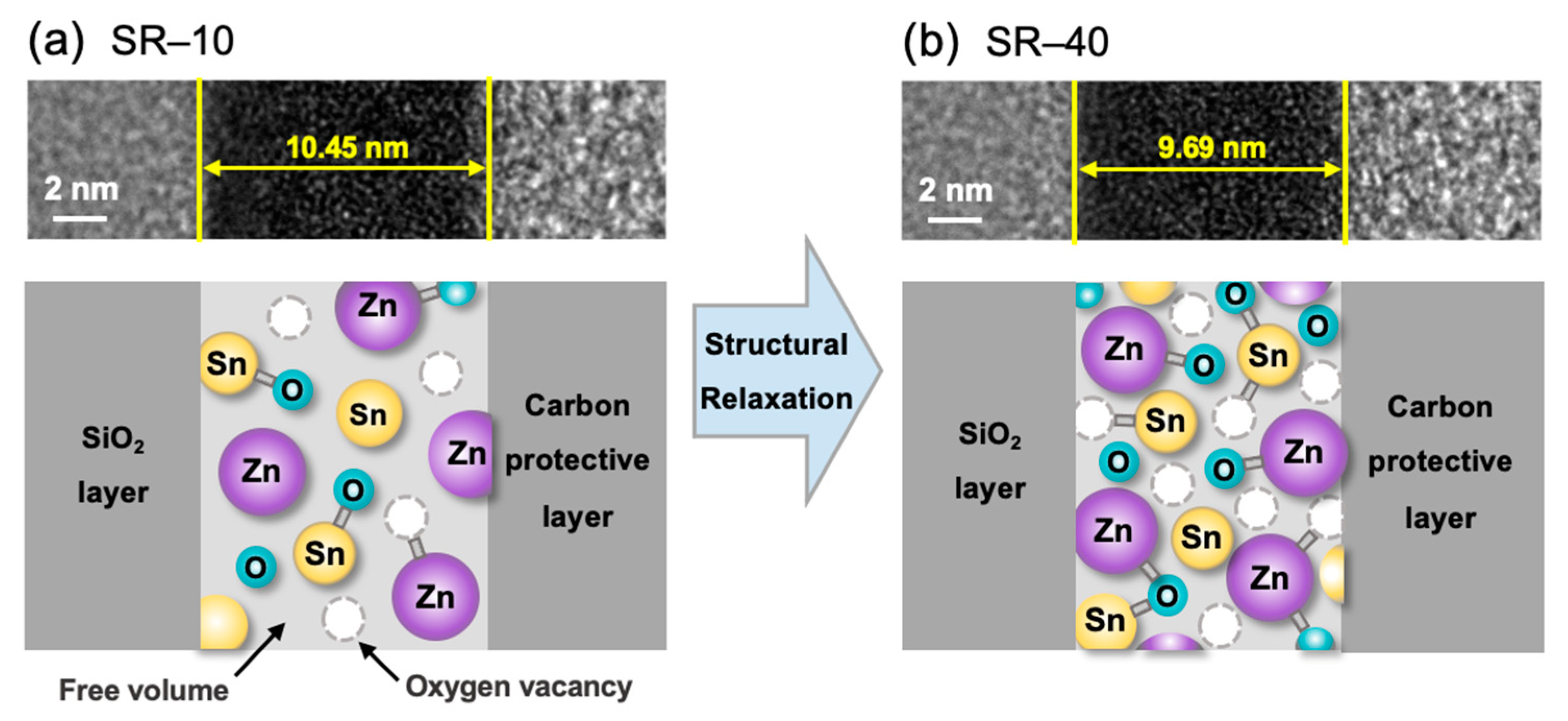

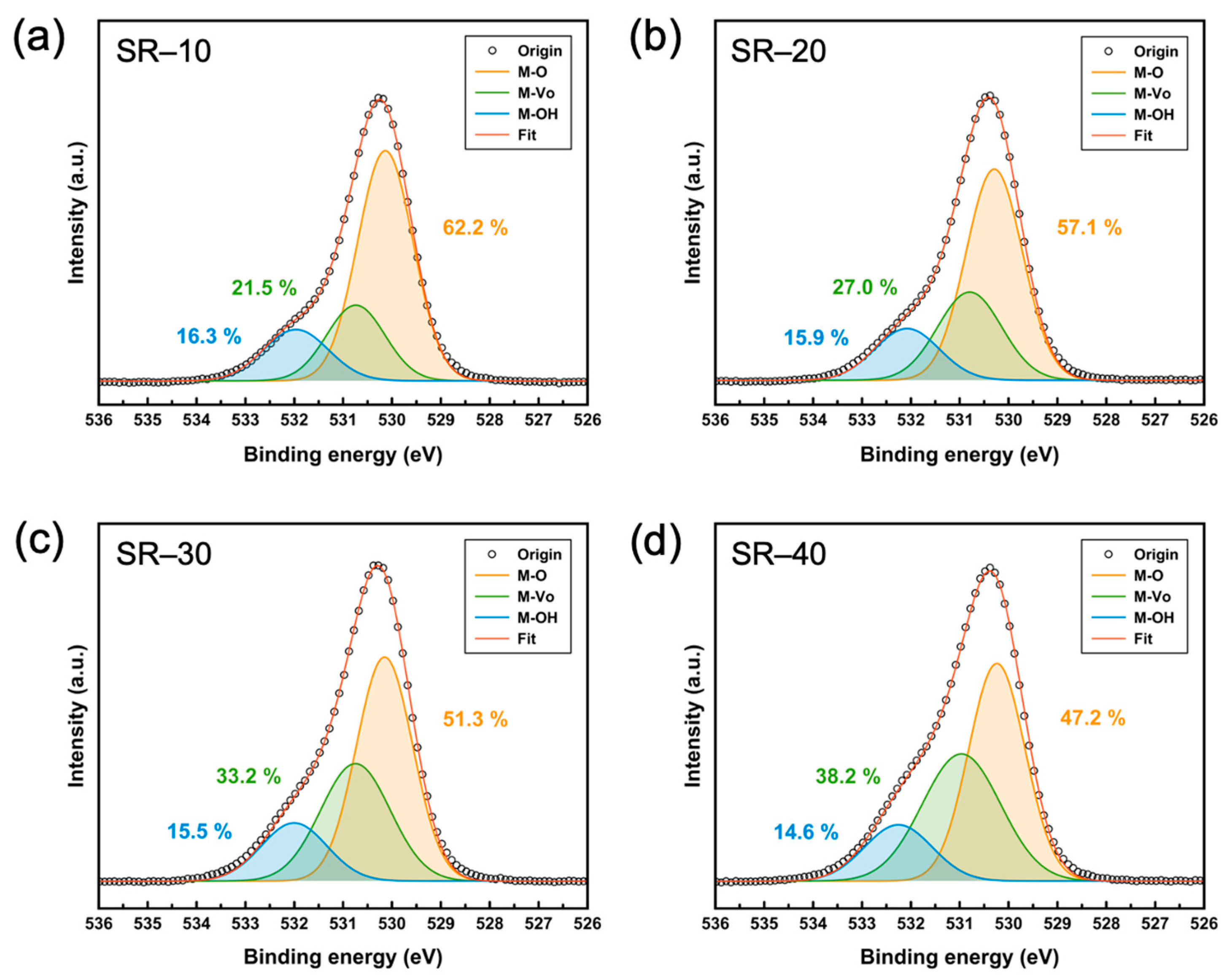

3.1. Physical and Chemical Properties of Structurally Relaxed ZTO Thin Films

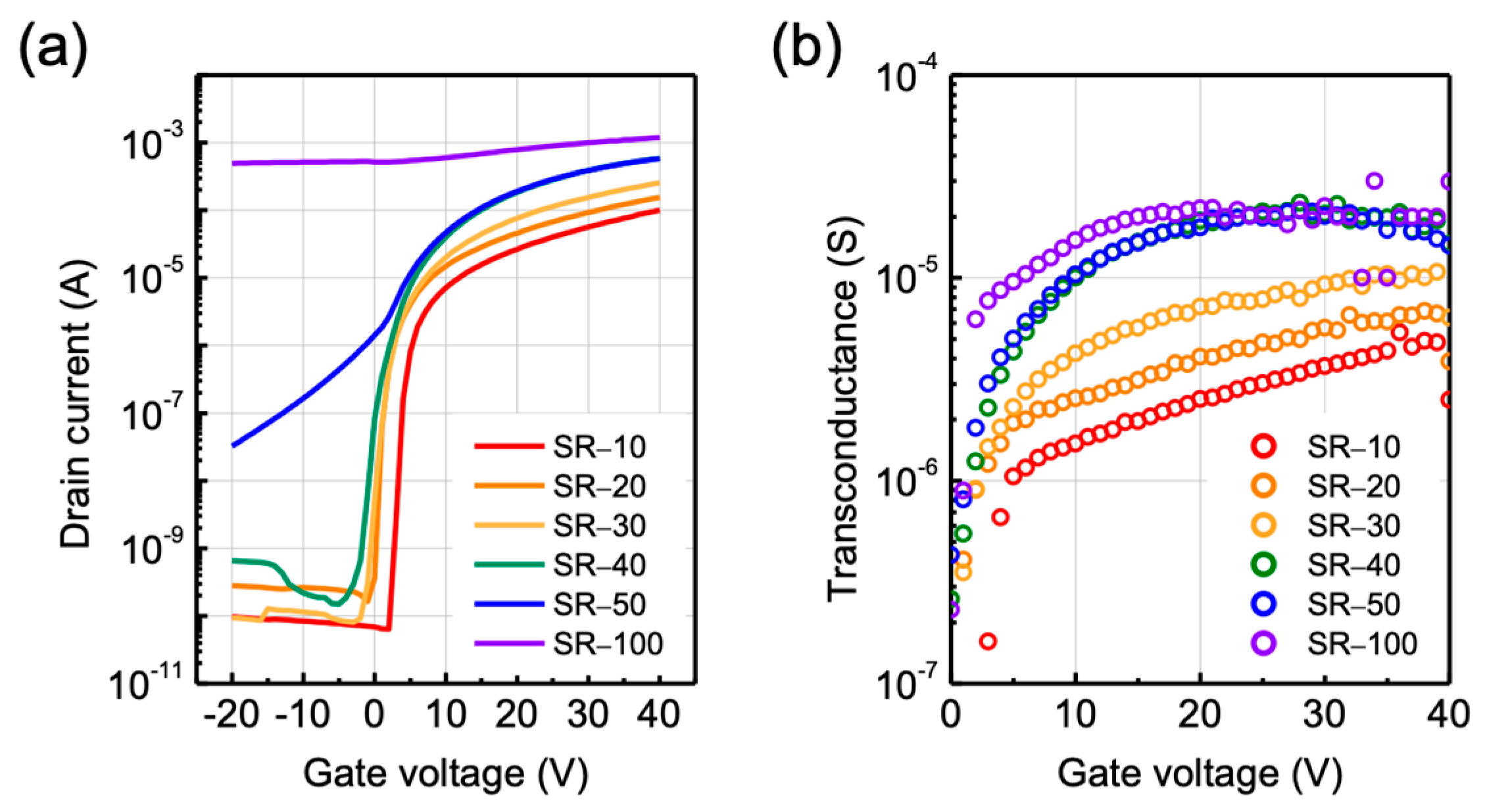

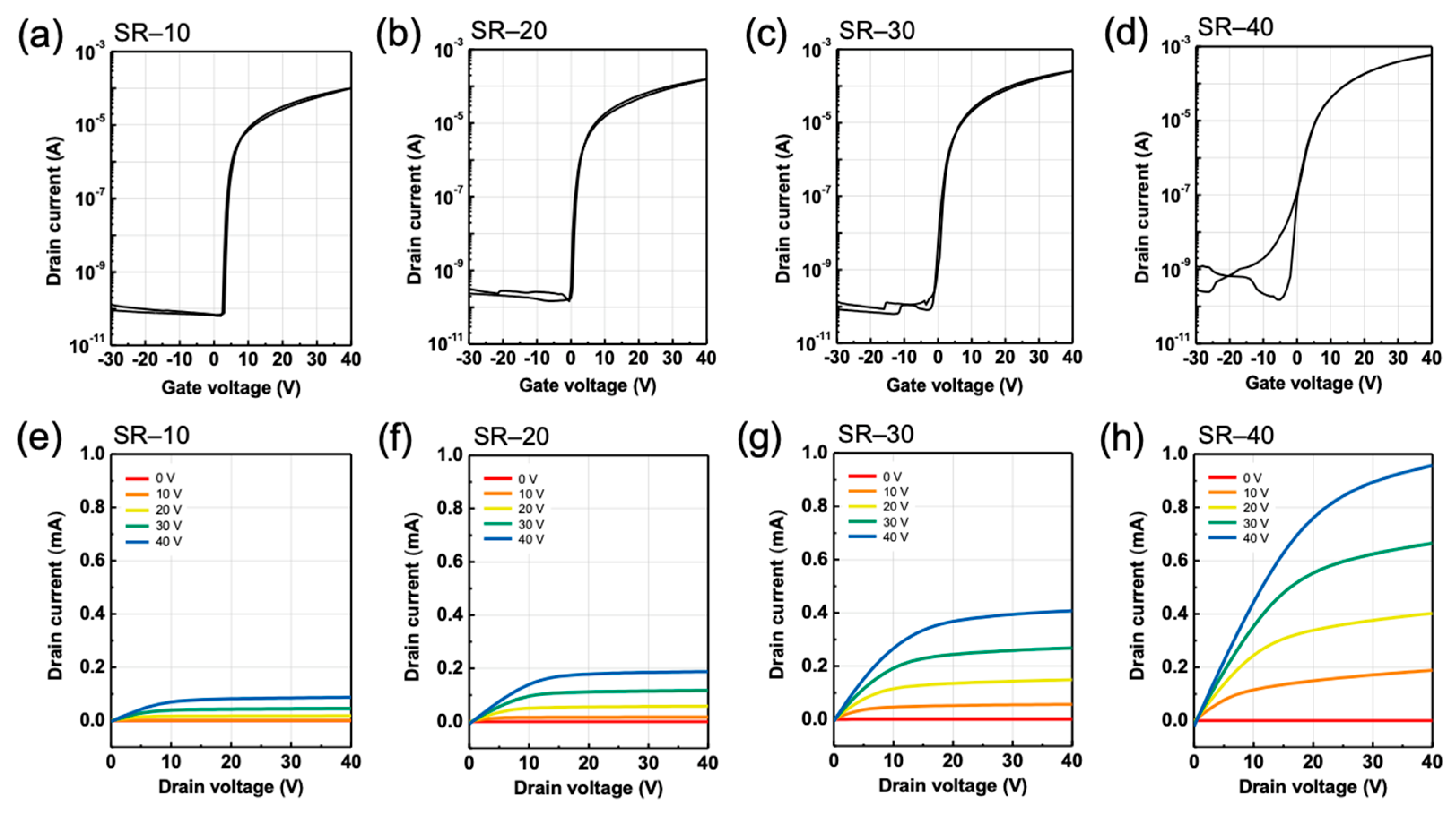

3.2. Effects of Structural Relaxation on Electrical Characteristics in ZTO TFTs

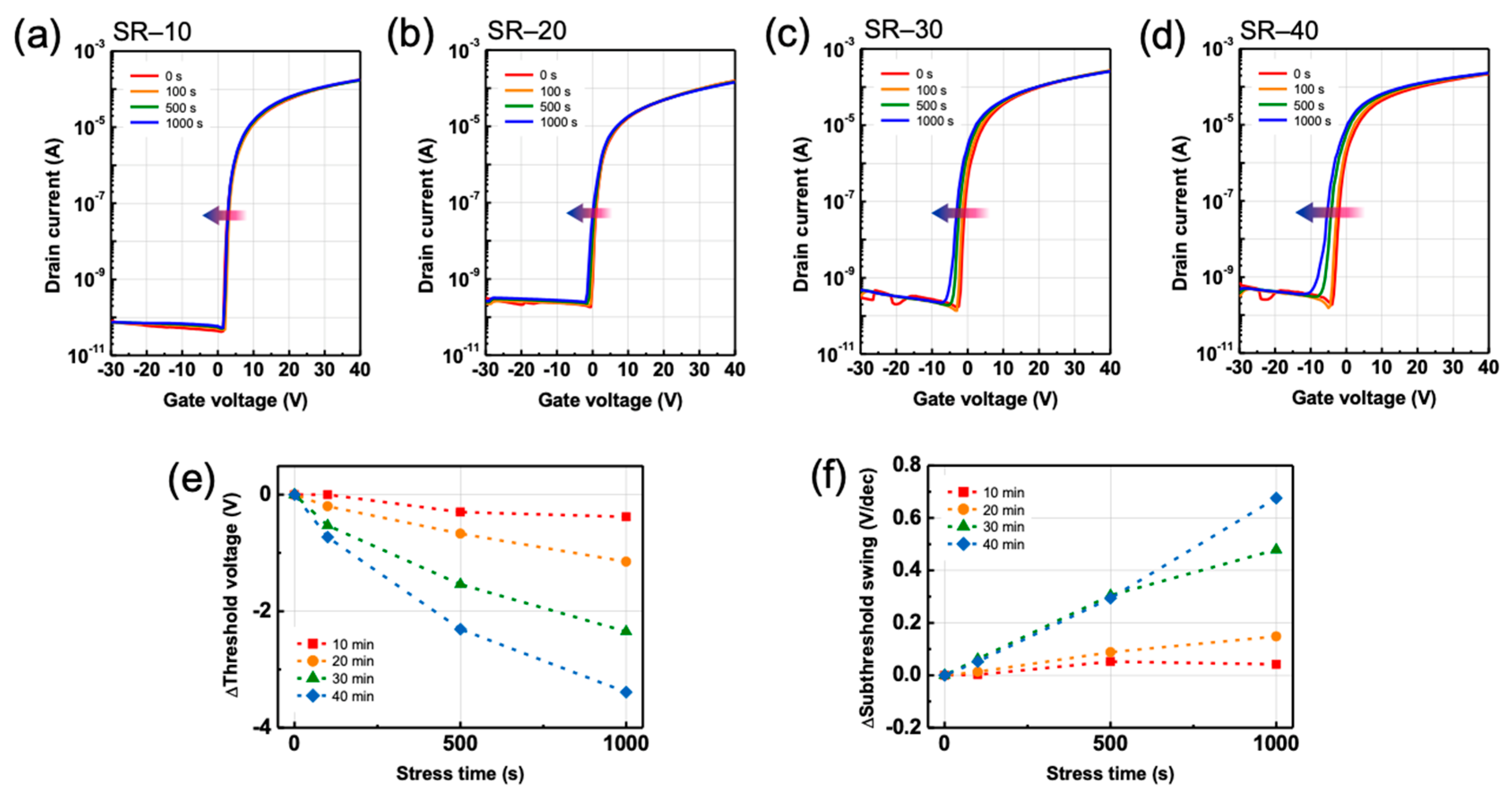

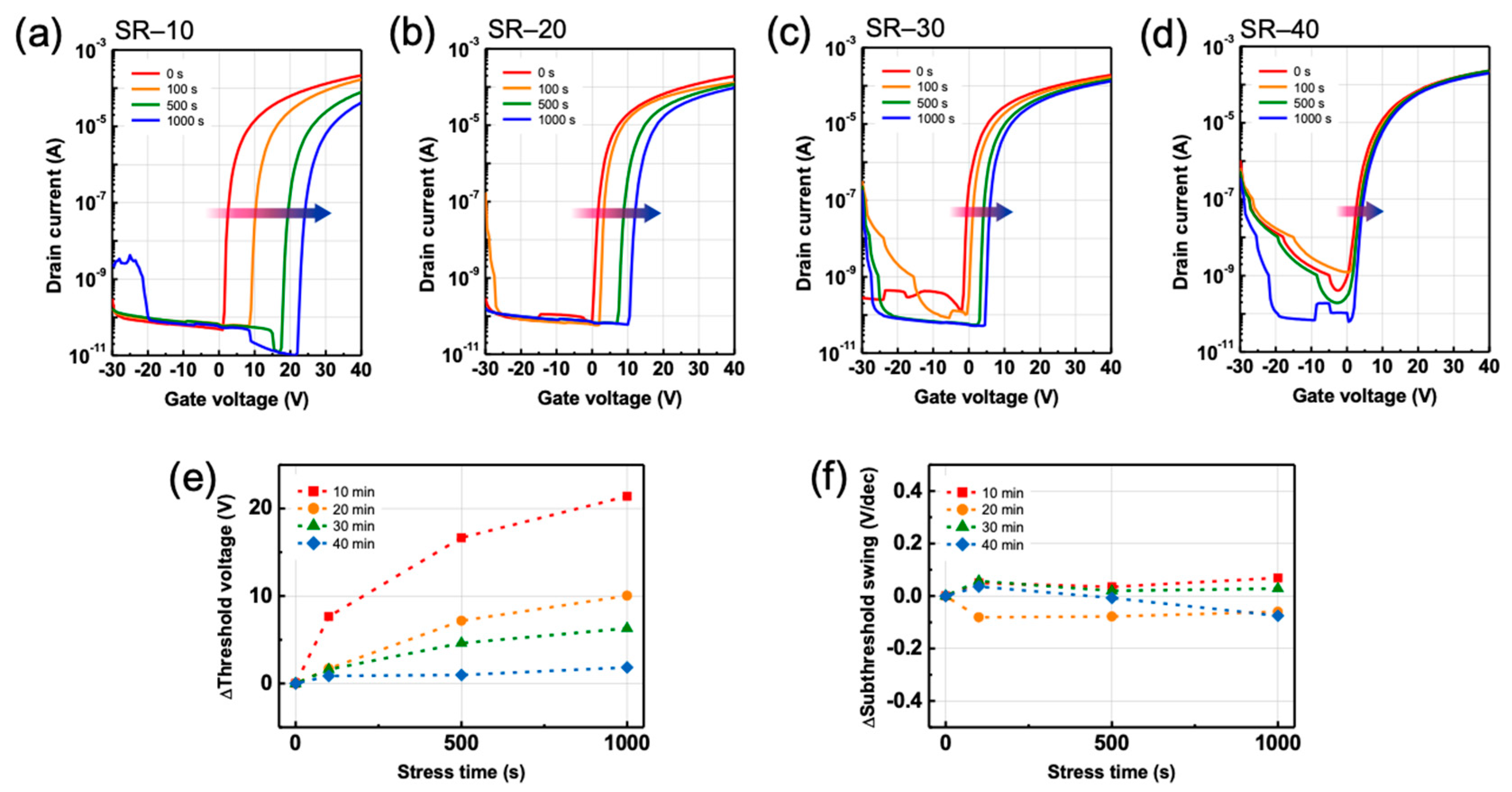

3.3. Effects of Structural Relaxation on Bias-Induced Instabilities in ZTO TFTs

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide semiconductor thin-film transistors: A review of recent advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef]

- Petti, L.; Münzenrieder, N.; Vogt, C.; Faber, H.; Büthe, L.; Cantarella, G.; Bottacchi, F.; Anthopoulos, T.D.; Tröster, G. Metal oxide semiconductor thin-film transistors for flexible electronics. Appl. Phys. Rev. 2016, 3, 021303. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Ueda, K.; Kamiya, T.; Hirano, M.; Hosono, H. Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor. Science 2003, 300, 1269–1272. [Google Scholar] [CrossRef] [PubMed]

- Thomas, S.; Pattanasattayavong, P.; Anthopoulos, T.D. Solution-processable metal oxide semiconductors for thin-film transistor applications. Chem. Soc. Rev. 2013, 42, 6910–6923. [Google Scholar] [CrossRef] [PubMed]

- Park, J.S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Film. 2012, 520, 1679–1698. [Google Scholar] [CrossRef]

- Chen, R.; Lan, L. Solution-processed metal-oxide thin-film transistors: A review of recent developments. Nanotechnology 2019, 30, 312001. [Google Scholar] [CrossRef] [PubMed]

- Ahn, B.D.; Jeon, H.-J.; Sheng, J.; Park, J.; Park, J.-S. A review on the recent developments of solution processes for oxide thin film transistors. Semicond. Sci. Technol. 2015, 30, 064001. [Google Scholar] [CrossRef]

- Kim, S.J.; Yoon, S.; Kim, H.J. Review of solution-processed oxide thin-film transistors. Jpn. J. Appl. Phys. 2014, 53, 02BA02. [Google Scholar] [CrossRef]

- Chun, J.; Tak, Y.J.; Kim, W.-G.; Park, J.W.; Kim, T.S.; Lim, J.H.; Kim, H.J. Low-temperature fabrication of solution-processed hafnium oxide gate insulator films using a thermally purified solution process. J. Mater. Chem. C 2018, 6, 4928–4935. [Google Scholar] [CrossRef]

- Jang, J.; Kitsomboonloha, R.; Swisher, S.L.; Park, E.S.; Kang, H.; Subramanian, V. Transparent high-performance thin film transistors from solution-processed SnO2/ZrO2 gel-like precursors. Adv. Mater. 2013, 25, 1042–1047. [Google Scholar] [CrossRef]

- Lim, K.-H.; Lee, J.; Huh, J.-E.; Park, J.; Lee, J.-H.; Kim, Y.S. A systematic study on effects of precursors and solvents for optimization of solution-processed oxide semiconductor thin-film transistors. J. Mater. Chem. C 2017, 5, 7768–7776. [Google Scholar] [CrossRef]

- Kim, D.-K.; Seo, K.-H.; Kwon, D.-H.; Jeon, S.-H.; Hwang, Y.-J.; Wang, Z.; Park, J.; Lee, S.-H.; Jang, J.; King, I.M.; et al. Viable strategy to minimize trap states of patterned oxide thin films for both exceptional electrical performance and uniformity in sol–gel processed transistors. Chem. Eng. J. 2022, 441, 135833. [Google Scholar] [CrossRef]

- Kim, D.J.; Kim, D.L.; Rim, Y.S.; Kim, C.H.; Jeong, W.H.; Lim, H.W.; Kim, H.J. Improved electrical performance of an oxide thin-film transistor having multistacked active layers using a solution process. ACS Appl. Mater. Interfaces 2012, 4, 4001–4005. [Google Scholar] [CrossRef] [PubMed]

- He, Z.; Chen, J.; Li, D.W. Polymer additive controlled morphology for high performance organic thin film transistors. Soft Matter 2019, 15, 5790–5803. [Google Scholar] [CrossRef] [PubMed]

- Hea, Z.; Zhang, K.A.-Y.; Bi, S. Manipulate organic crystal morphology and charge transport. Org. Electron. 2022, 103, 106448. [Google Scholar] [CrossRef]

- Lee, S.S.; Nathan, A. Localized tail state distribution in amorphous oxide transistors deduced from low temperature measurements. Appl. Phys. Lett. 2012, 101, 113502. [Google Scholar] [CrossRef]

- Zeumault, A.; Subramanian, V. Mobility Enhancement in Solution-Processed Transparent Conductive Oxide TFTs due to Electron Donation from Traps in High-k Gate Dielectrics. Adv. Funct. Mater. 2016, 26, 955–996. [Google Scholar] [CrossRef]

- Lee, C.; Lee, W.-Y.; Kim, D.W.; Kim, H.J.; Bae, J.-H.; Kang, I.-M.; Lim, D.; Kim, K.; Jang, J. Extremely bias stress stable enhancement mode sol–gel-processed SnO2 thin-film transistors with Y2O3 passivation layers. Appl. Surf. Sci. 2021, 559, 149971. [Google Scholar] [CrossRef]

- Kang, Y.; Ahn, B.D.; Song, J.H.; Mo, Y.G.; Nahm, H.-H.; Han, S.; Jeong, J.K. Hydrogen Bistability as the Origin of Photo-Bias-Thermal Instabilities in Amorphous Oxide Semiconductors. Adv. Electron. Mater. 2015, 1, 1400006. [Google Scholar] [CrossRef]

- Kim, J.-H.; Park, E.-K.; Kim, M.S.; Cho, H.J.; Lee, D.-H.; Kim, J.-H.; Khang, Y.; Park, K.C.; Kim, Y.-S. Bias and illumination instability analysis of solution-processed a-InGaZnO thin-film transistors with different component ratios. Thin Solid Film. 2018, 645, 154–159. [Google Scholar] [CrossRef]

- Liu, A.; Liu, G.; Zhu, H.; Shin, B.; Fortunato, E.; Martins, R.; Shan, F. Eco-friendly water-induced aluminum oxide dielectrics and their application in a hybrid metal oxide/polymer TFT. RSC Adv. 2015, 5, 86606–86613. [Google Scholar] [CrossRef]

- Yeon, H.-W.; Lim, S.-M.; Jung, J.-K.; Yoo, H.; Lee, Y.-J.; Kang, H.-Y.; Park, Y.-J.; Kim, M.; Joo, Y.-C. Structural-relaxation-driven electron doping of amorphous oxide semiconductors by increasing the concentration of oxygen vacancies in shallow-donor states. NPG Asia Mater. 2016, 8, e250. [Google Scholar] [CrossRef]

- Ide, K.; Nomura, K.; Hiramatsu, H.; Kamiya, T.; Hosono, H. Structural relaxation in amorphous oxide semiconductor, a-In-Ga-Zn-O. J. Appl. Phys. 2012, 111, 073513. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. Sci. Technol. Adv. Mater. 2010, 11, 044305. [Google Scholar] [CrossRef]

- Yabuta, H.; Sano, M.; Abe, K.; Aiba, K.; Den, T.; Kumomi, H.; Hosono, H. High-mobility thin-film transistor with amorphous In Ga Zn O4 channel fabricated by room temperature rf-magnetron sputtering. Appl. Phys. Lett. 2006, 89, 112123. [Google Scholar] [CrossRef]

- Jeong, S.; Moon, J. Low-temperature, solution-processed metal oxide thin film transistors. J. Mater. Chem. 2012, 22, 1243–1250. [Google Scholar] [CrossRef]

- Seo, S.-J.; Choi, C.G.; Hwang, Y.H.; Bea, B.-S. High performance solution-processed amorphous zinc tin oxide thin film transistor. J. Phys. D Appl. Phys. 2008, 42, 035106. [Google Scholar] [CrossRef]

- Fernandes, C.; Santa, A.; Santos, Â.; Bahubalindruni, P.; Deuermeier, J.; Martins, R.; Fortunato, E.; Barquinha, P. A sustainable approach to flexible electronics with zinc-tin oxide thin-film transistors. Adv. Electron. Mater. 2018, 4, 1800032. [Google Scholar] [CrossRef]

- Zeng, Z.; Zeng, Y.; Yao, R.; Fang, Z.; Zhang, H.; Hu, S.; Li, X.; Ning, H.; Peng, J.; Xie, W.; et al. All-sputtered, flexible, bottom-gate IGZO/Al2O3 bi-layer thin film transistors on PEN fabricated by a fully room temperature process. J. Mater. Chem. C 2017, 5, 7043–7050. [Google Scholar] [CrossRef]

- Lee, S.S.; Ghaffarzadeh, K.; Nathan, A.; Robertson, J.; Jeon, S.H.; Kim, C.J.; Song, I.-H.; Chung, U.-I. Trap-limited and percolation conduction mechanisms in amorphous oxide semiconductor thin film transistors. Appl. Phys. Lett. 2011, 98, 203508. [Google Scholar] [CrossRef]

- Lee, S.S.; Nathan, A.; Ye, Y.; Guo, Y.; Robertson, J. Localized Tail States and Electron Mobility in Amorphous ZnON Thin Film Transistors. Sci. Rep. 2015, 5, 13467. [Google Scholar] [CrossRef] [PubMed]

- Zhong, W.; Li, G.; Lan, L.; Li, B.; Chen, R. Effects of annealing temperature on properties of InSnZnO thin film transistors prepared by Co-sputtering. RSC Adv. 2018, 8, 34817–34822. [Google Scholar] [CrossRef]

- Jeong, J.K. Photo-bias instability of metal oxide thin film transistors for advanced active matrix displays. J. Mater. Res. 2013, 28, 2071–2084. [Google Scholar] [CrossRef]

- Kwon, J.-Y.; Jung, J.S.; Son, K.S.; Lee, K.-H.; Park, J.S.; Kim, T.S.; Park, J.S.; Choi, R.; Jeong, J.K.; Koo, B.; et al. The impact of gate dielectric materials on the light-induced bias instability in Hf–In–Zn–O thin film transistor. Appl. Phys. Lett. 2010, 97, 183503. [Google Scholar] [CrossRef]

- Oh, H.; Yoon, S.-M.; Hwang, C.-S.; Yang, S.; Ko Park, S.-H. Photon-accelerated negative bias instability involving subgap states creation in amorphous In–Ga–Zn–O thin film transistor. Appl. Phys. Lett. 2010, 97, 183502. [Google Scholar] [CrossRef]

| SR | μsat (cm2 V−1 s−1) | VT (V) | SS (V dec−1) | Ion/off Ratio |

|---|---|---|---|---|

| 10 | 0.38 | 3.08 | 0.36 | 1.58 × 106 |

| 20 | 0.50 | 0.45 | 0.45 | 1.06 × 106 |

| 30 | 1.10 | 0.15 | 0.83 | 4.07 × 106 |

| 40 | 2.41 | −0.95 | 1.25 | 3.9 × 106 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hwang, Y.-J.; Kim, D.-K.; Jeon, S.-H.; Wang, Z.; Park, J.; Lee, S.-H.; Jang, J.; Kang, I.M.; Bae, J.-H. Importance of Structural Relaxation on the Electrical Characteristics and Bias Stability of Solution-Processed ZnSnO Thin-Film Transistors. Nanomaterials 2022, 12, 3097. https://doi.org/10.3390/nano12183097

Hwang Y-J, Kim D-K, Jeon S-H, Wang Z, Park J, Lee S-H, Jang J, Kang IM, Bae J-H. Importance of Structural Relaxation on the Electrical Characteristics and Bias Stability of Solution-Processed ZnSnO Thin-Film Transistors. Nanomaterials. 2022; 12(18):3097. https://doi.org/10.3390/nano12183097

Chicago/Turabian StyleHwang, Yu-Jin, Do-Kyung Kim, Sang-Hwa Jeon, Ziyuan Wang, Jaehoon Park, Sin-Hyung Lee, Jaewon Jang, In Man Kang, and Jin-Hyuk Bae. 2022. "Importance of Structural Relaxation on the Electrical Characteristics and Bias Stability of Solution-Processed ZnSnO Thin-Film Transistors" Nanomaterials 12, no. 18: 3097. https://doi.org/10.3390/nano12183097

APA StyleHwang, Y.-J., Kim, D.-K., Jeon, S.-H., Wang, Z., Park, J., Lee, S.-H., Jang, J., Kang, I. M., & Bae, J.-H. (2022). Importance of Structural Relaxation on the Electrical Characteristics and Bias Stability of Solution-Processed ZnSnO Thin-Film Transistors. Nanomaterials, 12(18), 3097. https://doi.org/10.3390/nano12183097