Binary-Synaptic Plasticity in Ambipolar Ni-Silicide Schottky Barrier Poly-Si Thin Film Transistors Using Chitosan Electric Double Layer

Abstract

:1. Introduction

2. Experimental Details

2.1. Device Fabrication

2.2. Characterization and Measurements

3. Results and Discussion

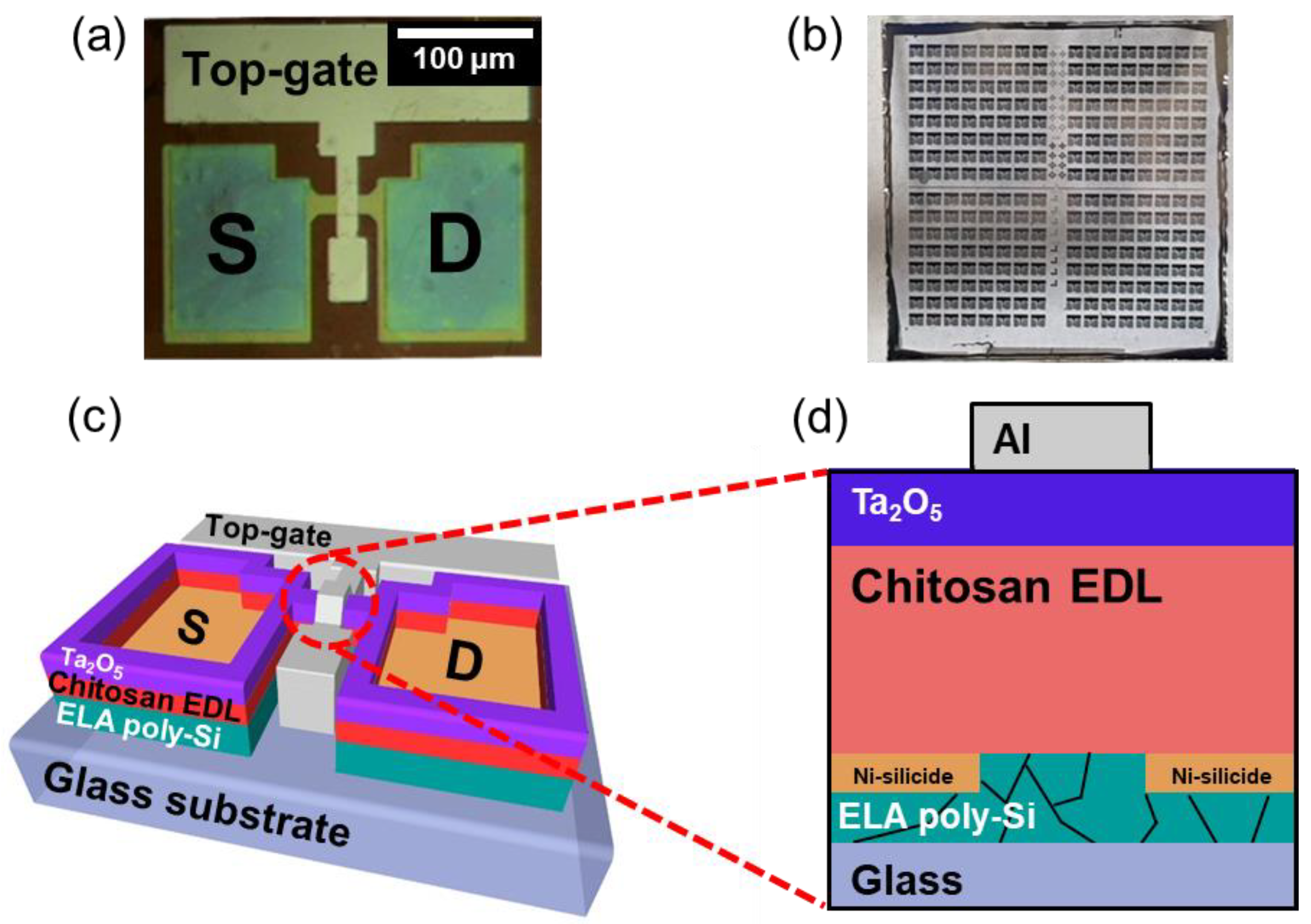

3.1. Device Structure of Ambipolar Chitosan Synaptic Transistor

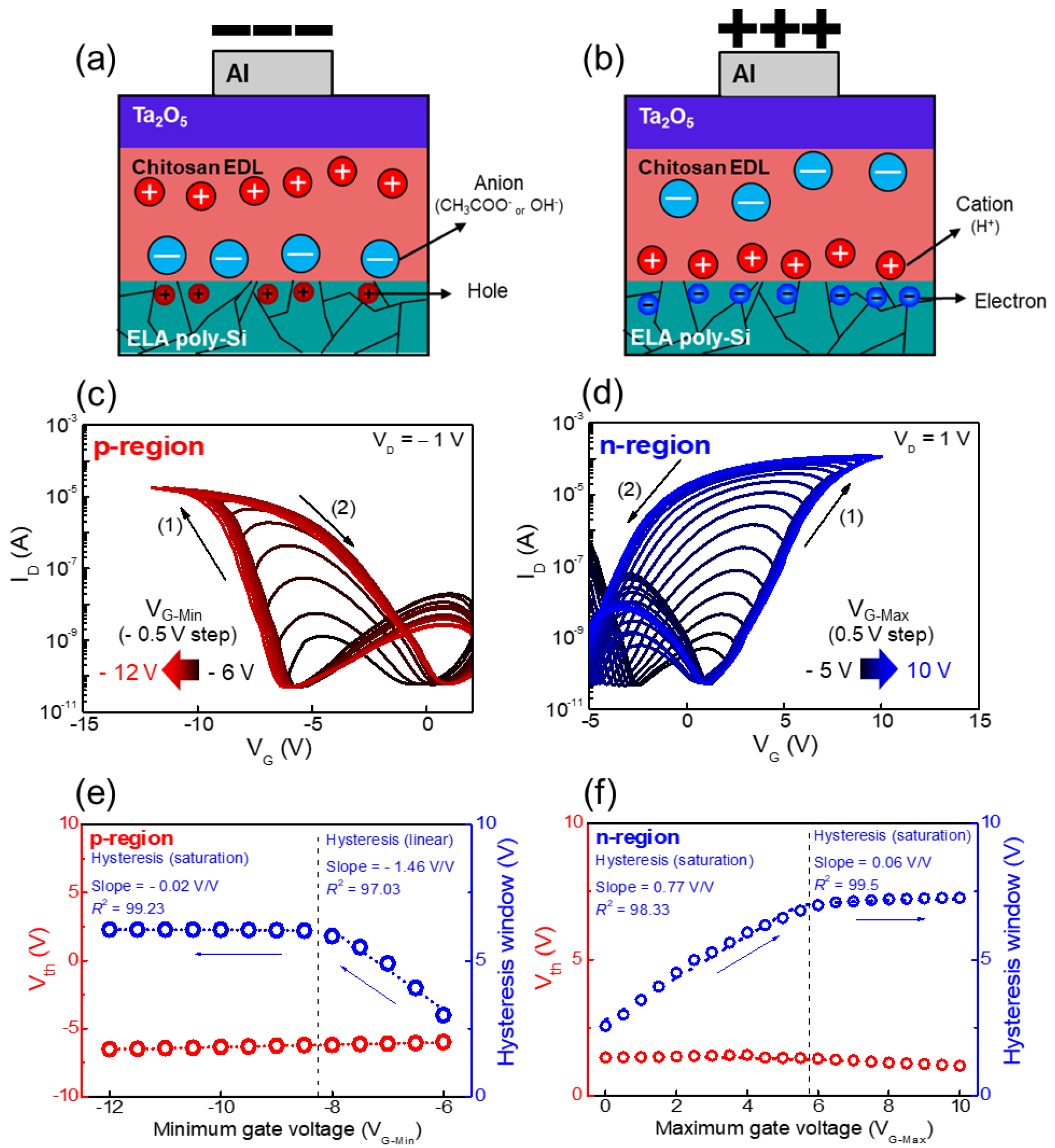

3.2. Characterization of Chitosan Electrolyte EDL and NiSi S/D

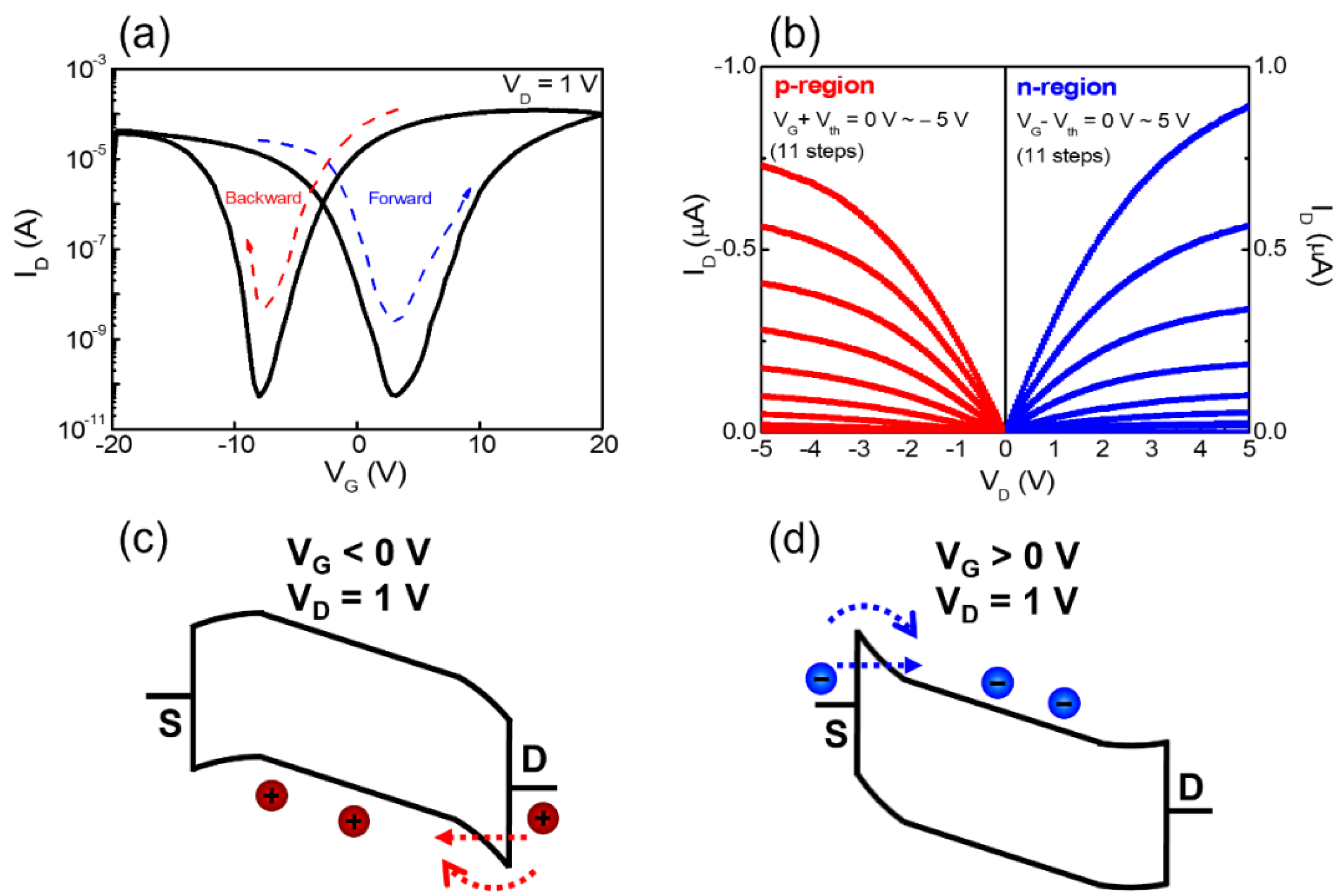

3.3. Electrical Properties of the Ambipolar Chitosan Synaptic Transistor

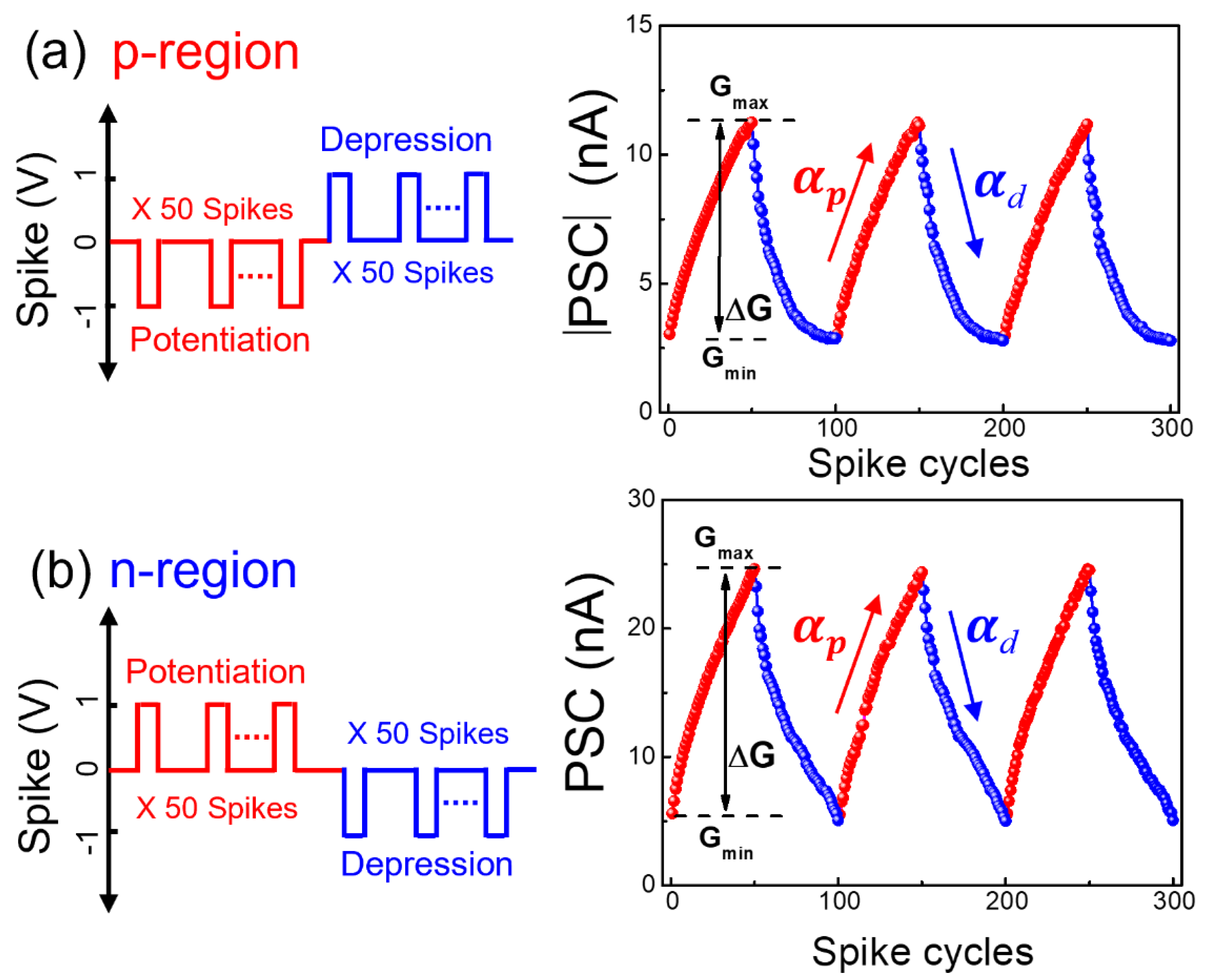

3.4. Synapse Mimicking Properties of the Ambipolar Chitosan Synaptic Transistor

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Tavakoli, M.; Carriere, J.; Torabi, A. Robotics, smart wearable technologies, and autonomous intelligent systems for healthcare during the COVID-19 pandemic: An analysis of the state of the art and future vision. Adv. Intell. Syst. 2020, 2, 2000071. [Google Scholar] [CrossRef]

- He, W.; Li, Z.; Chen, C.P. A survey of human-centered intelligent robots: Issues and challenges. IEEE/CAA J. Autom. Sin. 2017, 4, 602–609. [Google Scholar] [CrossRef]

- Li, B.H.; Hou, B.C.; Yu, W.T.; Lu, X.B.; Yang, C.W. Applications of artificial intelligence in intelligent manufacturing: A review. Front. Inf. Technol. Electron. Eng. 2017, 18, 86–96. [Google Scholar] [CrossRef]

- Nurvitadhi, E.; Sheffield, D.; Sim, J.; Mishra, A.; Venkatesh, G.; Marr, D. Accelerating Binarized Neural Networks: Comparison of FPGA, CPU, GPU, and ASIC. In Proceedings of the 2016 International Conference on Field-Programmable Technology (FPT), Xi’an, China, 7–9 December 2016. [Google Scholar]

- Nurvitadhi, E.; Venkatesh, G.; Sim, J.; Marr, D.; Huang, R.; Ong Gee Hock, J.; Liew, Y.T.; Srivatsan, K.; Moss, D.; Subhaschandra, S.; et al. Can FPGAs Beat GPUs in Accelerating Next-Generation Deep Neural Networks? In Proceedings of the 2017 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2017. [Google Scholar]

- Greenberg-Toledo, T.; Mazor, R.; Haj-Ali, A.; Kvatinsky, S. Supporting the momentum training algorithm using a memristor-based synapse. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 1571–1583. [Google Scholar] [CrossRef]

- Shi, J.; Ha, S.D.; Zhou, Y.; Schoofs, F.; Ramanathan, S. A correlated nickelate synaptic transistor. Nat. Commun. 2013, 4, 2676. [Google Scholar] [CrossRef]

- Zhu, L.Q.; Wan, C.J.; Guo, L.Q.; Shi, Y.; Wan, Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. Nat. Commun. 2014, 5, 3158. [Google Scholar] [CrossRef]

- Yang, C.S.; Shang, D.S.; Liu, N.; Fuller, E.J.; Agrawal, S.; Talin, A.A.; Li, Y.Q.; Shen, B.G.; Sun, Y. All-solid-state synaptic transistor with ultralow conductance for neuromorphic computing. Adv. Funct. Mater. 2018, 28, 1804170. [Google Scholar] [CrossRef]

- Zhu, L.Q.; Wan, C.J.; Gao, P.Q.; Liu, Y.H.; Xiao, H.; Ye, J.C.; Wan, Q. Flexible proton-gated oxide synaptic transistors on Si membrane. ACS Appl. Mater. Interfaces 2016, 8, 21770–21775. [Google Scholar] [CrossRef]

- Shao, F.; Yang, Y.; Zhu, L.Q.; Feng, P.; Wan, Q. Oxide-based synaptic transistors gated by sol–gel silica electrolytes. ACS Appl. Mater. Interfaces 2016, 8, 3050–3055. [Google Scholar] [CrossRef]

- Kalia, M.; Meijer, H.G.; van Gils, S.A.; van Putten, M.J.; Rose, C.R. Ion dynamics at the energy-deprived tripartite synapse. PLoS Comput. Biol. 2021, 17, e1009019. [Google Scholar] [CrossRef]

- Lee, J.; Panzer, M.J.; He, Y.; Lodge, T.P.; Frisbie, C.D. Ion gel gated polymer thin-film transistors. J. Am. Chem. Soc. 2007, 129, 4532–4533. [Google Scholar] [CrossRef] [PubMed]

- Choi, J.H.; Xie, W.; Gu, Y.; Frisbie, C.D.; Lodge, T.P. Single ion conducting, polymerized ionic liquid triblock copolymer films: High capacitance electrolyte gates for n-type transistors. ACS Appl. Mater. Interfaces 2015, 7, 7294–7302. [Google Scholar] [CrossRef] [PubMed]

- Hosseini, N.R.; Lee, J.S. Biocompatible and flexible chitosan-based resistive switching memory with magnesium electrodes. Adv. Funct. Mater. 2015, 25, 5586–5592. [Google Scholar] [CrossRef]

- Liu, Y.H.; Zhu, L.Q.; Feng, P.; Shi, Y.; Wan, Q. Freestanding artificial synapses based on laterally proton-coupled transistors on chitosan membranes. Adv. Mater. 2015, 27, 5599–5604. [Google Scholar] [CrossRef] [PubMed]

- Fu, W.H.; Li, J.; Jiang, D.L.; Yang, Y.H.; Chen, Q.; Zhu, W.Q.; Zhang, J.H. Proton conducting C3N4/chitosan composite electrolytes based InZnO thin film transistor for artificial synapse. Org. Electron. 2020, 85, 105870. [Google Scholar] [CrossRef]

- Kim, S.H.; Cho, W.J. Lithography processable Ta2O5 barrier-layered chitosan electric double layer synaptic transistors. Int. J. Mol. Sci. 2021, 22, 1344. [Google Scholar] [CrossRef]

- Min, S.Y.; Cho, W.J. CMOS-compatible synaptic transistor gated by chitosan electrolyte-Ta2O5 hybrid electric double layer. Sci. Rep. 2020, 10, 15561. [Google Scholar] [CrossRef]

- Hu, W.; Jiang, J.; Xie, D.; Liu, B.; Yang, J.; He, J. Proton–electron-coupled MoS2 synaptic transistors with a natural renewable biopolymer neurotransmitter for brain-inspired neuromorphic learning. J. Mater. Chem. C 2019, 7, 682–691. [Google Scholar] [CrossRef]

- Yu, F.; Zhu, L.Q.; Gao, W.T.; Fu, Y.M.; Xiao, H.; Tao, J.; Zhou, J.M. Chitosan-based polysaccharide-gated flexible indium tin oxide synaptic transistor with learning abilities. ACS Appl. Mater. Interfaces 2018, 10, 16881–16886. [Google Scholar] [CrossRef]

- Liu, R.; Zhu, L.Q.; Wang, W.; Hui, X.; Liu, Z.P.; Wan, Q. Biodegradable oxide synaptic transistors gated by a biopolymer electrolyte. J. Mater. Chem. C 2016, 4, 7744–7750. [Google Scholar] [CrossRef]

- Sundaram, R.S.; Gowtham, L.; Nayak, B.S. The role of excitatory neurotransmitter glutamate in brain physiology and pathology. Asian J. Pharm. Clin. Res. 2012, 5, 1–7. [Google Scholar]

- McCormick, D.A. GABA as an inhibitory neurotransmitter in human cerebral cortex. J. Neurophysiol. 1989, 62, 1018–1027. [Google Scholar] [CrossRef] [PubMed]

- Yao, Y.; Huang, X.; Peng, S.; Zhang, D.; Shi, J.; Yu, G.; Liu, Q.; Jin, Z. Reconfigurable artificial synapses between excitatory and inhibitory modes based on single-gate graphene transistors. Adv. Electron. Mater. 2019, 5, 1800887. [Google Scholar] [CrossRef]

- Wang, Y.; Liao, Q.; She, D.; Lv, Z.; Gong, Y.; Ding, G.; Ye, W.; Chen, J.; Xiong, Z.; Wang, G.; et al. Modulation of binary neuroplasticity in a heterojunction-based ambipolar transistor. ACS Appl. Mater. Interfaces 2020, 12, 15370–15379. [Google Scholar] [CrossRef]

- Choi, S.J.; Han, J.W.; Kim, S.; Moon, D.I.; Jang, M.; Choi, Y.K. High-performance polycrystalline silicon TFT on the structure of a dopant-segregated schottky-barrier source/drain. IEEE Electron. Device Lett. 2010, 31, 228–230. [Google Scholar] [CrossRef]

- Shin, J.W.; Cho, W.J. Microwave annealing effects of indium-tin-oxide thin films: Comparison with conventional annealing methods. Phys. Status Solidi A 2018, 215, 1700975. [Google Scholar] [CrossRef]

- Kim, S.H.; Cho, W.J. Improvement of structural, electrical, and optical properties of sol–gel-derived indium–tin-oxide films by high efficiency microwave irradiation. J. Nanosci. Nanotechnol. 2021, 21, 1875–1882. [Google Scholar] [CrossRef]

- Long, T.Y.; Zhu, L.Q.; Guo, Y.B.; Ren, Z.Y.; Xiao, H.; Ge, Z.Y.; Wang, L. Flexible oxide neuromorphic transistors with synaptic learning functions. J. Phys. D Appl. Phys. 2019, 52, 405101. [Google Scholar] [CrossRef]

- Chen, C.; He, Y.; Zhu, L.; Zhu, Y.; Shi, Y.; Wan, Q. Flexible dual-date MoS2 neuromorphic transistors on freestanding proton-conducting chitosan membranes. IEEE Trans. Electron. Devices 2021, 68, 3119–3123. [Google Scholar] [CrossRef]

- Ren, Z.Y.; Zhu, L.Q.; Yu, F.; Xiao, H.; Xiong, W.; Ge, Z.Y. Synaptic metaplasticity of protonic/electronic coupled oxide neuromorphic transistor. Org. Electron. 2019, 74, 304–308. [Google Scholar] [CrossRef]

- Yu, F.; Zhu, L.Q.; Xiao, H.; Gao, W.T.; Guo, Y.B. Restickable oxide neuromorphic transistors with spike-timing-dependent plasticity and pavlovian associative learning activities. Adv. Funct. Mater. 2018, 28, 1804025. [Google Scholar] [CrossRef]

- Lu, G.; Liu, Y.; Lin, F.; Gen, K.; Wu, W.; Yao, R. Realization of artificial synapse and inverter based on oxide electric-double-layer transistor gated by a chitosan biopolymer electrolyte. Semicond. Sci. Technol. 2020, 35, 075014. [Google Scholar] [CrossRef]

- Jiang, S.; He, Y.; Liu, R.; Zhang, C.; Shi, Y.; Wan, Q. Synaptic metaplasticity emulation in a freestanding oxide-based neuromorphic transistor with dual in-plane gates. J. Phys. D Appl. Phys. 2021, 54, 185106. [Google Scholar] [CrossRef]

- Woranuch, S.; Yoksan, R. Preparation, characterization and antioxidant property of water-soluble ferulic acid grafted chitosan. Carbohydr. Polym. 2013, 96, 495–502. [Google Scholar] [CrossRef] [PubMed]

- Wu, C.T.; Lee, Y.J.; Hsueh, F.K.; Sung, P.J.; Cho, T.C.; Current, M.I.; Chao, T.S. Characterization of ultra-thin Ni silicide film by two-step low temperature microwave anneal. ECS J. Solid State Sci. Technol. 2014, 3, P122. [Google Scholar] [CrossRef]

- Bhaskaran, M.; Sriram, S.; Perova, T.S.; Ermakov, V.; Thorogood, G.J.; Short, K.T.; Holland, A.S. In situ micro-raman analysis and X-ray diffraction of nickel silicide thin films on silicon. Micron 2009, 40, 89–93. [Google Scholar] [CrossRef]

- Iwai, H.; Ohguro, T.; Ohmi, S.I. NiSi salicide technology for scaled CMOS. Microelectron. Eng. 2002, 60, 157–169. [Google Scholar] [CrossRef]

- Bennett, K.; Lala, P.K.; Busaba, F. Off-Line Testing for Bridge Faults in CMOS Domino Logic Circuits. In NASA University Research Centers Technical Advances in Education, Aeronautics, Space, Autonomy, Earth and Environment; NASA: Washington, DC, USA, 1997. [Google Scholar]

- Byon, K.; Tham, D.; Fischer, J.E.; Johnson, A.T. Systematic study of contact annealing: Ambipolar silicon nanowire transistor with improved performance. Appl. Phys. Lett. 2007, 90, 143513. [Google Scholar] [CrossRef]

- Kim, J.B.; Fuentes-Hernandez, C.; Kim, S.J.; Potscavage, W.J., Jr.; Choi, S.; Kippelen, B. Ambipolar thin-film transistors with a co-planar channel geometry. Org. Electron. 2010, 11, 1351–1356. [Google Scholar] [CrossRef]

- Wang, H.; Wang, J.; Yan, X.; Shi, J.; Tian, H.; Geng, Y.; Yan, D. Ambipolar organic field-effect transistors with air stability, high mobility, and balanced transport. Appl. Phys. Lett. 2006, 88, 133508. [Google Scholar] [CrossRef]

- Schießl, S.P.; Fröhlich, N.; Held, M.; Gannott, F.; Schweiger, M.; Forster, M.; Scherf, U.; Zaumseil, J. Polymer-sorted semiconducting carbon nanotube networks for high-performance ambipolar field-effect transistors. ACS Appl. Mater. Interfaces 2015, 7, 682–689. [Google Scholar] [CrossRef] [PubMed]

- Zhou, J.; Liu, Y.; Shi, Y.; Wan, Q. Solution-processed chitosan-gated IZO-based transistors for mimicking synaptic plasticity. IEEE Electron. Device Lett. 2014, 35, 280–282. [Google Scholar] [CrossRef]

- Yin, C.; Li, Y.; Wang, J.; Wang, X.; Yang, Y.; Ren, T.L. Carbon nanotube transistor with short-term memory. Tsinghua Sci. Technol. 2016, 21, 442–448. [Google Scholar] [CrossRef]

- Huang, H.Y.; Ge, C.; Zhang, Q.H.; Liu, C.X.; Du, J.Y.; Li, J.K.; Wang, C.; Gu, L.; Yang, G.Z.; Jin, K.J. Electrolyte-gated synaptic transistor with oxygen ions. Adv. Funct. Mater. 2019, 29, 1902702. [Google Scholar] [CrossRef]

- Guo, L.Q.; Zhu, L.Q.; Ding, J.N.; Huang, Y.K. Paired-pulse facilitation achieved in protonic/electronic hybrid indium gallium zinc oxide synaptic transistors. AIP Adv. 2015, 5, 087112. [Google Scholar] [CrossRef]

- Guo, L.; Wan, Q.; Wan, C.; Zhu, L.; Shi, Y. Short-term memory to long-term memory transition mimicked in IZO homojunction synaptic transistors. IEEE Electron. Device Lett. 2013, 34, 1581–1583. [Google Scholar] [CrossRef]

- Veletić, M.; Mesiti, F.; Floor, P.A.; Balasingham, I. Communication Theory Aspects of Synaptic Transmission. In Proceedings of the 2015 IEEE International Conference on Communications (ICC), London, UK, 8–12 June 2015. [Google Scholar]

- Lai, Q.; Zhang, L.; Li, Z.; Stickle, W.F.; Williams, R.S.; Chen, Y. Ionic/electronic hybrid materials integrated in a synaptic transistor with signal processing and learning functions. Adv. Mater. 2010, 22, 2448–2453. [Google Scholar] [CrossRef]

- Li, H.K.; Chen, T.P.; Liu, P.; Hu, S.G.; Liu, Y.; Zhang, Q.; Lee, P.S. A light-stimulated synaptic transistor with synaptic plasticity and memory functions based on InGaZnOx–Al2O3 thin film structure. J. Appl. Phys. 2016, 119, 244505. [Google Scholar] [CrossRef]

- Lan, S.; Zhong, J.; Chen, J.; He, W.; He, L.; Yu, R.; Chen, G.; Chen, H. An optoelectronic synaptic transistor with efficient dual modulation by light illumination. J. Mater. Chem. C 2021, 9, 3412–3420. [Google Scholar] [CrossRef]

- Zucker, R.S.; Regehr, W.G. Short-term synaptic plasticity. Annu. Rev. Physiol. 2002, 64, 355–405. [Google Scholar] [CrossRef]

- Kim, S.; Choi, B.; Lim, M.; Kim, Y.; Kim, H.D.; Choi, S.J. Synaptic device network architecture with feature extraction for unsupervised image classification. Small 2018, 14, 1800521. [Google Scholar] [CrossRef] [PubMed]

- Kang, D.H.; Kim, J.H.; Oh, S.; Park, H.Y.; Dugasani, S.R.; Kang, B.S.; Choi, C.; Choi, R.; Lee, S.; Park, S.H.; et al. A neuromorphic device implemented on a salmon-DNA electrolyte and its application to artificial neural networks. Adv. Sci. 2019, 6, 1901265. [Google Scholar] [CrossRef] [PubMed] [Green Version]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, K.-W.; Cho, W.-J. Binary-Synaptic Plasticity in Ambipolar Ni-Silicide Schottky Barrier Poly-Si Thin Film Transistors Using Chitosan Electric Double Layer. Nanomaterials 2022, 12, 3063. https://doi.org/10.3390/nano12173063

Park K-W, Cho W-J. Binary-Synaptic Plasticity in Ambipolar Ni-Silicide Schottky Barrier Poly-Si Thin Film Transistors Using Chitosan Electric Double Layer. Nanomaterials. 2022; 12(17):3063. https://doi.org/10.3390/nano12173063

Chicago/Turabian StylePark, Ki-Woong, and Won-Ju Cho. 2022. "Binary-Synaptic Plasticity in Ambipolar Ni-Silicide Schottky Barrier Poly-Si Thin Film Transistors Using Chitosan Electric Double Layer" Nanomaterials 12, no. 17: 3063. https://doi.org/10.3390/nano12173063

APA StylePark, K.-W., & Cho, W.-J. (2022). Binary-Synaptic Plasticity in Ambipolar Ni-Silicide Schottky Barrier Poly-Si Thin Film Transistors Using Chitosan Electric Double Layer. Nanomaterials, 12(17), 3063. https://doi.org/10.3390/nano12173063