Surface Nano-Patterning for the Bottom-Up Growth of III-V Semiconductor Nanowire Ordered Arrays

Abstract

1. Introduction

2. Semiconductor Nanowires and Nanowire Arrays

3. Bottom-Up Approaches to the Realization of Ordered Arrays of Vertically Aligned Semiconductor Nanowires

3.1. Nanowire Arrays Growth from the Bottom-Up

3.2. Substrate Metal Patterning for Nanowire Array Growth

3.2.1. EBL Pre-Patterned Substrates for Nanowire Epitaxial Growth

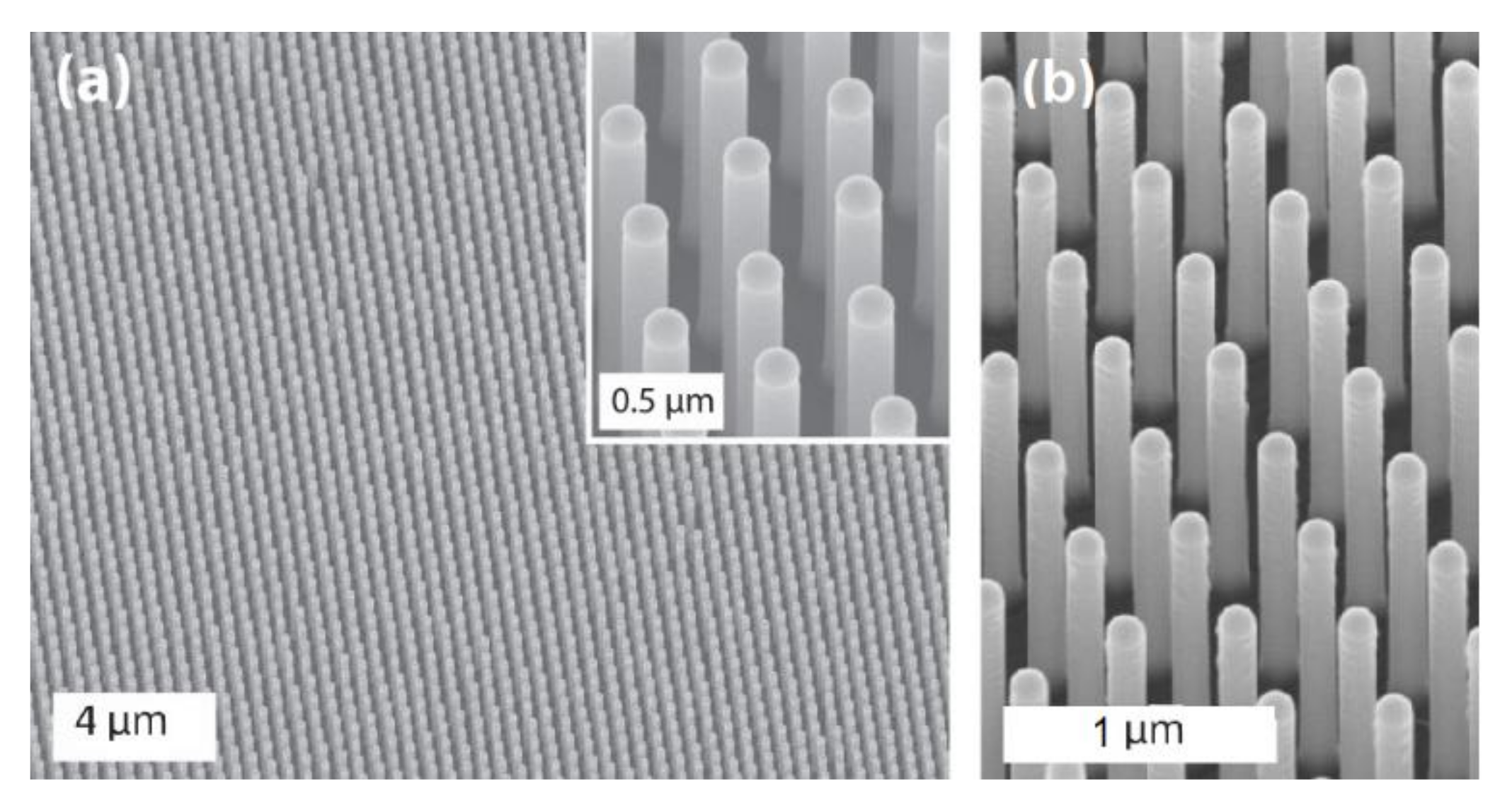

3.2.2. Nanoimprint Lithography Pre-Patterned Substrates

3.3. Substrate Patterning Approach for Self-Assisted Growth and Catalyst-Free Selective Area Growth

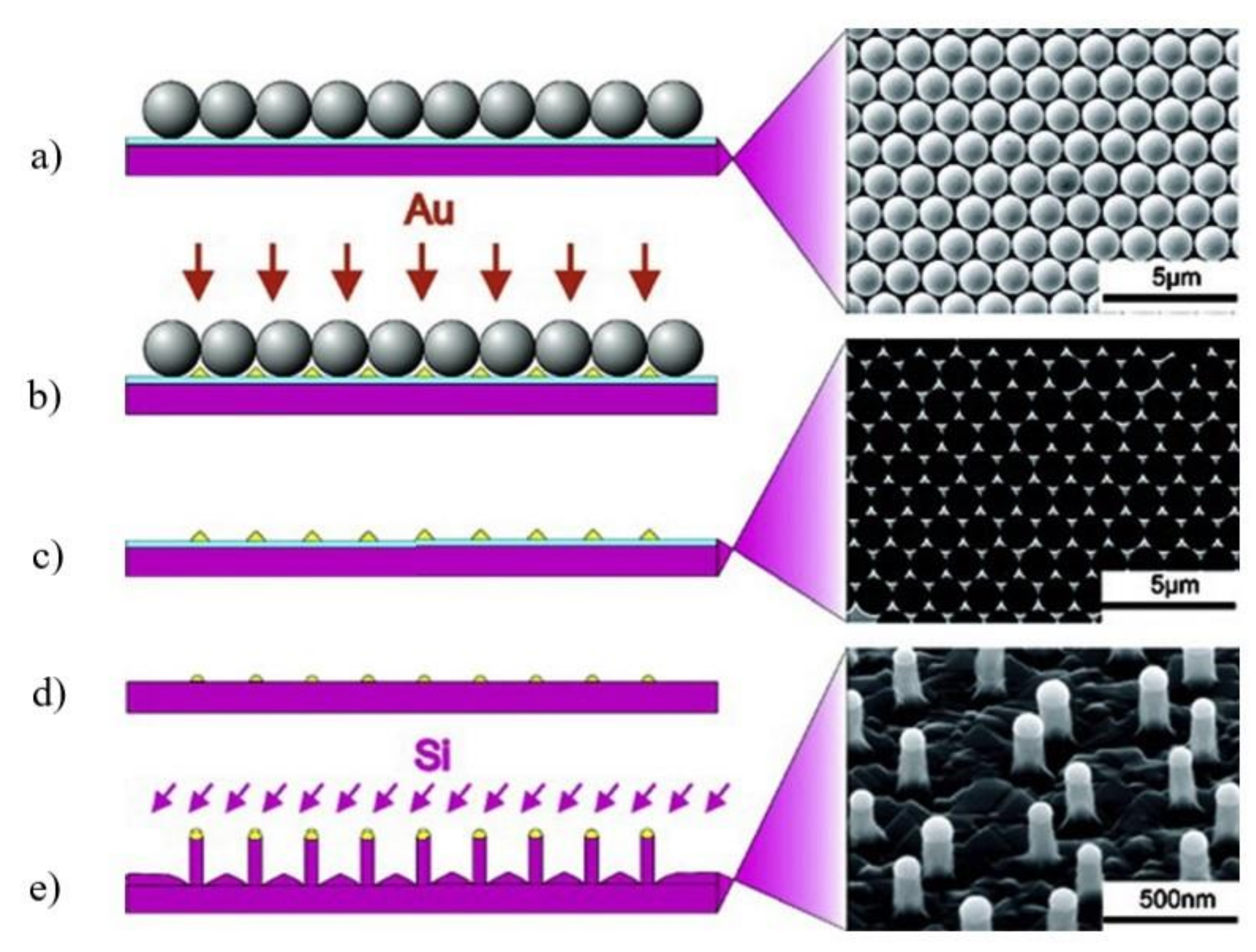

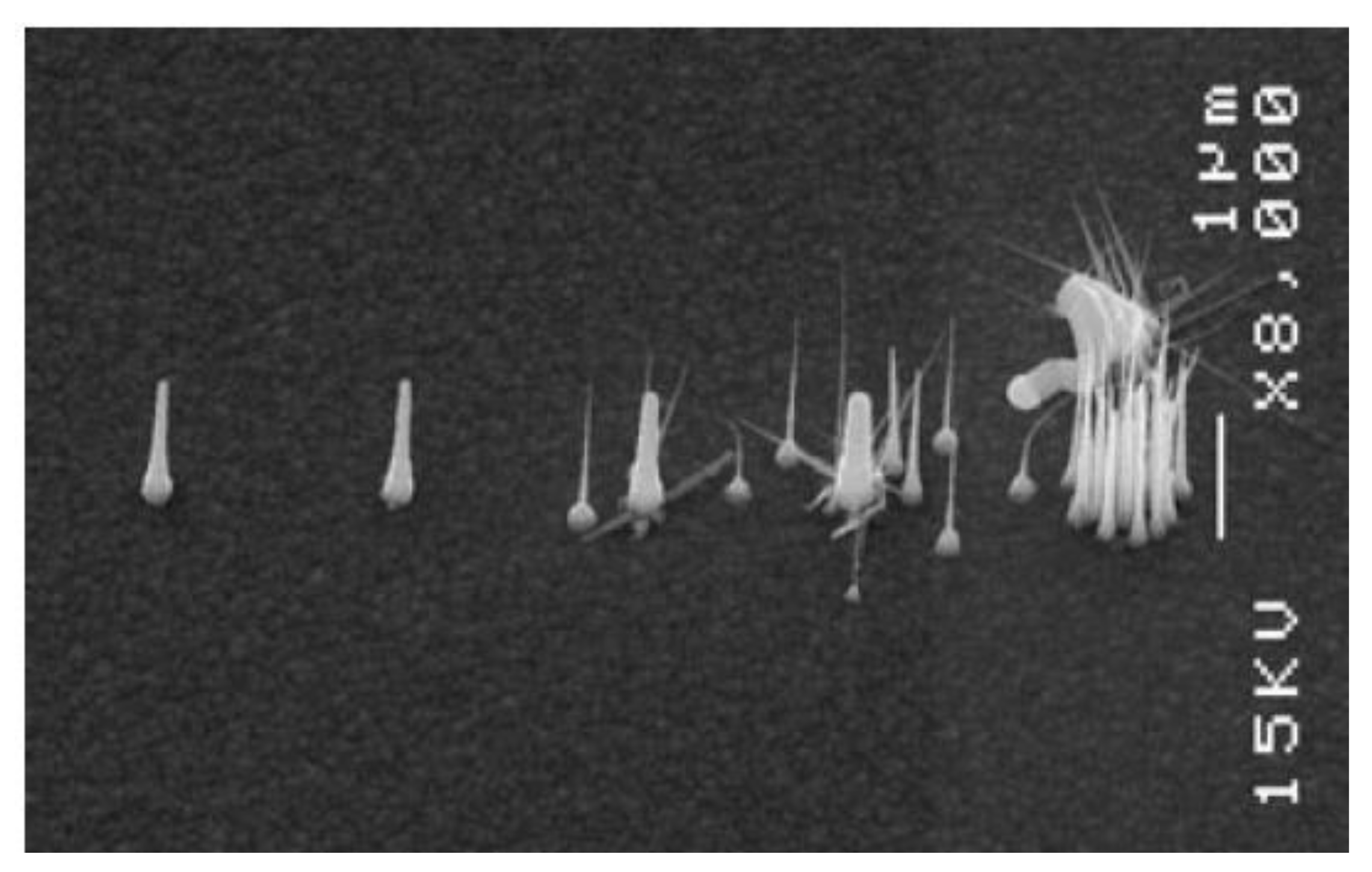

3.4. Alternative Nanopatterning Techniques

4. Influence of the Pattern Characteristics

4.1. Role of the Pattern’s Individual Element Shape

4.1.1. Role of the Pattern’s Individual Element in Defining the Nanowire Diameter

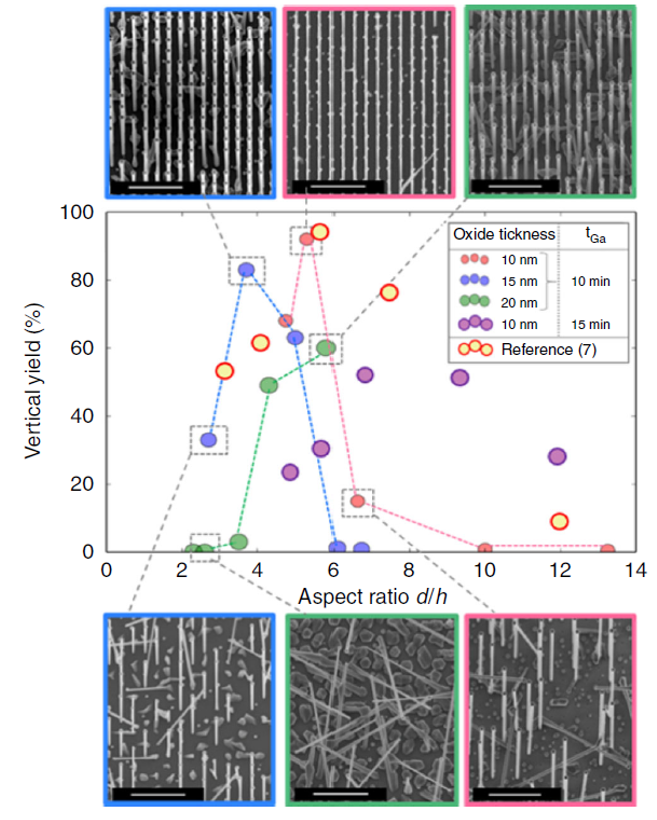

4.1.2. Role of the Pattern Individual Element Aspect Ratio

4.1.3. Role of the Pattern Individual Element Shape in Improving the Pattern Fidelity

4.2. Role of the Pattern Pitch on the Axial and Radial Growth Rate

4.3. Impact of Tapering

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Güniat, L.; Caroff, P.; Fontcuberta I Morral, A. Vapor phase growth of semiconductor nanowires: Key developments and open questions. Chem. Rev. 2019, 119, 8958–8971. [Google Scholar] [CrossRef]

- LaPierre, R.R.; Robson, M.; Azizur-Rahman, K.M.; Kuyanov, P. A review of III–V nanowire infrared photodetectors and sensors. J. Phys. D Appl. Phys. 2017, 50, 123001. [Google Scholar] [CrossRef]

- Vukajlovic-Plestina, J.; Kim, W.; Ghisalberti, L.; Varnavides, G.; Tütüncuoglu, G.; Potts, H.; Friedl, M.; Güniat, L.; Carter, W.C.; Dubrovskii, V.G.; et al. Fundamental aspects to localize self-catalyzed III-V nanowires on silicon. Nat. Commun. 2019, 10, 869. [Google Scholar] [CrossRef]

- Tomioka, K.; Yoshimura, M.; Fukui, T.A. III–V nanowire channel on silicon for high-performance vertical transistors. Nature 2012, 488, 189–192. [Google Scholar] [CrossRef]

- McIntyre, P.C.; Fontcuberta I Morral, A. Semiconductor nanowires: To grow or not to grow? Mater. Today Nano 2020, 9, 100058. [Google Scholar] [CrossRef]

- Barrigonemar, B.; Samuelson, L. Synthesis and applications of III–V nanowires. Chem. Rev. 2019, 119, 9170–9220. [Google Scholar] [CrossRef] [PubMed]

- Lin, S.Y.; Chow, E.; Hietala, V.; Villeneuve, P.R.; Joannopoulos, J.D. Experimental demonstration of guiding and bending of electromagnetic waves in a photonic crystal. Science 1998, 282, 274–276. [Google Scholar] [CrossRef]

- Fan, Z.; Kapadia, R.; Leu, P.W.; Zhang, X.; Chueh, Y.-L.; Takei, K.; Yu, K.; Jamshidi, A.; Rathore, A.A.; Ruebusch, D.J. Ordered arrays of dual-diameter nanopillars for maximized optical absorption. Nano Lett. 2010, 10, 3823–3827. [Google Scholar] [CrossRef] [PubMed]

- Demontis, V.; Marini, A.; Floris, F.; Sorba, L.; Rossella, F. Engineering the optical reflectance of randomly arranged self-assembled semiconductor nanowires. AIP Conf. Proc. 2020, 2257, 020009. [Google Scholar]

- Larrieu, G.; Han, X.L. Vertical nanowire array-based field effect transistors for ultimate scaling. Nanoscale 2013, 5, 2437. [Google Scholar] [CrossRef]

- Thelander, C.; Agarwal, P.; Brongersma, S.; Eymery, J.; Feiner, L.F.; Forchel, A.; Scheffler, M.; Riess, W.; Ohlsson, B.J.; Goesele, U.; et al. Nanowire-based one-dimensional electronics. Mater. Today 2006, 9, 28–35. [Google Scholar] [CrossRef]

- Chandra, N.; Tracy, C.J.; Cho, J.H.; Picraux, S.T.; Hathwar, R.; Goodnick, S.M. Vertically grown Ge nanowire Schottky diodes on Si and Ge substrates. J. Appl. Phys. 2015, 118, 024301. [Google Scholar] [CrossRef]

- Garnett, E.; Yang, P. Light trapping in silicon nanowire solar cells. Nano Lett. 2010, 10, 1082–1087. [Google Scholar] [CrossRef] [PubMed]

- Goktas, N.I.; Wilson, P.; Ghukasyan, D.; Wagner, D.; McNamee, S.; LaPierre, R.R. Nanowires for energy: A review. Appl. Phys. Rev. 2018, 5, 041305. [Google Scholar] [CrossRef]

- Kelzenberg, M.; Boettcher, S.; Petykiewicz, J.; Turner-Evans, D.B.; Putnam, M.C.; Warren, E.L.; Spurgeon, J.M.; Briggs, R.M.; Lewis, N.S.; Atwater, H.A. Enhanced absorption and carrier collection in Si wire arrays for photovoltaic applications. Nat. Mater. 2010, 9, 239–244. [Google Scholar] [CrossRef]

- Wallentin, J.; Anttu, N.; Asoli, D.; Huffman, M.; Aberg, I.; Magnusson, M.H.; Siefer, G.; Fuss-Kailuweit, P.; Dimroth, F.; Witzigmann, B.; et al. InP nanowire array solar cells achieving 13.8% efficiency by exceeding the ray optics limit. Science 2013, 339, 1050–1060. [Google Scholar] [CrossRef]

- Schüffelgen, P.; Schmitt, T.; Schleenvoigt, M.; Rosenbach, D.; Perla, P.; Jalil, A.R.; Mussler, G.; Lepsa, M.; Schäpers, T.; Grützmacher, D. Exploiting topological matter for Majorana physics and devices. Solid-State Electron. 2019, 155, 99–104. [Google Scholar] [CrossRef]

- Gibson, S.J.; van Kasteren, B.; Tekcan, B.; Cui, Y.; van Dam, D.; Haverkort, J.E.M.; Bakkers, E.P.A.M.; Reimer, M.E. Tapered InP nanowire arrays for efficient broadband high-speed single-photon detection. Nat. Nanotechnol. 2019, 14, 473–479. [Google Scholar] [CrossRef]

- Kim, H.; Lee, W.; Farrell, A.C.; Morales, J.S.D.; Senanayake, P.; Prikhodko, S.V.; Ochalski, T.J.; Huffaker, D.L. Monolithic InGaAs nanowire array lasers on silicon-on-insulator operating at room temperature. Nano Lett. 2017, 17, 3465–3470. [Google Scholar] [CrossRef] [PubMed]

- Yan, R.; Gargas, D.; Yang, P. Nanowire photonics. Nat. Photonics 2009, 3, 569–576. [Google Scholar] [CrossRef]

- Liao, Y.L.; Zhao, Y. Ultra-narrowband dielectric metamaterial absorber with ultra-sparse nanowire grids for sensing applications. Sci. Rep. 2020, 10, 1480. [Google Scholar] [CrossRef]

- Patolsky, F.; Lieber, C.M. Nanowire nanosensors. Mater. Today 2005, 8, 20–28. [Google Scholar] [CrossRef]

- Offermans, P.; Crego-Calama, M.; Brongersma, S.K. Gas detection with vertical InAs nanowire arrays. Nano Lett. 2010, 10, 2412–2415. [Google Scholar] [CrossRef]

- Elnathan, R.; Kwiat, M.; Patolsky, F.; Voelcker, N.H. Engineering vertically aligned semiconductor nanowire arrays for applications in the life sciences. Nano Today 2014, 9, 172–196. [Google Scholar] [CrossRef]

- Muskens, O.L.; Diedenhofen, S.L.; van Weert, M.H.M.; Borgström, M.T.; Bakkers, E.P.A.M.; Gómez Rivas, J. Epitaxial growth of aligned semiconductor nanowire metamaterials for photonic applications. Adv. Fun. Mat. 2008, 18, 103–1046. [Google Scholar] [CrossRef]

- Quan, L.N.; Kang, J.; Ning, C.Z.; Yang, P. Nanowires for Photonics. Chem. Rev. 2019, 119, 9153–9169. [Google Scholar] [CrossRef]

- Simovski, C.; Belov, P.; Atrashchenko, A.V.; Kivshar, Y. Wire metamaterials: Physics and applications. Adv. Mater. 2010, 24, 4229–4248. [Google Scholar] [CrossRef]

- Tsai, K.; Wurtz, G.A.; Chu, J.; Cheng, T.; Wang, H.; Krasavin, A.V.; He, J.; Wells, B.M.; Podolskiy, V.A.; Wang, J. Looking into meta-atoms of plasmonic nanowire metamaterial. Nano Lett. 2014, 14, 4971–4976. [Google Scholar] [CrossRef]

- Yao, J.; Liu, Z.; Liu, Y.; Wang, Y.; Sun, C.; Bartal, G.; Stacy, A.M.; Zhang, X. Optical negative refraction in bulk metamaterials of nanowires. Science 2008, 321, 930. [Google Scholar] [CrossRef]

- Cai, W.; Chettiar, U.K.; Kildishev, A.V.; Shalaev, V.M. Optical cloaking with metamaterials. Nat. Photonics 2007, 1, 224–227. [Google Scholar] [CrossRef]

- Salary, M.M.; Mosallaei, H. Electrically tunable metamaterials based on multimaterial nanowires incorporating transparent conductive oxides. Sci. Rep. 2017, 7, 10055. [Google Scholar] [CrossRef] [PubMed]

- Yang, Z.P.; Ci, L.; Bur, J.A.; Lin, S.Y.; Ajayan, P.M. Experimental observation of an extremely dark material made by a low-density nanotube array. Nano Lett. 2008, 8, 446–451. [Google Scholar] [CrossRef]

- Lim, A.J.; Adam, J.; Rago, D.; Esquerre, V.; Bordo, V. Optical properties of nanowire metamaterials with gain. Opt. Commun. 2016, 379, 25–31. [Google Scholar] [CrossRef]

- Floris, F.; Fornasari, L.; Bellani, V.; Marini, A.; Banfi, F.; Marabelli, F.; Beltram, F.; Ercolani, D.; Battiato, S.; Sorba, L.; et al. Strong modulations of optical reflectance in tapered core-shell nanowires. Materials 2019, 12, 3572. [Google Scholar] [CrossRef]

- Floris, F.; Fornasari, L.; Marini, A.; Bellani, V.; Banfi, F.; Roddaro, S.; Ercolani, D.; Rocci, M.; Beltram, F.; Cecchini, M.; et al. Self-assembled InAs nanowires as optical reflectors. Nanomaterials 2017, 7, 400. [Google Scholar] [CrossRef]

- Kim, S.; Song, H.; Ahn, H.; Jun, S.W.; Kim, S.; Song, Y.M.; Yang, S.Y.; Kim, C.S.; Kim, K. 3D super-resolved imaging in live cells using sub-diffractive plasmonic localization of hybrid nanopillar arrays. Nanophotonics 2020, 9, 2847–2859. [Google Scholar] [CrossRef]

- Soci, C.; Zhang, A.; Bao, X.Y.; Kim, H.; Lo, Y.; Wang, D. Nanowire photodetectors. J. Nanosci. Nanotechnol. 2010, 10, 1430–1449. [Google Scholar] [CrossRef]

- Huang, L.; Wei, Q.; Sun, R.; Mai, L. Nanowire electrodes for advanced lithium batteries. Front. Energy Res. 2014, 2, 43. [Google Scholar] [CrossRef]

- Wagner, R.S.; Ellis, W.C. Vapor-liquid-solid mechanism of single crystal growth. Appl. Phys. Lett. 1964, 4, 89–90. [Google Scholar] [CrossRef]

- Hobbes, R.G.; Petkov, N.; Holmes, J.D. Semiconductor nanowire fabrication by bottom-up and top-down paradigms. Chem. Mater. 2012, 24, 1975–1991. [Google Scholar] [CrossRef]

- Duan, X.; Lieber, C.M. Laser-assisted catalytic growth of single crystal gan nanowires. J. Am. Chem. Soc. 2000, 122, 188–189. [Google Scholar] [CrossRef]

- Hu, J.T.; Min, O.Y.; Yang, P.D.; Lieber, C.M. Controlled growth and electrical properties of heterojunctions of carbon nanotubes and silicon nanowires. Nature 1999, 399, 48–51. [Google Scholar] [CrossRef]

- Wu, Y.; Yang, P. Germanium nanowire growth via simple vapor transport. Chem. Mater. 2000, 12, 605–607. [Google Scholar] [CrossRef]

- Samuelson, L.; Carlsson, S.B.; Junno, T.; Xu, H.; Montelius, L. Real time control of nanowire formation. Nanoscale Sci. Technol. 1998, 348, 19–22. [Google Scholar]

- Gazibegovic, S.; Car, D.; Zhang, H.; Balk, S.C.; Logan, J.A.; de Moor, M.W.A.; Cassidy, M.C.; Schmits, R.; Di, X.; Wang, G. Epitaxy of advanced nanowire quantum devices. Nature 2017, 548, 434–438. [Google Scholar] [CrossRef]

- Caroff, P.; Messing, M.E.; Borg, B.M.; Dick, K.A.; Deppert, K.; Wernersson, L.E. InSb heterostructure nanowires: MOVPE growth under extreme lattice mismatch. Nanotechnology 2009, 20, 495606. [Google Scholar] [CrossRef]

- Sadre-Momtaz, Z.; Servino, S.; Demontis, V.; Zannier, V.; Ercolani, D.; Rossi, F.; Rossella, F.; Sorba, L.; Beltram, F.; Roddaro, S. Orbital tuning of tunnel coupling in InAs/InP nanowire quantum dots. Nano Lett. 2020, 22, 1693–1699. [Google Scholar] [CrossRef] [PubMed]

- Cornia, S.; Rossella, F.; Demontis, V.; Zannier, V.; Beltram, F.; Sorba, L.; Affronte, M.; Ghirri, A. Microwave-assisted tunneling in hard-wall InAs/InP nanowire quantum dots. Sci. Rep. 2019, 9, 19523. [Google Scholar] [CrossRef]

- Rocci, M.; Rossella, F.; Gomes, U.P.; Zannier, V.; Rossi, F.; Ercolani, D.; Sorba, L.; Beltram, F.; Roddaro, S. Tunable esaki effect in catalyst-free InAs/GaSb core–shell nanowires. Nano Lett. 2016, 16, 7950–7955. [Google Scholar] [CrossRef]

- Battiato, S.; Wu, S.; Zannier, V.; Bertoni, A.; Goldoni, G.; Li, A.; Xiao, S.; Han, X.D.; Beltram, F.; Sorba, L.; et al. Polychromatic emission in a wide energy range from InP-InAs-InP multi-shell nanowires. Nanotechnology 2019, 30, 194004. [Google Scholar] [CrossRef] [PubMed]

- Monemar, B.; Ohlsson, B.J.; Gardner, N.F.; Samuelson, L. Chapter seven-nanowire-based visible light emitters, present status and outlook. Semicond. Semimet. 2016, 94, 227–271. [Google Scholar]

- Tatebayashi, J.; Kako, S.; Ho, J.; Ota, Y.; Iwamoto, S.; Arakawa, Y. Room-temperature lasing in a single nanowire with quantum dots. Nat. Photonics 2015, 9, 501–505. [Google Scholar] [CrossRef]

- Li, D.; Lan, C.; Manikandan, A.; Yip, S.; Zhou, Z.; Liang, X.; Shu, L.; Chueh, Y.L.; Han, N.; Ho, J.C. Ultra-fast photodetectors based on high-mobility indium gallium antimonide nanowires. Nat. Commun. 2019, 10, 1664. [Google Scholar] [CrossRef]

- Heiss, M.; Fontana, Y.; Gustafsson, A.; Wüst, G.; Magen, C.; O′Regan, D.D.; Luo, J.W.; Ketterer, B.; Conesa-Boj, S.; Kuhlmann, A.V.; et al. Self-assembled quantum dots in a nanowire system for quantum photonics. Nat. Mater. 2013, 12, 439–444. [Google Scholar] [CrossRef]

- Chen, R.; Lee, J.; Lee, W.; Li, D. Thermoelectrics of nanowires. Chem. Rev. 2019, 119, 9260–9302. [Google Scholar] [CrossRef] [PubMed]

- Prete, D.; Erdman, P.A.; Demontis, V.; Zannier, V.; Ercolani, D.; Sorba, L.; Beltram, F.; Rossella, F.; Taddei, F.; Roddaro, S. Thermoelectric conversion at 30 K in InAs/InP nanowire quantum dots. Nano Lett. 2019, 19, 3033–3039. [Google Scholar] [CrossRef] [PubMed]

- Demontis, V.; Rocci, M.; Donarelli, M.; Maiti, R.; Zannier, V.; Beltram, F.; Sorba, L.; Roddaro, S.; Rossella, F.; Baratto, C. Conductometric sensing with individual InAs nanowires. Sensors 2019, 19, 2994. [Google Scholar] [CrossRef] [PubMed]

- Nadj-Perge, S.; Frolov, S.M.; Bakkers, E.P.A.M.; Kouwenhoven, L.P. Spin-orbit qubit in a semiconductor nanowire. Nature 2010, 468, 1084–1087. [Google Scholar] [CrossRef]

- Nadj-Perge, S.; Frolov, S.M.; van Tilburg, J.W.W.; Danon, J.; Nazarov, Y.V.; Algra, R.; Bakkers, E.P.A.M.; Kouwenhoven, L.P. Disentangling the effects of spin-orbit and hyperfine interactions on spin blockade. Phys. Rev. B 2010, 81, 201305. [Google Scholar] [CrossRef]

- Wu, S.; Peng, K.; Battiato, S.; Zannier, V.; Bertoni, A.; Goldoni, G.; Xie, X.; Yang, J.; Xiao, S.; Qian, C.; et al. Anisotropies of the g-factor tensor and diamagnetic coefficient in crystal-phase quantum dots in InP nanowires. Nano Res. 2019, 12, 2842–2848. [Google Scholar] [CrossRef]

- Frolov, S.M.; Plissard, R.S.; Nadj-Perge, S.; Kouwenhoven, L.P.; Bakkers, E.P.A.M. Quantum computing based on semiconductor nanowires. Mrs Bull. 2013, 38, 809–815. [Google Scholar] [CrossRef]

- Zhang, H.; Liu, D.E.; Wimmer, M.; Kouwenhoven, L.P. Next steps of quantum transport in Majorana nanowire devices. Nat. Commun. 2019, 10, 5128. [Google Scholar] [CrossRef]

- Björk, M.; Fuhrer, A.; Hansen, A.; Larsson, M.; Jensen, L.E.; Samuelson, L. Tunable effective g factor in InAs nanowire quantum dots. Phys. Rev. B Condens. Matter Mater. Phys. 2005, 72, 201307. [Google Scholar] [CrossRef]

- Rocci, M.; Demontis, V.; Prete, D.; Ercolani, D.; Sorba, L.; Beltram, F.; Pennelli, G.; Roddaro, S.; Rossella, F. Suspended InAs nanowire-based devices for thermal conductivity measurement using the 3x method. J. Mater. Eng. Perform. 2018, 27, 6299–6305. [Google Scholar] [CrossRef]

- Arcangeli, A.; Rossella, F.; Tomadin, A.; Xu, J.; Ercolani, D.; Sorba, L.; Beltram, F.; Tredicucci, A.; Polini, M.; Roddaro, S. Gate-tunable spatial modulation of localized plasmon resonances. Nano Lett. 2016, 16, 5688–5693. [Google Scholar] [CrossRef]

- Lieb, J.; Demontis, V.; Prete, D.; Ercolani, D.; Zannier, V.; Sorba, L.; Ono, S.; Beltram, F.; Sacepe, B.; Rossella, F. Ionic-liquid gating of InAs nanowire-based field-effect transistors. Adv. Funct. Mater. 2019, 29, 1804378. [Google Scholar] [CrossRef]

- Prete, D.; Lieb, J.; Demontis, V.; Bellucci, L.; Tozzini, V.; Ercolani, D.; Zannier, V.; Sorba, L.; Ono, S.; Beltram, F.; et al. III-V semicondutor nanostructures and iontronics: InAs nanowire-based electric double layer field effect transistors. AIP Conf. Proc. 2019, 2145, 020003. [Google Scholar]

- Prete, D.; Demontis, V.; Zannier, V.; Rodriguez-Douton, M.J.; Guazzelli, L.; Beltram, F.; Sorba, L.; Rossella, F. Impact of electrostatic doping on carrier concentration and mobility in InAs nanowires. Nanotechnology 2021, 32, 145204. [Google Scholar] [CrossRef] [PubMed]

- Prete, D.; Dimaggio, E.; Demontis, V.; Zannier, V.; Rodriguez-Douton, M.J.; Guazzelli, L.; Beltram, F.; Sorba, L.; Pennelli, G.; Rossella, F. Electrostatic control of the thermoelectric figure of merit in Ion-gated nanotransistors. Adv. Func. Mat. 2021, 2104175. [Google Scholar] [CrossRef]

- Su, Z.; Tacla, A.B.; Hocevar, M.; Car, D.; Plissard, S.R.; Bakkers, E.P.A.M.; Daley, A.J.; Pekker, D.; Frolov, S.M. Andreev molecules in semiconductor nanowire double quantum dots. Nat. Commun. 2017, 8, 585. [Google Scholar] [CrossRef] [PubMed]

- Prada, E.; San-Jose, P.; de Moor, M.W.A.; Geresdi, A.; Lee, E.J.H.; Klinovaja, J.; Loss, D.; Nygård, J.; Aguado, R.; Kouwenhoven, L.P. From Andreev to Majorana bound states in hybrid superconductor-semiconductor nanowires. Nat. Rev. Phys. 2020, 2, 575–594. [Google Scholar] [CrossRef]

- Mauthe, S.; Baumgartner, Y.; Sousa, M.; Ding, Q.; Rossell, M.D.; Schenk, A.; Czornomaz, L.; Moselund, K.E. High-speed III-V nanowire photodetector monolithically integrated on Si. Nat. Commun. 2020, 11, 4565. [Google Scholar] [CrossRef] [PubMed]

- Assali, S.; Zardo, I.; Plissard, S.; Kriegner, D.; Verheijen, M.A.; Bauer, G.; Meijerink, A.; Belabbes, A.; Bechstedt, F.; Haverkort, J.E.M.; et al. Direct band gap wurtzite gallium phosphide nanowires. Nano Lett. 2013, 13, 1559–1563l. [Google Scholar] [CrossRef] [PubMed]

- Iorio, A.; Rocci, M.; Bours, L.; Carrega, M.; Zannier, V.; Sorba, L.; Roddaro, S.; Giazotto, F.; Strambini, E. Vectorial control of the spin–orbit interaction in suspended InAs nanowires. Nano Lett. 2019, 19, 652–657. [Google Scholar] [CrossRef]

- Wong-Leung, J.; Yang, I.; Li, Z.; Karuturi, S.K.; Fu, L.; Tan, H.H.; Jagadish, C. Engineering III–V semiconductor nanowires for device applications. Adv. Mater. 2019, 32, 1904359. [Google Scholar] [CrossRef] [PubMed]

- Kuykendall, T.; Pauzauskie, P.J.; Zhang, Y.; Goldberg, J.; Sirbuly, D.; Denlimger, J.; Yang, P. Crystallographic alignment of high-density gallium nitride nanowire arrays. Nat. Mater. 2004, 3, 524–528. [Google Scholar] [CrossRef] [PubMed]

- Mohan, P.; Motohisa, J.; Fukui, T. Fabrication of InP/InAs/InP core-multishell heterostructure nanowires by selective area metalorganic vapor phase epitaxy. Appl. Phys. Lett. 2006, 88, 133105. [Google Scholar] [CrossRef]

- Mårtensson, T.; Carlberg, P.; Borgström, M.; Montelius, L.; Seifert, W.; Samuelson, L. Nanowire arrays defined by nanoimprint lithography. Nano Lett. 2004, 4, 699. [Google Scholar] [CrossRef]

- Mårtensson, T.; Svensson, C.P.T.; Wacaser, B.A.; Larsson, M.W.; Seifert, W.; Deppert, K.; Gustafsson, A.; Wallenberg, L.R.; Samuelson, L. Epitaxial III-V nanowires on silicon. Nano Lett. 2004, 4, 1987–1990. [Google Scholar] [CrossRef]

- Tomioka, K.; Motohisa, J.; Hara, S.; Hiruma, K.; Fukui, T. GaAs/AlGaAs core multishell nanowire-based light-emitting diodes on Si. Nano Lett. 2010, 10, 1639–1644. [Google Scholar] [CrossRef] [PubMed]

- Paulitschke, P.; Keber, F.; Lebedev, A.; Stephan, J.; Lorenz, H.; Hasselmann, S.; Heinrich, D.; Weig, E.M. Ultraflexible nanowire array for label- and distortion-free cellular force tracking. Nano Lett. 2019, 19, 2207–2214. [Google Scholar] [CrossRef] [PubMed]

- Sekiguchi, H.; Kishino, K.; Kikuchi, A. Emission color control from blue to red with nanocolumn diameter of InGaN/GaN nanocolumn arrays grown on same substrate. Appl. Phys. Lett. 2010, 96, 23. [Google Scholar] [CrossRef]

- Giuntoni, I.; Geelhaar, L.; Bruns, J.; Riechert, H. Light coupling between vertical III-As nanowires and planar Si photonic waveguides for the monolithic integration of active optoelectronic devices on a Si platform. Opt. Express 2016, 24, 18417–18427. [Google Scholar] [CrossRef] [PubMed]

- Prokes, S.M.; Arnold, S. Synthesis of Si nanowires for MEMS cantilever sensor applications. In Proceedings of the SPIE 5593, Nanosensing: Materials and Devices, Bellingham, WA, USA, 29 December 2004. [Google Scholar]

- Hiruma, K.; Katsuyama, T.; Ogaw, K.; Koguchi, M.; Kakibayashi, H.; Morgan, P. Quantum size microcrystals grown using organometallic vapor phase epitaxy. Appl. Phys. Lett. 1991, 59, 431. [Google Scholar] [CrossRef]

- Sato, T.; Hiruma, K.; Shirai, M.; Tominaga, K.; Haraguchi, K.; Katsuyama, T.; Shimada, T. Site-controlled growth of nanowhiskers. Appl. Phys. Lett. 1995, 66, 159. [Google Scholar] [CrossRef]

- Hiruma, K.; Yazawa, M.; Katsuyama, T.; Ogawa, K.; Haraguchi, K.; Koguchi, M.; Kakibayashi, H. Growth and optical properties of nanometer-scale GaAs and InAs whiskers. J. Appl. Phys. 1995, 77, 447. [Google Scholar] [CrossRef]

- Detz, H. Lithography-free positioned GaAs nanowire growth with focused ion beam implantation of GaH. J. Vac. Sci. Technol. B 2017, 35, 011803. [Google Scholar] [CrossRef]

- Gibson, S.J.; LaPierre, R.R. Model of patterned self-assisted nanowire growth. Nanotechnology 2014, 25, 415304. [Google Scholar] [CrossRef]

- Heiss, M.; Russo-Averchi, E.; Dalmau-Mallorquí, A.; Tütüncüoğlu, G.; Matteini, F.; Rüffer, D.; Conesa-Boj, S.; Demichel, O.; Alarcon-Lladó, E.; Fontcuberta I Morral, A. III–V nanowire arrays: Growth and light interaction. Nanotechnology 2014, 25, 014015. [Google Scholar] [CrossRef]

- Dasgupta, N.P.; Sun, J.; Liu, C.; Brittman, S.; Andrews, S.C.; Lim, J.; Gao, H.; Yan, R.; Yang, P. Semiconductor Nanowires– + Synthesis, Characterization, and Applications. Adv. Mater. 2014, 6, 2137–2184. [Google Scholar] [CrossRef]

- Wagner, R. Whisker Technology; Levitt, A., Ed.; Academic: New York, NY, USA, 1969. [Google Scholar]

- Garnett, E.; Mai, L.; Yang, P. Introduction: 1D nanomaterials/nanowires. Chem. Rev. 2019, 119, 8955–8957. [Google Scholar] [CrossRef] [PubMed]

- Bellucci, S.; Chiaretti, M.; Onorato, P.; Rossella, F.; Grandi, M.S.; Galinetto, P.; Sacco, I.; Micciulla, F. Micro-Raman study of the role of sterilization on carbon nanotubes for biomedical applications. Nanomedicine 2010, 5, 209–215. [Google Scholar] [CrossRef] [PubMed]

- Dick, K.; Caroff, P. Metal-seeded growth of III–V semiconductor nanowires: Towards gold-free synthesis. Nanoscale 2014, 6, 3006–3021. [Google Scholar] [CrossRef] [PubMed]

- Heun, S.; Radha, B.; Ercolani, D.; Kulkarni, G.U.; Rossi, F.; Grillo, V.; Salviati, G.; Beltram, F.; Sorba, L. Pd-assisted growth of InAs nanowires. Cryst. Growth Des. 2010, 10, 4197–4202. [Google Scholar] [CrossRef]

- Adhikari, H.; McIntyre, P.C. Conditions for subeutectic growth of Ge nanowires by the vapor-liquid-solid mechanism. J. Appl. Phys. 2007, 102, 094311. [Google Scholar] [CrossRef]

- Kamins, T.I.; Stanley Williams, R.; Basile, D.P.; Hesjedal, T.; Harris, J.S. Ti-catalyzed Si nanowires by chemical vapor deposition: Microscopy and growth mechanisms. J. Appl. Phys. 2001, 89, 1008. [Google Scholar] [CrossRef]

- Hiruma, K.; Yazawa, M.; Haraguchi, K.; Ogawa, K.; Katsuyama, T.; Koguchi, M.; Kakibayashi, H. GaAs free-standing quantum-size wires. J. Appl. Phys. 1993, 7, 3162. [Google Scholar] [CrossRef]

- Guo, Y.N.; Zou, J.; Paladugu, M.; Wang, H.; Gao, Q.; Tan, H.H.; Jagadish, C. Structural characteristics of GaSb/GaAs nanowire heterostructures grown by metal-organic chemical vapor deposition. Appl. Phys. Lett. 2006, 89, 231917. [Google Scholar] [CrossRef]

- Morales, A.M.; Lieber, C.M. A laser ablation method for the synthesis of crystalline semiconductor nanowires. Science 1998, 279, 208–211. [Google Scholar] [CrossRef]

- Wu, Z.H.; Mei, X.Y.; Kim, D.; Blumin, M.; Ruda, H.E. Growth of Au-catalyzed ordered GaAs nanowire arrays by molecular-beam epitaxy. Appl. Phys. Lett. 2002, 81, 5177. [Google Scholar] [CrossRef]

- Xu, T.; Dick, K.A.; Plissard, S.R.; Nguyen, T.H.; Makoudi, Y.; Berthe, M.; Nys, J.-P.; Wallart, X.; Grandidier, B.; Caroff, P. Faceting, composition and crystal phase evolution in III–V antimonide nanowire heterostructures revealed by combining microscopy techniques. Nanotechnology 2012, 23, 095702. [Google Scholar] [CrossRef]

- Jensen, L.E.; Björk, M.T.; Jeppesen, S.; Persson, A.I.; Ohlsson, B.J.; Samuelson, L. Role of surface diffusion in chemical beam epitaxy of InAs nanowires. Nano Lett. 2004, 4, 1961–1964. [Google Scholar] [CrossRef]

- Cui, Y.; Lauhon, L.J.; Gudiksen, M.S.; Wang, J.; Lieber, C.M. Diameter-controlled synthesis of single-crystal silicon nanowires. Appl. Phys. Lett. 2001, 78, 2214. [Google Scholar] [CrossRef]

- Dresselhaus, M.S.; Ming Lin, Y.; Rabin, O.; Black, M.R.; Kong, J.; Dresselhaus, J. Springer Handbook of Nanotechnology; Springer: Berlin/Heidelberg, Germany, 2004; p. 99. [Google Scholar]

- Yan, Z.X.; Milnes, A.G. The electrochemical society, find out more deep level transient spectroscopy of silver and gold levels in LEC grown gallium arsenide. J. Electrochem. Soc. 1982, 129, 1353. [Google Scholar] [CrossRef]

- Cheze, C.; Geelhaar, L.; Brandt, O.; Weber, W.M.; Riechert, H.; Münch, S.; Rothemund, R.; Reitzenstein, S.; Forchel, A.; Kehagias, T.; et al. Direct comparison of catalyst-free and catalyst-induced GaN nanowires. Nano Res. 2010, 3, 528–536. [Google Scholar] [CrossRef]

- Mandl, B.; Stangl, J.; Hilner, E.; Zakharov, A.A.; Hillerich, K.; Dey, A.W.; Samuelson, L.; Bauer, G.; Deppert, K.; Mikkelsen, A. Growth mechanism of self-catalyzed group III−V nanowires. Nano Lett. 2010, 10, 4443–4449. [Google Scholar] [CrossRef]

- Renard, V.T.; Jublot, M.; Gergaud, P.; Cherns, P.; Rouchon, D.; Chabli, A.; Jousseaume, V. Catalyst preparation for CMOS-compatible silicon nanowire synthesis. Nat. Nanotechnol. 2009, 4, 654–657. [Google Scholar] [CrossRef]

- Gomes, U.P.; Ercolani, D.; Zannier, V.; David, J.; Gemmi, M.; Beltram, F.; Sorba, L. Nucleation and growth mechanism of self-catalyzed InAs nanowires on silicon. Nanotechnology 2016, 27, 255601. [Google Scholar] [CrossRef] [PubMed]

- Gao, L.; Woo, R.L.; Liang, B.; Pozuelo, M.; Prikhodko, S.; Jackson, M.; Goel, N.; Hudait, M.K.; Huffaker, D.L.; Goorsky, M.S.; et al. Self-catalyzed epitaxial growth of vertical indium phosphide nanowires on silicon. Nano Lett. 2009, 9, 2223–2228. [Google Scholar] [CrossRef] [PubMed]

- Ishiyama, T.; Nakagawa, S.; Wakamatsu, T. Growth of epitaxial silicon nanowires on a Si substrate by a metal-catalyst-free process. Sci. Rep. 2018, 6, 30608. [Google Scholar] [CrossRef]

- Ikejiri, K.; Noborisaka, J.; Hara, S.; Motohisa, J.; Fukui, T. Mechanism of catalyst-free growth of GaAs nanowires by selective area MOVPE. J. Cryst. Growth 2007, 298, 616–619. [Google Scholar] [CrossRef]

- Gomes, U.P.; Ercolani, D.; Zannier, V.; Battiato, S.; Ubyivovk, E.; Mikhailovskii, V.; Murata, Y.; Heun, S.; Beltram, F.; Sorba, L. Heterogeneous nucleation of catalyst-free InAs nanowires on silicon. Nanotechnology 2017, 28, 1255–1258. [Google Scholar] [CrossRef] [PubMed]

- Ho, S.T.; Wang, C.Y.; Liu, H.L.; Lin, H.N. Catalyst-free selective-area growth of vertically aligned zinc oxide nanowires. Chem. Phys. Lett. 2008, 463, 141–144. [Google Scholar] [CrossRef]

- Koblmüller, G.; Hertenberger, S.; Vizbara, S.K.; Bichler, M.; Bao, F.; Zhang, J.P.; Abstreiter, G. Self-induced growth of vertical free-standing InAs nanowires on Si(111) by molecular beam epitaxy. Nanotechnology 2010, 21, 365601–365602. [Google Scholar] [CrossRef]

- Tomioka, K.; Motohisa, J.; Hara, S.; Fukui, T. Control of InAs nanowire growth directions on Si. Nano Lett. 2008, 8, 3475–3480. [Google Scholar] [CrossRef]

- Yuan, X.; Pan, D.; Zhou, Y.; Zhang, X.; Peng, K.; Zhao, B.; Deng, M.; He, J.; Tan, H.H.; Jagadish, C. Selective area epitaxy of III–V nanostructure arrays and networks: Growth, applications, and future directions. Appl. Phys. Rev. 2021, 8, 021302. [Google Scholar] [CrossRef]

- Dalacu, D.; Kam, A.; Austing, D.G.; Wu, X.; Lapointe, J.; Aers, G.C.; Poole, P.J. Selective-area vapour–liquid–solid growth of InP nanowires. Nanotechnology 2009, 20, 395602. [Google Scholar] [CrossRef]

- Kawaguchi, K.; Sudo, H.; Matsuda, M.; Ekawa, M.; Yamamoto, T.; Arakawa, Y. Position-controlled InP nanowires with 10–100 μm pitches using Au-deposited SiO2/InP patterned substrates. Appl. Phys. Lett. 2014, 104, 063102. [Google Scholar] [CrossRef]

- Otnes, G.; Heurlin, M.; Graczyk, M.; Wallentin, J.; Jacobsson, D.; Berg, A.; Maximov, I.; Borgström, M.T. Strategies to obtain pattern fidelity in nanowire growth from large-area surfaces patterned using nanoimprint lithography. Nano Res. 2016, 9, 2852–2861. [Google Scholar] [CrossRef]

- Fan, H.J.; Werner, P.; Zacharias, M. Semiconductor nanowires: From self-organization to patterned growth. Small 2006, 2, 700–717. [Google Scholar] [CrossRef]

- Hochbaum, A.I.; Fan, R.; He, R.; Yang, P. Controlled growth of Si nanowire arrays for device integration. Nano Lett. 2005, 5, 457–460. [Google Scholar] [CrossRef]

- Mårtensson, T.; Borgstrom, M.; Seifert, W.; Ohlsson, B.J.; Samuelson, L. Fabrication of individually seeded nanowire arrays by vapour–liquid–solid growth. Nanotechnology 2003, 14, 1255–1258. [Google Scholar] [CrossRef]

- Pierret, A.; Hocevar, M.; Diedenhofen, S.L.; Algra, R.E.; Vlieg, E.; Timmering, E.C.; Verschuuren, M.A.; Immink, G.W.G.; Verheijen, M.A.; Bakkers, E.P.A.M. Generic nano-imprint process for fabrication of nanowire arrays. Nanotechnology 2010, 21, 065305. [Google Scholar] [CrossRef]

- Manfrinato, V.R.; Zhang, L.; Su, D.; Duan, H.; Hobbs, R.G.; Stach, E.A.; Berggren, K.K. Resolution limits of electron-beam lithography toward the atomic scale. Nano Lett. 2013, 13, 1555–1558. [Google Scholar] [CrossRef] [PubMed]

- Caridad, J.M.; McCloskey, D.; Rossella, F.; Bellani, F.; Donegan, J.F.; Krstic, V. Effective wavelength scaling of and damping in plasmonic helical antennae. ACS Photonics 2015, 2, 675–679. [Google Scholar] [CrossRef]

- Medeghini, F.; Crut, A.; Gandolfi, M.; Rossella, F.; Maioli, P.; Vallée, F.; Banfi, F.; Del Fatti, N. Controlling the quality factor of a single acoustic nanoresonator by tuning its morphology. Nano Lett. 2018, 18, 5159–5166. [Google Scholar] [CrossRef] [PubMed]

- Borgstrom, M.T.; Immink, G.; Ketelaars, B.; Algra, R.; Bakkers, E.P.A.M. Synergetic nanowire growth. Nat. Nanotechnol. 2007, 2, 541–544. [Google Scholar] [CrossRef] [PubMed]

- Kelrich, A.; Calahorra, Y.; Greenberg, Y.; Gavrilov, A.; Cohen, S.; Ritter, D. Shadowing and mask opening effects during selective-area vapor–liquid–solid growth of InP nanowires by metalorganic molecular beam epitaxy. Nanotechnology 2013, 24, 475302. [Google Scholar] [CrossRef]

- Calahorra, Y.; Greenberg, Y.; Cohen, S.; Ritter, D. Native-oxide-based selective area growth of InP nanowires via metal–organic molecular beam epitaxy mediated by surface diffusion. Nanotechnology 2012, 23, 245603. [Google Scholar] [CrossRef]

- Schift, H.; Kristensen, A. Handbook of Nanotechnology; Springer: Berlin/Heidelberg, Germany, 2007; pp. 239–278. [Google Scholar]

- Chou, S.Y.; Krauss, P.R.; Renstrom, P.J. Imprint lithography with 25-nanometer resolution. Science 1996, 272, 85–87. [Google Scholar] [CrossRef]

- Traub, M.C.; Longsine, W.; Truskett Van, N. Advances in nanoimprint lithography. Annu. Rev. Chem. Biomol. Eng. 2016, 7, 583–604. [Google Scholar] [CrossRef]

- Anttu, N.; Dagyté, V.; Zeng, X.; Otnes, G.; Borgström, M. Absorption and transmission of light in III–V nanowire arrays for tandem solar cell applications. Nanotechnology 2017, 28, 205203. [Google Scholar] [CrossRef]

- Anttu, N.; ABramd, A.; Asoli, D.; Heurlin, M.; Åber, I.; Samuelson, L.; Borgström, M. Absorption of light in InP nanowire arrays. Nano Res. 2014, 7, 816–823. [Google Scholar] [CrossRef]

- Messing, M.E.; Hillerich, K.; Johansson, J.; Deppert, K.; Dick, K.A. The use of gold for fabrication of nanowire structures. Gold Bull. 2009, 42, 3. [Google Scholar] [CrossRef]

- Tomioka, K.; Ikejiri, K.; Tanaka, T.; Motohisa, J.; Hara, S.; Hiruma, K.; Fukui, T. Selective-area growth of III-V nanowires and their applications. J. Mater. Res. 2011, 26, 2127–2141. [Google Scholar] [CrossRef]

- Zi, Y.; Suslov, S.; Yang, C. Understanding self-catalyzed epitaxial growth of III–V nanowires toward controlled synthesis. Nano Lett. 2017, 17, 1167–1173. [Google Scholar] [CrossRef] [PubMed]

- Borg, M.; Schmid, H.; Moselund, K.E.; Cutaia, D.; Riel, H. Mechanisms of template-assisted selective epitaxy of InAs nanowires on Si. J. Appl. Phys. 2015, 117, 144303. [Google Scholar] [CrossRef]

- Mohan, P.; Motohisa, J.; Fukui, T. Controlled growth of highly uniform, axial/radial direction-defined, individually addressable InP nanowire arrays. Nanotechnology 2005, 16, 2903–2907. [Google Scholar] [CrossRef]

- Bauer, B.; Rudolph, A.; Soda, M.; Fontcuberta I Morral, A.; Zweck, J.; Schuh, D.; Reiger, E. Position controlled self-catalyzed growth of GaAs nanowires by molecular beam epitaxy. Nanotechnology 2010, 21, 435601. [Google Scholar] [CrossRef] [PubMed]

- Ermez, S.; Jones, E.J.; Crawford, S.C.; Gradecak, S. Self-seeded growth of GaAs nanowires by metal–organic chemical vapor deposition. Growth Des. 2015, 15, 2768–2774. [Google Scholar] [CrossRef]

- Matteini, F.; Tutuncuoglu, G.; Mikulik, D.; Vukajlovic-Plestina, J.; Potts, H.; Leran, J.-B.; Carter, W.C.; Fontcuberta I Morral, A. Wetting of Ga on SiOx and its impact on GaAs nanowire growth. Cryst. Growth Des. 2016, 16, 5781–5786. [Google Scholar] [CrossRef]

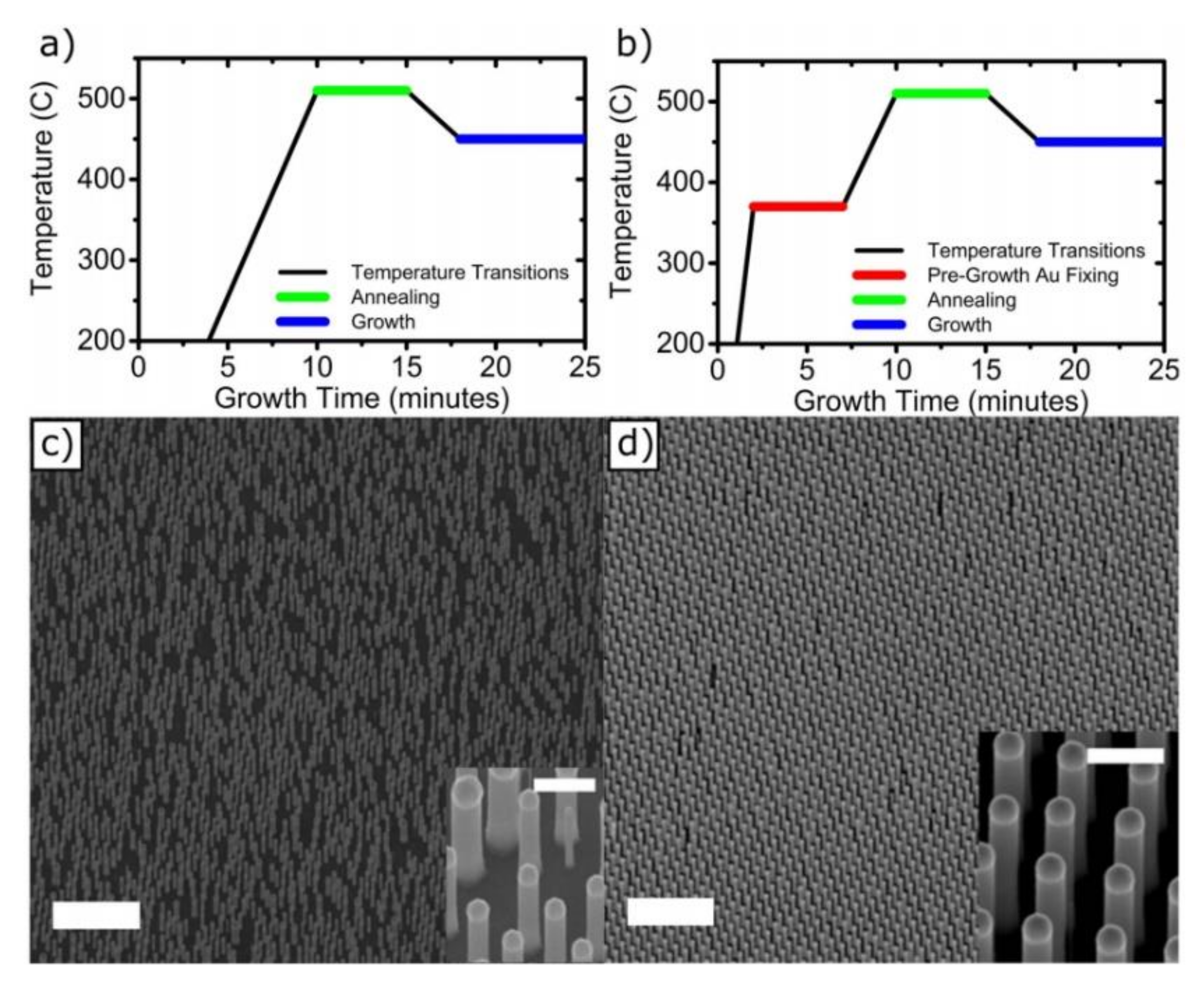

- Plissard, S.; Larrieu, G.; Wallart, X.; Caroff, P. High yield of self-catalyzed GaAs nanowire arrays grown on silicon via gallium droplet positioning. Nanotechnology 2011, 22, 275602. [Google Scholar] [CrossRef] [PubMed]

- Shumann, T.; Gotschke, T.; Limbach, F.; Stoica, T.; Calarco, R. Selective-area catalyst-free MBE growth of GaN nanowires using a patterned oxide layer. Nanotechnology 2011, 22, 095603. [Google Scholar] [CrossRef]

- Tomioka, K.; Izhizaka, F.; Fukui, T. Selective-area growth of InAs nanowires on Ge and vertical transistor application. Nano Lett. 2015, 15, 7253–7257. [Google Scholar] [CrossRef]

- Kreuse, J.E.; Lymperakis, L.; Eftychis, S.; Adikimenakis, A.; Doundoulakis, G.; Tsagaraki, K.; Androulidaki, M.; Olziersky, A.; Dimitrakis, P.; Ioannou-Sougleridis, V.; et al. Selective-area growth of GaN nanowires on SiO2-masked Si (111) substrates by molecular beam epitaxy. J. Appl. Phys. 2016, 119, 224305. [Google Scholar] [CrossRef]

- Bassett, K.P.; Mohseni, P.K.; Li, X. Evolution of GaAs nanowire geometry in selective area epitaxy. Appl. Phys. Lett. 2015, 106, 133102. [Google Scholar] [CrossRef]

- Ghalamestani, S.G.; Johansson, S.; Borg, B.M.; Lind, E.; Dick, K.A.; Wernersson, L.E. Uniform and position-controlled InAs nanowires on 2” Si substrates for transistor applications. Nanotechnology 2012, 23, 015302. [Google Scholar] [CrossRef]

- Munshi, A.M.; Dheeraj, D.L.; Fauske, V.T.; Kim, D.C.; Huh, J.; Reinertsen, J.F.; Ahtapodov, L.; Lee, K.D.; Heidari, B.; van Helvoort, A.T.J.; et al. Position-controlled uniform GaAs nanowires on silicon using nanoimprint lithography. Nano Lett. 2014, 14, 960–966. [Google Scholar] [CrossRef] [PubMed]

- Madaria, A.R.; Yao, M.; Chi, C.; Huang, N.; Lin, C.; Li, R.; Povinelli, M.L.; Dapkus, P.D.; Zhou, C. Toward optimized light utilization in nanowire arrays using scalable nanosphere lithography and selected area growth. Nano Lett. 2012, 12, 2839–2845. [Google Scholar] [CrossRef]

- Fan, H.J.; Fuhrmann, B.; Scholz, R.; Syrowatka, F.; Dadgar, A.; Krost, A.; Zacharias, M. Well-ordered ZnO nanowire arrays on GaN substrate fabricated via nanosphere lithography. J. Cryst. Growth 2006, 287, 34–38. [Google Scholar] [CrossRef]

- Fuhrmann, B.; Leipner, H.S.; Höche, H.; Schubert, L.; Werner, P.; Gösele, U. Ordered arrays of silicon nanowires produced by nanosphere lithography and molecular beam epitaxy. Nano Lett. 2005, 5, 2524–2527. [Google Scholar] [CrossRef]

- Colson, P.; Henrist, C.; Cloots, R. Nanosphere lithography: A powerful method for the controlled manufacturing of nanomaterials. J. Nanomater. 2013, 2013, 948510. [Google Scholar] [CrossRef]

- Rybczynski, J.; Banerjee, D.; Kosiorek, A.; Giersig, M.; Ren, Z.F. Formation of super arrays of periodic nanoparticles and aligned ZnO nanorods−Simulation and experiments. Nano Lett. 2004, 4, 2037. [Google Scholar] [CrossRef]

- Park, M.; Harrison, C.; Chaikin, P.M.; Register, R.A.; Adamson, R.H. Block copolymer lithography: Periodic arrays of ~1011 holes in 1 square centimeter. Science 1997, 276, 1401. [Google Scholar] [CrossRef]

- Huang, Y.; Kim, T.W.; Xiong, S.; Mawst, L.J.; Kuech, T.F.; Nealey, P.F.; Dai, Y.; Wang, Z.; Guo, W.; Forbes, D.; et al. InAs nanowires grown by metal–organic vapor-phase epitaxy (MOVPE) employing PS/PMMA diblock copolymer nanopatterning. Nano Lett. 2013, 13, 5979–5984. [Google Scholar] [CrossRef] [PubMed]

- Löfstrand, A.; Svensson, J.; Wernersson, L.; Maximov, I. Feature size control using surface reconstruction temperature in block copolymer lithography for InAs nanowire growth. Nanotechnology 2020, 31, 325303. [Google Scholar] [CrossRef] [PubMed]

- Coulon, P.-M.; Damilano, B.; Alloing, B.; Chausse, P.; Walde, S.; Enslin, J.; Armstrong, R.; Vézian, S.; Hagedorn, S.; Wernicke, T.; et al. Displacement Talbot lithography for nano-engineering of III-nitride materials. Microsyst. Nanoeng. 2019, 5, 52. [Google Scholar] [CrossRef]

- Patorski, K. The self-imaging phenomenon and its applications. Prog. Opt. 1989, 27, 1–108. [Google Scholar]

- Hersee, S.; Sun, X.; Wang, X. The controlled growth of GaN nanowires. Nano Lett. 2006, 6, 1808–1811. [Google Scholar] [CrossRef] [PubMed]

- Brueck, S.R.J. Optical and interferometric lithography-nanotechnology enablers. Proc. IEEE 2005, 93, 1704–1721. [Google Scholar] [CrossRef]

- Lin, S.K.; Crawford, S.; Hoberfehlner, G.; Gradečak, S. Controlled Modulation of Diameter and Composition along Individual III–V Nitride Nanowires. Nano Lett. 2013, 13, 331–336. [Google Scholar]

- Schmidt, V.; Wittemann, J.V.; Senz, S.; Gösele, U. Silicon nanowires: A review on aspects of their growth and their electrical properties. Adv. Mater. 2009, 21, 2681–2702. [Google Scholar] [CrossRef]

- Wu, Y.; Yang, P. Direct observation of vapor−liquid−solid nanowire growth. J. Am. Chem. Soc. 2001, 123, 3165–3166. [Google Scholar] [CrossRef]

- Tersoff, J. Stable self-catalyzed growth of III–V nanowires. Nano Lett. 2015, 15, 6609–6613. [Google Scholar] [CrossRef] [PubMed]

- Jacobsson, D.; Panciera, F.; Tersoff, J.; Reuter, M.C.; Lehman, S.; Hofmann, S.; Dick, K.A.; Ross, F.M. Interface dynamics and crystal phase switching in GaAs nanowires. Nature 2016, 531, 317–322. [Google Scholar] [CrossRef]

- Wang, J.; Plissard, S.; Verheijen, M.A.; Feiner, L.F.; Cavalli, A.; Bakkers, E.P.A.M. Reversible switching of InP nanowire growth direction by catalyst engineering. Nano Lett. 2013, 13, 3802–3806. [Google Scholar] [CrossRef]

- Del Giudice, F.; Becker, J.; de Rose, C.; Döblinger, M.; Suomenniemi, L.; Treu, J.; Riedl, H.; Finley, J.J.; Koblmüller, J. Ultrathin catalyst-free InAs nanowires on silicon with distinct 1D sub-band transport properties. Nanoscale 2020, 42, 21857–21868. [Google Scholar] [CrossRef]

- Kim, W.; Dubrovskii, W.G.; Vukajlovic-Plestina, J.; Tütüncüoglu, G.; Francaviglia, L.; Güniat, L.; Potts, H.; Friedl, M.; Leran, J.B.; Fontcuberta I Morral, A. Bistability of contact angle and its role in achieving quantum-thin self-assisted GaAs nanowires. Nano Lett. 2018, 18, 49–57. [Google Scholar] [CrossRef] [PubMed]

- Cavalli, A.; Cui, Y.; Kölling, S.; Verheijen, M.; Plissard, S.R.; Wang, J.; Koenraad, P.M.; Haverkort, J.E.M.; Bakkers, E.P.A.M. Influence of growth conditions on the performance of InP nanowire solar cells. Nanotechnology 2016, 27, 454003. [Google Scholar] [CrossRef]

- Melechko, A.V.; McKnight, T.E.; Hensley, D.K.; Guillorn, M.A.; Borisevich, A.Y.; Merkulov, V.I.; Lowndes, D.H.; Simpson, M.L. Large-scale synthesis of arrays of high-aspect-ratio rigid vertically aligned carbon nanofibres. Nanotechnology 2003, 14, 1029. [Google Scholar] [CrossRef]

- Ng, H.T.; Han, J.; Yamada, T.; Nguyen, P.; Chen, Y.P.; Meyyappan, M. Single crystal nanowire vertical surround-gate field-effect transistor. Nano Lett. 2004, 4, 1247–1252. [Google Scholar] [CrossRef]

- Greyson, E.C.; Babayan, Y.; Odom, T.W. Directed growth of ordered arrays of small-diameter ZnO nanowires. Adv. Mater. 2004, 16, 1348. [Google Scholar] [CrossRef]

- Scaccabarozzi, A.; Cattoni, A.; Patriarche, G.; Travers, L.; Collin, S.; Harmand, J.; Glas, S.; Oehler, F. Stable and high yield growth of GaP and In0.2Ga0.8As nanowire arrays using In as a catalyst. Nanoscale 2020, 35, 18240–18248. [Google Scholar] [CrossRef] [PubMed]

- Mandl, B.; Dey, A.; Stangl, J.; Cantoro, M.; Wernersson, L.; Bauer, G.; Samuelson, L.; Deppert, K.; Thelander, C. Self-seeded, position-controlled InAs nanowire growth on Si: A growth parameter study. J. Cryst. Growth 2011, 334, 51–56. [Google Scholar] [CrossRef]

- Hertenberger, S.; Rudolph, D.; Bichler, M.; Finley, J.J.; Abstreiter, G.; Koblmüller, G. Growth kinetics in position-controlled and catalyst-free InAs nanowire arrays on Si(111) grown by selective area molecular beam epitaxy. J. Appl. Phys. 2010, 108, 114316. [Google Scholar] [CrossRef]

- Schroth, P.; Humaidi, M.A.; Feigl, L.; Jakob, J.; Hassan, A.A.; Davtyan, A.; Küpers, H.; Tahraoui, A.; Geelhaar, L.; Pietsch, U.; et al. Impact of the shadowing effect on the crystal structure of patterned self-catalyzed gaas nanowires. Nano Lett. 2019, 19, 4263–4271. [Google Scholar] [CrossRef]

- Sibirev, N.V.; Tchernycheva, M.; Timofeeva, M.A.; Harmand, J.C.; Cirlin, G.E.; Dubrovskii, V.G. Influence of shadow effect on the growth and shape of InAs nanowires. J. Appl. Phys. 2012, 111, 104317. [Google Scholar] [CrossRef]

- Madsen, M.H.; Krogstrup, P.; Johnson, E.; Venkatesan, S.; Mühlbauer, E.; Scheu, C.; Sørensen, C.B.; Nygård, J. Experimental determination of adatom diffusion lengths for growth of InAs nanowires. J. Cryst. Growth 2013, 364, 16–22. [Google Scholar] [CrossRef]

- Plissard, S.R.; Slapak, D.R.; Verheijen, M.A.; Hocevar, M.; Immink, G.W.G.; van Weperen, I.; Nadj-Perge, S.; Frolov, S.M.; Kouwenhoven, L.P.; Bakkers, E.P.A.M. From InSb nanowires to nanocubes: Looking for the sweet spot. Nano Lett. 2012, 12, 1794–1798. [Google Scholar] [CrossRef][Green Version]

- Persson, A.I.; Fröberg, L.E.; Jeppesen, S.; Björk, M.T.; Samuelson, L. Surface diffusion effects on growth of nanowires by chemical beam epitaxy. J. Appl. Phys. 2007, 101, 034313. [Google Scholar] [CrossRef]

- Colombo, C.; Spirkoska, D.; Frimmer, M.; Abstreiter, G.; Fontcuberta I Morral, A. Ga-assisted catalyst-free growth mechanism of GaAs nanowires by molecular beam epitaxy. Phys. Rev. B 2008, 77, 155326. [Google Scholar] [CrossRef]

- Küpers, H.; Lewis, R.B.; Tahraoui, A.; Matalla, M.; Krüger, O.; Bastiman, F.; Riechert, H.; Geelhaar, L. Diameter evolution of selective area grown Ga-assisted GaAs nanowires. Nano Res. 2018, 11, 2885–2893. [Google Scholar] [CrossRef]

- Zagaglia, L.; Demontis, V.; Rossella, F.; Floris, F. Semiconductor nanowire arrays for optical sensing: A numerical insight on the impact of array periodicity and density. Nanotechnology 2021, 32, 335502. [Google Scholar] [CrossRef]

- Zhang, G.; Sasaki, S.; Tateno, K.; Gotoh, H.; Sogawa, T. Au-free InAs nanowires grown in In-particle-assisted vapor-liquid-solid mode: Growth, structure, and electrical property. AIP Adv. 2013, 3, 052107. [Google Scholar] [CrossRef]

- Tornberb, M.; Maliakkal, C.B.; Jacobsson, D.; Dick, K.A.; Johansson, J. Limits of III–V nanowire growth based on droplet dynamics. J. Phys. Chem. Lett. 2020, 11, 2949–2954. [Google Scholar] [CrossRef] [PubMed]

- Rudolph, D.; Hertenberger, S.; Bolte, S.; Paosangthong, W.; Spirkoska, D.; Döblinger, M.; Bichler, M.; Finley, J.J.; Abstreiter, G.; Koblmüller, G. Direct observation of a noncatalytic growth regime for gaas nanowires. Nano Lett. 2011, 11, 3848–3854. [Google Scholar] [CrossRef] [PubMed]

- Sutter, E.; Sutter, P. Phase diagram of nanoscale alloy particles used for vapor–liquid–solid growth of semiconductor nanowires. Nano Lett. 2011, 8, 411–414. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Demontis, V.; Zannier, V.; Sorba, L.; Rossella, F. Surface Nano-Patterning for the Bottom-Up Growth of III-V Semiconductor Nanowire Ordered Arrays. Nanomaterials 2021, 11, 2079. https://doi.org/10.3390/nano11082079

Demontis V, Zannier V, Sorba L, Rossella F. Surface Nano-Patterning for the Bottom-Up Growth of III-V Semiconductor Nanowire Ordered Arrays. Nanomaterials. 2021; 11(8):2079. https://doi.org/10.3390/nano11082079

Chicago/Turabian StyleDemontis, Valeria, Valentina Zannier, Lucia Sorba, and Francesco Rossella. 2021. "Surface Nano-Patterning for the Bottom-Up Growth of III-V Semiconductor Nanowire Ordered Arrays" Nanomaterials 11, no. 8: 2079. https://doi.org/10.3390/nano11082079

APA StyleDemontis, V., Zannier, V., Sorba, L., & Rossella, F. (2021). Surface Nano-Patterning for the Bottom-Up Growth of III-V Semiconductor Nanowire Ordered Arrays. Nanomaterials, 11(8), 2079. https://doi.org/10.3390/nano11082079