Interface Optimization and Transport Modulation of Sm2O3/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer

Abstract

:1. Introduction

2. Materials and Methods

3. Results and Discussion

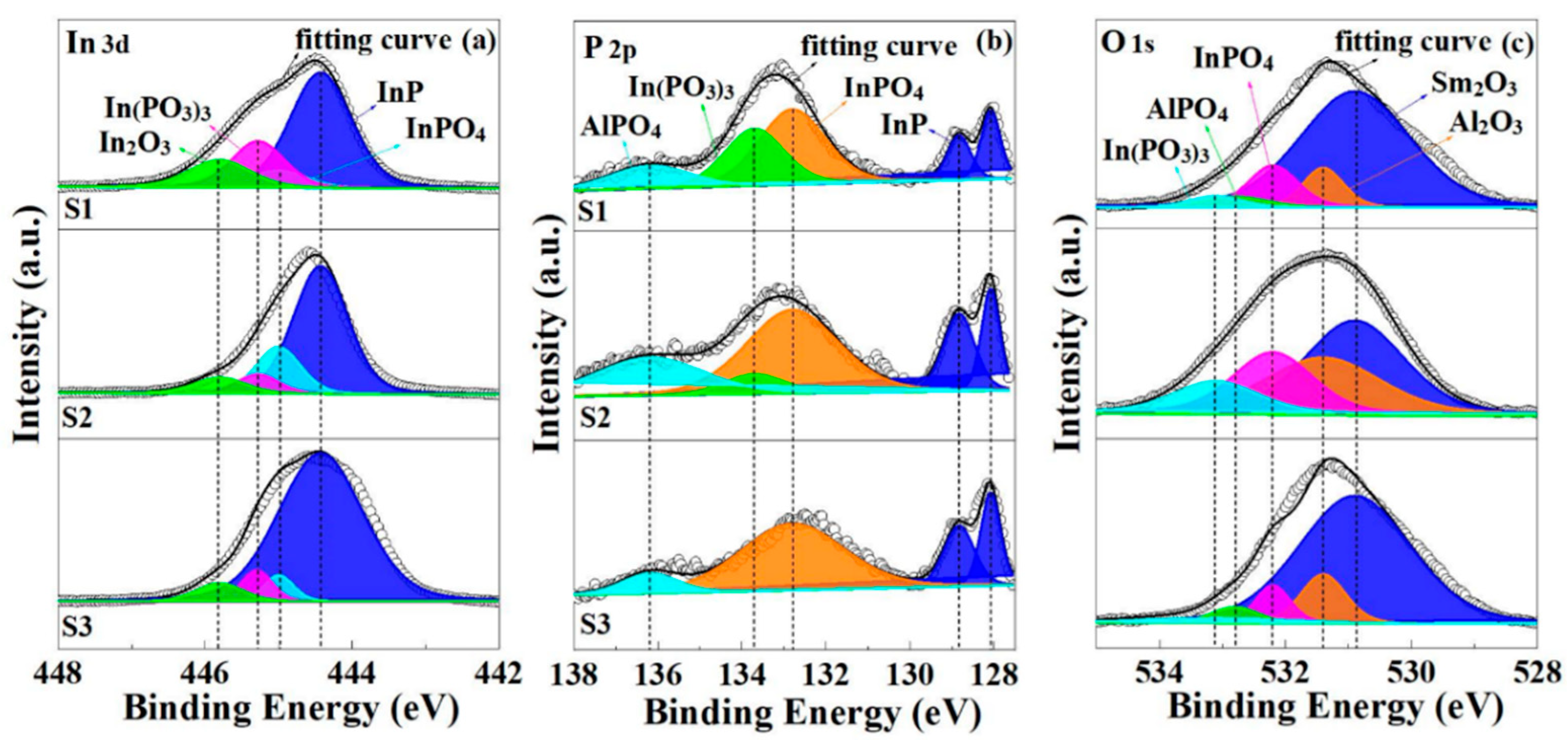

3.1. XPS Analyses

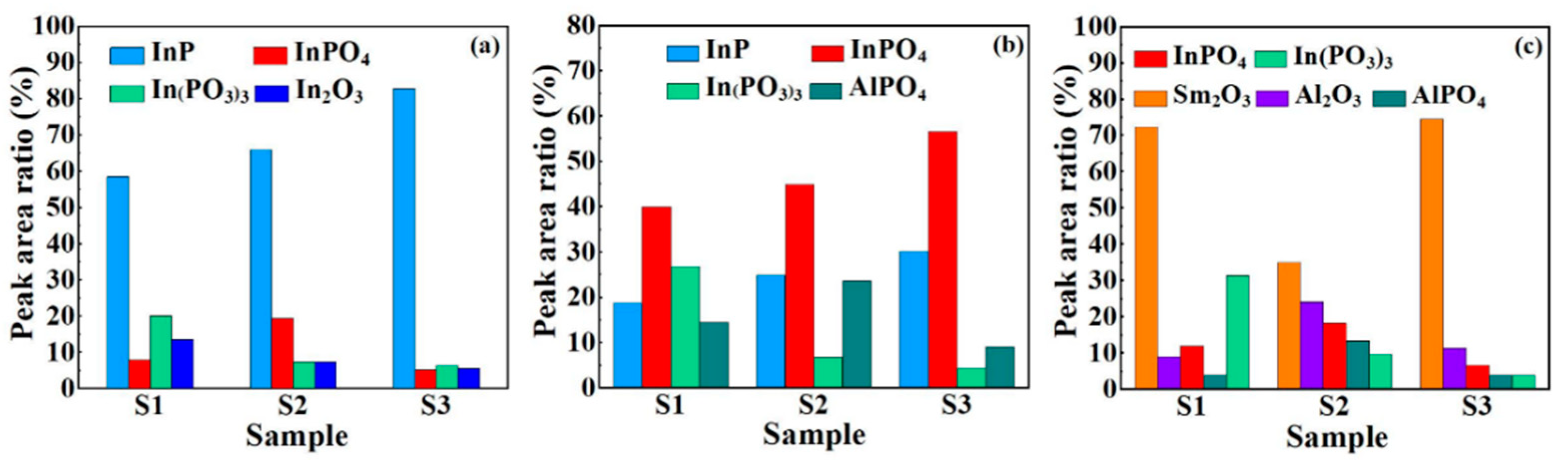

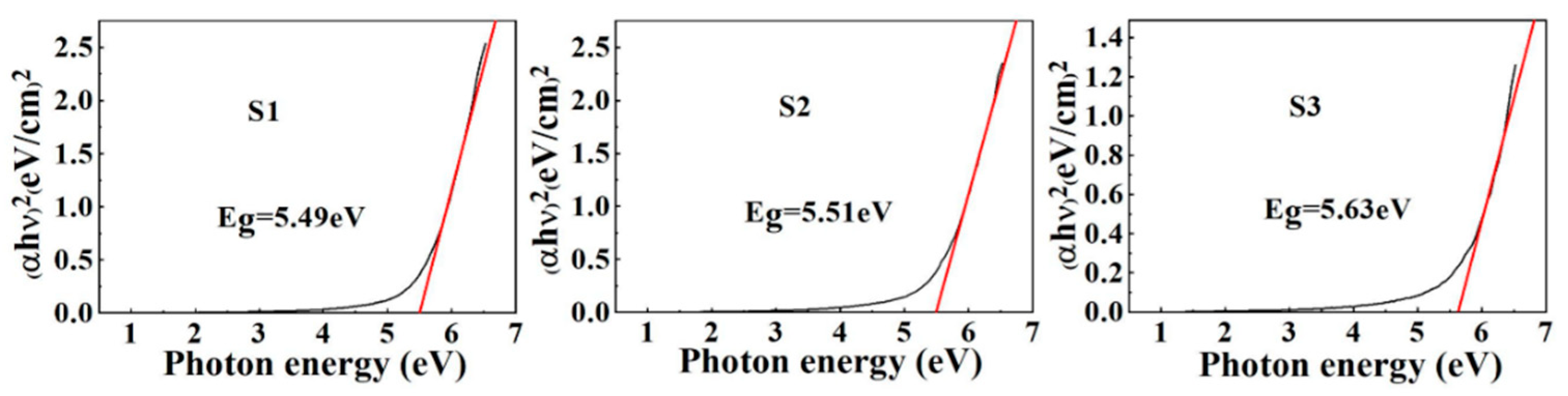

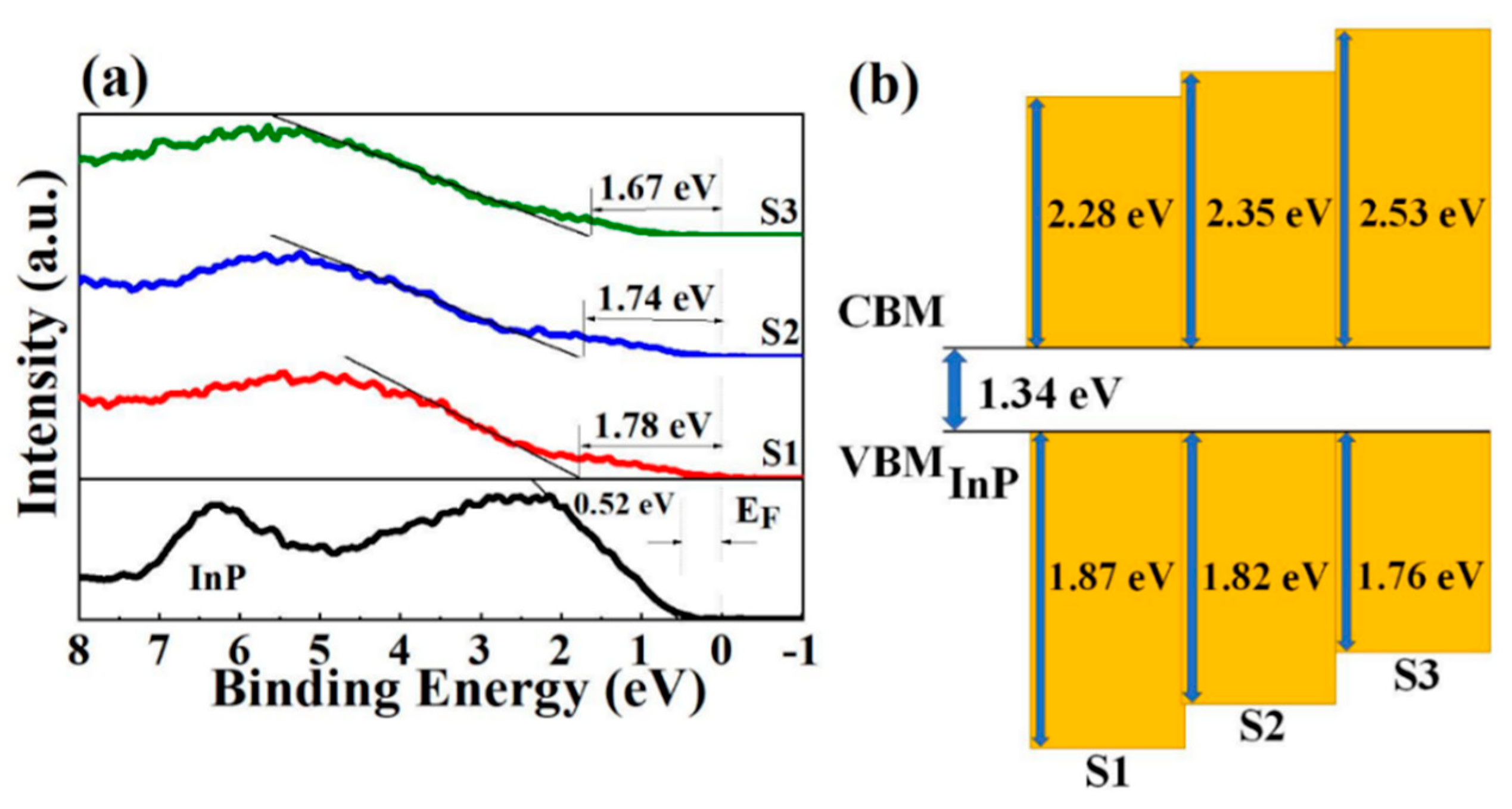

3.2. Band Alignment Characteristics

3.3. Electrical Properties of InP-MOS Capacitors

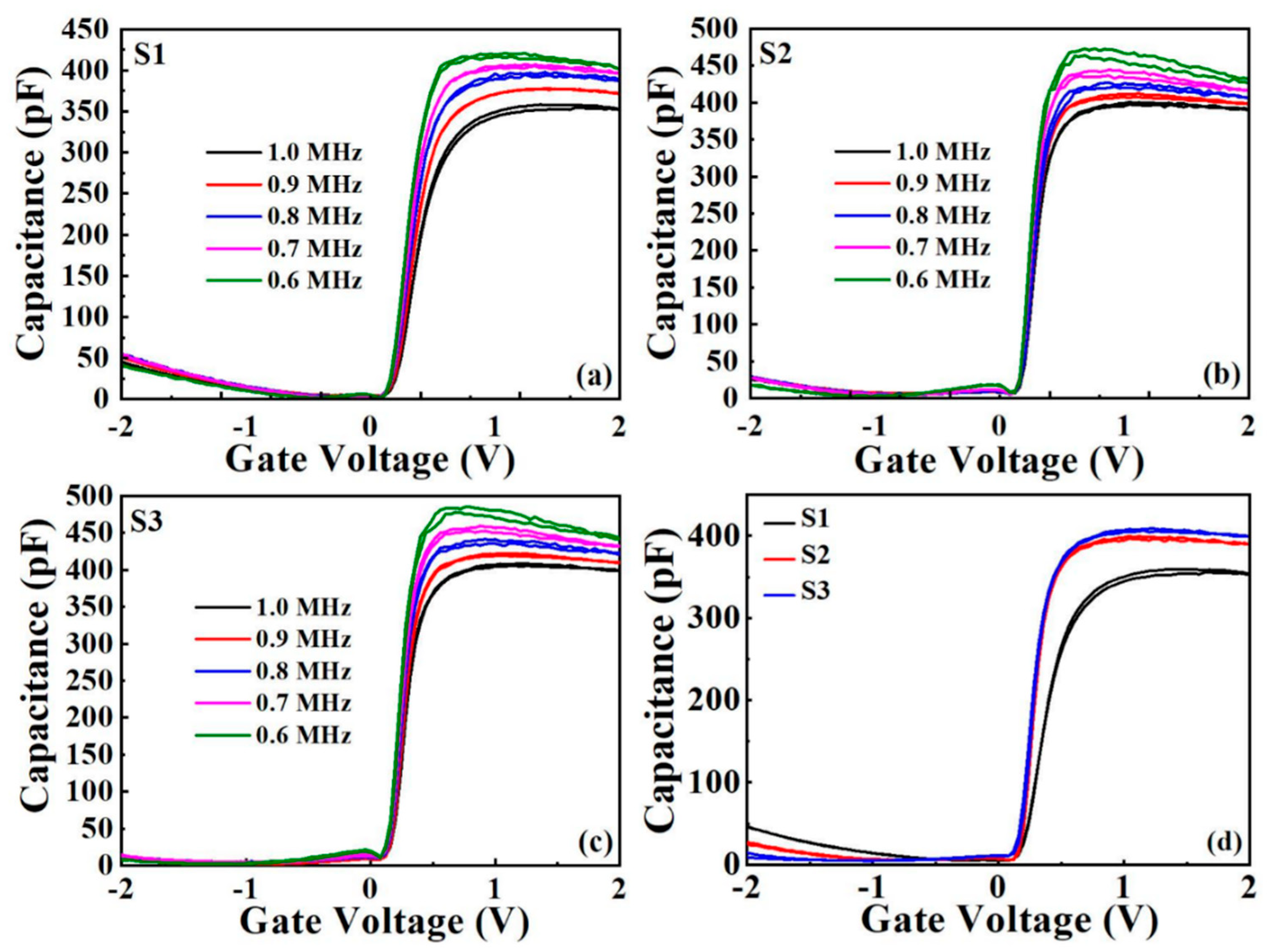

3.3.1. Capacitance-Voltage Measurements

3.3.2. Conductivity-Voltage Measurements

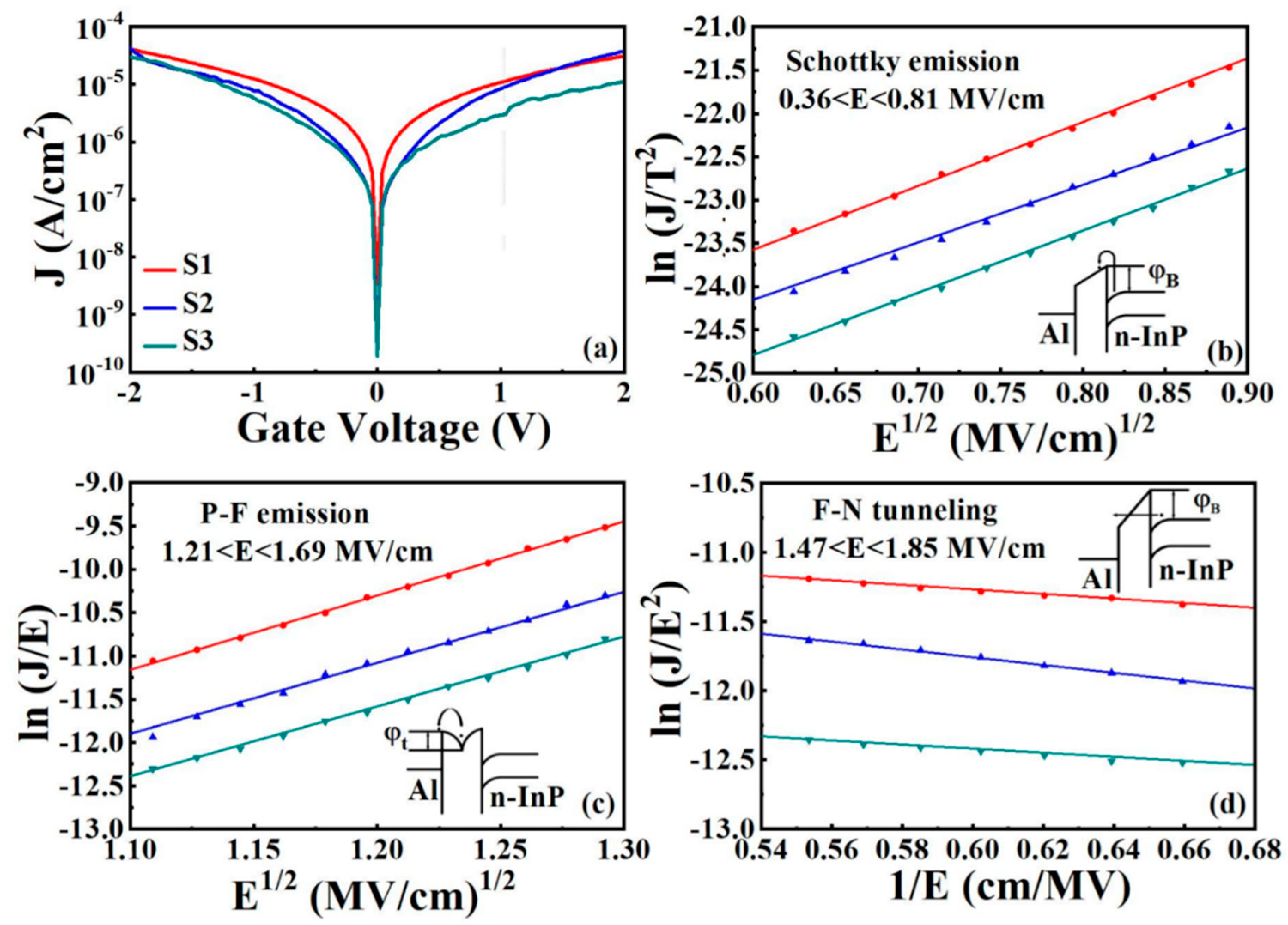

3.3.3. J−V Analyses and Conduction Mechanisms at Room Temperature

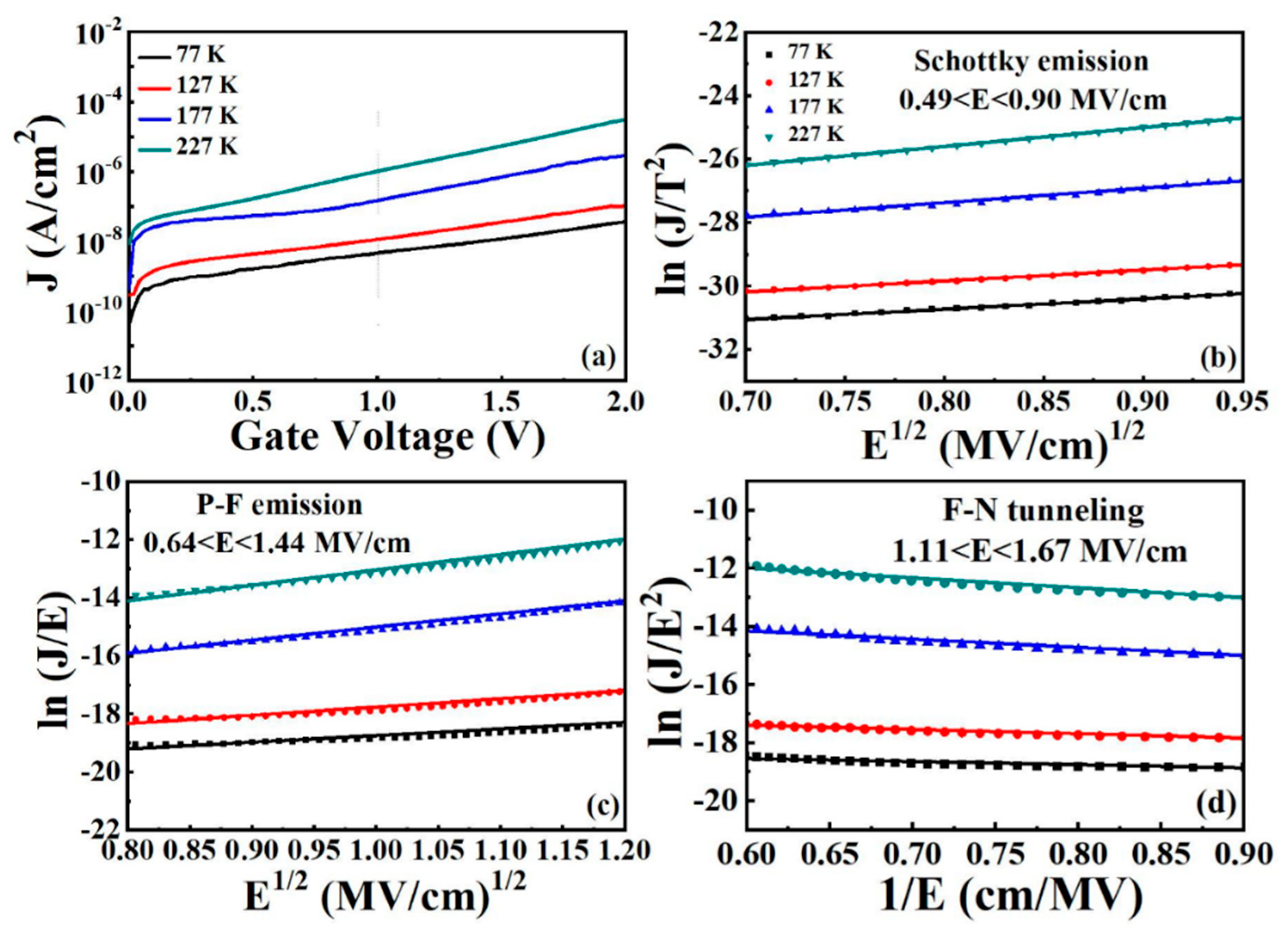

3.3.4. Low Temperature J–V Analyses and Conduction Mechanisms

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Pelella, M.M.; Fossum, J.G.; Suh, D.; Krishnan, S.; Jenkins, K.A.; Hargrove, M.J. Low-voltage transient bipolar effect induced by dynamic floating-body charging in scaled PD/SOI MOSFET’s. IEEE Electron Dev. Lett. 1996, 17, 196–198. [Google Scholar] [CrossRef]

- Lauer, I.; Antoniadis, D.A. Enhancement of electron mobility in ultrathin-body silicon-on-insulator MOSFETs with uniaxial strain. IEEE Electron Dev. Lett. 2005, 26, 314–316. [Google Scholar] [CrossRef]

- Robertson, J.; Wallace, R.M. High-K materials and metal gates for CMOS applications. Mater. Sci. Eng. R 2015, 88, 1–41. [Google Scholar] [CrossRef] [Green Version]

- Chin, W.C.; Cheong, K.Y. Effects of post-deposition annealing temperature and ambient on RF magnetron sputtered Sm2O3 gate on n-type silicon substrate. J. Mater. Sci. Mater. Electron. 2011, 22, 1816–1826. [Google Scholar] [CrossRef]

- Stewart, A.D.; Gerger, A.; Gila, B.P.; Abernathy, C.R.; Pearton, S.J. Determination of Sm2O3 GaAs heterojunction band offsets by X-ray photoelectron spectroscopy. Appl. Phys. Lett. 2008, 92, 153511. [Google Scholar] [CrossRef]

- Dakhel, A.A. Dielectric and optical properties of samarium oxide thin films. J. Alloy. Compd. 2004, 365, 233–239. [Google Scholar] [CrossRef]

- Mahata, C.; Oh, I.K.; Yoon, C.M.; Lee, C.W.; Seo, J.; Algadi, H. The impact of atomic layer deposited SiO2 passivation for high-k Ta1-xZrxO on the InP substrate. J. Mater. Chem. C 2015, 3, 10293–10301. [Google Scholar] [CrossRef]

- Sonnet, A.M.; Hinkle, C.L.; Jivani, M.N.; Chapman, R.A.; Pollack, G.P.; Wallace, R.M.; Vogel, E.M. Performance enhancement of n-channel inversion type InxGa1-xAs metal-oxide-semiconductor field effect transistor using ex situ deposited thin amorphous silicon layer. Appl. Phys. Lett. 2008, 93, 122109. [Google Scholar] [CrossRef]

- Yuan, Y.; Yu, B.; Ahn, J.; McIntyre, P.C.; Asbeck, P.M.; Rodwell, M.J.W.; Taur, Y. A Distributed Bulk-Oxide Trap Model for Al2O3 InGaAs MOS Devices. IEEE Trans. Electron Devices 2012, 59, 2100–2106. [Google Scholar] [CrossRef]

- Yen, C.F.; Yeh, M.Y.; Chong, K.K.; Hsu, C.F.; Lee, M.K. InP MOS capacitor and E-mode n-channel FET with ALD Al2O3-based high-k dielectric. Appl. Phys. A 2016, 122, 1–9. [Google Scholar] [CrossRef]

- Sun, Y.; Liu, Z.; MacHuca, F.; Pianetta, P.; Spicer, W.E. Optimized cleaning method for producing device quality InP(100) surfaces. J. Appl. Phys. 2005, 97, 124902. [Google Scholar] [CrossRef] [Green Version]

- He, G.; Gao, J.; Chen, H.S.; Cui, J.B.; Sun, Z.Q.; Chen, X.S. Modulating the Interface Quality and Electrical Properties of HfTiO/InGaAs Gate Stack by Atomic- Layer-Deposition-Derived Al2O3 Passivation Layer. ACS Appl. Mater. Interfaces 2014, 6, 22013–22025. [Google Scholar] [CrossRef] [PubMed]

- Wang, S.K.; Cao, M.; Sun, B.; Li, H.; Liu, H. Reducing the interface trap density in Al2O3/InP stacks by low-temperature thermal process. Appl. Phys. Exp. 2015, 8, 091201. [Google Scholar] [CrossRef]

- Ingrey, S.; Lau, W.M.; McIntyre, N.S.; Sodhi, R. An X-ray photoelectron spectroscopy study on ozone treated InP surfaces. J. Vac. Sci. Technol. A 1987, 5, 1621–1624. [Google Scholar] [CrossRef]

- Çetin, H.; Ayyildiz, E. The electrical properties of metal-oxide-semiconductor devices fabricated on the chemically etched n-InP substrate. Appl. Surf. Sci. 2007, 253, 5961–5966. [Google Scholar] [CrossRef]

- Lebedev, M.V.; Serov, Y.M.; Lvova, T.V.; Endo, R.; Masuda, T.; Sedova, I.V. InP(1 0 0) surface passivation with aqueous sodium sulfide solution. Appl. Surf. Sci. 2020, 533, 147484. [Google Scholar] [CrossRef]

- Carpenter, M.S.; Melloch, M.R.; Lundstrom, M.S.; Tobin, S.P. Effects of Na2S and (NH4)2S edge passivation treatments on the dark current-voltage characteristics of GaAs pn diodes. Appl. Phys. Lett. 1988, 52, 2157–2159. [Google Scholar] [CrossRef] [Green Version]

- Driad, R.; Sah, R.E.; Schmidt, R.; Kirste, L. Passivation of InP heterojunction bipolar transistors by strain controlled plasma assisted electron beam evaporated hafnium oxide. Appl. Phys. Lett. 2012, 100, 014102. [Google Scholar] [CrossRef]

- Galatage, R.V.; Dong, H.; Zhernokletov, D.M.; Brennan, B.; Hinkle, C.L.; Wallace, R.M.; Vogel, E.M. Effect of post deposition anneal on the characteristics of HfO2/InP metal-oxide-semiconductor capacitors. Appl. Phys. Lett. 2011, 99, 172901. [Google Scholar] [CrossRef]

- An, C.H.; Byun, Y.C.; Cho, M.H.; Kim, H. Thermal instability of HfO2 on InP structure with ultrathin Al2O3 interface passivation layer. Phys. Status Solidi Rapid Res. Lett. 2012, 6, 247–249. [Google Scholar] [CrossRef]

- Kakiuchi, H.; Ohmi, H.; Harada, M.; Watanabe, H.; Yasutake, K. Significant enhancement of Si oxidation rate at low temperatures by atmospheric pressure Ar/O2 plasma. Appl. Phys. Lett. 2007, 90, 151904. [Google Scholar] [CrossRef]

- Hollinger, G.; Bergignat, E.; Joseph, J.; Robach, Y. On the nature of oxides on InP surfaces. J. Vac. Sci. Technol. A 1985, 3, 2082–2088. [Google Scholar] [CrossRef]

- Aguirre-Tostado, F.S.; Milojevic, M.; Hinkle, C.L.; Vogel, E.M.; Wallace, R.M.; McDonnell, S.; Hughes, G.J. Indium stability on InGaAs during atomic H surface cleaning. Appl. Phys. Lett. 2008, 92, 171906. [Google Scholar] [CrossRef] [Green Version]

- Murphy, A.B. Band-gap determination from diffuse reflectance measurements of semiconductor films, and application to photoelectrochemical water-splitting. Sol. Energy Mater. Sol. Cells 2007, 91, 1326–1337. [Google Scholar] [CrossRef]

- Jaggernauth, A.; Mendes, J.C.; Silva, R.F. Atomic layer deposition of high-: κ layers on polycrystalline diamond for MOS devices: A review. J. Mater. Chem. C 2020, 8, 13127–13153. [Google Scholar] [CrossRef]

- Kraut, E.A.; Grant, R.W.; Waldrop, J.R.; Kowalczyk, S.P. Precise Determination of the Valence-Band Edge in X Ray Photoemission Spectra. Phys. Rev. Lett. 1980, 44, 1620–1623. [Google Scholar] [CrossRef]

- Mahata, C.; Byun, Y.-C.; An, C.-H.; Choi, S.; An, Y.; Kim, H. Comparative study of atomic-layer-deposited stacked (HfO2/Al2O3) and nanolaminated (HfAlOx) dielectric on In0.53Ga0.47As. ACS Appl. Mater. Interfaces 2013, 5, 4195–4201. [Google Scholar] [CrossRef]

- Çiçek, O.; Durmuş, H.; Altındal, Ş. Identifying of series resistance and interface states on rhenium/n-GaAs structures using C-V-T and G/ω-V-T characteristics in frequency ranged 50 kHz to 5 MHz. J. Mater. Sci. Mater. Electron. 2020, 31, 704–713. [Google Scholar] [CrossRef]

- Yoshioka, H.; Nakamura, T.; Kimoto, T. Accurate evaluation of interface state density in SiC metal-oxide-semiconductor structures using surface potential based on depletion capacitance. J. Appl. Phys. 2012, 111, 04C100. [Google Scholar] [CrossRef] [Green Version]

- Mutale, A.; Deevi, S.C.; Yilmaz, E. Effect of annealing temperature on the electrical characteristics of Al/Er2O3/n-Si/Al MOS capacitors. J. Alloy. Compd. 2021, 863, 158718. [Google Scholar] [CrossRef]

- Varzgar, J.B.; Kanoun, M.; Uppal, S.; Chattopadhyay, S.; Tsang, Y.L.; Escobedo-Cousins, E.; Olsen, S.H.; O’Neill, A.; Hellström, P.E.; Edholm, J.; et al. Reliability study of ultra-thin gate oxides on strained-Si/SiGe MOS structures. Mater. Sci. Eng. B 2006, 135, 203–206. [Google Scholar] [CrossRef]

- Foster, A.S.; Lopez Gejo, F.; Shluger, A.L.; Nieminen, R.M. Vacancy and interstitial defects in hafnia. Phys. Rev. B 2002, 65, 1741171–17411713. [Google Scholar] [CrossRef] [Green Version]

- Liu, J.W.; Oosato, H.; Da, B.; Koide, Y. Fixed charges investigation in Al2O3/hydrogenated-diamond metal-oxide-semiconductor capacitors. Appl. Phys. Lett. 2020, 117, 163502. [Google Scholar] [CrossRef]

- Shahinur Rahman, M.; Evangelou, E.K.; Konofaos, N.; Dimoulas, A. Gate stack dielectric degradation of rare-earth oxides grown on high mobility Ge substrates. J. Appl. Phys. 2012, 112, 094501. [Google Scholar] [CrossRef] [Green Version]

- Wang, D.; He, G.; Hao, L.; Qiao, L.; Fang, Z.; Liu, J. Interface Chemistry and Dielectric Optimization of TMA-Passivated high-k/Ge Gate Stacks by ALD-Driven Laminated Interlayers. ACS Appl. Mater. Interfaces 2020, 12, 25390–25399. [Google Scholar] [CrossRef] [PubMed]

- Engel-Herbert, R.; Hwang, Y.; Stemmer, S. Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces. J. Appl. Phys. 2010, 108, 124101. [Google Scholar] [CrossRef] [Green Version]

- Lin, H.C.; Wang, W.E.; Brammertz, G.; Meuris, M.; Heyns, M. Electrical study of sulfur passivated In0.53Ga0.47As MOS capacitor and transistor with ALD Al2O3 as gate insulator. Microelectron. Eng. 2009, 86, 1554–1557. [Google Scholar] [CrossRef]

- Martens, K.; Wang, W.; De Keersmaecker, K.; Borghs, G.; Groeseneken, G.; Maes, H. Impact of weak Fermi-level pinning on the correct interpretation of III-V MOS C-V and G-V characteristics. Microelectron. Eng. 2007, 84, 2146–2149. [Google Scholar] [CrossRef]

- Qiao, L.; He, G.; Hao, L.; Lu, J.; Gao, Q.; Zhang, M.; Fang, Z. Interface Optimization of Passivated Er2O3/Al2O3/InP MOS Capacitors and Modulation of Leakage Current Conduction Mechanism. IEEE Trans. Electron Devices 2021, 68, 2899–2905. [Google Scholar] [CrossRef]

- Carter, A.D.; Mitchell, W.J.; Thibeault, B.J.; Law, J.J.M.; Rodwell, M.J.W. Al2O3 growth on (100) In0.53Ga0.47 as initiated by cyclic trimethylaluminum and hydrogen plasma exposures. Appl. Phys. Exp. 2011, 4, 091102. [Google Scholar] [CrossRef]

- Yen, C.-F.; Lee, M.-K. Very Low Leakage Current of High Band-Gap Al2O3 Stacked on TiO2/InP Metal–Oxide–Semiconductor Capacitor with Sulfur and Hydrogen Treatments. Jpn. J. Appl. Phys. 2012, 51, 081201. [Google Scholar]

- Chen, Y.-T.; Zhao, H.; Yum, J.H.; Wang, Y.; Lee, J.C. Metal-oxide-semiconductor field-effect-transistors on indium phosphide using HfO2 and silicon passivation layer with equivalent oxide thickness of 18 Å. Appl. Phys. Lett. 2009, 94, 213505. [Google Scholar] [CrossRef]

- Suzuki, R.; Taoka, N.; Yokoyama, M.; Lee, S.; Kim, S.H. 1-nm-capacitance-equivalent-thickness HfO2/Al2O3/InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density. Appl. Phys. Lett. 2012, 100, 132906. [Google Scholar] [CrossRef]

- Shahrjerdi, D.; Rotter, T.; Balakrishnan, G. Fabrication of Self-Aligned Enhancement-Mode MOSFETs With Gate Stack. IEEE Electron Dev. Lett. 2008, 29, 557–560. [Google Scholar] [CrossRef]

- He, G.; Zhang, L.D.; Liu, M.; Sun, Z.Q. HfO2-GaAs metal-oxide-semiconductor capacitor using dimethylaluminumhydride-derived aluminum oxynitride interfacial passivation layer. Appl. Phys. Lett. 2010, 97, 223501. [Google Scholar] [CrossRef]

- Yang, M.; Wang, H.; Ma, X.; Gao, H.; Wang, B. Effect of nitrogen-accommodation ability of electrodes in SiNx-based resistive switching devices. Appl. Phys. Lett. 2017, 111, 223510. [Google Scholar] [CrossRef]

- Kim, J.; Krishnan, S.A.; Narayanan, S.; Chudzik, M.P.; Fischetti, M.V. Thickness and temperature dependence of the leakage current in hafnium-based Si SOI MOSFETs. Microelectron. Reliab. 2012, 52, 2907–2913. [Google Scholar] [CrossRef]

- Sadeq, M.S.; Morshidy, H.Y. Effect of samarium oxide on structural, optical and electrical properties of some alumino-borate glasses with constant copper chloride. J. Rare Earths 2020, 38, 770–775. [Google Scholar] [CrossRef]

- Paskaleva, A.; Bauer, A.J.; Lemberger, M.; Zürcher, S. Different current conduction mechanisms through thin hlgh-k Hf xTiySizO films due to the varying Hf to Ti ratio. J. Appl. Phys. 2004, 95, 5583–5590. [Google Scholar] [CrossRef]

- Chiu, F.C. Interface characterization and carrier transportation in metal/ HfO2/silicon structure. J. Appl. Phys. 2006, 100, 114102. [Google Scholar] [CrossRef]

| Sample | EOT (nm) | k | Vfb (V) | △Vfb (mV) | Qox (cm−2) | Nbt (cm−2) | J (A/cm−2) |

|---|---|---|---|---|---|---|---|

| S1 | 3.01 | 12.96 | 0.25 | 3.44 | −1.62 × 1012 | −2.46 × 1010 | 1.07 × 10−5 |

| S2 | 2.71 | 14.39 | 0.21 | 5.16 | −1.43 × 1012 | −4.11 × 1010 | 8.42 × 10−6 |

| S3 | 2.65 | 14.75 | 0.19 | 1.55 | −1.30 × 1012 | −1.26 × 1010 | 2.87 × 10−6 |

| Sm2O3/Al2O3/InP (This Work) | PMA-TiO2/S-InP [41] | TiO2/S-InP [41] | 10 Å Si IPL/51 Å HfO2/InP [42] | 70 Å HfO2/InP [42] | HfO2 (10 nm)/Al2O3 (0.2 nm)/InGaAs/InP [43] | |

|---|---|---|---|---|---|---|

| Leakage current density (A/cm2) | 2.87 × 10−6 at 1 V | 1.9 × 10−7 at 2 V 2.7 × 10−5 at −2 V | 5.01 × 10−6 at 2 V 1.5 × 10−2 at −2 V | 1.32 × 10−3 at 1 V | 3.94 × 10−2 at 1 V | 2.4 × 10−2 |

| k | 14.75 | 39 | 34 | / | / | / |

| ∆Vfb (mV) | 1.55 | 40 | 250 | 240 | 280 | / |

| Dit (cm−2eV−1) | (G-V) 1.05 × 1013 | (C-V) 3.1 × 1011 | (C-V) 5 × 1011 | (C-V) 3-8 × 1012 | (C-V) 2-9 × 1013 | (C-V) 2 × 1012 |

| Sample | J (A/cm2) | εr | n | εox | φt (eV) |

|---|---|---|---|---|---|

| S1 | 1.07 × 10−5 | 4.00 | 2.00 | 11.90 | 0.53 |

| S2 | 8.42 × 10−6 | 4.96 | 2.23 | 13.01 | 0.54 |

| S3 | 2.87 × 10−6 | 4.23 | 2.06 | 13.41 | 0.55 |

| T | J (A/cm2) | εr | n | εox | φt (eV) |

|---|---|---|---|---|---|

| 77 K | 4.64 × 10−9 | 20.39 | 4.52 | 164.88 | 0.54 |

| 127 K | 1.13 × 10−8 | 18.53 | 4.31 | 108.14 | 0.53 |

| 177 K | 1.48 × 10−7 | 10.40 | 3.22 | 42.66 | 0.50 |

| 227 K | 1.02 × 10−6 | 6.10 | 2.47 | 31.05 | 0.47 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lu, J.; He, G.; Yan, J.; Dai, Z.; Zheng, G.; Jiang, S.; Qiao, L.; Gao, Q.; Fang, Z. Interface Optimization and Transport Modulation of Sm2O3/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer. Nanomaterials 2021, 11, 3443. https://doi.org/10.3390/nano11123443

Lu J, He G, Yan J, Dai Z, Zheng G, Jiang S, Qiao L, Gao Q, Fang Z. Interface Optimization and Transport Modulation of Sm2O3/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer. Nanomaterials. 2021; 11(12):3443. https://doi.org/10.3390/nano11123443

Chicago/Turabian StyleLu, Jinyu, Gang He, Jin Yan, Zhenxiang Dai, Ganhong Zheng, Shanshan Jiang, Lesheng Qiao, Qian Gao, and Zebo Fang. 2021. "Interface Optimization and Transport Modulation of Sm2O3/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer" Nanomaterials 11, no. 12: 3443. https://doi.org/10.3390/nano11123443

APA StyleLu, J., He, G., Yan, J., Dai, Z., Zheng, G., Jiang, S., Qiao, L., Gao, Q., & Fang, Z. (2021). Interface Optimization and Transport Modulation of Sm2O3/InP Metal Oxide Semiconductor Capacitors with Atomic Layer Deposition-Derived Laminated Interlayer. Nanomaterials, 11(12), 3443. https://doi.org/10.3390/nano11123443