Optimization of Sacrificial Layer Etching in Single-Crystal Silicon Nano-Films Transfer Printing for Heterogeneous Integration Application

Abstract

:1. Introduction

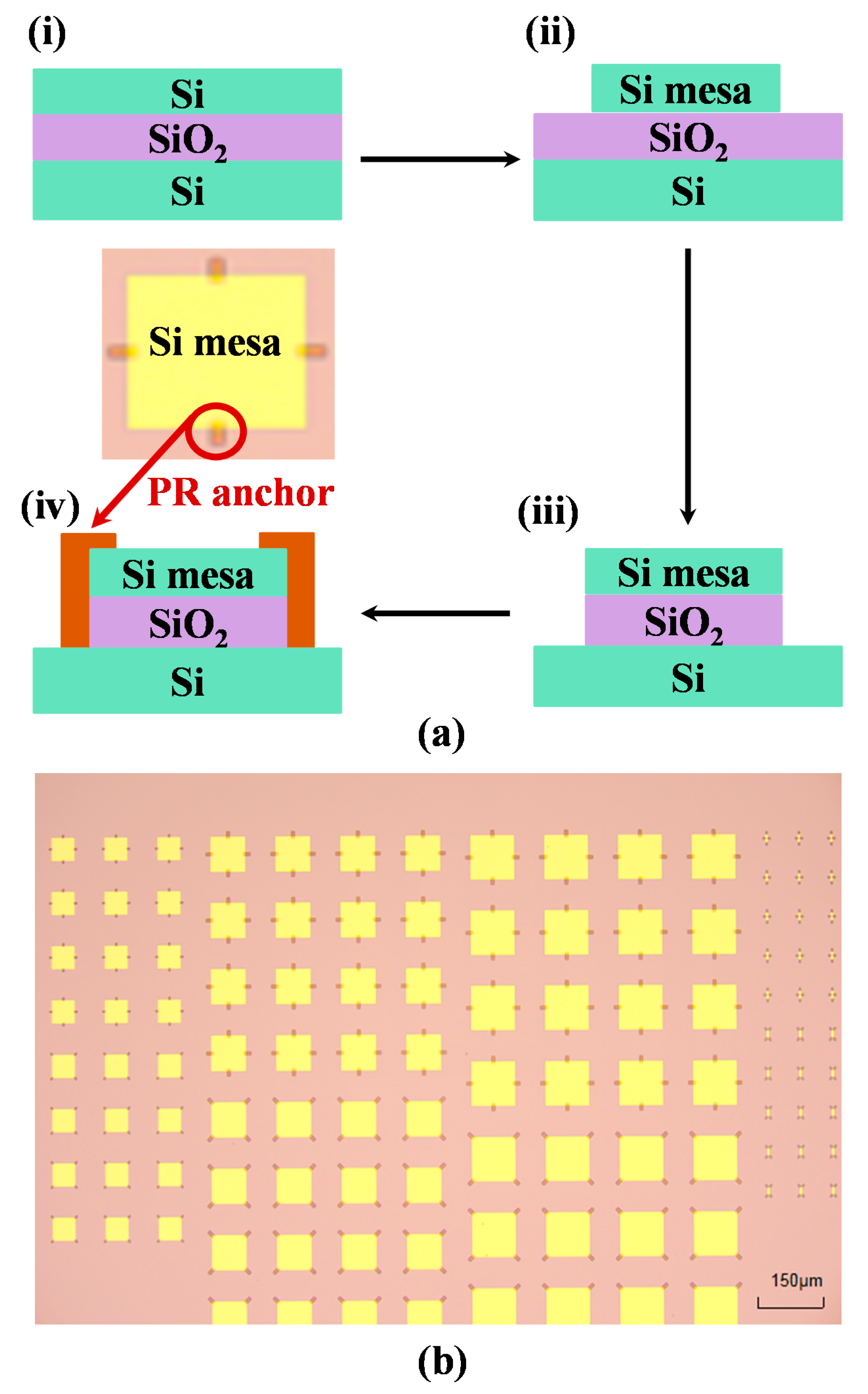

2. Experiment Process

3. Results and Discussion

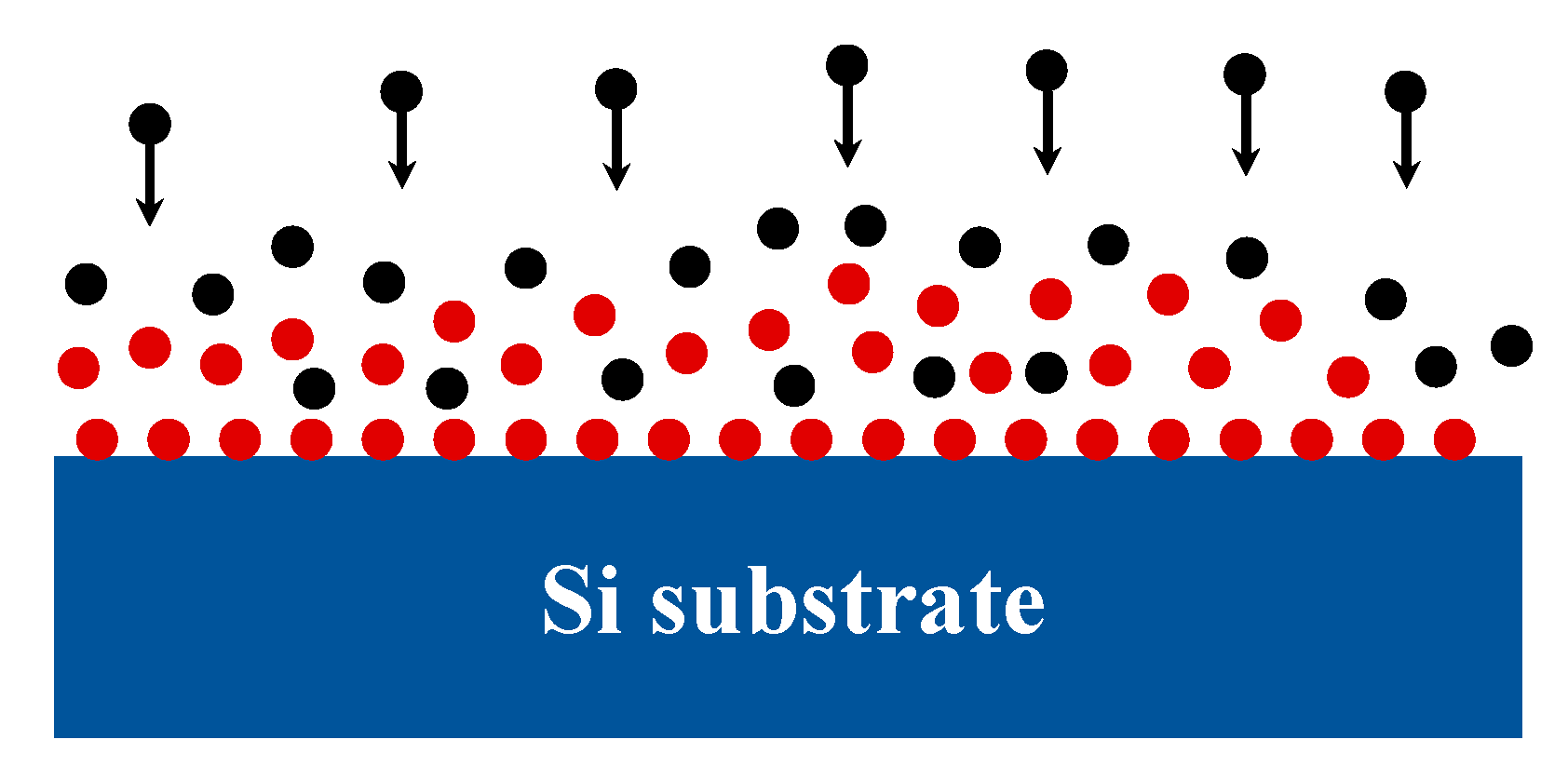

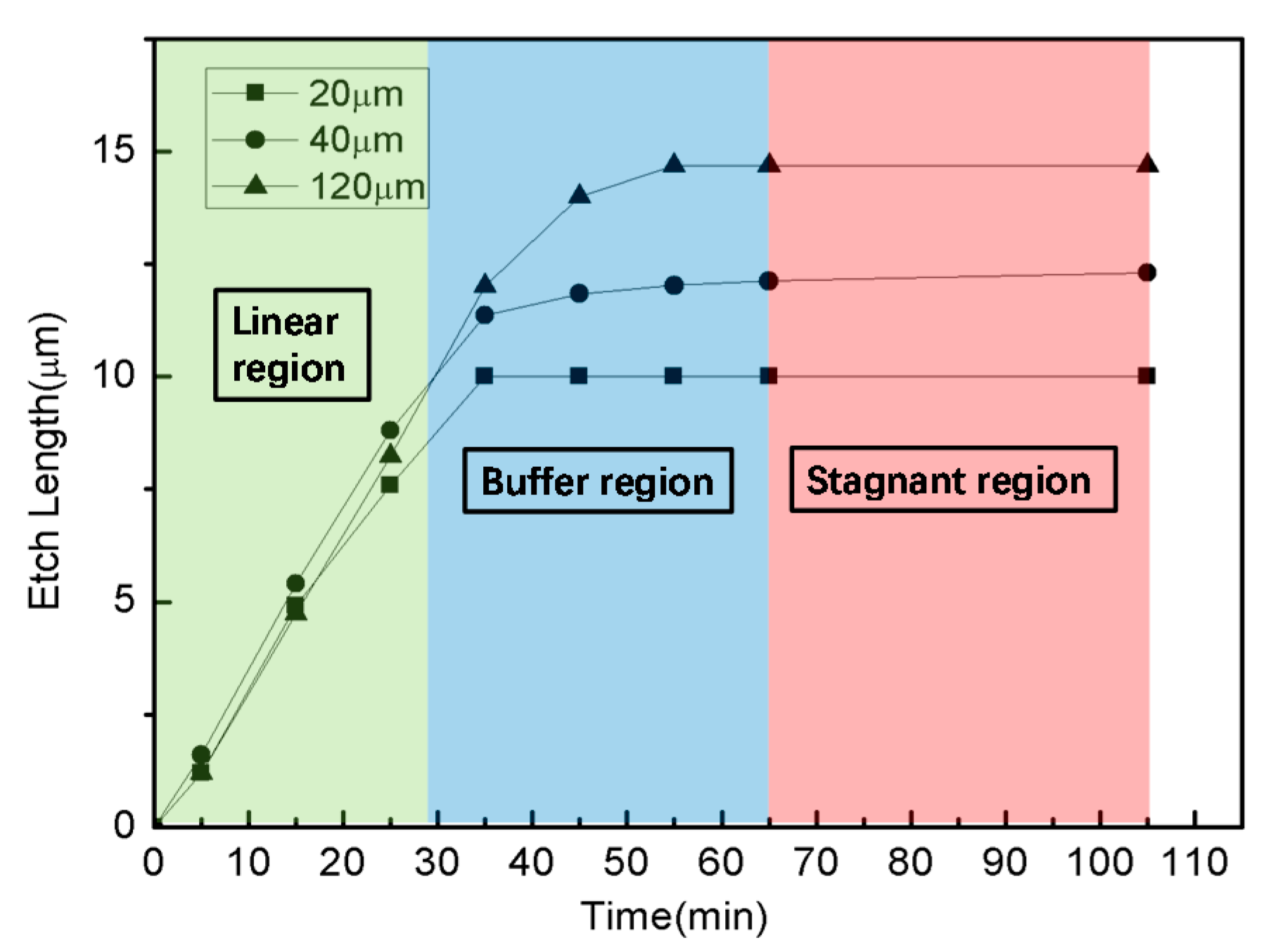

3.1. Influence of Graphic Size of the Top Si Mesa on Wet Etching Effect

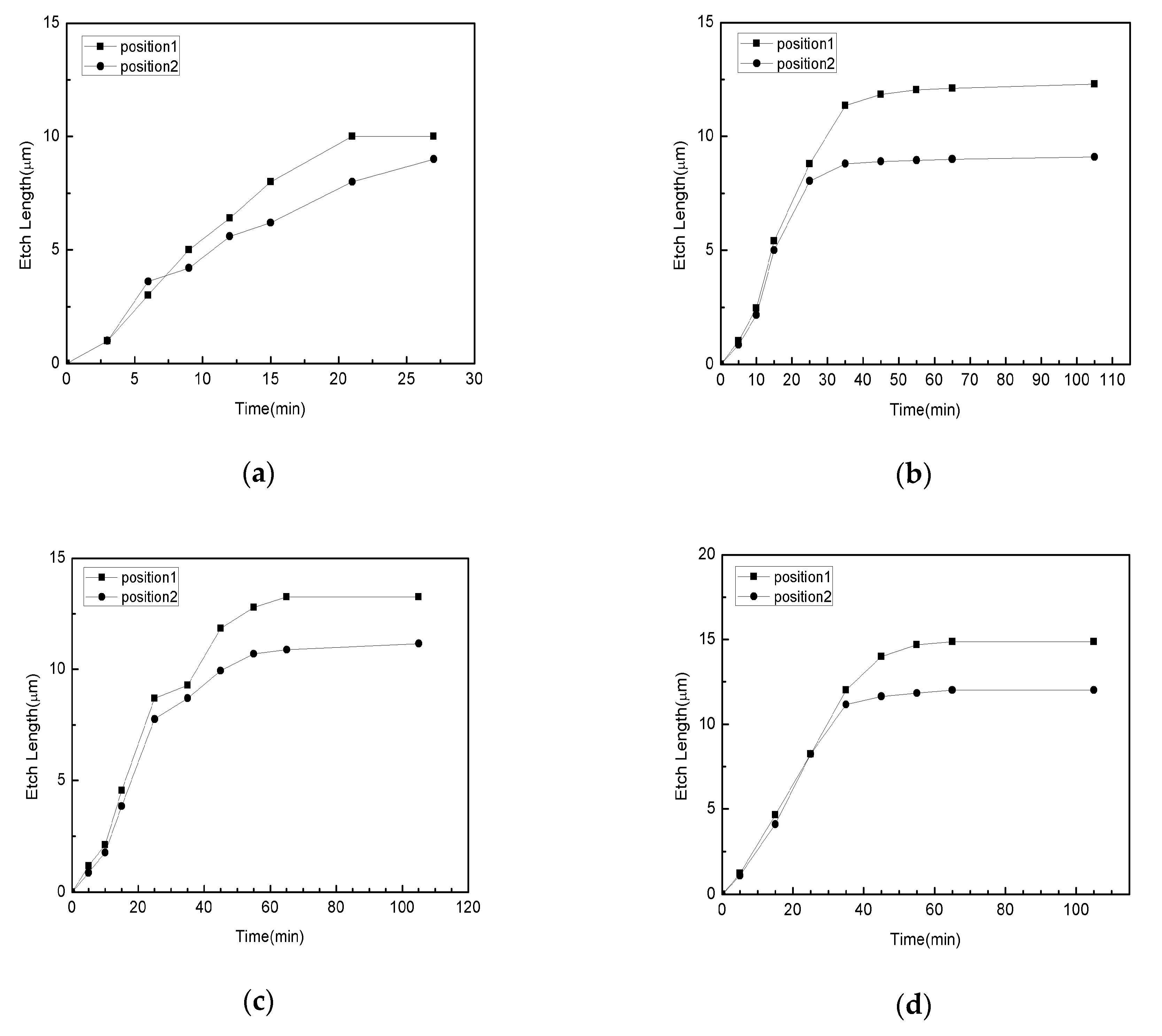

3.2. Influence of the Location of the PR Anchors on Wet Etching Effect

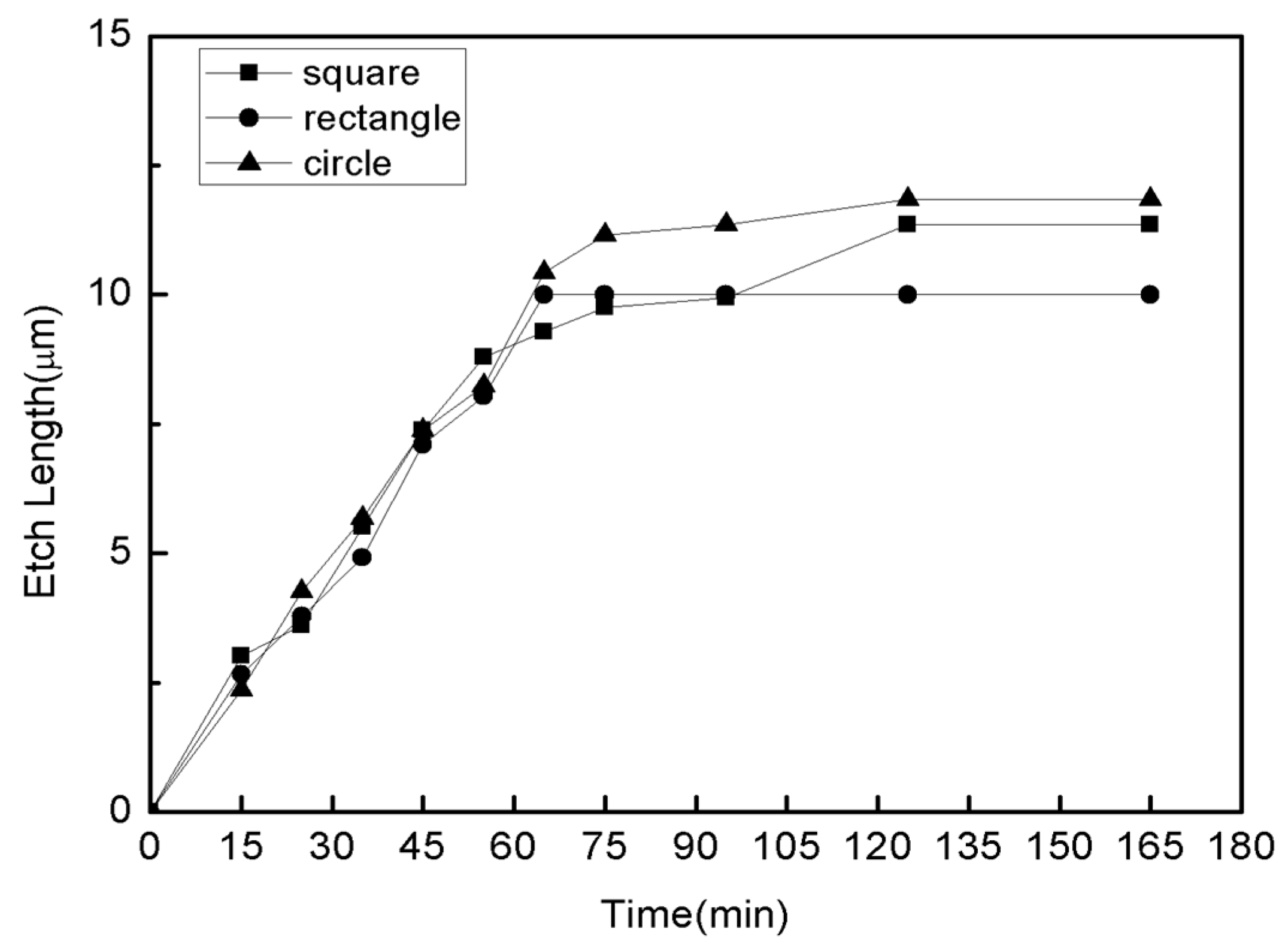

3.3. Influence of Graphic Shape of the Top Si Mesa on Wet Etching Effect

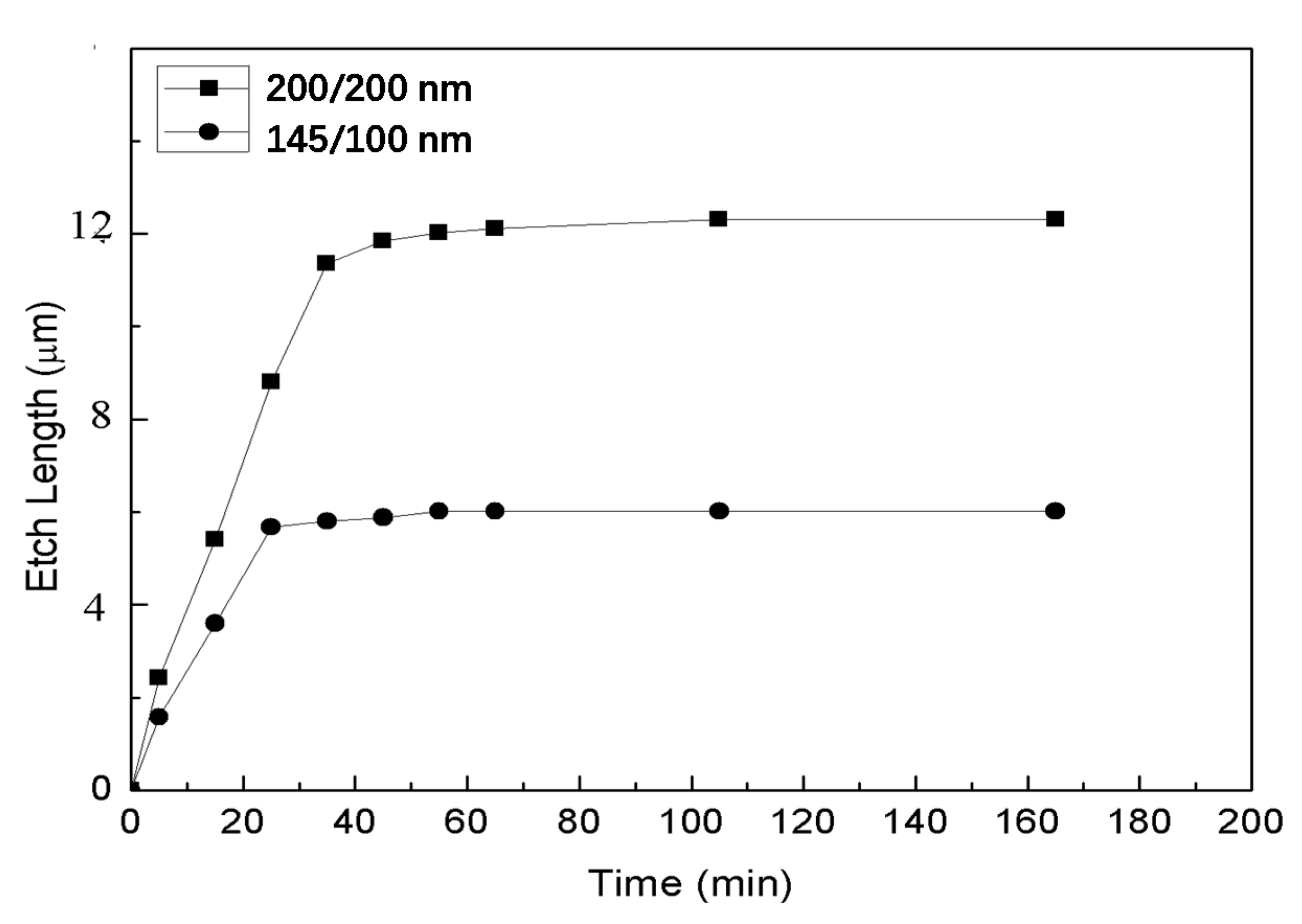

3.4. Influence of Thickness Ratios of Si/SiO2

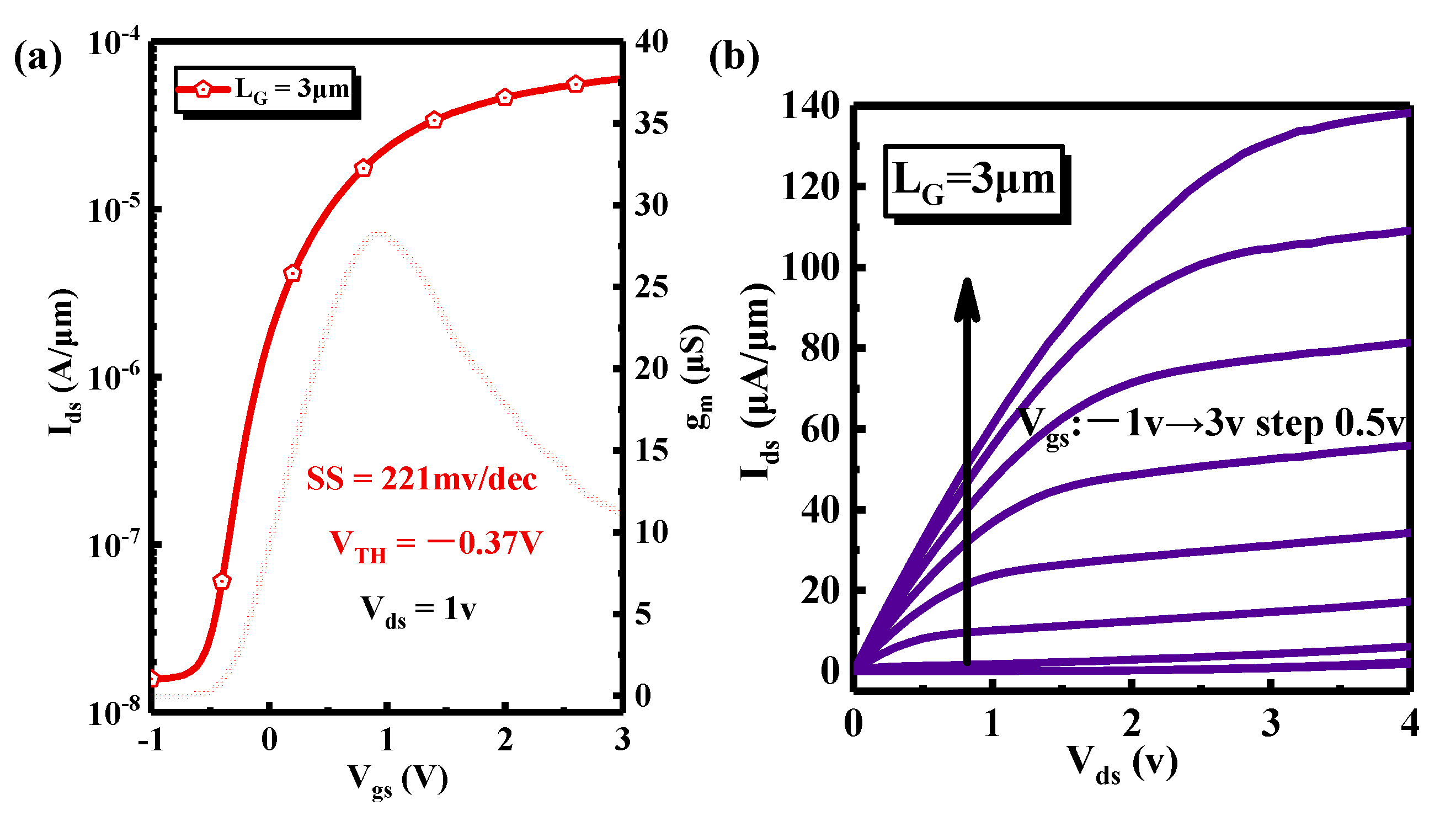

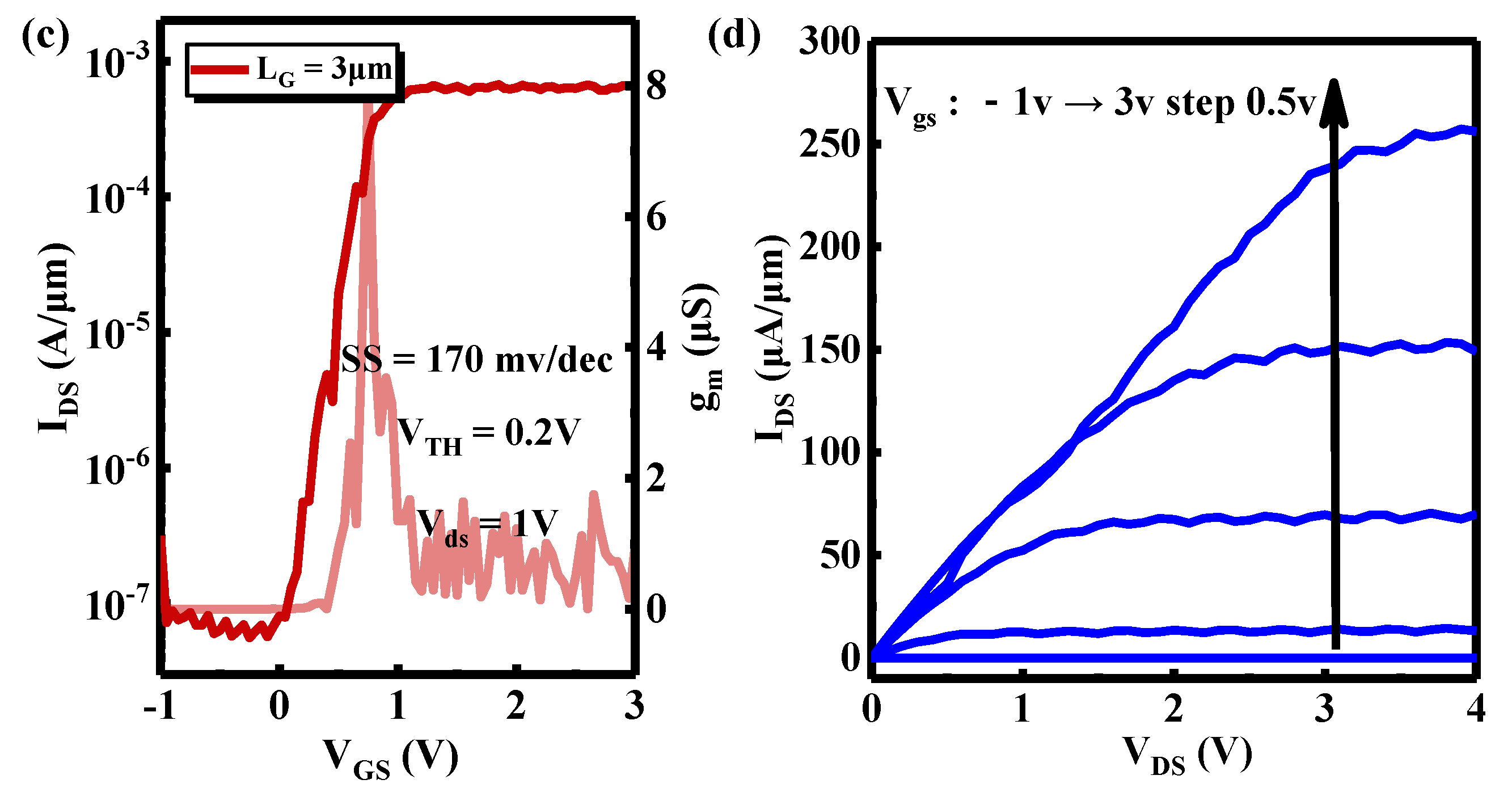

3.5. Si MOSFET Transferred on Sapphire Substrate by Transfer Printing

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kim, N.S.; Austin, T.; Blaauw, D.; Mudge, T.; Flautner, K.; Hu, J.S.; Irwin, M.J.; Kandemir, M.; Narayanan, V. Leakage Current: Moore’s Law Meets Static Power. Computer 2003, 36, 68–75. [Google Scholar]

- Li, C.; Lin, J.; Liu, H.; Chu, M.; Chen, H.; Ma, C.; Tsai, C.; Huang, H.; Lin, H.; Liu, H.; et al. Van der Waal Epitaxy of Flexible and Transparent VO2 Film on Muscovite. Chem. Mater. 2016, 28, 3914–3919. [Google Scholar] [CrossRef]

- Chen, H.; Feng, X.; Chen, Y. Directionally controlled transfer printing using micropatterned stamps. Appl. Phys. Lett. 2013, 103, 151607. [Google Scholar] [CrossRef]

- Li, G.; Song, E.; Guo, Q.; Huang, G.; Mei, Y. Transfer techniques for single-crystal silicon/germanium nanomembranes and their application in flexible electronics. Sci. Sin. Inf. 2018, 48, 670–687. [Google Scholar] [CrossRef]

- Yuan, H.-C.; Ma, Z. Microwave thin-film transistors using Si nanomembranes on flexible polymer substrate. Appl. Phys. Lett. 2006, 89, 1682. [Google Scholar] [CrossRef]

- Katz, H.E. Recent Advances in Semiconductor Performance and Printing Processes for Organic Transistor-Based Electronics. Chem. Mater. 2004, 16, 4748–4756. [Google Scholar] [CrossRef]

- Zhang, J.; Wu, Y.; Li, Z.; Zhang, Y.; Peng, Y.; Chen, D.; Zhu, W.; Xu, S.; Zhang, C.; Hao, Y. High-performance acetone soluble tape transfer printing method for heterogeneous integration. Sci. Rep. 2019, 9, 15769. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Zhang, J.; Zhang, W.; Wu, Y.; Zhang, Y.; Peng, Y.; Feng, Z.; Chen, D.; Zhao, S.; Zhang, J.; Zhang, C.; et al. Wafer-Scale Si–GaN Monolithic Integrated E-Mode Cascode FET Realized by Transfer Printing and Self-Aligned Etching Technology. IEEE Trans. Electron Devices 2020, 67, 3304–3308. [Google Scholar] [CrossRef]

- Zhang, J.; Zhang, Y.; Chen, D.; Zhu, W.; Xi, H.; Zhang, J.; Zhang, C.; Hao, Y. Bendable Single Crystal Silicon Nanomembrane Thin Film Transistors with Improved Low-Temperature Processed Metal/n-Si Ohmic Contact by Inserting TiO2 Interlayer. Nanomaterials 2018, 8, 1060. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Chou, S.Y.; Keimel, C.; Gu, J. Ultrafast and Direct Imprint of Nanostructures in Silicon. Nature 2002, 417, 835–837. [Google Scholar] [CrossRef] [PubMed]

- McDonald, J.C.; Duffy, D.C.; Anderson, J.R.; Chiu, D.T.; Wu, H.; Schueller, O.J.; Whitesides, G.M. Fabrication of Microfluidic Systems in Poly (Dimethylsiloxane). Electrophoresis 2000, 21, 27–40. [Google Scholar] [CrossRef]

- Lee, S.; Biswas, R.; Li, W.; Kang, D.; Chan, L.; Yoon, J. Printable nanostructured silicon solar cells for high-performance, large-area flexible photovoltaics. ACS Nano 2014, 8, 10507–10516. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.; Wu, J.; Carlson, A.; Jin, S.H.; Kovalsky, A.; Glass, P.; Liu, Z.; Ahmed, N.; Elgan, S.L.; Chen, W.; et al. Microstructured elastomeric surfaces with reversible adhesion and examples of their use in deterministic assembly by transfer printing. Proc. Natl. Acad. Sci. USA 2010, 107, 17095–17100. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Lee, K.J.; Lee, J.; Hwang, H.; Reitmeier, Z.J.; Davis, R.F.; Rogers, J.A.; Nuzzo, R.G. A printable form of single-crystalline gallium nitride for flexible optoelectronic systems. Small 2005, 1, 1164–1168. [Google Scholar] [CrossRef] [PubMed]

- Lerner, R.; Eisenbrandt, S.; Bonafede, S.; Meitl, M.A.; Fecioru, A.; Trindade, A.J.; Reiner, R.; Waltreit, P.; Bower, C.A. Heterogeneous Integration of Microscale Gallium Nitride Transistors by Micro-Transfer-Printing. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference, Las Vegas, NV, USA, 31 May–3 June 2016. [Google Scholar]

- Navaraj, W.T.; Gupta, S.; Lorenzelli, L.; Dahiya, R. Wafer Scale Transfer of Ultrathin Silicon Chips on Flexible Substrates for High Performance Bendable Systems. Adv. Electron. Mater. 2018, 4, 1700277. [Google Scholar] [CrossRef] [Green Version]

- Sim, K.; Chen, S.; Li, Y.; Kammoun, M.; Peng, Y.; Xu, M.; Gao, Y.; Song, J.; Zhang, Y.; Ardebili, H.; et al. High Fidelity Tape Transfer Printing Based on Chemically Induced Adhesive Strength Modulation. Sci. Rep. 2015, 5, 16133. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Yan, Z.; Pan, T.; Xue, M.; Chen, C.; Cui, Y.; Yao, G.; Huang, L.; Liao, F.; Jing, W.; Zhang, H.; et al. Thermal release transfer printing for stretchable conformal bioelectronics. Adv. Sci. 2017, 4, 1700251. [Google Scholar] [CrossRef] [PubMed]

- Khang, D.-Y.; Jiang, H.; Huang, Y.; Rogers, J.A. A stretchable form of single-crystal silicon for high-performance electronics on rubber substrates. Science 2006, 311, 208–212. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Ng, E.Y.K.; Poh, S.T. Modeling of Electric Double Layer Effects through Pressure-driven Microchannel Flows. Comput. Model. Eng. Sci. 2002, 3, 351–365. [Google Scholar]

| Square (The Length of its Sides) | Circle (The Radius) | Rectangle (The Length and Width) |

|---|---|---|

| 20 μm | 12.5 μm | 30 μm, 10 μm |

| 40 μm | 25 μm | 60 μm, 20 μm |

| 80 μm | 50 μm | 120 μm, 40 μm |

| 120 μm | 75 μm | 160 μm, 80 μm |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, J.; Wu, Y.; Yang, G.; Chen, D.; Zhang, J.; You, H.; Zhang, C.; Hao, Y. Optimization of Sacrificial Layer Etching in Single-Crystal Silicon Nano-Films Transfer Printing for Heterogeneous Integration Application. Nanomaterials 2021, 11, 3085. https://doi.org/10.3390/nano11113085

Zhang J, Wu Y, Yang G, Chen D, Zhang J, You H, Zhang C, Hao Y. Optimization of Sacrificial Layer Etching in Single-Crystal Silicon Nano-Films Transfer Printing for Heterogeneous Integration Application. Nanomaterials. 2021; 11(11):3085. https://doi.org/10.3390/nano11113085

Chicago/Turabian StyleZhang, Jiaqi, Yichang Wu, Guofang Yang, Dazheng Chen, Jincheng Zhang, Hailong You, Chunfu Zhang, and Yue Hao. 2021. "Optimization of Sacrificial Layer Etching in Single-Crystal Silicon Nano-Films Transfer Printing for Heterogeneous Integration Application" Nanomaterials 11, no. 11: 3085. https://doi.org/10.3390/nano11113085

APA StyleZhang, J., Wu, Y., Yang, G., Chen, D., Zhang, J., You, H., Zhang, C., & Hao, Y. (2021). Optimization of Sacrificial Layer Etching in Single-Crystal Silicon Nano-Films Transfer Printing for Heterogeneous Integration Application. Nanomaterials, 11(11), 3085. https://doi.org/10.3390/nano11113085