Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors

Abstract

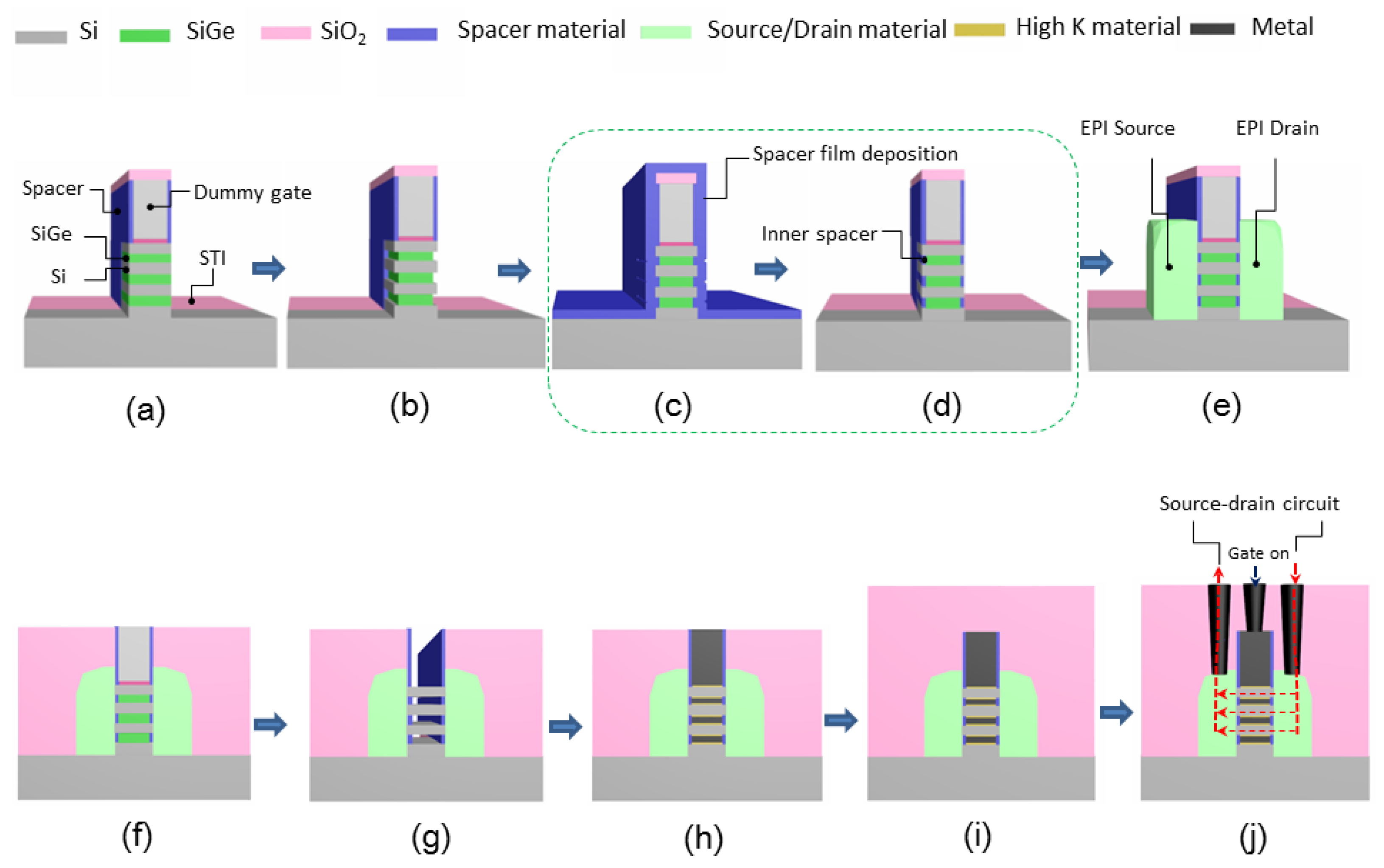

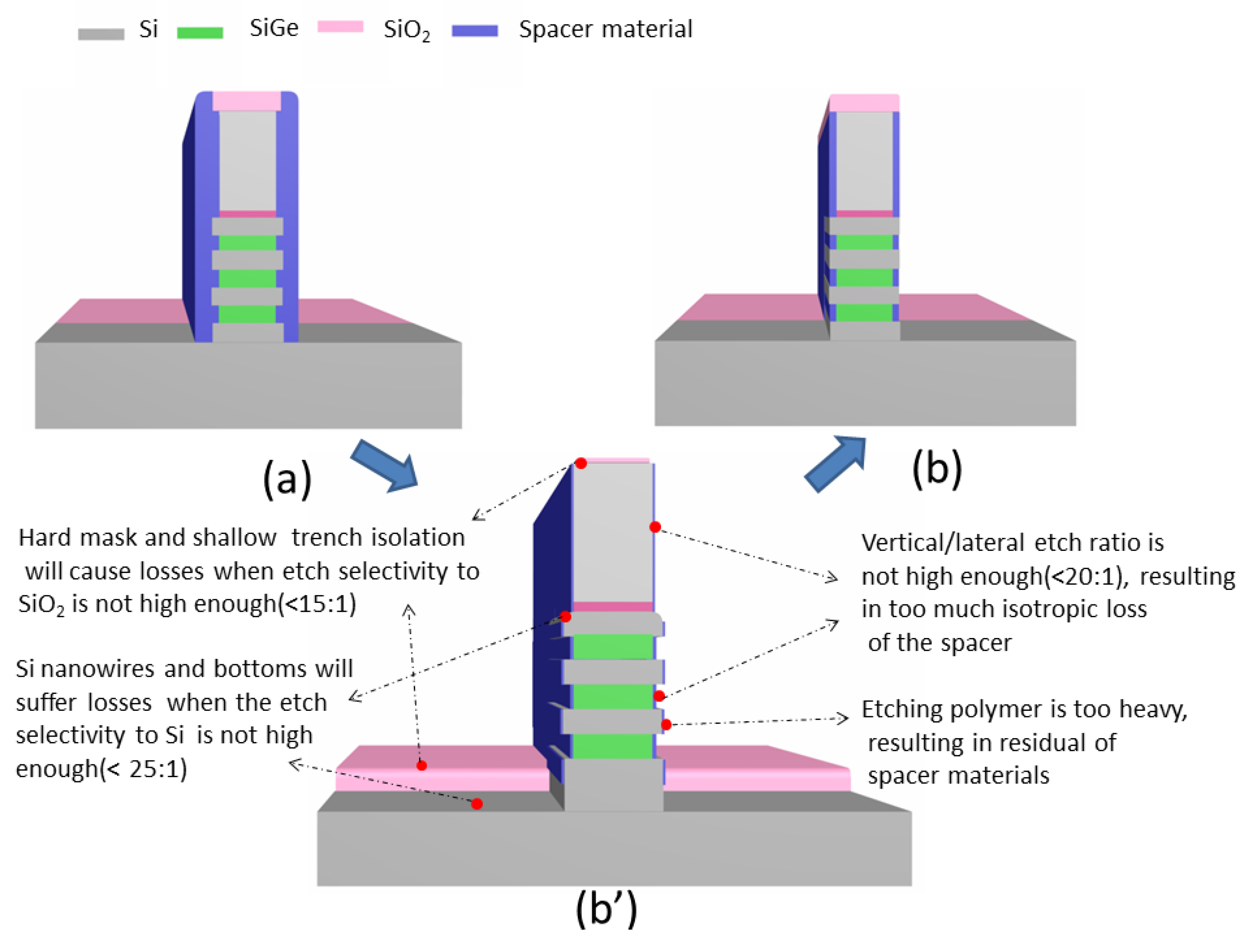

1. Introduction

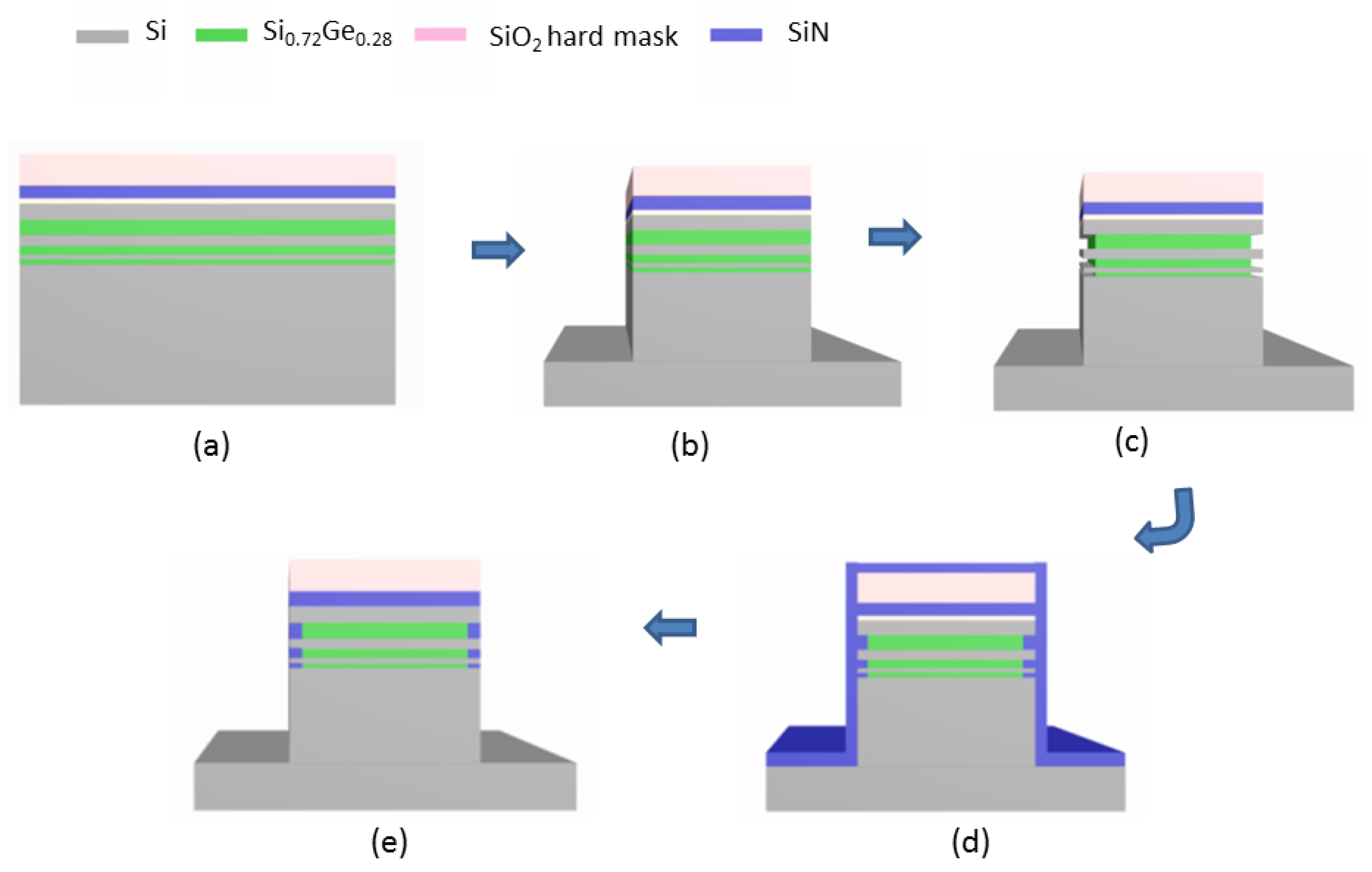

2. Materials and Methods

3. Results and Discussion

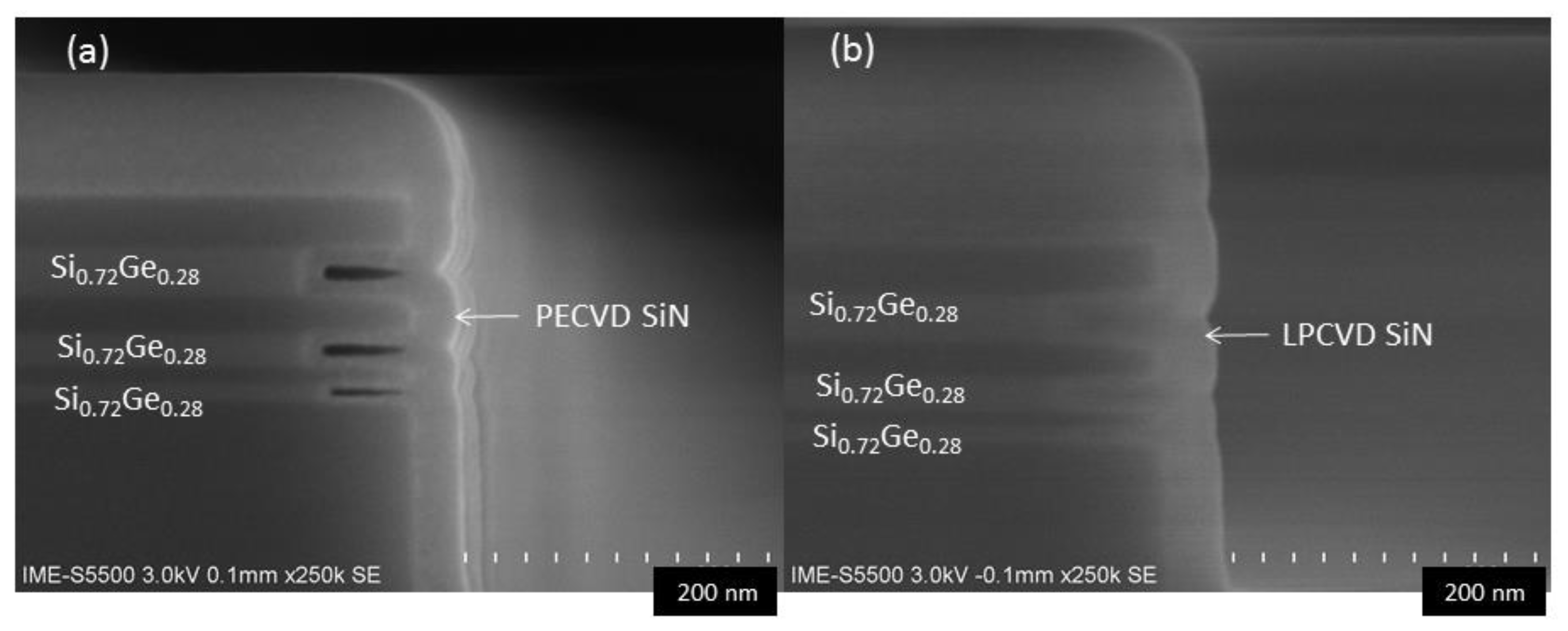

3.1. Effect of Thin Film Process on Gap Filling

3.2. Effect of CH4 Flow on Inner Spacer Etching

3.3. Effect of O2 Flow on Inner Spacer Etching

3.4. Effect of Pressure on Inner Spacer Etching

3.5. Material Quality and Interface Analysis

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Saremi, M.; Afzali-Kusha, A.; Mohammadi, S. Ground plane fin-shaped field effect transistor (GP-FinFET): A FinFET for low leakage power circuits. Microelectron. Eng. 2012, 95, 74–82. [Google Scholar] [CrossRef]

- Imenabadi, R.M.; Saremi, M.; Vandenberghe, W. A Novel PNPN-Like Z-Shaped Tunnel Field- Effect Transistor With Improved Ambipolar Behavior and RF Performance. IEEE Trans. Electron Devices 2017, 64, 4752–4758. [Google Scholar] [CrossRef]

- Abadi, R.M.I.; Saremi, M. A Resonant Tunneling Nanowire Field Effect Transistor with Physical Contractions: A Negative Differential Resistance Device for Low Power Very Large Scale Integration Applications. J. Electron. Mater. 2018, 47, 1091–1098. [Google Scholar] [CrossRef]

- Radamson, H.; He, X.; Zhang, Q.; Liu, J.; Cui, H.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. Micromachines 2019, 10, 293. [Google Scholar] [CrossRef]

- Radamson, H.H.; Zhang, Y.; He, X. The Challenges of Advanced CMOS Process from 2D to 3D. Appl. Sci.-Basel 2017, 7, 1047. [Google Scholar] [CrossRef]

- Moon, D.-I.; Choi, S.-J.; Duarte, J.P.; Choi, Y.-K. Investigation of Silicon Nanowire Gate-All-Around Junctionless Transistors Built on a Bulk Substrate. IEEE Trans. Electron Devices 2013, 60, 1355–1360. [Google Scholar] [CrossRef]

- Zhang, Q.; Yin, H.; Meng, L.; Yao, J.; Li, J.; Wang, G.; Li, Y.; Wu, Z.; Xiong, W.; Yang, H.; et al. Novel GAA Si Nanowire p-MOSFETs With Excellent Short-Channel Effect Immunity via an Advanced Forming Process. IEEE Electron Device Lett. 2018, 39, 464–467. [Google Scholar] [CrossRef]

- Mertens, H.; Ritzenthaler, R.; Chasin, R. Vertically Stacked Gate-All-Around Si Nanowire CMOS Transistors with Dual Work Function Metal Gates. In Proceedings of the IEEE 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [Google Scholar]

- Yin, X.; Zhang, Y.; Zhu, H.; Wang, G.L.; Li, J.J.; Du, A.Y.; Xie, L. Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variation. IEEE Electron Device Lett. 2020, 41, 8–11. [Google Scholar] [CrossRef]

- Loubet, N.; Hook, T.; Montanini, P. Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET. In Proceedings of the IEEE 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Pena1, V. Vertically Stacked Gate-All-Around Si Nanowire Transistors:Key Process Optimizations and Ring Oscillator Demonstration. In Proceedings of the IEEE 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017. [Google Scholar]

- Kal, S.; Pereira, C.; Oniki, Y. Selective isotropic etching of Group IV semiconductors to enable gate all around device architectures. In Proceedings of the 19th The Surface Preparation and Cleaning Conference (SPCC), Cambridge, MA, USA, 10–11 April 2018. [Google Scholar]

- Oniki, Y.; Altamirano-Sánchez, E.; Holsteyns, F. Selective Etches for Gate-All-Around (GAA) Device Integration: Opportunities and Challenges. ECS Trans. 2019, 92, 3–12. [Google Scholar] [CrossRef]

- Loubet, N.; Kal, S.; Alix, C. A Novel Dry Selective Etch of SiGe for the Enablement of High Performance Logic Stacked Gate-All-Around NanoSheet Devices. In Proceedings of the IEEE 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Li, J.; Wang, W.; Li, Y.; Zhou, N.; Wang, G.; Kong, Z.; Fu, J.; Yin, X.; Li, C.; Wang, X.; et al. Study of selective isotropic etching Si1−xGex in process of nanowire transistors. J. Mater. Sci. Mater. Electron. 2020, 31, 134–143. [Google Scholar] [CrossRef]

- Li, J.; Li, Y.; Zhou, N.; Wang, G.; Zhang, Q. A Novel Dry Selective Isotropic Atomic Layer Etching of SiGe for Manufacturing Vertical Nanowire Array with Diameter Less than 20 nm. Materials 2020, 13, 771. [Google Scholar] [CrossRef] [PubMed]

- Koehler, F.H.; Triyoso, D.; Hussain, I. Challenges in spacer process developmen for leading-edge high-k metal gate technology. Phys. Status Solidi-R. 2014, 11, 73–76. [Google Scholar]

- Hållstedt, J.; Hellström, P.; Radamson, H.H. Sidewall transfer lithography for reliable fabrication of nanowires and deca-nanometer MOSFETs. Thin Solid Films 2008, 517, 117–120. [Google Scholar] [CrossRef]

- Kaneko, A.; Yagishita, A.K.; Yahashi, T. Sidewall Transfer Process and Selective Gate Sidewall Spacer Formation Technology for Sub-15nm FinFET with Elevated Source/Drain Extension. In Proceedings of the IEEE 2005 IEEE International Electron Devices Meeting (IEDM), Tempe, AZ, USA, 5 December 2005. [Google Scholar]

- Kastenmeier, B.; Matsuo, P.; Beulens, J. Chemical dry etching of silicon nitride and silicon dioxide using CF4/O2/N2 gas mixtures. J. Vac. Sci. Technol. A 1996, 14, 2802–2812. [Google Scholar] [CrossRef]

- Nakayama, D.; Wada, A.; Kubota1, T. Highly selective silicon nitride etching to Si and SiO2 for a gate sidewall spacer using a CF3I/O2/H2 neutral beam. J. Phys. D Appl. Phys. 2013, 46, 1–7. [Google Scholar] [CrossRef]

- Kastenmeier, B.E.E.; Matsuo, P.J.; Oehrlein, G.S. Highly selective etching of silicon nitride over silicon and silicon dioxide. J. Vac. Sci. Technol. A 1999, 17, 3179–3184. [Google Scholar] [CrossRef]

- Sherpa, S.D.; Ranjan, A. Quasi-atomic layer etching of silicon nitride. J. Vac. Sci. Technol. A 2017, 35, 01A102. [Google Scholar] [CrossRef]

- Posseme, N.; Ah-Leung, V.; Pollet, O. Thin layer etching of silicon nitride: A comprehensive study of selective removal using NH3/NF3 remote plasma. J. Vac. Sci. Technol. A 2016, 34, 061301. [Google Scholar] [CrossRef]

- Posseme, N.; Pollet, O.; Barnola, S. Alternative process for thin layer etching: Application to nitride spacer etching stopping on silicon germanium. Appl. Phys. Lett. 2014, 105, 051605. [Google Scholar] [CrossRef]

- Radamson, H.H.; Simoen, E.; Luo, J.; Zhao, C. Past, Present and Future of CMOS; Elsevier: London, UK, 2018. [Google Scholar]

- Radamson, H.H.; Thylen, L. Monolithic Nanoscale Photonics-Electronics Integration in Silicon and Other Group 1V Elements; Elsevier: San Diego, CA, USA, 2014. [Google Scholar]

- Wang, G.; Abedin, A.; Moeen, M.; Kolahdouz, M.; Luo, J.; Guo, Y.; Zhao, C. Integration of highly-strained SiGe materials in 14 nm and beyond nodes FinFETtechnology. Solid State Electron. 2018, 103, 222–228. [Google Scholar] [CrossRef]

- Wang, G.; Luo, J.; Qin, C.; Liang, R.; Xu, Y.; Liu, J.; Xu, J. Integration of Highly Strained SiGe in Source and Drain with HK and MG for 22 nm Bulk PMOS Transistors. Nanoscale Res. Lett. 2017, 12, 1–7. [Google Scholar] [CrossRef] [PubMed]

- Zhang, Q.; Tu, H.; Gu, S. Influence of Rapid Thermal Annealing on Ge-Si Interdiffusion in Epitaxial Multilayer Ge0.3Si0.7/Si Superlattices with Various GeSi Thicknesses. ECS J. Solid State Sci. Technol. 2018, 7, 671–676. [Google Scholar] [CrossRef]

- Bangsaruntip, S.; Cohen, G.M.; Majumdar, A.; Zhang, Y.; Engelmann, S.U.; Fuller, N.C.M.; Gignac, L.M.; Mittal, S.; Newbury, J.S.; Guillorn, M.; et al. High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling. In Proceedings of the IEEE 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009. [Google Scholar]

- Bangsaruntip, S.; Balakrishnan, K.; Cheng, S.-L. Density scaling with gate-all-around silicon nanowire MOSFETs for the 10 nm node and beyond. In Proceedings of the IEEE 2013 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 9–11 December 2013. [Google Scholar]

- Nishimura, H.; Takagi, S.; Fujino, M.; Nishi, N. Gap-Fill Process of Shallow Trench Isolation for 0.13 µm Technologies. Jpn. J. Appl. Phys. 2002, 41, 2886–2893. [Google Scholar] [CrossRef]

- Nishimura, H.; Takagi, S.; Joshi, M.; Eranna, G.; Runthala, D. LPCVD and PECVD silicon nitride for microelectronics technology. Indian J. Eng. Mater. Sci. 2000, 7, 303–309. [Google Scholar]

- Donnelly, V.M.; Kornblit, A. Plasma etching: Yesterday, today, and tomorrow. J. Vac. Sci. Technol. A 2013, 31, 050825. [Google Scholar] [CrossRef]

- Park, J.; Hu, C. Air Spacer MOSFET Technology for 20nm Node and Beyond. In Proceedings of the IEEE 2008 9th International Conference on Solid-State and Integrated-Circuit Technology (ICSICT), Beijing, China, 20–23 October 2008. [Google Scholar]

| Parameter | Data in This Work 1 | Ref. [21] 2 | Ref. [22] 3 | Ref. [24] 4 |

|---|---|---|---|---|

| Selectivity to Si | 101.5 | 6.2 | 100 | -- 5 |

| Selectivity to SiO2 | 31.6 | 18.6 | 70 | 100 |

| Vertical/lateral etch ratio | 82.5 | -- 5 | 1 | 8 |

| Etch accuracy (%) | 2 | -- 5 | -- 5 | -- 5 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, J.; Li, Y.; Zhou, N.; Xiong, W.; Wang, G.; Zhang, Q.; Du, A.; Gao, J.; Kong, Z.; Lin, H.; et al. Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors. Nanomaterials 2020, 10, 793. https://doi.org/10.3390/nano10040793

Li J, Li Y, Zhou N, Xiong W, Wang G, Zhang Q, Du A, Gao J, Kong Z, Lin H, et al. Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors. Nanomaterials. 2020; 10(4):793. https://doi.org/10.3390/nano10040793

Chicago/Turabian StyleLi, Junjie, Yongliang Li, Na Zhou, Wenjuan Xiong, Guilei Wang, Qingzhu Zhang, Anyan Du, Jianfeng Gao, Zhenzhen Kong, Hongxiao Lin, and et al. 2020. "Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors" Nanomaterials 10, no. 4: 793. https://doi.org/10.3390/nano10040793

APA StyleLi, J., Li, Y., Zhou, N., Xiong, W., Wang, G., Zhang, Q., Du, A., Gao, J., Kong, Z., Lin, H., Xiang, J., Li, C., Yin, X., Wang, X., Yang, H., Ma, X., Han, J., Zhang, J., Hu, T., ... Radamson, H. H. (2020). Study of Silicon Nitride Inner Spacer Formation in Process of Gate-all-around Nano-Transistors. Nanomaterials, 10(4), 793. https://doi.org/10.3390/nano10040793