Border Trap Characterizations of Al2O3/ZrO2 and Al2O3/HfO2 Bilayer Films Based on Ambient Post Metal Annealing and Constant Voltage Stress

Abstract

1. Introduction

2. Materials and Methods

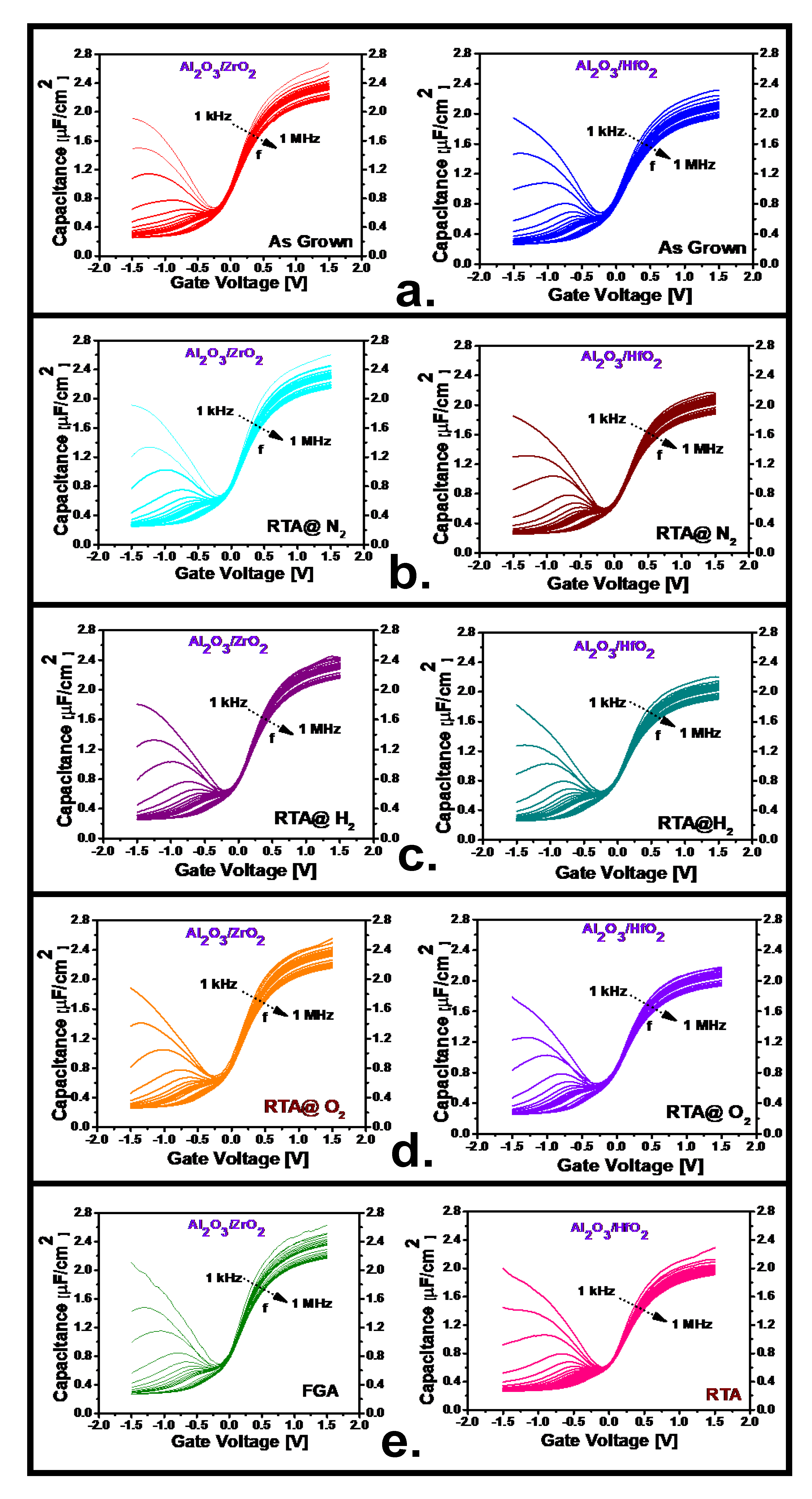

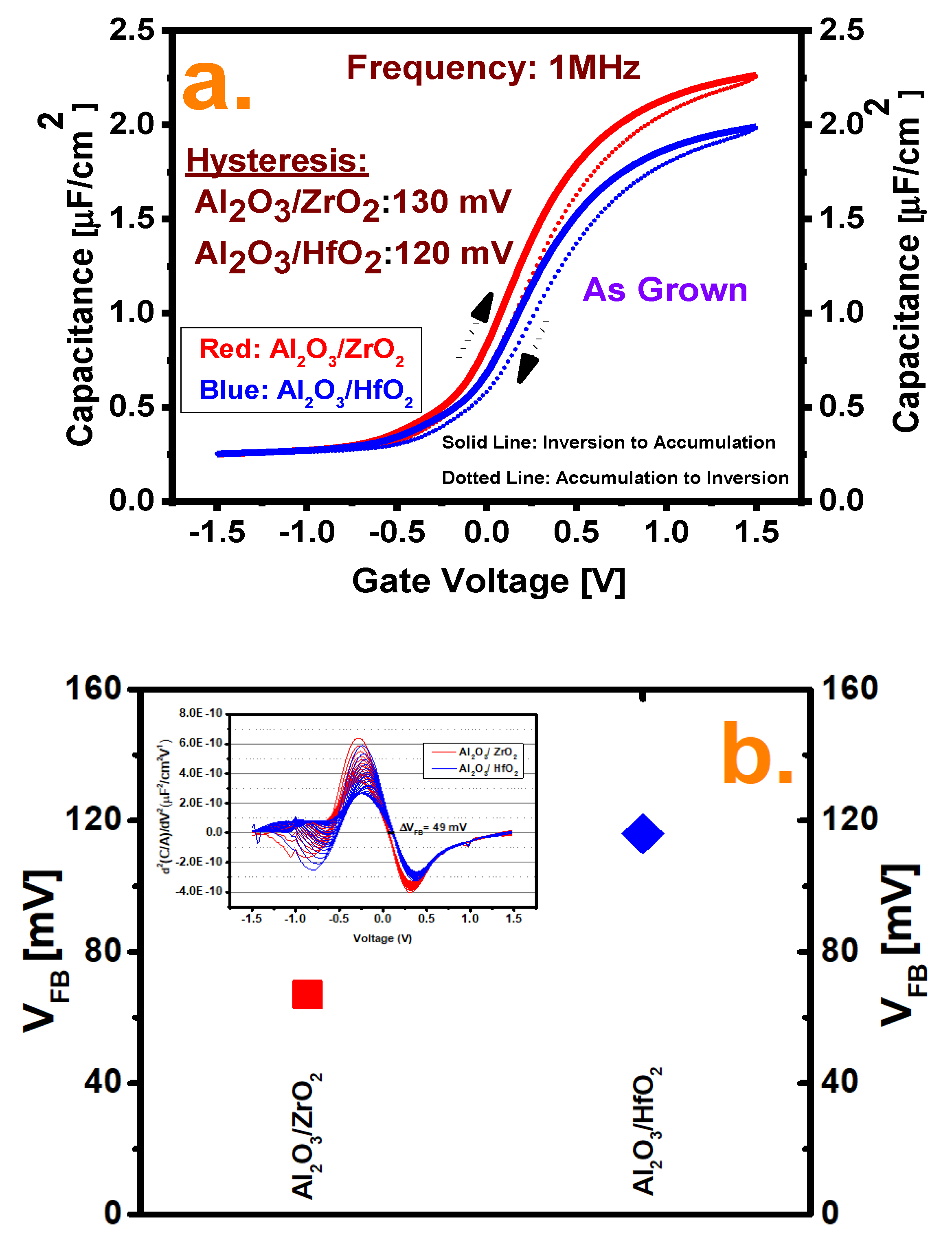

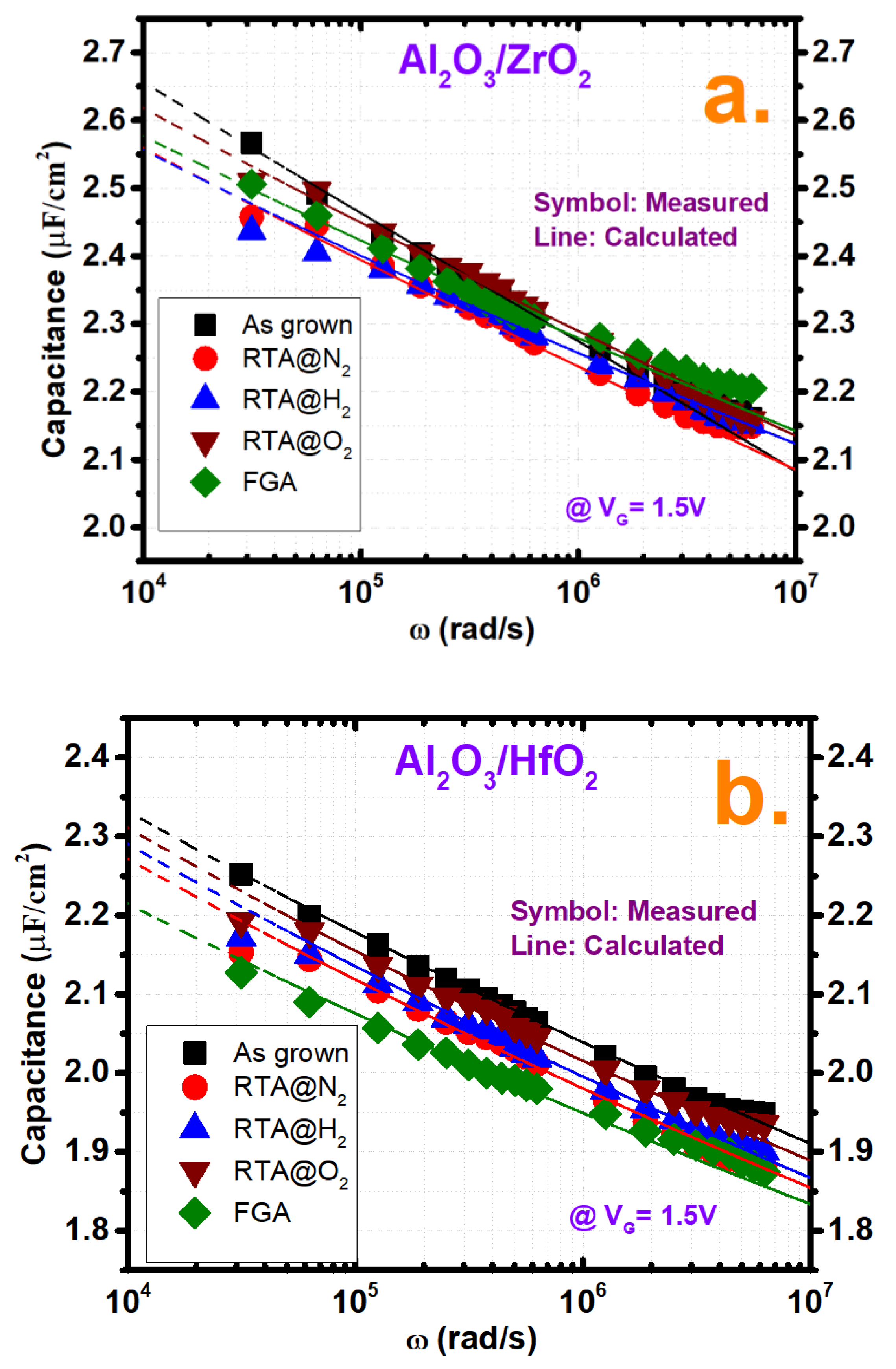

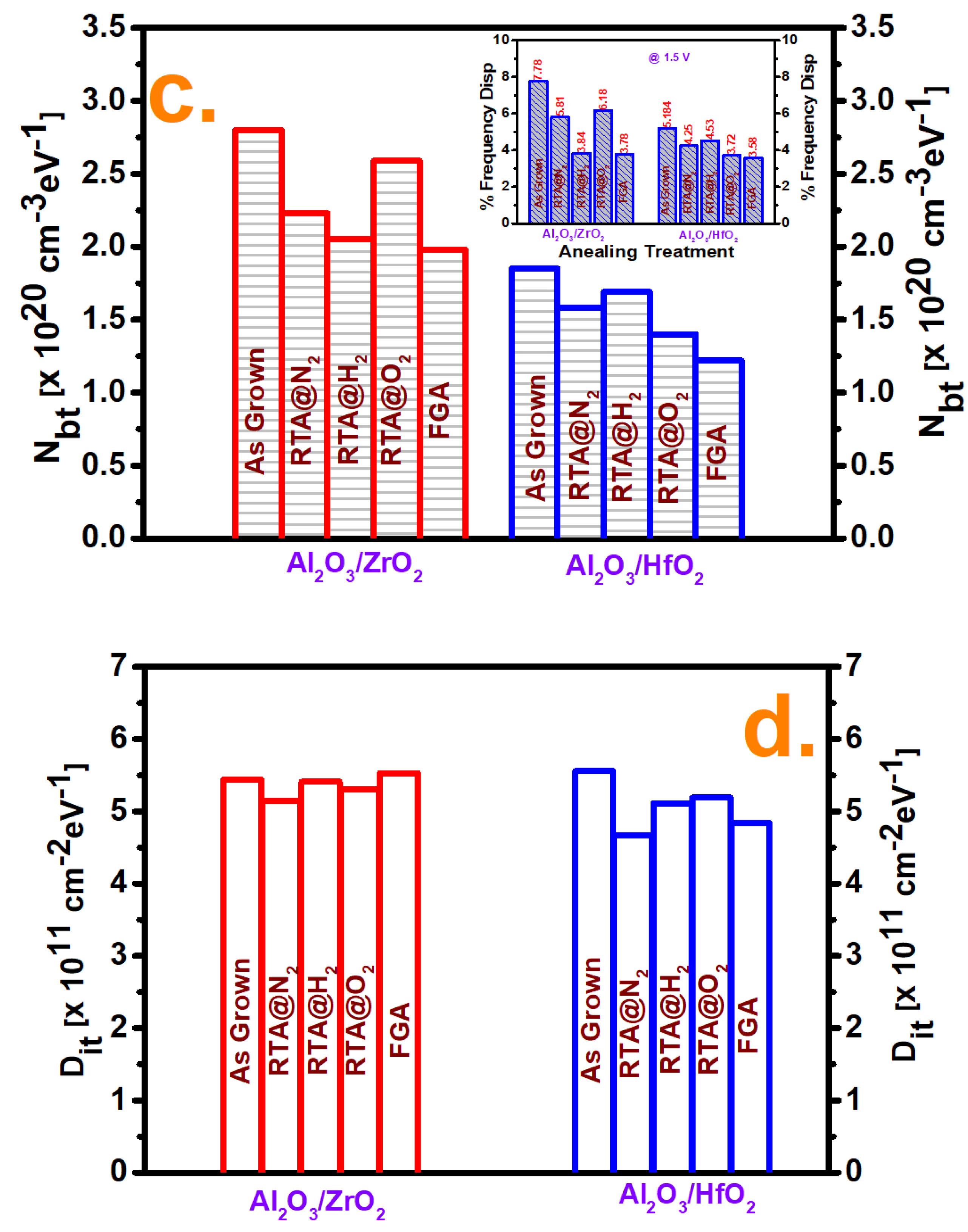

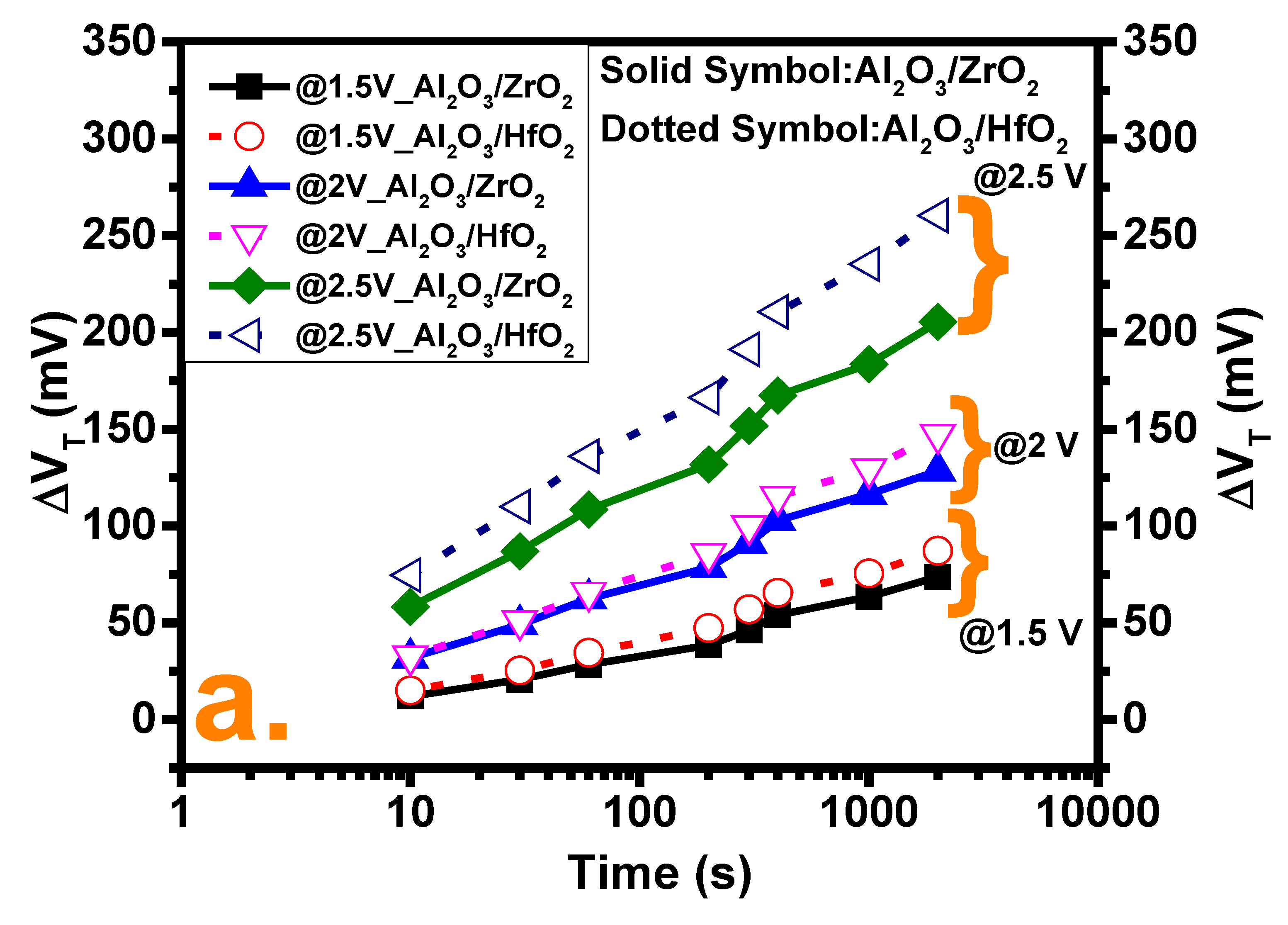

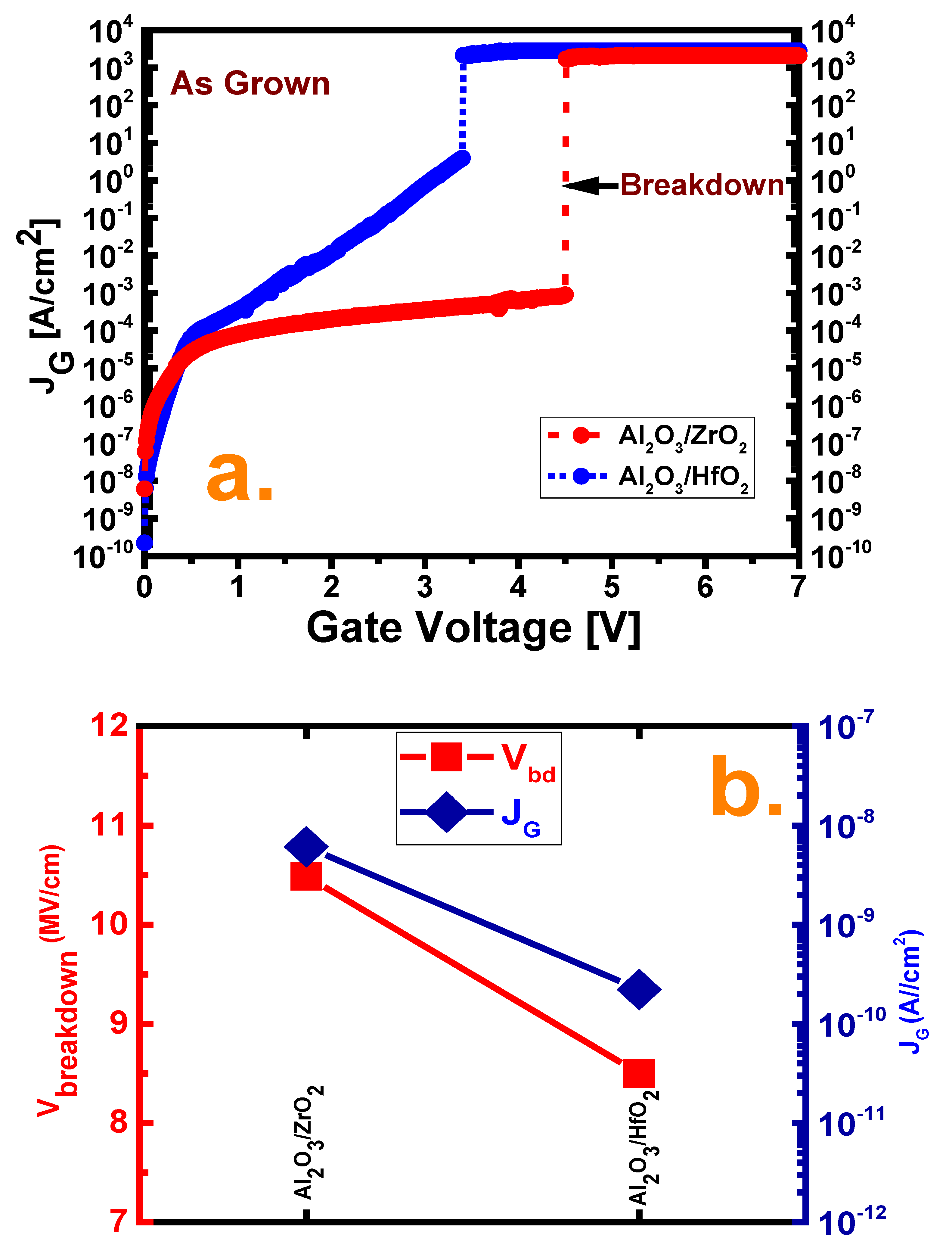

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Del Alamo, J.A. Nanometre-scale electronics with III–V compound semiconductors. Nature 2011, 479, 317–323. [Google Scholar] [CrossRef] [PubMed]

- Baik, M.; Kang, H.-K.; Kang, Y.-S.; Jeong, K.-S.; An, Y.; Choi, S.; Kim, H.; Song, J.-D.; Cho, M.-H. Electrical properties and thermal stability in stack structure of HfO2/Al2O3/InSb by atomic layer deposition. Sci. Rep. 2017, 7, 11337. [Google Scholar] [CrossRef] [PubMed]

- Rahman, M.M.; Kim, J.-G.; Kim, D.-H.; Kim, T.-W. Characterization of Al Incorporation into HfO2 Dielectric by Atomic Layer Deposition. Micromachines 2019, 10, 361. [Google Scholar] [CrossRef] [PubMed]

- Tahir, D.; Jae Kang, H.; Tougaard, S. Band Alignment and Optical Properties of (ZrO2)0.66(HfO2)0.34 Gate Dielectrics Thin Films on p-Si (100). ITB J. Sci. 2011, 43, 199–208. [Google Scholar] [CrossRef][Green Version]

- Kang, H.K.; Kang, Y.S.; Kim, D.K.; Baik, M.; Song, J.D.; An, Y.; Kim, H.; Cho, M.H. Al2O3 Passivation Effect in HfO2·Al2O3 Laminate Structures Grown on InP Substrates. ACS Appl. Mater. Interfaces 2017, 9, 17526–17535. [Google Scholar] [CrossRef] [PubMed]

- Kim, I.; Koo, J.; Lee, J.; Jeon, H. A Comparison of Al2O3/HfO2 and Al2O3/ZrO2 Bilayers Deposited by the Atomic Layer Deposition Method for Potential Gate Dielectric Applications. Jpn. J. Appl. Phys. 2006, 45, 919–925. [Google Scholar] [CrossRef]

- Rahman, M.M.; Kim, J.-G.; Kim, D.-H.; Kim, T. Comparison of the interface and border traps of nanolaminate and bilayer structures of Al2O3 and HfO2 on In0.53Ga0.47As. Jpn. J. Appl. Phys. 2019, 58, 120905. [Google Scholar] [CrossRef]

- Kim, J.-G.; Kwon, H.-M.; Kim, D.-H.; Kim, T.-W. Impact of in situ atomic layer deposition TiN/high-κ stack onto In 0.53 Ga0.47 As MOSCAPs on 300 mm Si substrate. Jpn. J. Appl. Phys. 2019, 58, 040905. [Google Scholar] [CrossRef]

- Chobpattana, V.; Mikheev, E.; Zhang, J.Y.; Mates, T.E.; Stemmer, S. Extremely scaled high-k /In0.53 Ga 0.47 As gate stacks with low leakage and low interface trap densities. J. Appl. Phys. 2014, 116, 124104. [Google Scholar] [CrossRef]

- Rahman, M.M.; Kim, J.-G.; Kim, D.-H.; Kim, T.-W. Border Trap Extraction with Capacitance- Equivalent Thickness to Reflect the Quantum Mechanical Effect on Atomic Layer Deposition High-k/In0.53Ga0.47As on 300-mm Si Substrate. Sci. Rep. 2019, 9, 9861. [Google Scholar] [CrossRef] [PubMed]

- Dou, C.; Lin, D.; Vais, A.; Ivanov, T.; Chen, H.; Martens, K.; Kakushima, K.; Iwai, H.; Taur, Y.; Thean, A.; et al. Determination of energy and spatial distribution of oxide border traps in In0.53Ga0.47As MOS capacitors from capacitance–voltage characteristics measured at various temperatures. Microelectron. Reliab. 2014, 54, 746–754. [Google Scholar] [CrossRef]

- Fleetwood, D.M. Border traps and bias-temperature instabilities in MOS devices. Microelectron. Reliab. 2018, 80, 266–277. [Google Scholar] [CrossRef]

- Gan, J. Extraction of Border Trap Density in InAs Nanowire Transistors. Master’s Thesis, Lund University, Lund, Sweden, 2012. [Google Scholar]

- Vais, A.; Martens, K.; Lin, D.; Collaert, N.; Mocuta, A.; DeMeyer, K.; Thean, A. On MOS admittance modeling to study border trap capture/emission and its effect on electrical behavior of high-k/III–V MOS devices. Microelectron. Eng. 2015, 147, 227–230. [Google Scholar] [CrossRef]

- Kwon, H.-M.; Kwon, S.-K.; Jeong, K.-S.; Oh, S.-K.; Oh, S.-H.; Choi, W.-I.; Kim, T.-W.; Kim, D.-H.; Kang, C.-Y.; Lee, B.H.; et al. A Correlation Between Oxygen Vacancies and Reliability Characteristics in a Single Zirconium Oxide Metal-Insulator-Metal Capacitor. IEEE Trans. Electron Devices 2014, 61, 2619–2627. [Google Scholar] [CrossRef]

- Jung, H.-S.; Lee, S.-A.; Rha, S.; Lee, S.Y.; Kim, H.K.; Kim, D.H.; Oh, K.H.; Park, J.-M.; Kim, W.-H.; Song, M.-W.; et al. Impacts of Zr Composition in Hf1-xZrxOy Gate Dielectrics on Their Crystallization Behavior and Bias-Temperature-Instability Characteristics. IEEE Trans. Electron Devices 2011, 58, 2094–2103. [Google Scholar] [CrossRef]

- Lin, J.; Monaghan, S.; Cherkaoui, K.; Povey, I.M.; Sheehan, B.; Hurley, P.K. Examining the relationship between capacitance-voltage hysteresis and accumulation frequency dispersion in InGaAs metal-oxide-semiconductor structures based on the response to post-metal annealing. Microelectron. Eng. 2017, 178, 204–208. [Google Scholar] [CrossRef]

- Tang, K.; Winter, R.; Zhang, L.; Droopad, R.; Eizenberg, M.; Mcintyre, P.C. Border trap reduction in Al2O3 / InGaAs gate stacks. Appl. Phys. Lett. 2015, 107, 202102. [Google Scholar] [CrossRef]

- Orzali, T.; Vert, A.; Kim, T.-W.; Hung, P.Y.; Herman, J.L.; Vivekanand, S.; Huang, G.; Kelman, M.; Karim, Z.; Hill, R.J.W.; et al. Growth and characterization of an In0.53Ga0.47As-based Metal-Oxide-Semiconductor Capacitor (MOSCAP) structure on 300 mm on-axis Si (001) wafers by MOCVD. J. Cryst. Growth 2015, 427, 72–79. [Google Scholar] [CrossRef]

- Li, C.-C.; Chang-Liao, K.-S.; Chi, W.-F.; Li, M.-C.; Chen, T.-C.; Su, T.-H.; Chang, Y.-W.; Tsai, C.-C.; Liu, L.-J.; Fu, C.-H.; et al. Improved Electrical Characteristics of Ge pMOSFETs With ZrO2/HfO2 Stack Gate Dielectric. IEEE Electron Device Lett. 2016, 37, 12–15. [Google Scholar]

- Winter, R.; Ahn, J.; McIntyre, P.C.; Eizenberg, M. New method for determining flat-band voltage in high mobility semiconductors. J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom. 2013, 31, 030604. [Google Scholar] [CrossRef]

- Yuan, Y.; Yu, B.; Ahn, J.; McIntyre, P.C.; Asbeck, P.M.; Rodwell, M.J.W.; Taur, Y. A Distributed Bulk-Oxide Trap Model for Al2O3 InGaAs MOS Devices. IEEE Trans. Electron Devices 2012, 59, 2100–2106. [Google Scholar] [CrossRef]

- Sereni, G.; Vandelli, L.; Larcher, L.; Morassi, L.; Veksler, D.; Bersuker, G. A new method for extracting interface state and border trap densities in high-k/III-V MOSFETs. In Proceedings of the 2014 IEEE International Reliability Physics Symposium, Waikoloa, HI, USA, 1–5 June 2014; pp. 2C.3.1–2C.3.6. [Google Scholar]

- Birner, S. The Nextnano Software for the Simulation of Semiconductor Heterostructures. Available online: https://www.nextnano.de/downloads/publications/abstracts/Abstract_TopologicalNanodeviceModeling_2014_Delft_Birner.pdf (accessed on 19 July 2019).

- Engel-Herbert, R.; Hwang, Y.; Stemmer, S. Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces. J. Appl. Phys. 2010, 108, 124101. [Google Scholar] [CrossRef]

- Lin, D.; Alian, A.; Gupta, S.; Yang, B.; Bury, E.; Sioncke, S.; Degraeve, R.; Toledano, M.L.; Krom, R.; Favia, P.; et al. Beyond interface: The impact of oxide border traps on InGaAs and Ge n-MOSFETs. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 28.3.1–28.3.4. [Google Scholar]

- Lin, J.; Monaghan, S.; Cherkaoui, K.; Povey, I.; O’Connor, É.; Sheehan, B.; Hurley, P. A study of capacitance–voltage hysteresis in the HfO2/InGaAs metal-oxide-semiconductor system. Microelectron. Eng. 2015, 147, 273–276. [Google Scholar] [CrossRef]

- Berthelot, A.; Caillat, C.; Huard, V.; Barnola, S.; Boeck, B.; Del-Puppo, H.; Emonet, N.; Lalanne, F. Highly Reliable TiN/ZrO2/TiN 3D Stacked Capacitors for 45 nm Embedded DRAM Technologies. In Proceedings of the 2006 European Solid-State Device Research Conference, Montreux, Switzerland, 19–21 September 2006; pp. 343–346. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rahman, M.M.; Kim, D.-H.; Kim, T.-W. Border Trap Characterizations of Al2O3/ZrO2 and Al2O3/HfO2 Bilayer Films Based on Ambient Post Metal Annealing and Constant Voltage Stress. Nanomaterials 2020, 10, 527. https://doi.org/10.3390/nano10030527

Rahman MM, Kim D-H, Kim T-W. Border Trap Characterizations of Al2O3/ZrO2 and Al2O3/HfO2 Bilayer Films Based on Ambient Post Metal Annealing and Constant Voltage Stress. Nanomaterials. 2020; 10(3):527. https://doi.org/10.3390/nano10030527

Chicago/Turabian StyleRahman, Md. Mamunur, Dae-Hyun Kim, and Tae-Woo Kim. 2020. "Border Trap Characterizations of Al2O3/ZrO2 and Al2O3/HfO2 Bilayer Films Based on Ambient Post Metal Annealing and Constant Voltage Stress" Nanomaterials 10, no. 3: 527. https://doi.org/10.3390/nano10030527

APA StyleRahman, M. M., Kim, D.-H., & Kim, T.-W. (2020). Border Trap Characterizations of Al2O3/ZrO2 and Al2O3/HfO2 Bilayer Films Based on Ambient Post Metal Annealing and Constant Voltage Stress. Nanomaterials, 10(3), 527. https://doi.org/10.3390/nano10030527