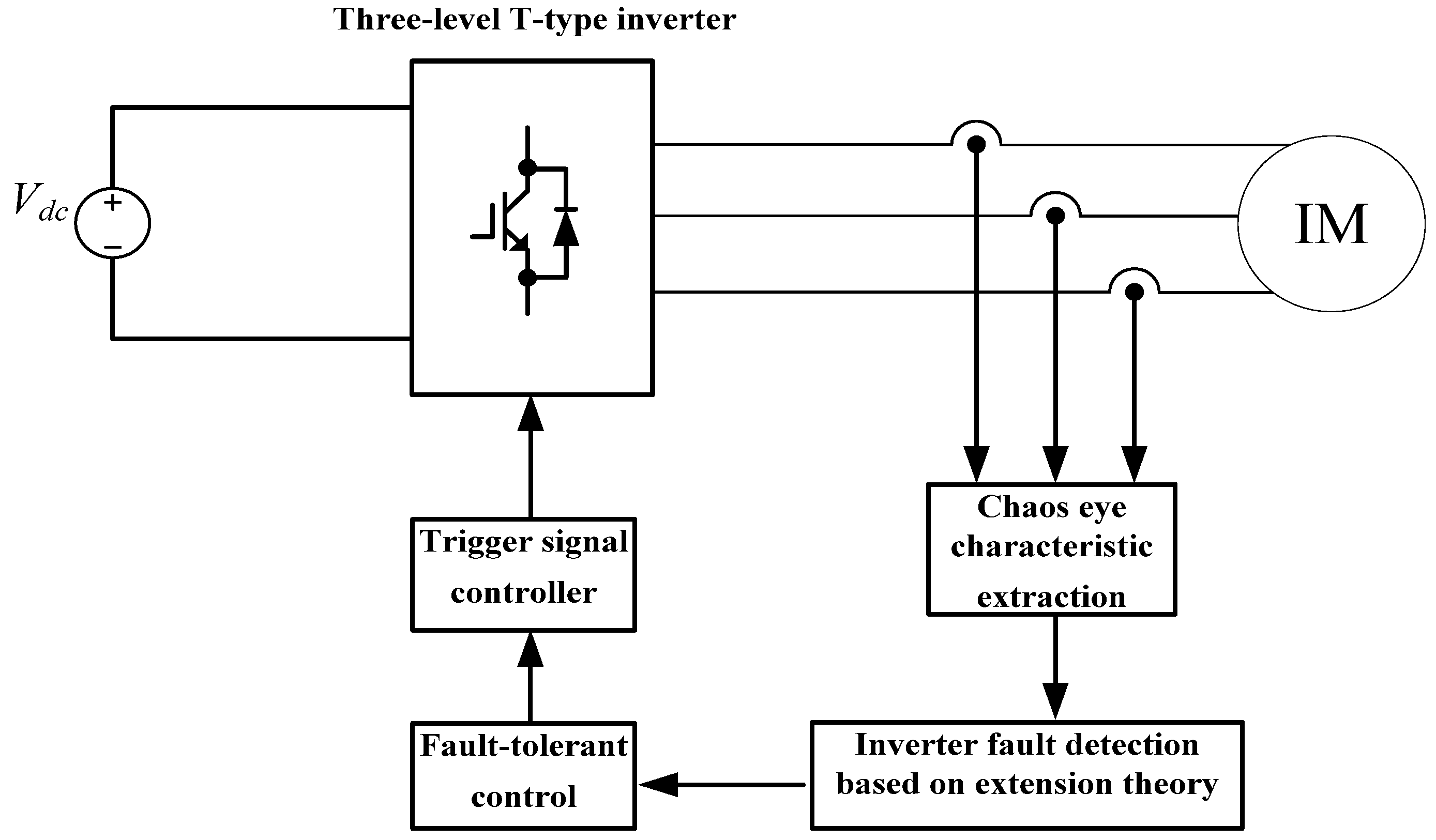

Smart Fault-Tolerant Control System Based on Chaos Theory and Extension Theory for Locating Faults in a Three-Level T-Type Inverter

Abstract

:1. Introduction

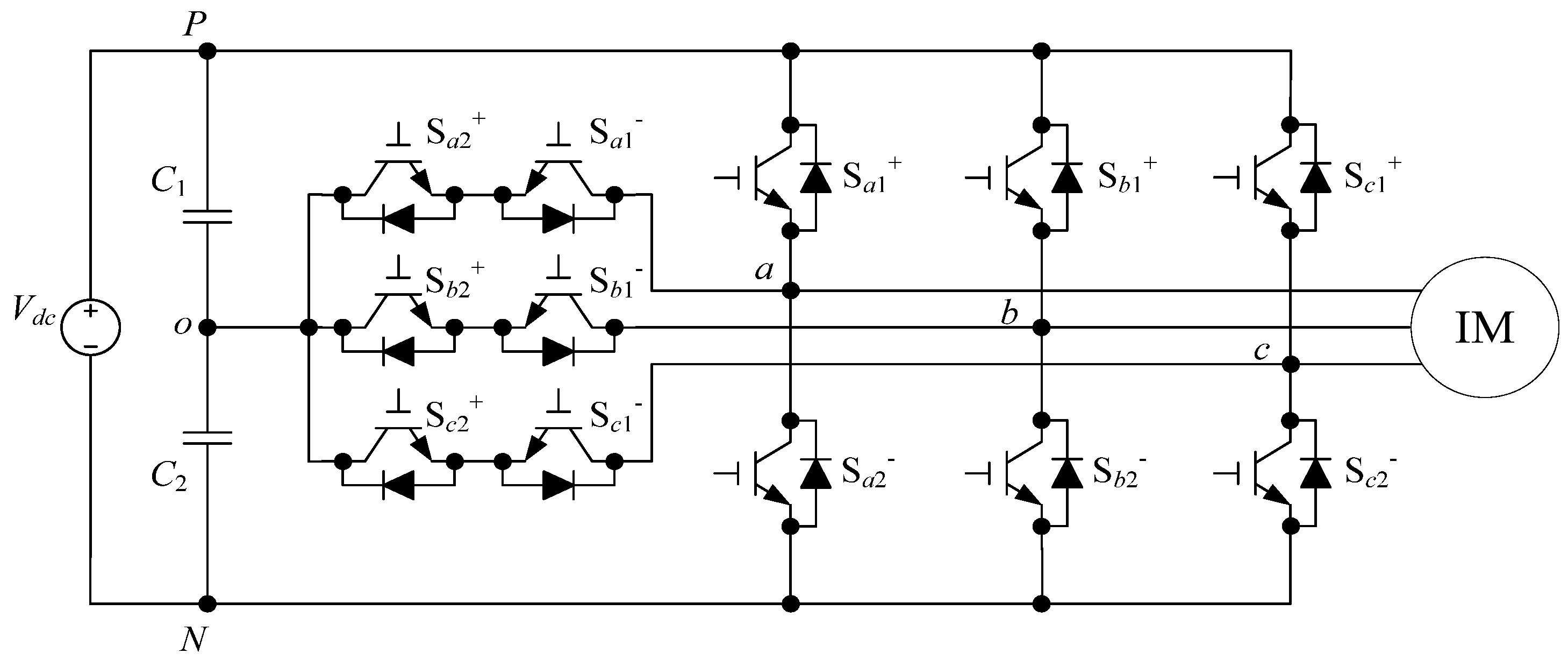

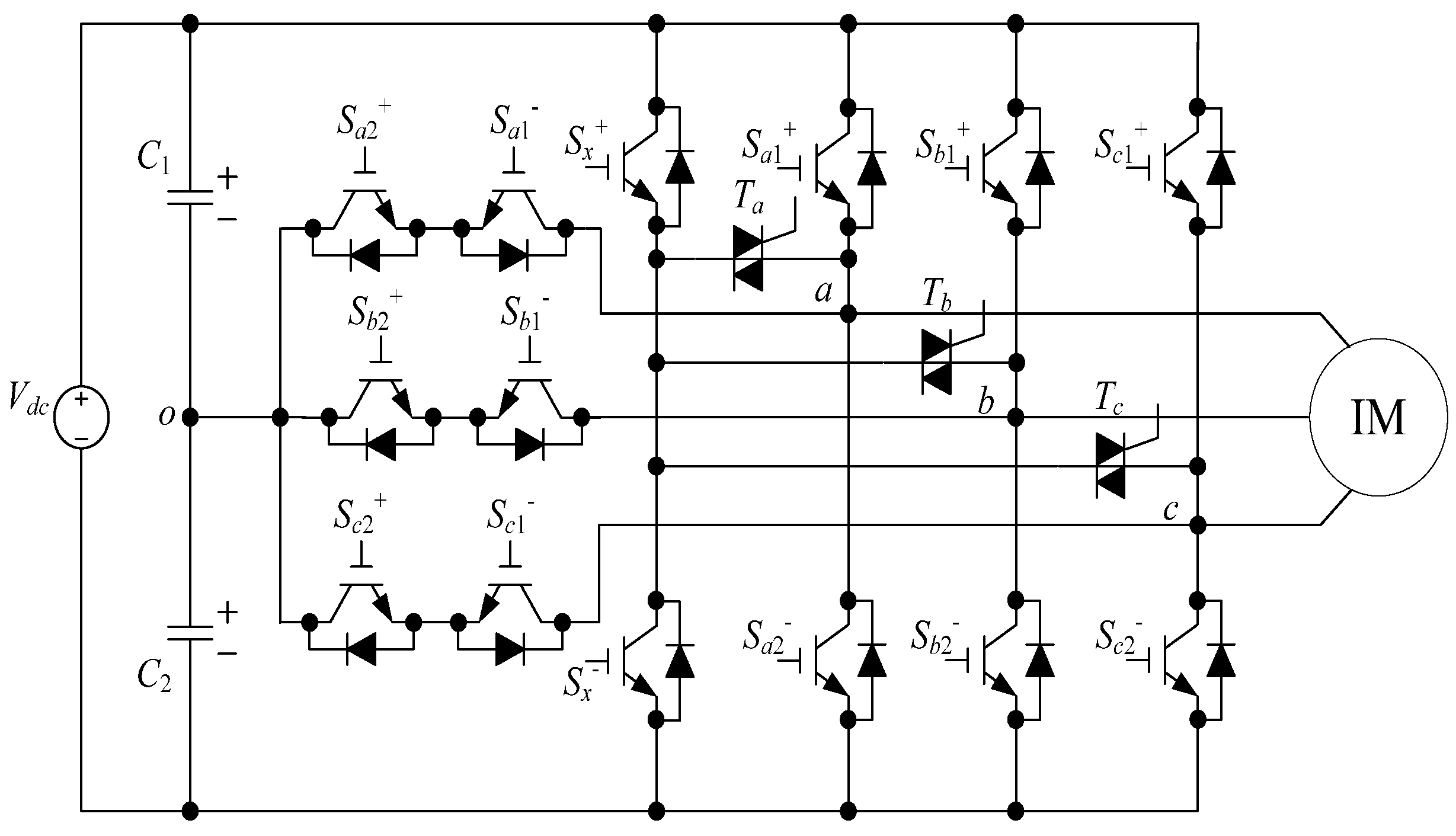

2. Materials and Methods

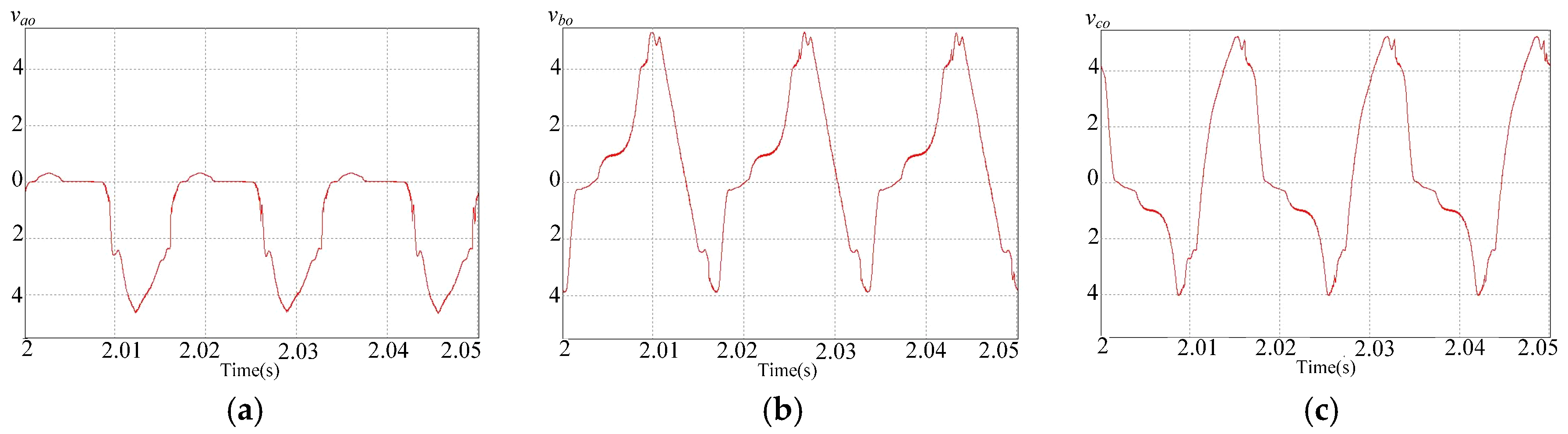

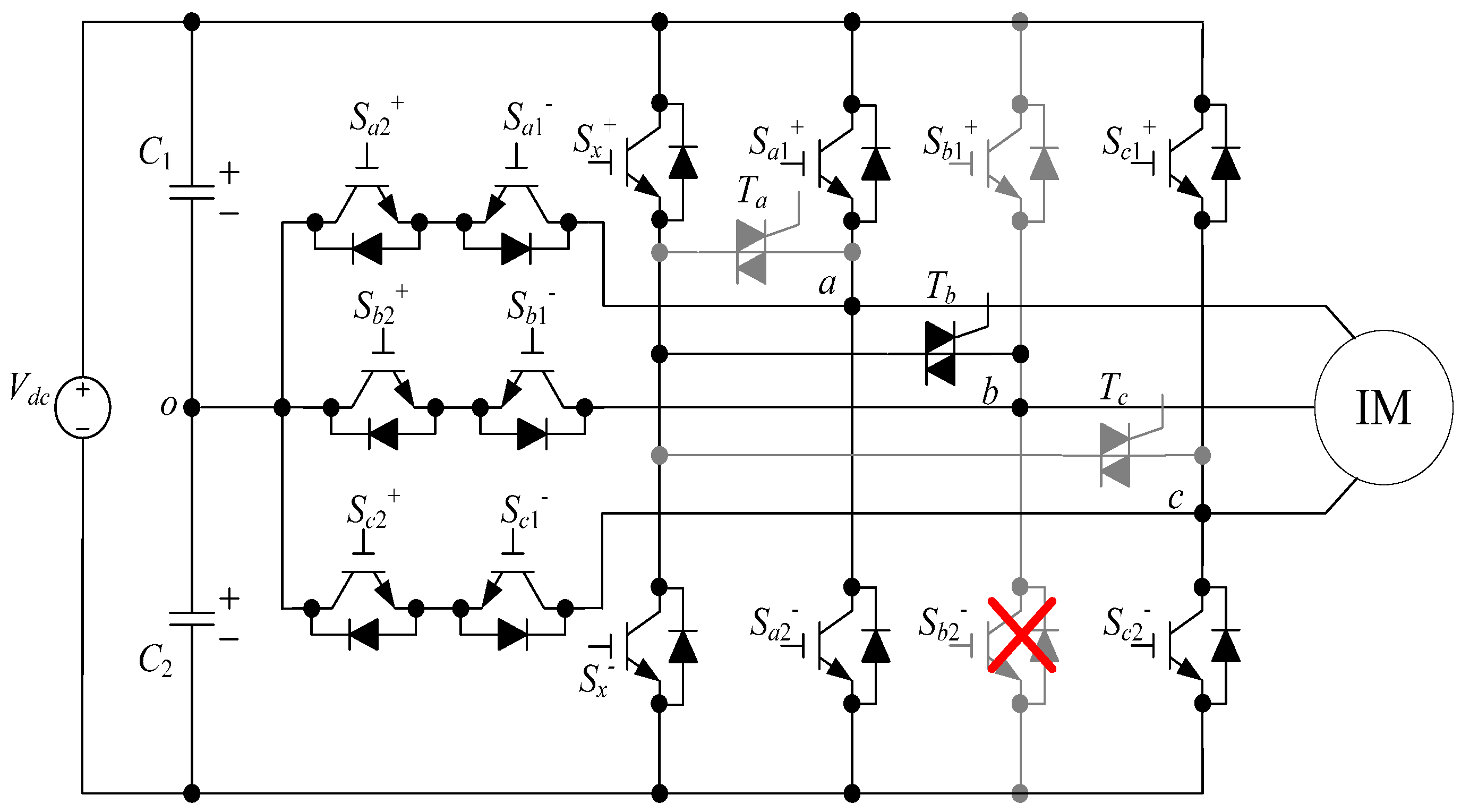

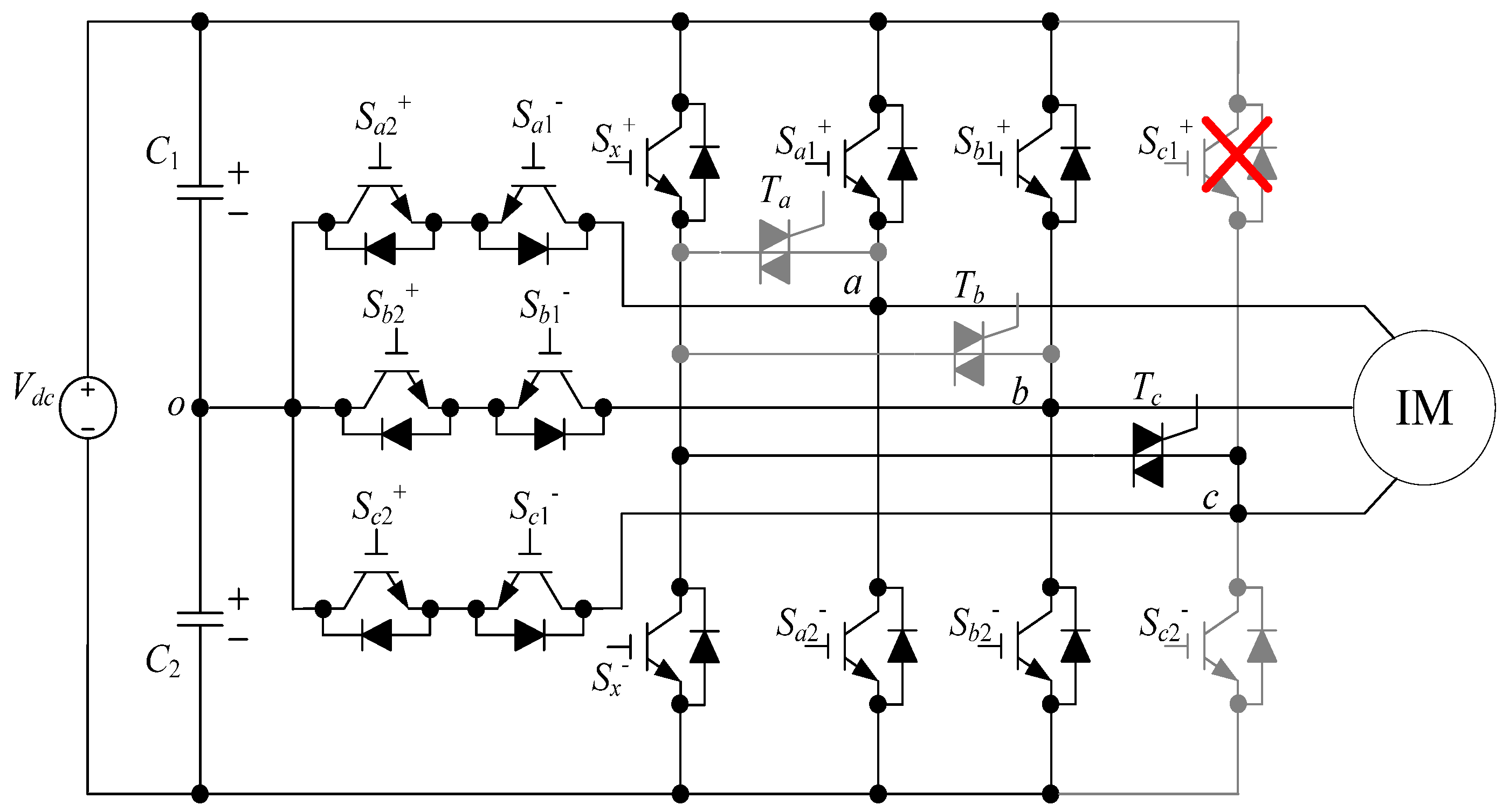

2.1. Fault Characteristics of Three-Level Inverter

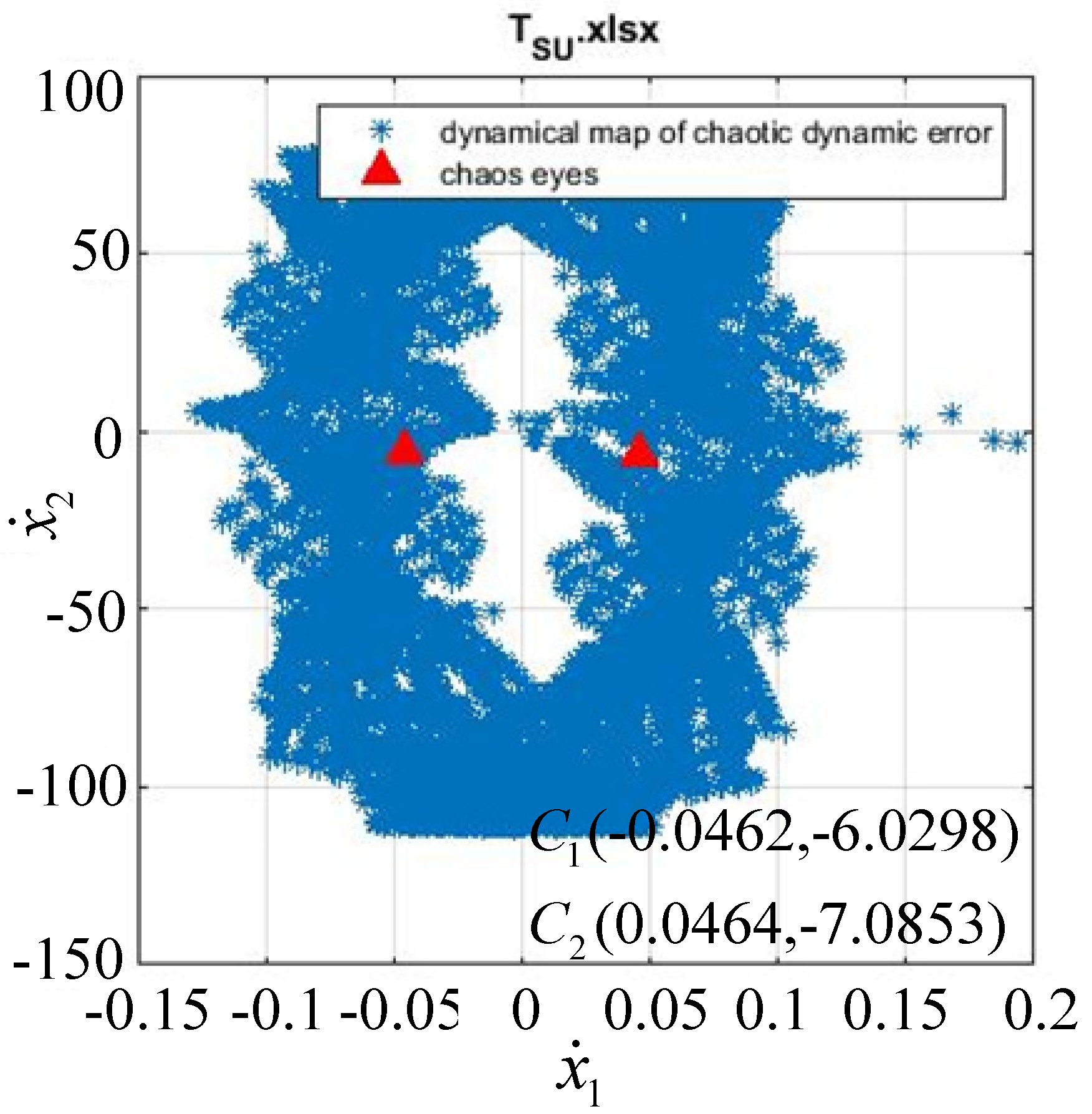

2.2. Theory of the Lorenz Chaotic System

2.3. Inverter Fault Diagnosis Based on Extension Theory

2.3.1. Concept of Extension Matter

2.3.2. Distance and Position Value

2.3.3. Correlation Function

- Step 1.

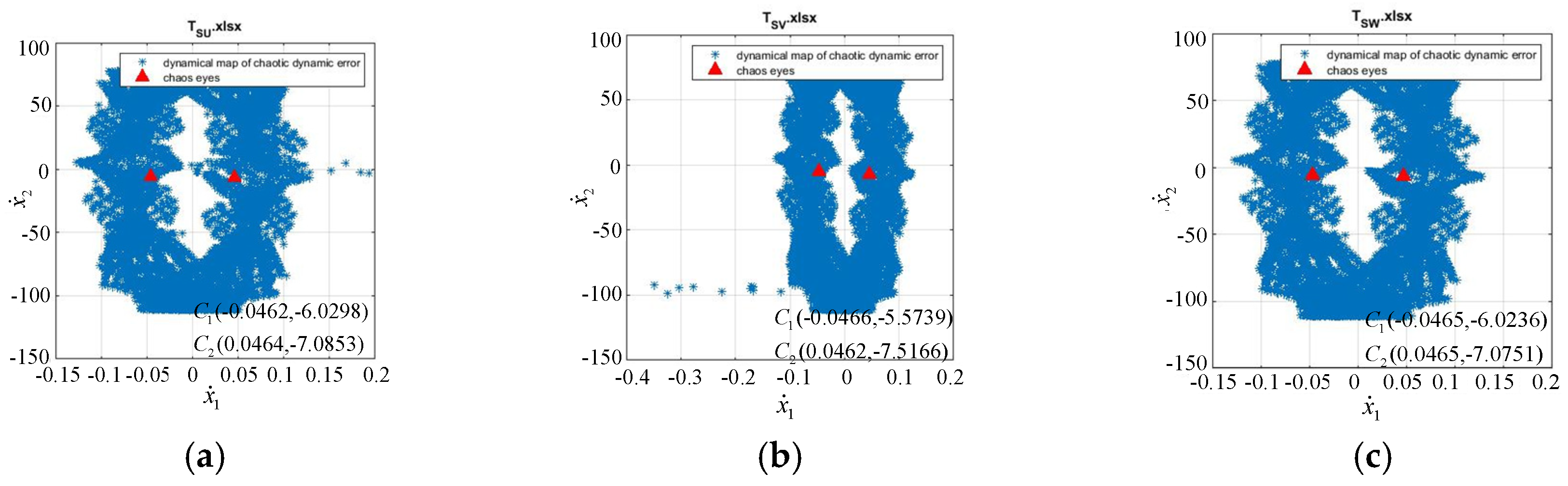

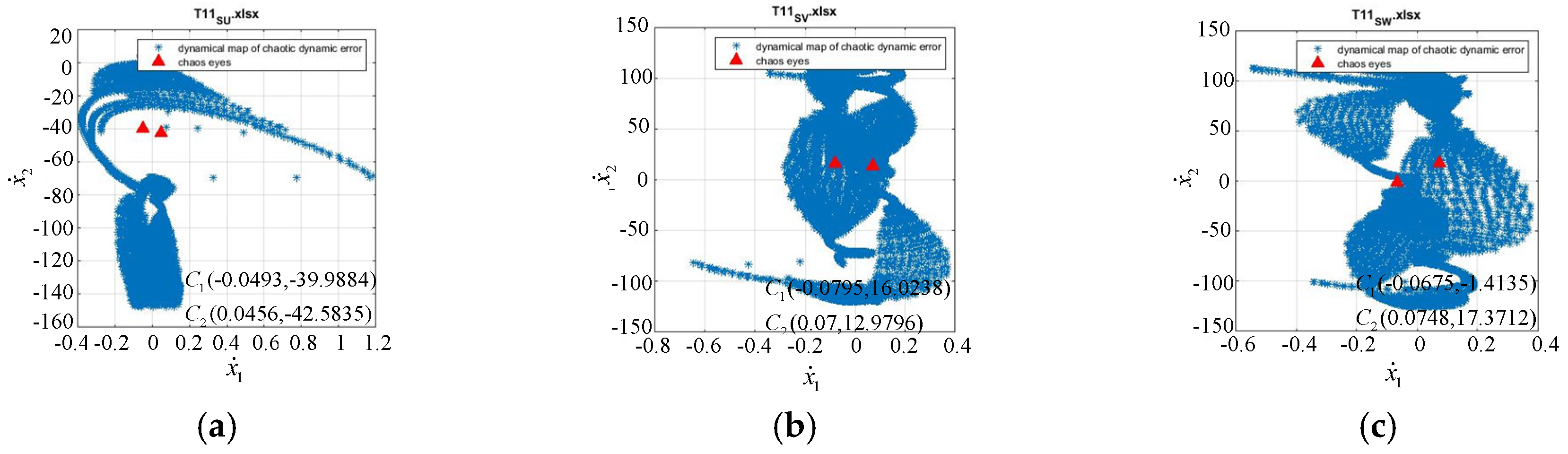

- For each transistor failure, the chaos eye coordinates C1 and C2 on the chaos scatter diagram are used to establish the matter element model.

- Step 2.

- The chaos eye coordinates of the faulty transistor to be determined, namely C1 and C2, are input into the model, and the resulting matter element model can be expressed as follows:

- Step 3.

- The characteristics (C1 and C2) and their corresponding weights W1 and W2 (representing the relative importance of the characteristics) are determined. Here, W1 = W2 = 0.5.

- Step 4.

- The degree of correlation between the fault categories of characteristics to be tested is calculated.

- Step 5.

- The largest correlation value of each fault category derived from the calculation represents the fault category to which a fault characteristic belongs. Therefore, the faulty transistor can be determined according to the category.

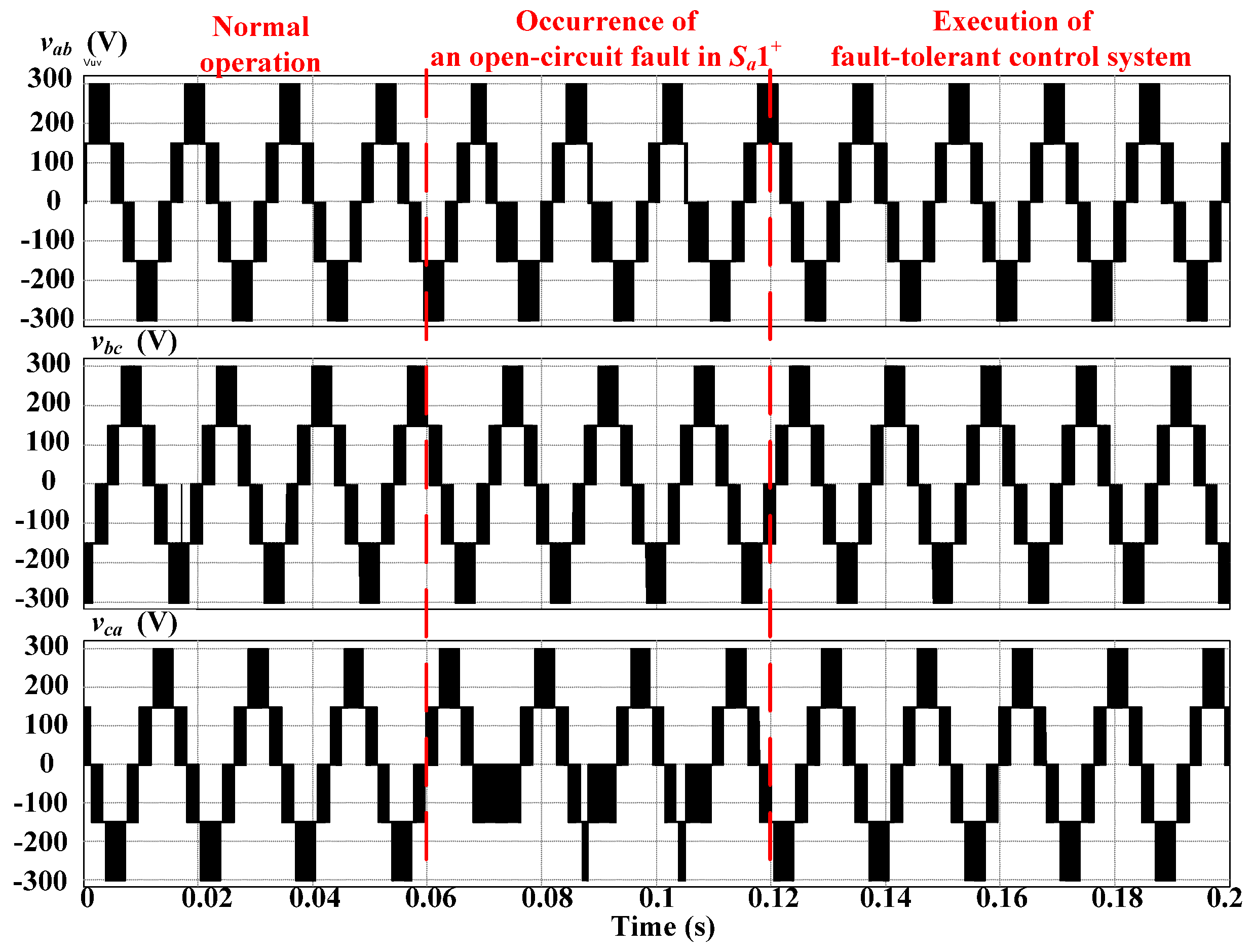

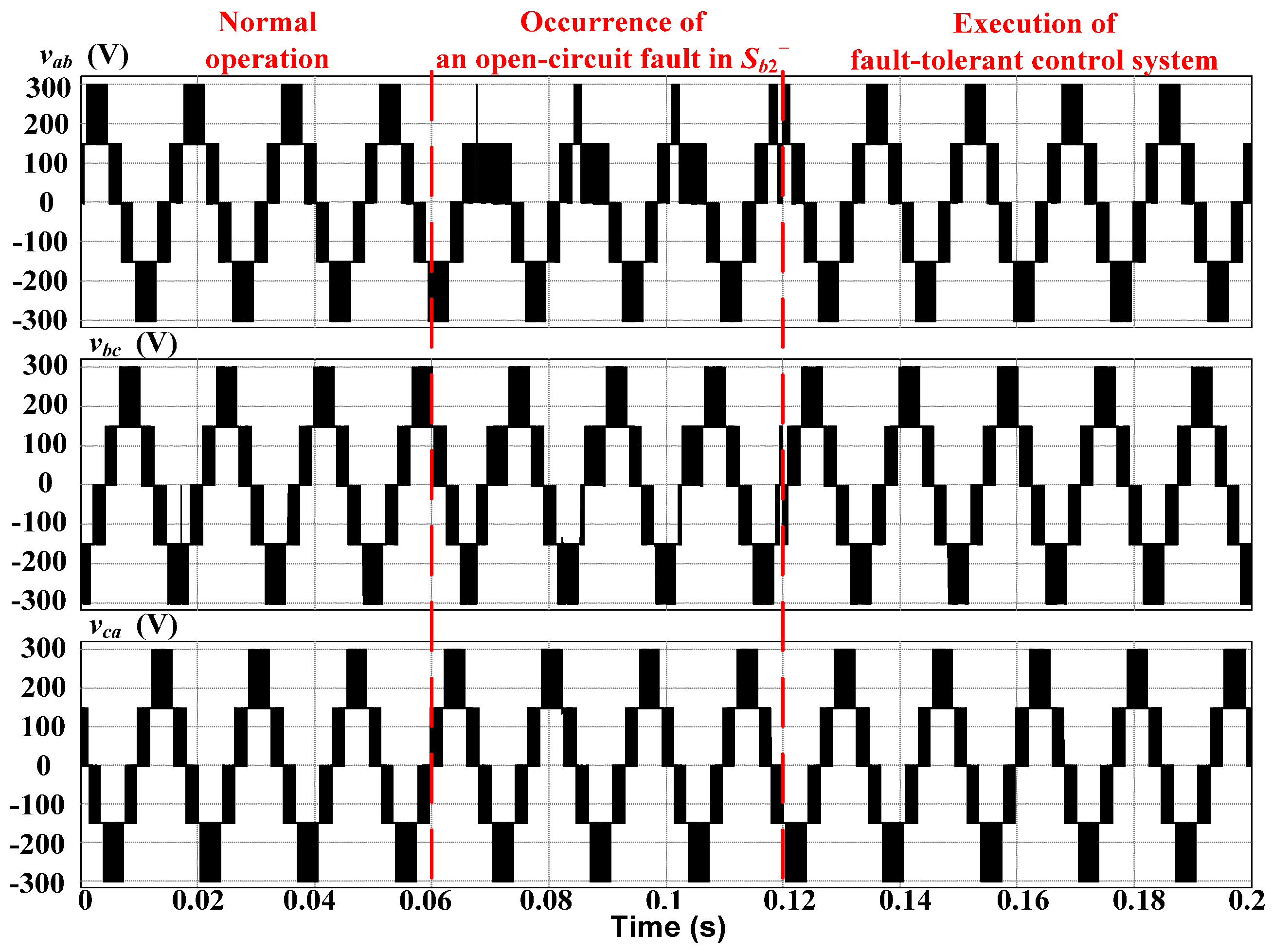

3. Simulation Results

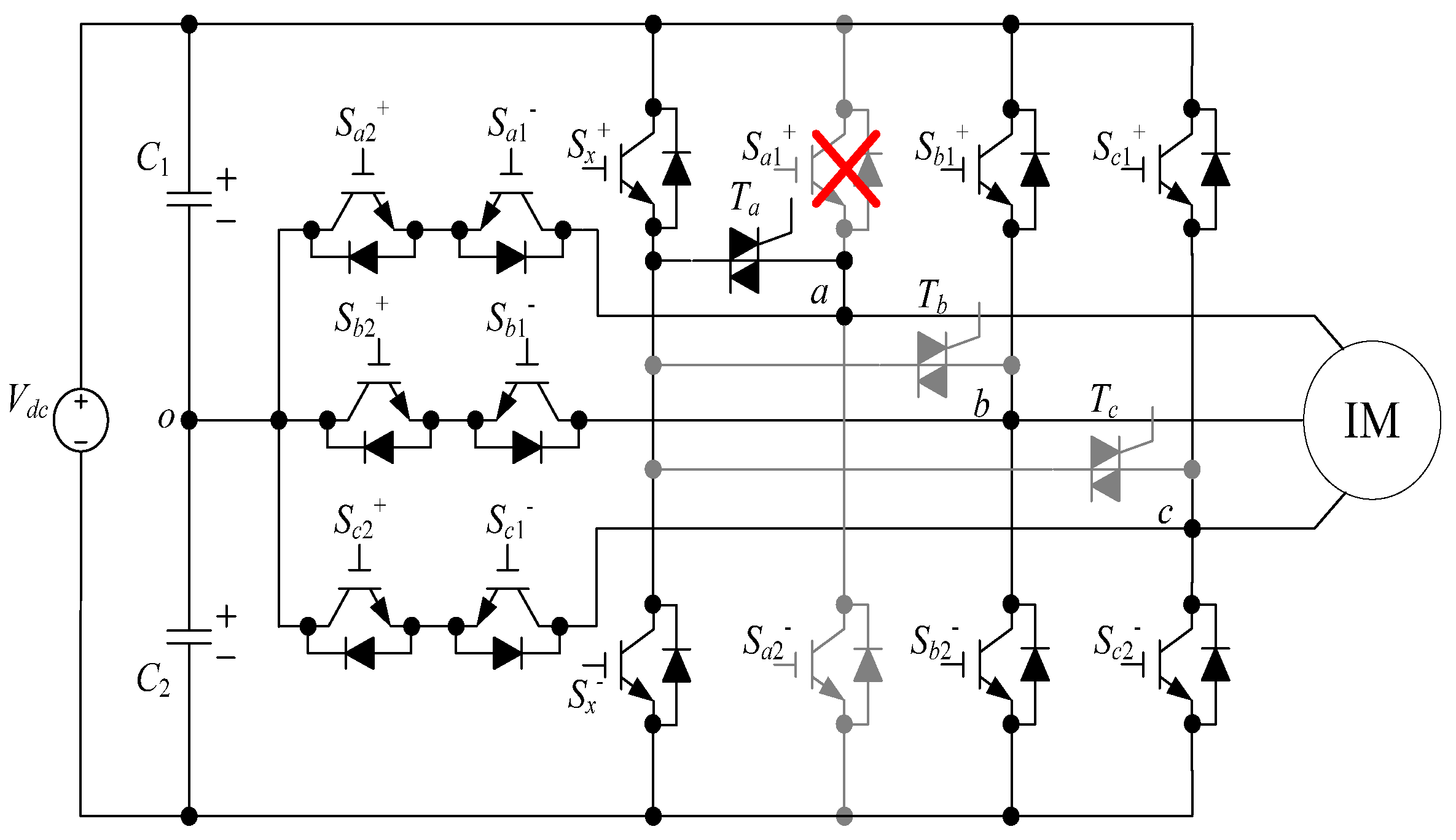

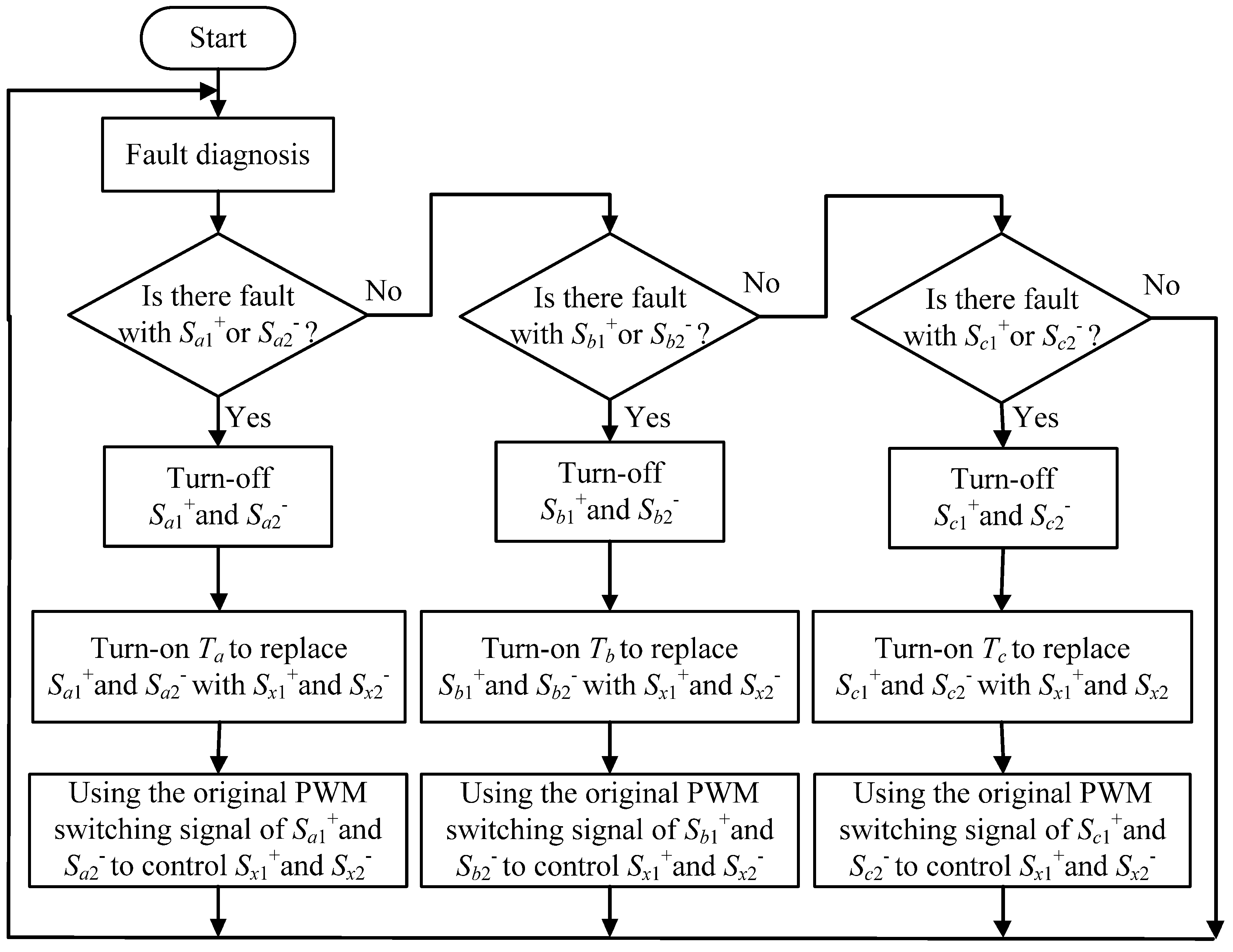

4. Fault-Tolerant Control of Three-Level T-Type Inverter

4.1. Fault-Tolerant Control Analysis

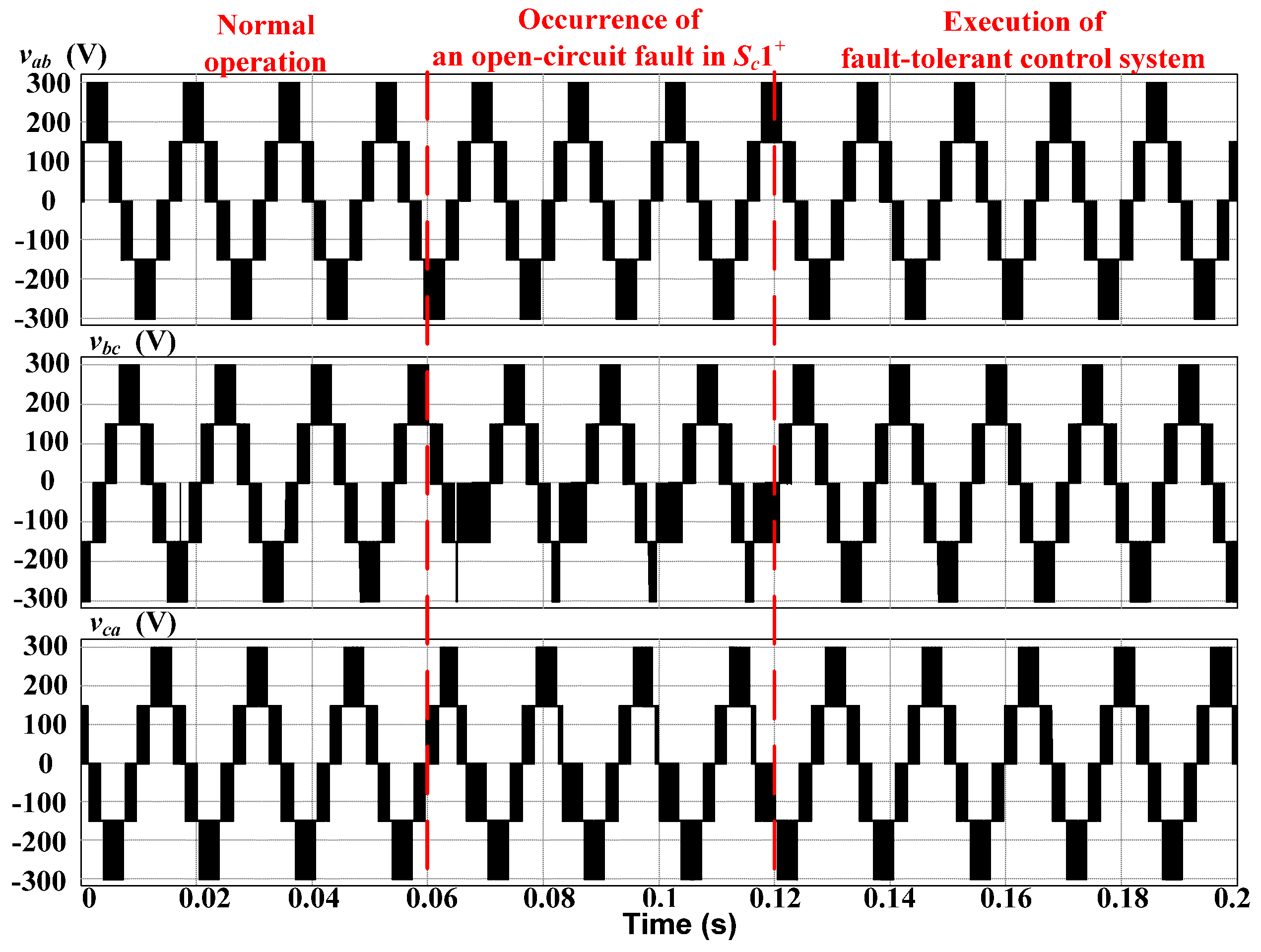

4.2. Fault-Tolerant Control Simulation

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter for low-voltage applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Escalante, M.F.; Vannier, J.C.; Arzande, A. Flying capacitor multilevel inverters and DTC motor drive applications. IEEE Trans. Ind. Electron. 2002, 49, 809–815. [Google Scholar] [CrossRef]

- Rodriguez, J.I.; Leeb, S.B. A multilevel inverter topology for inductively coupled power transfer. IEEE Trans. Power Electron. 2006, 21, 1607–1617. [Google Scholar] [CrossRef]

- Daher, S.; Schmid, J.; Antunes, F.L.M. Multilevel inverter topologies for stand-alone PV systems. IEEE Trans. Ind. Electron. 2008, 55, 2703–2712. [Google Scholar] [CrossRef]

- Naik, R.L.; Udaya, K.R.Y. A novel technique for control of cascaded multilevel inverter for photovoltaic power supplies. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005; pp. 1–9. [Google Scholar]

- Chen, L.; Hu, L.; Chen, L.F.; Deng, Y.; He, X.N. A multilevel converter topology with fault-tolerant ability. IEEE Trans. Power Electron. 2005, 20, 405–415. [Google Scholar] [CrossRef]

- Khomfoi, S.; Tolbert, L.M. Fault diagnostic system for a multilevel inverter using a neural network. IEEE Trans. Power Electron. 2007, 22, 1062–1069. [Google Scholar] [CrossRef]

- Choi, U.; Lee, K.; Blaabjerg, F. Diagnosis and tolerant strategy of an open-switch fault for T-type three-level inverter systems. IEEE Trans. Ind. Appl. 2014, 50, 495–508. [Google Scholar] [CrossRef]

- Topcu, A.; Sozer, Y. Multiple device open circuit fault diagnosis for T-Type multilevel inverters. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 4056–4061. [Google Scholar]

- Wang, K.; Tang, Y.; Zhang, C. Open-circuit fault diagnosis and tolerance strategy applied to four-wire T-type converter systems. IEEE Trans. Power Electron. 2019, 34, 5764–5778. [Google Scholar] [CrossRef]

- Peuget, R.; Courtine, S.; Rognon, J. Fault detection and isolation on a PWM inverter by knowledge-based model. IEEE Trans. Ind. Appl. 1998, 34, 1318–1326. [Google Scholar] [CrossRef]

- Kato, T.; Nagata, M.; Maki, K.; Kojima, H.; Souma, K.; Iwaji, Y. Motor insulation aging diagnosis with pre-installed current sensors for inverter control. In Proceedings of the 2018 XIII International Conference on Electrical Machines (ICEM), Alexandroupoli, Greece, 3–6 September 2018; pp. 1894–1899. [Google Scholar]

- Martin-Diaz, I.; Morinigo-Sotelo, D.; Duque-Perez, O.; Romero-Troncoso, R.J. An experimental comparative evaluation of machine learning techniques for motor fault diagnosis under various operating conditions. IEEE Trans. Ind. Appl. 2018, 54, 2215–2224. [Google Scholar] [CrossRef]

- Torabi, N.; Sundaram, V.M.; Toliyat, H.A. On-line fault diagnosis of multi-phase drives using self-recurrent wavelet neural networks with adaptive learning rates. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 570–577. [Google Scholar]

- Chowdhury, D.; Bhattacharya, M.; Khan, D.; Saha, S.; Dasgupta, A. Wavelet decomposition based fault detection in cascaded H-bridge multilevel inverter using artificial neural network. In Proceedings of the 2nd IEEE International Conference on Recent Trends in Electronics, Information Communication Technology (RTEICT), Bangalore, India, 19–20 May 2017; pp. 1931–1935. [Google Scholar]

- Xu, J.; Song, B.; Zhang, J.; Xu, L. A new approach to fault diagnosis of multilevel inverter. In Proceedings of the Chinese Control and Decision Conference (CCDC), Shenyang, China, 9–11 June 2018; pp. 1054–1058. [Google Scholar]

- Awadallah, M.A.; Morcos, M.M. Diagnosis of switch open-circuit fault in PM brushless DC motor drives. In Proceedings of the Large Engineering Systems Conference on Power Engineering, Montreal, QC, Canada, 7–9 May 2003; pp. 69–73. [Google Scholar]

- Song, Y.; Wang, B. Survey on reliability of power electronic systems. IEEE Trans. Power Electron. 2013, 28, 591–604. [Google Scholar] [CrossRef]

- Zhang, T.; Wang, F.; Fu, W. Fault detection and isolation for redundant inertial measurement unit under quantization. Appl. Sci. 2018, 8, 865. [Google Scholar] [CrossRef]

- Aleenejad, M.; Mahmoudi, H.; Moamaei, P.; Ahmadi, R. A new fault-tolerant strategy based on a modified selective harmonic technique for three-phase multilevel converters with a single faulty cell. IEEE Trans. Power Electron. 2016, 31, 3141–3150. [Google Scholar] [CrossRef]

- Xu, S.; Zhang, J.; Hang, J. Investigation of a fault-tolerant three-level T-type inverter system. IEEE Trans. Ind. Appl. 2017, 53, 4613–4623. [Google Scholar] [CrossRef]

- Wang, X.; Shen, Y. Fault-Tolerant Control strategy of a wind energy conversion system considering multiple fault reconstruction. Appl. Sci. 2018, 8, 794. [Google Scholar] [CrossRef]

- Hosseinzadeh, M.; Salmasi, F.R. Fault-tolerant supervisory controller for a hybrid AC/DC micro-grid. IEEE Trans. Smart Grid 2018, 9, 2809–2823. [Google Scholar] [CrossRef]

- Chao, K.H.; Ho, S.H.; Wang, M.H. Modeling and fault diagnosis of a photovoltaic system. Electr. Power Syst. Res. 2008, 78, 97–105. [Google Scholar] [CrossRef]

- Li, Y.; Yuan, C.; Huang, Y. A novel watermarking technology based on Lorenz chaotic attractor. In Proceedings of the 2009 International Conference on Computational Intelligence and Natural Computing, Wuhan, China, 6–7 June 2009; Volume 2, pp. 330–332. [Google Scholar]

- Li, M.; Li, G. Based on theory of extenics research assessment and classification of soil erosion. In Proceedings of the World Automation Congress, Puerto Vallarta, Mexico, 24–28 June 2012; pp. 1–6. [Google Scholar]

| Fault State | Category |

|---|---|

| Switch Sa1+ fails | F1 |

| Switch Sa1− or Sa2+ fails | F2 |

| Switch Sa2− fails | F3 |

| Switch Sb1+ fails | F4 |

| Switch Sb1− or Sb2+ fails | F5 |

| Switch Sb2− fails | F6 |

| Switch Sc1+ fails | F7 |

| Switch Sc1− or Sc2+ fails | F8 |

| Switch Sc2− fails | F9 |

| Phase | Fault Category | C1X axis | C1Y axis | C2X axis | C2Y axis |

|---|---|---|---|---|---|

| a-phase chaos eye feature value | F1 | −0.049 | −39.988 | 0.046 | −42.584 |

| F2 | −0.046 | 32.789 | 0.049 | 30.448 | |

| F3 | −0.068 | −1.429 | 0.075 | 17.557 | |

| F4 | −0.074 | −36.222 | 0.067 | −11.218 | |

| F5 | −0.079 | 15.843 | 0.069 | 13.017 | |

| F6 | −0.07 | −24.913 | 0.08 | −31.164 | |

| F7 | −0.06 | −8.153 | 0.057 | −4.901 | |

| F8 | −0.08 | 15.631 | 0.07 | 13.255 | |

| F9 | −0.052 | −6.24 | 0.051 | −6.531 | |

| b-phase chaos eye feature value | F1 | −0.08 | −0.08 | −0.08 | −0.08 |

| F2 | −0.07 | −0.07 | −0.07 | −0.07 | |

| F3 | −0.049 | −0.049 | −0.049 | −0.049 | |

| F4 | −0.045 | −0.045 | −0.045 | −0.045 | |

| F5 | −0.067 | −0.067 | −0.067 | −0.067 | |

| F6 | −0.075 | −0.075 | −0.075 | −0.075 | |

| F7 | −0.052 | −0.052 | −0.052 | −0.052 | |

| F8 | −0.058 | −0.058 | −0.058 | −0.058 | |

| F9 | −0.053 | −0.053 | −0.053 | −0.053 | |

| c-phase chaos eye feature value | F1 | −0.068 | −0.068 | −0.068 | −0.068 |

| F2 | −0.075 | −0.075 | −0.075 | −0.075 | |

| F3 | −0.08 | −0.08 | −0.08 | −0.08 | |

| F4 | −0.069 | −0.069 | −0.069 | −0.069 | |

| F5 | −0.049 | −0.049 | −0.049 | −0.049 | |

| F6 | −0.046 | −0.046 | −0.046 | −0.046 | |

| F7 | −0.052 | −0.052 | −0.052 | −0.052 | |

| F8 | −0.052 | −0.052 | −0.052 | −0.052 | |

| F9 | −0.058 | −0.058 | −0.058 | −0.058 |

| Fault Category | Output Weight Value | Detection Result | ||

|---|---|---|---|---|

| F1 | F2 | F3 | ||

| F1 | 0.782085 | −0.564565 | −0.591532 | F1 |

| F2 | −0.544865 | 0.861617 | −0.629411 | F2 |

| F3 | −0.037735 | −0.378546 | 0.553326 | F3 |

| Fault Category | Output Weight Value | Detection Result | ||

|---|---|---|---|---|

| F4 | F5 | F6 | ||

| F4 | 0.780133 | −0.549192 | −0.594745 | F4 |

| F5 | −0.572378 | 0.872429 | −0.648071 | F5 |

| F6 | −0.225007 | −0.346686 | 0.701689 | F6 |

| Fault Category | Output Weight Value | Detection Result | ||

|---|---|---|---|---|

| F7 | F8 | F9 | ||

| F7 | 0.813761 | −0.569932 | −0.600617 | F7 |

| F8 | −0.549737 | 0.884781 | −0.62921 | F8 |

| F9 | −0.253144 | −0.351958 | 0.521521 | F9 |

| Fault Category | Error Percentage | Output Weight Value | Detection Result | ||

|---|---|---|---|---|---|

| F1 | F2 | F3 | |||

| F1 | 5% | 0.227338 | −0.577322 | −0.589176 | F1 |

| F1 | −5% | 0.563368 | −0.512827 | −0.593788 | F1 |

| F2 | 5% | −0.554998 | 0.442223 | −0.617735 | F2 |

| F2 | −5% | −0.514244 | 0.598609 | −0.653885 | F2 |

| F3 | 5% | 0.0491609 | −0.39636 | 0.37029 | F3 |

| F3 | −5% | −0.124961 | −0.361071 | 0.709824 | F3 |

| Fault Category | Error Percentage | Output Weight Value | Detection Result | ||

|---|---|---|---|---|---|

| F4 | F5 | F6 | |||

| F4 | 5% | 0.225285 | −0.581416 | −0.59255 | F4 |

| F4 | −5% | 0.565218 | −0.498222 | −0.59684 | F4 |

| F5 | 5% | −0.555554 | 0.510485 | −0.629454 | F5 |

| F5 | −5% | −0.542088 | 0.536848 | −0.665188 | F5 |

| F6 | 5% | −0.147346 | −0.362908 | 0.727323 | F6 |

| F6 | −5% | −0.30369 | −0.331795 | 0.639154 | F6 |

| Fault Category | Error Percentage | Output Weight Value | Detection Result | ||

|---|---|---|---|---|---|

| F7 | F8 | F9 | |||

| F7 | 5% | 0.281603 | −0.581739 | −0.598714 | F7 |

| F7 | −5% | 0.51428 | −0.517926 | −0.602419 | F7 |

| F8 | 5% | −0.551061 | 0.455688 | −0.617525 | F8 |

| F8 | −5% | −0.522304 | 0.586427 | −0.654039 | F8 |

| F9 | 5% | −0.17552 | −0.367097 | 0.50828 | F9 |

| F9 | −5% | −0.330461 | −0.336816 | 0.514661 | F9 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chao, K.-H.; Chang, L.-Y.; Xu, F.-Q. Smart Fault-Tolerant Control System Based on Chaos Theory and Extension Theory for Locating Faults in a Three-Level T-Type Inverter. Appl. Sci. 2019, 9, 3071. https://doi.org/10.3390/app9153071

Chao K-H, Chang L-Y, Xu F-Q. Smart Fault-Tolerant Control System Based on Chaos Theory and Extension Theory for Locating Faults in a Three-Level T-Type Inverter. Applied Sciences. 2019; 9(15):3071. https://doi.org/10.3390/app9153071

Chicago/Turabian StyleChao, Kuei-Hsiang, Long-Yi Chang, and Fu-Qiang Xu. 2019. "Smart Fault-Tolerant Control System Based on Chaos Theory and Extension Theory for Locating Faults in a Three-Level T-Type Inverter" Applied Sciences 9, no. 15: 3071. https://doi.org/10.3390/app9153071

APA StyleChao, K.-H., Chang, L.-Y., & Xu, F.-Q. (2019). Smart Fault-Tolerant Control System Based on Chaos Theory and Extension Theory for Locating Faults in a Three-Level T-Type Inverter. Applied Sciences, 9(15), 3071. https://doi.org/10.3390/app9153071