RHLP-18T: A Radiation-Hardened 18T SRAM with Enhanced Read Stability and Low Power Consumption

Abstract

1. Introduction

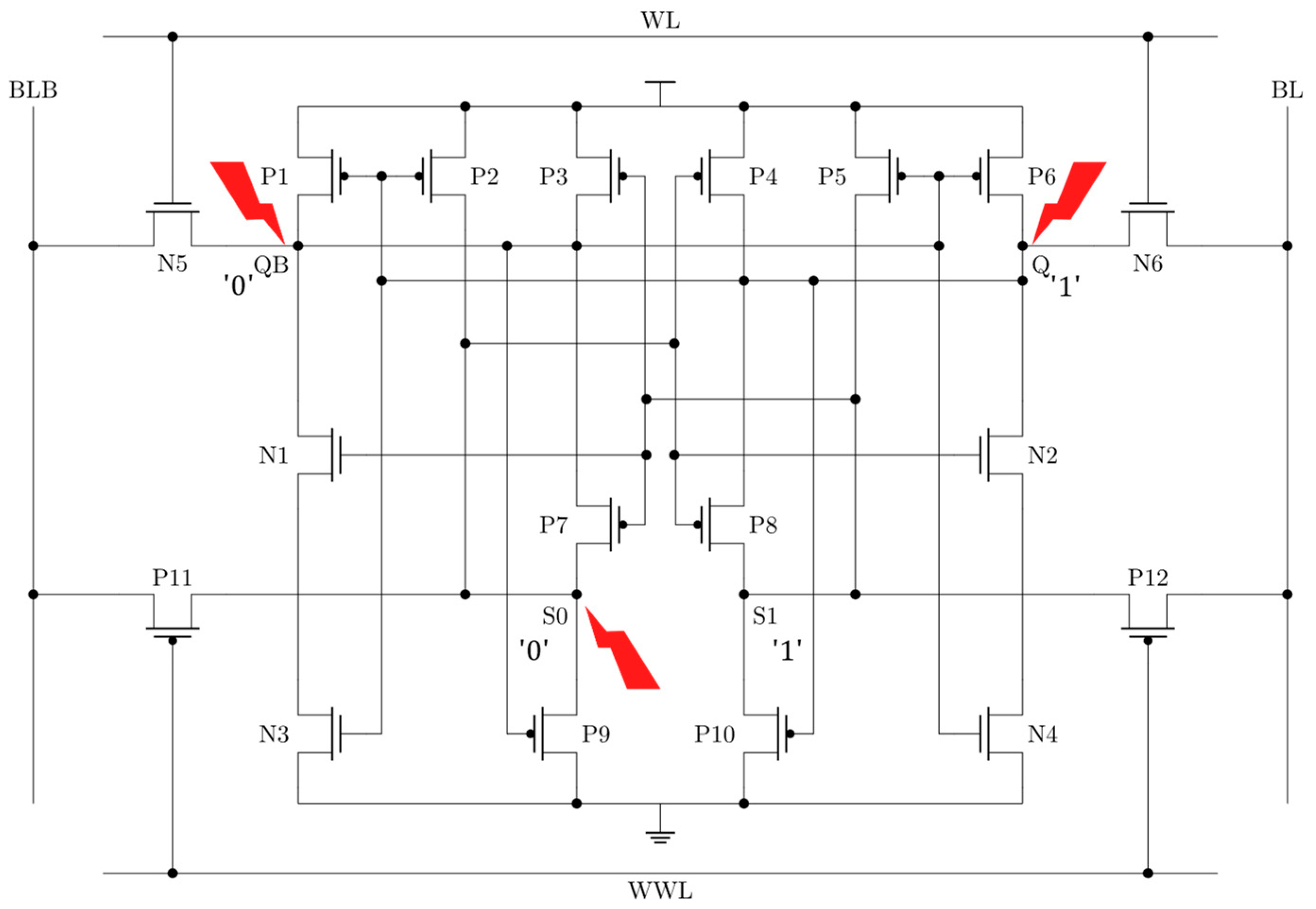

2. Proposed RHLP-18T Cell and Its Operations

2.1. Memory Operation of the Proposed RHLP-18T Cell

2.1.1. Hold Mode

2.1.2. Read Mode

2.1.3. Write Mode

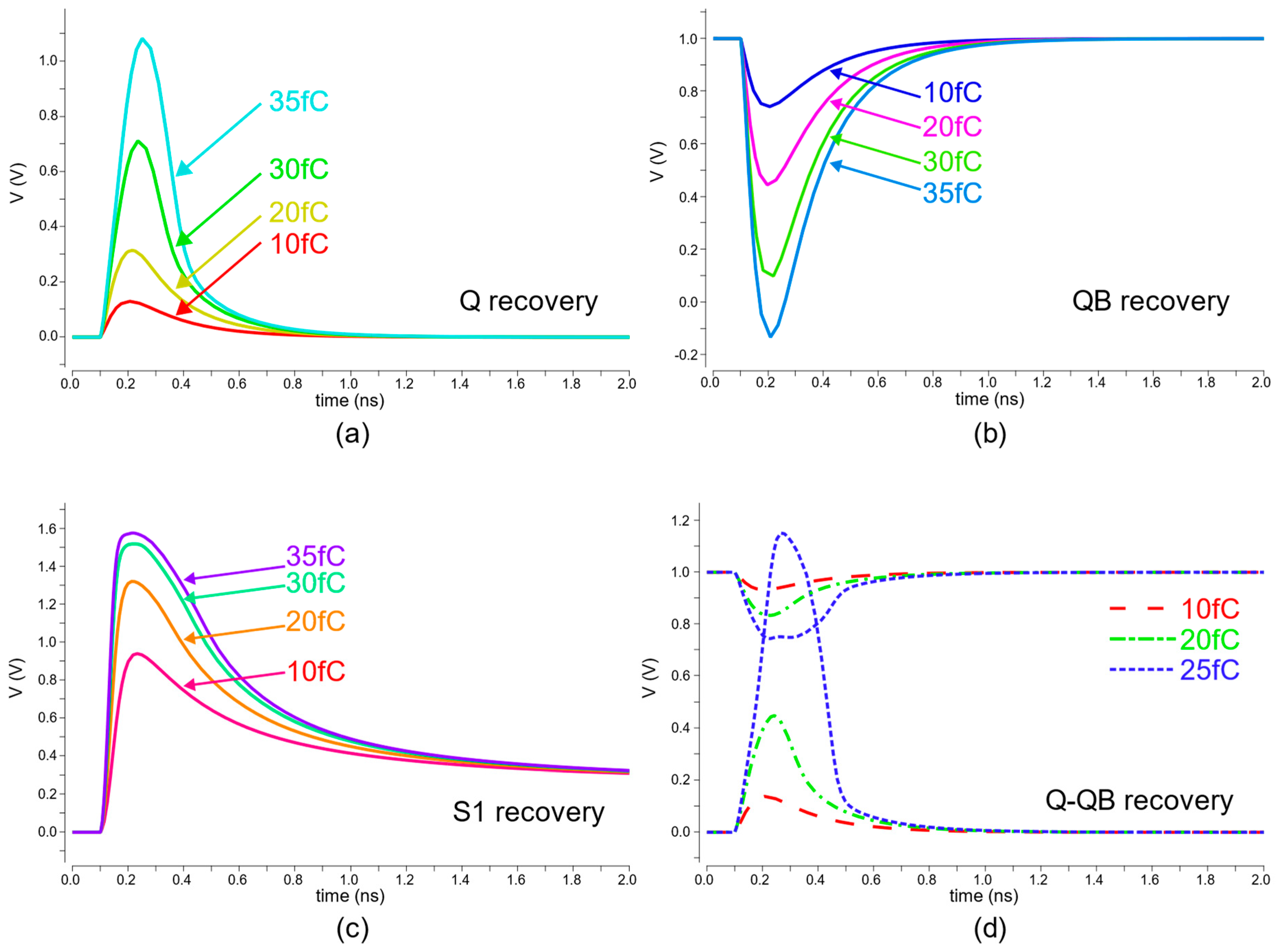

2.2. Radiation-Hardened SEU Recovery Analysis

- (1)

- When a high-energy particle strike momentarily flips node Q from ‘1’ down to ‘0’, this turns on transistors P1 and P2, and it turns off N3, causing node QB’s voltage to rise. Crucially, transistor P3 is designed with significantly more pull-up strength than P1 (approximately three times greater). This difference ensures that node Q is quickly pulled back up to logic ‘1’ before the related nodes (S0 and S1) can fully change state. This rapid restoration prevents the upset from corrupting stored data.

- (2)

- When a high-energy particle strike flips node QB from ‘0’ up to ‘1’, this turns off P5, P6, and P9, and turns on N4. Node S0 briefly enters a high-impedance state but effectively stays at logic ‘0’. As a result, N2 remains off, shielding primary storage node Q from the disturbance. The transient upset at QB does not manage to flip Q. Afterward, QB is pulled back down to logic ‘0’ through the path provided by N1 and N3 (which are on because Q = 1).

- (3)

- When a high-energy particle strike flips node S0 from ‘0’ to ‘1’, transistors P4 and P8 turn off, while N2 turns on. As a result, node S1 floats, and node Q also temporarily floats because N4 is off. Despite these transient disruptions, the main latch (Q/QB) does not flip its state. Node S0 is then pulled back to logic ‘0’ by transistor P9, which connects it to QB (normally at logic ‘0’).

- (4)

- When a single event strike simultaneously flips node Q from ‘1’ to ‘0’ and node QB from ‘0’ to ‘1’, the design ensures that the restoring pull-up strength of P3 (driving Q high) overcomes the combined pull-down strength attempting to keep Q low. This pull-down involves N2 and N4, depending on the transient states of S0 and S1. Because the pull-up is stronger, node Q recovers to logic ‘1’ before the secondary nodes S0 and S1 fully invert, successfully restoring the original state.

- (5)

- When a high-energy particle simultaneously strikes the sensitive nodes Q-S0 or QB-S0, an upset occurs from 1–0 to 0–1 in Q-S0, and from 0–0 to 1–1 in QB-S0. This turns on P1, P2, P4, P8, N4 and turns off P3, P7, P5, P6, N3. In this case, all storage nodes change and are unrecoverable. According to [7], to prevent the charge-sharing effect, the distance between transistors (PMOS to PMOS and PMOS to NMOS) connected to the sensitive nodes must be at least 0.6 um. Accordingly, the layout was designed with a distance of 0.85 um between P1 and P2, and a distance of 3.71 um between P7 and N2, as shown in Figure 2.

3. Simulation Results and Analysis

3.1. Stability Comparison

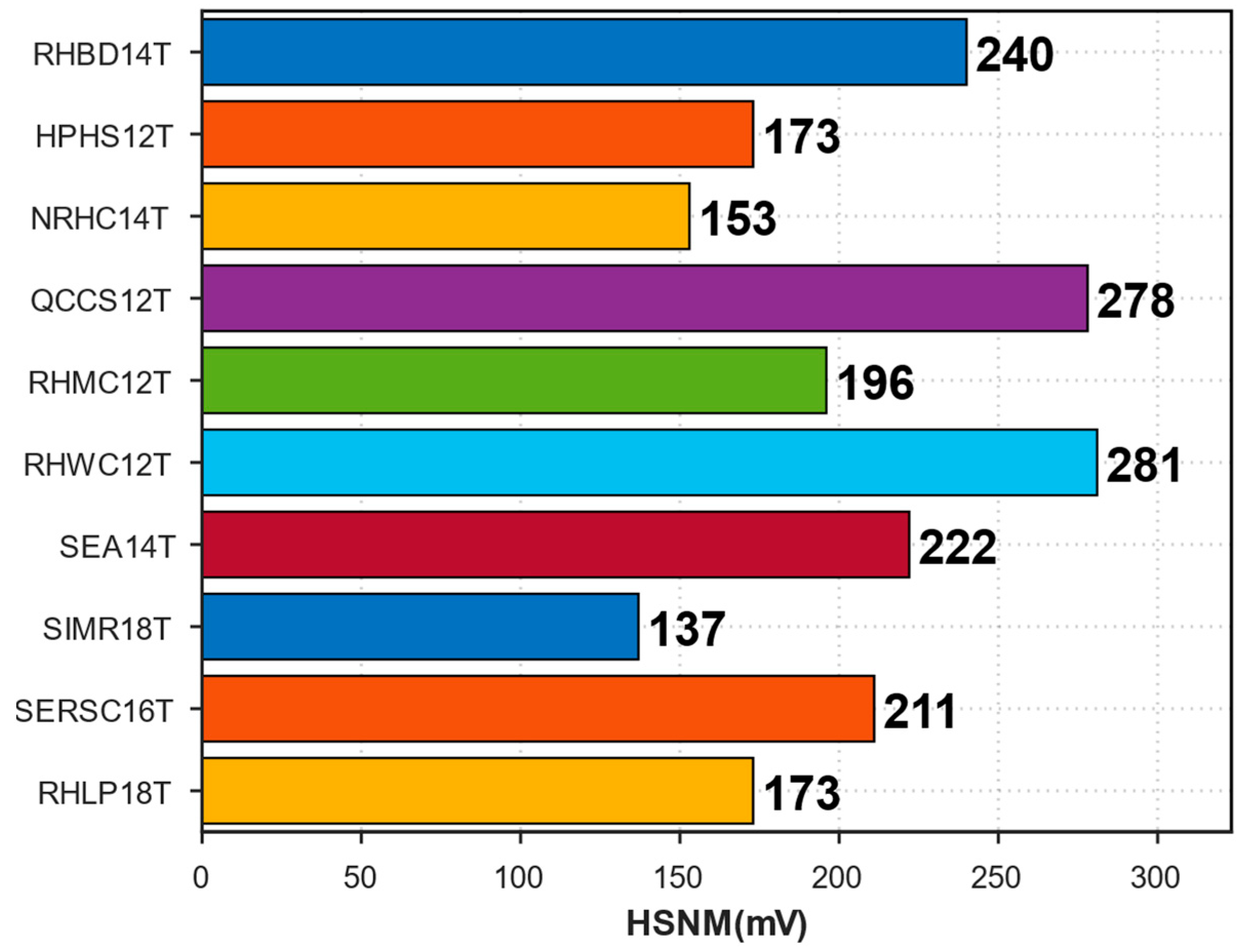

3.1.1. HSNM Comparison

3.1.2. RSNM Comparison

- (1)

- Write Path Decoupling via WWL: The use of the separate Write Word Line (WWL) helps maintain stability during reads. By setting WWL to VDD, the PMOS write access transistors (P11, P12) are turned off. This effectively decouples the write circuitry from the storage nodes and bit lines during the read operation, preventing potential interference or loading effects from the write transistors.

- (2)

- Robust Core Latch and Cell Ratio: The core latch structure’s robustness is enhanced by its design, including the relative sizing of driver and access transistors, often characterized by the Cell Ratio (CR). In this design, the primary pull-down NMOS transistors (N1, N2, N3, N4) have a width twice the minimum size. Assuming the read access transistors (N5, N6) are minimum size, this results in an effective Cell Ratio (CR) of approximately 2. This relatively high CR enhances the latch’s ability to hold its state during a read operation, contributing significantly to the high RSNM.

- (3)

- Cell Characteristics: A large internal voltage swing during operation likely also contributes to the enhanced read stability margin.

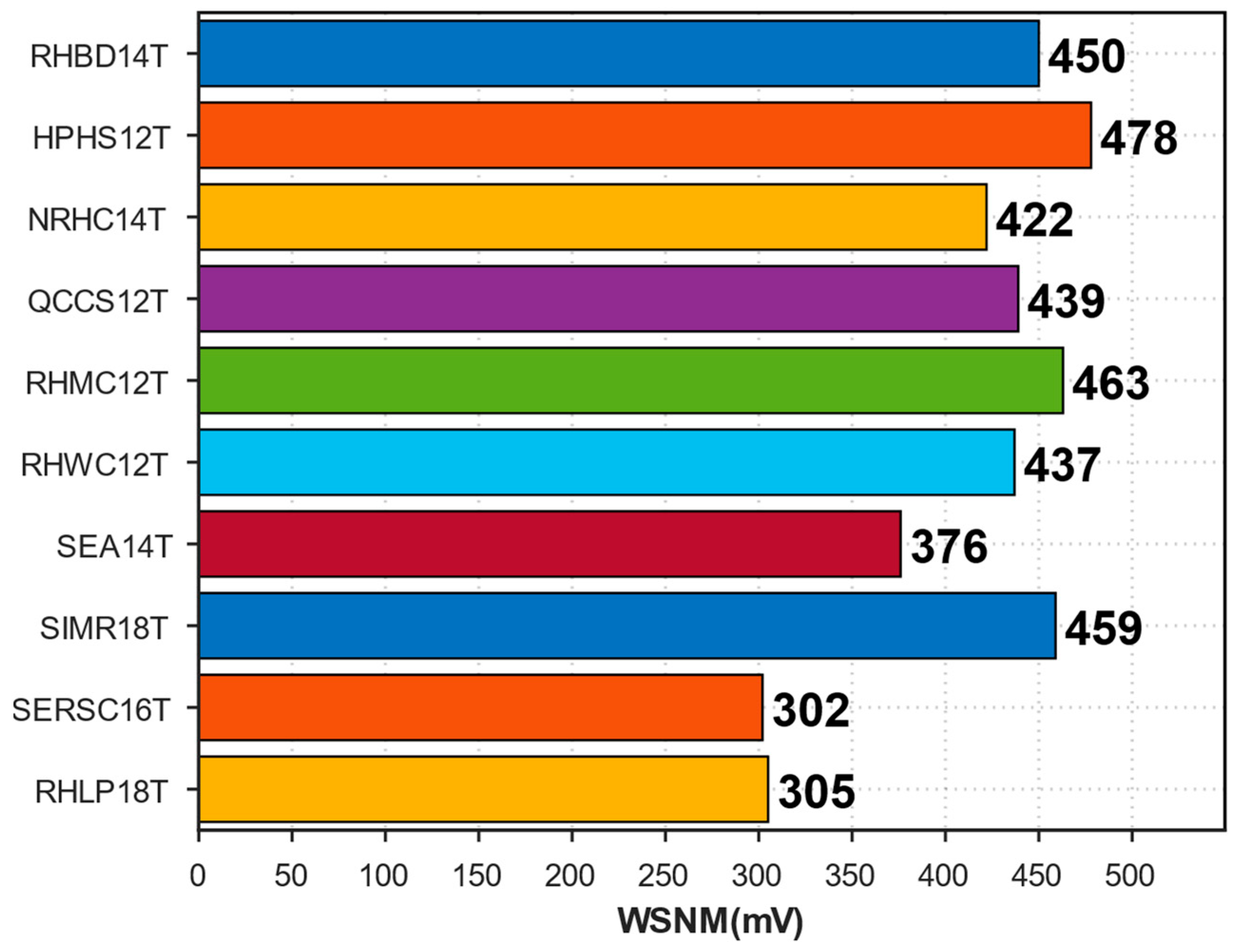

3.1.3. WSNM Comparison

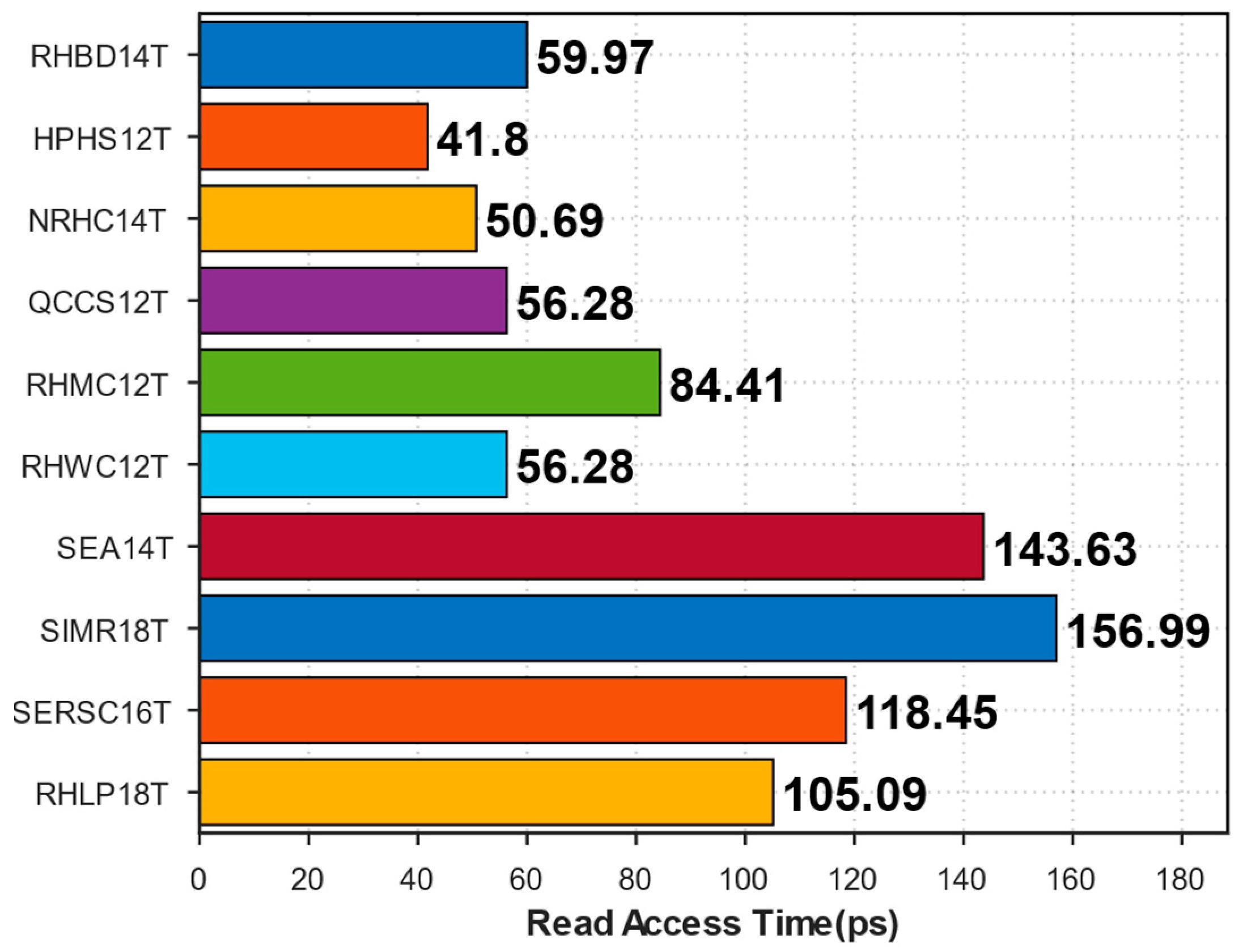

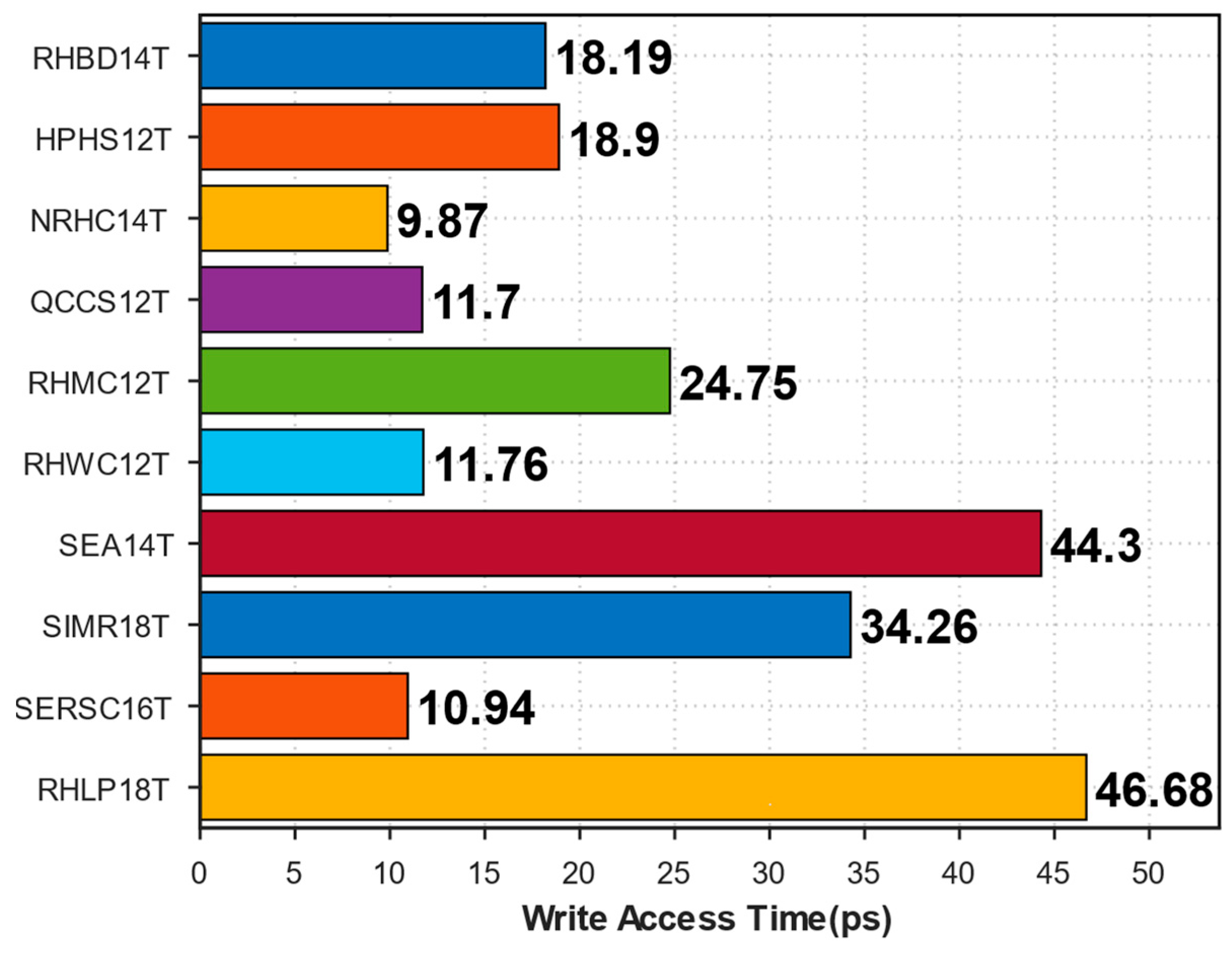

3.2. Access Time Comparison

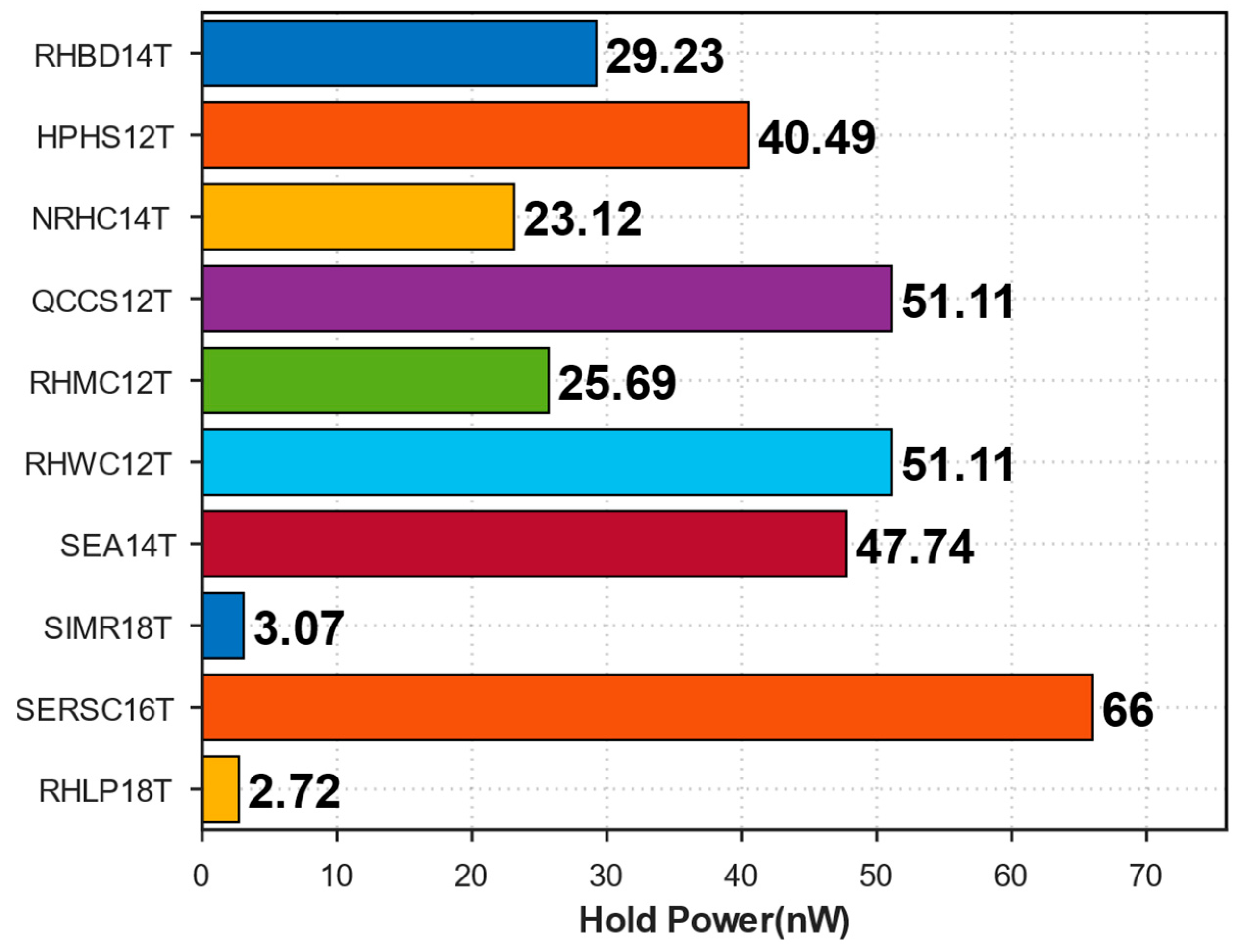

3.3. Hold Power Comparison

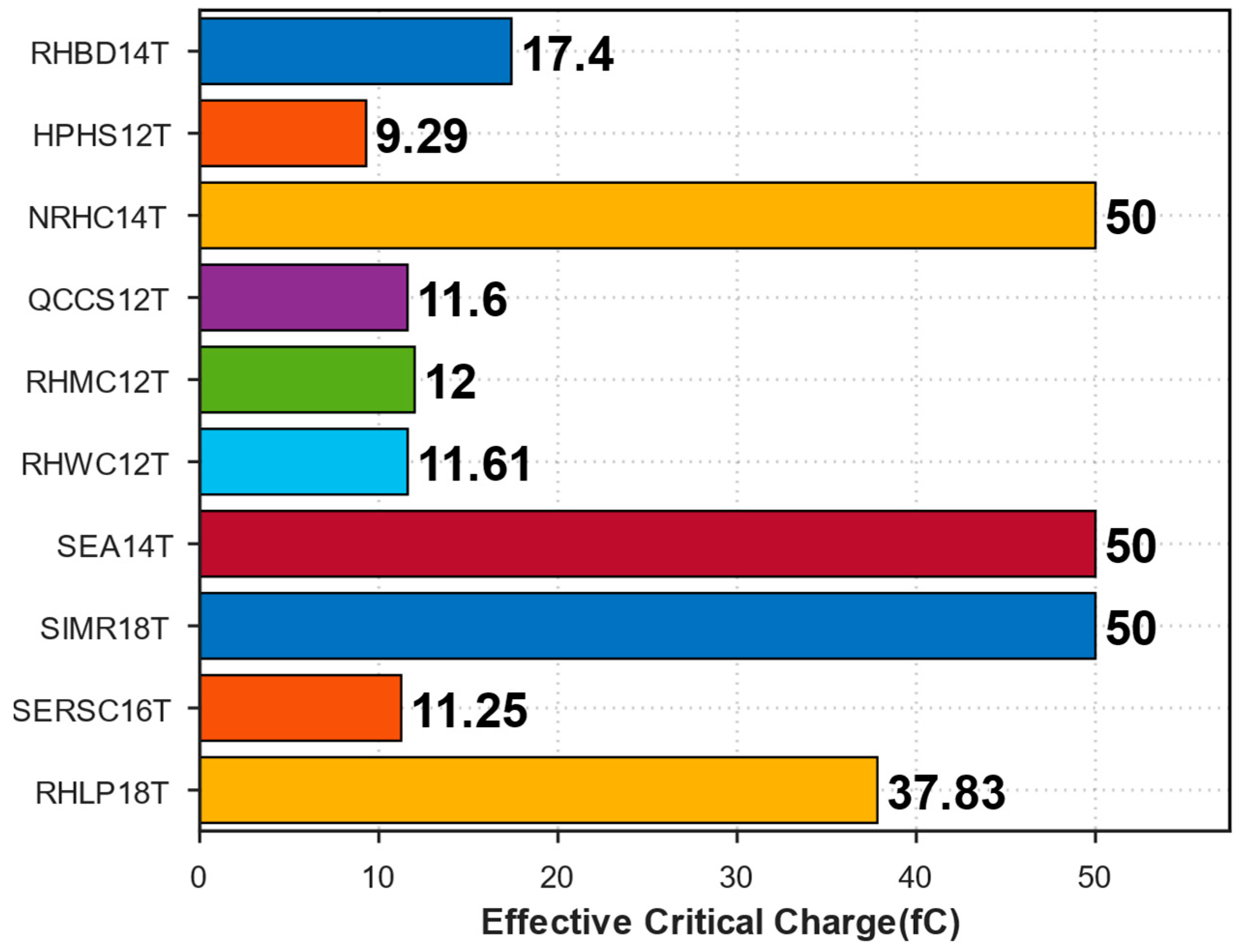

3.4. SEU and SEDNU Robustness Comparison

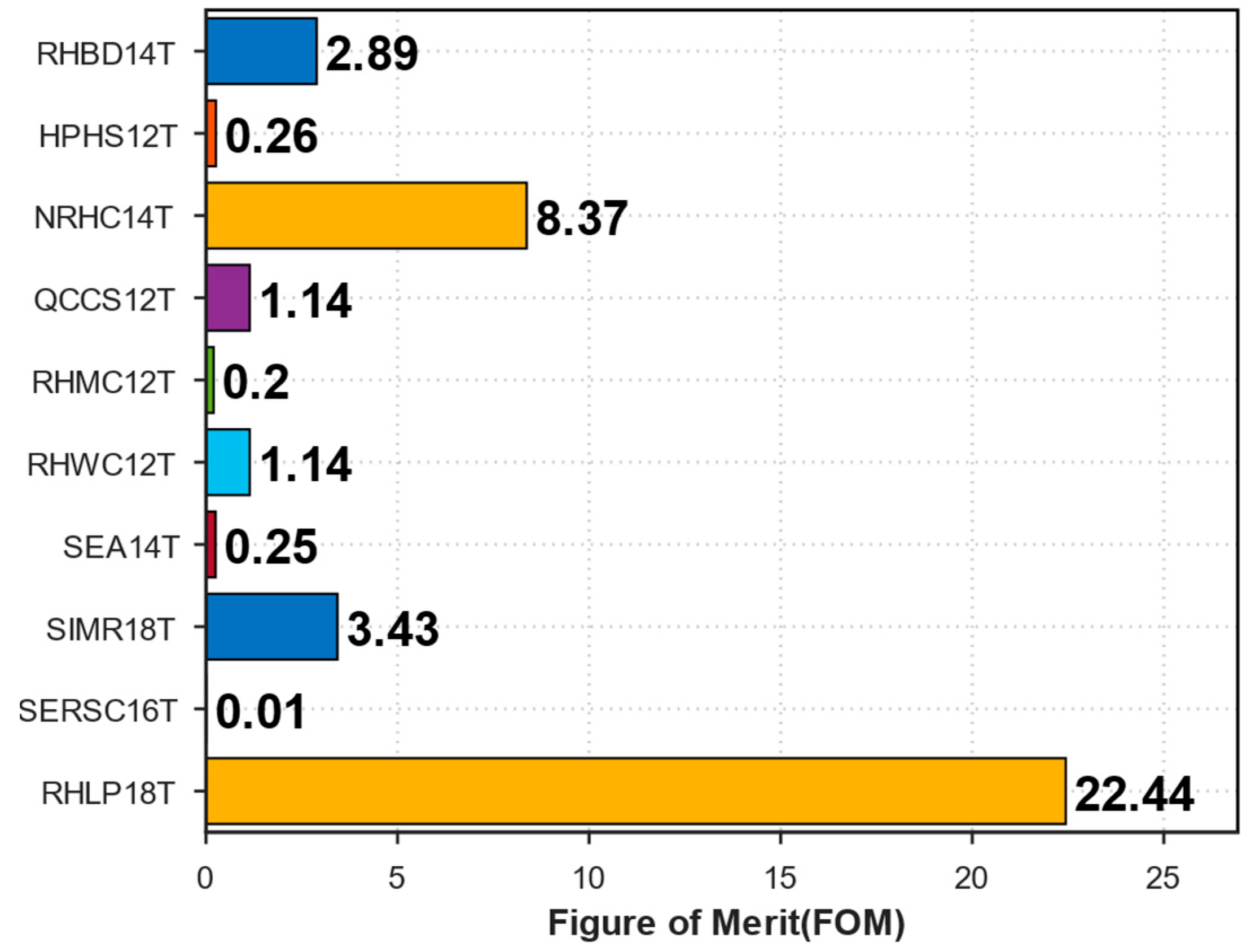

3.5. Figure of Merit (FOM)

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Holmes-Siedle, A.; Adams, L. Handbook of Radiation Effects; Oxford University Press: Oxford, UK, 2002; ISBN 978-0-19-850733-8. [Google Scholar]

- Pasupathy, K.R.; Bindu, B. Analysis of Bipolar Amplification Due to Heavy-Ion Irradiation in 45 Nm FDSOI MOSFET with Thin BOX and Ground Plane. Microelectron. Reliab. 2019, 98, 56–62. [Google Scholar] [CrossRef]

- Pal, S.; Ki, W.-H.; Tsui, C.-Y. Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM with Multi-Node Upset Recoverability for Aerospace Applications. IEEE Trans. Circuits Syst. I 2022, 69, 1560–1570. [Google Scholar] [CrossRef]

- Dodd, P.E.; Massengill, L.W. Basic Mechanisms and Modeling of Single-Event Upset in Digital Microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Dohar, S.S.; Siddharth, R.K.; Vasantha, M.H.; Nithin Kumar, Y.B. A 1.2 V, Highly Reliable RHBD 10T SRAM Cell for Aerospace Application. IEEE Trans. Electron Devices 2021, 68, 2265–2270. [Google Scholar] [CrossRef]

- Huang, Q. Investigation of Radiation-Hardened Design of Electronic Systems with Applications to Post-Accident Monitoring for Nuclear Power Plants. Ph.D. Thesis, The University of Western Ontario, London, ON, Canada, 2019. [Google Scholar]

- Cai, S.; Liang, X.; Wen, Y.; Yu, F.; Yin, L. A Radiation-Hardened 20T SRAM Cell with High Reliability and Low Power Consumption. In Proceedings of the 2024 IEEE International Test Conference in Asia (ITC-Asia), Changsha, China, 18 August 2024. [Google Scholar]

- Aguiar, Y.Q.D.; Wrobel, F.; Autran, J.-L.; García Alía, R. Single-Event Effects, from Space to Accelerator Environments: Analysis, Prediction and Hardening by Design; Springer International Publishing: Cham, Switzerland, 2025; ISBN 978-3-031-71722-2. [Google Scholar]

- Kiamehr, S.; Osiecki, T.; Tahoori, M.; Nassif, S. Radiation-Induced Soft Error Analysis of SRAMs in SOI FinFET Technology: A Device to Circuit Approach. In Proceedings of the 51st Annual Design Automation Conference, San Francisco, CA, USA, 1–5 June 2014. [Google Scholar]

- Prasad, G.; Mandi, B.C.; Ali, M. Energy-Efficient Radiation Hardened SRAM Cell for Low Voltage Terrestrial Applications. Microelectron. J. 2022, 120, 105340. [Google Scholar] [CrossRef]

- Mukku, P.K.; Lorenzo, R. An Efficient Radiation Hardening SRAM Cell to Mitigate Single and Double Node Upset Soft Errors. Microelectron. Reliab. 2024, 152, 115303. [Google Scholar] [CrossRef]

- Hao, L.; Liu, L.; Shi, Q.; Qiang, B.; Li, Z.; Liu, N.; Dai, C.; Zhao, Q.; Peng, C.; Lu, W.; et al. Design of Radiation-Hardened Memory Cell by Polar Design for Space Applications. Microelectron. J. 2023, 132, 105691. [Google Scholar] [CrossRef]

- Kumar, S.; Mukherjee, A. Design of Soft-Error Resilient SRAM Cell with High Read and Write Stability for Robust Operations. AEU Int. J. Electron. Commun. 2023, 168, 154719. [Google Scholar] [CrossRef]

- Pal, S.; Mohapatra, S.; Ki, W.-H.; Islam, A. Design of Soft-Error-Aware SRAM with Multi-Node Upset Recovery for Aerospace Applications. IEEE Trans. Circuits Syst. I 2021, 68, 2470–2480. [Google Scholar] [CrossRef]

- Liu, Z.; Zhang, H.; Xie, Y.; Bi, D.; Hu, Z.; Zou, S.; Zhang, Z. High-Performance and Highly-Stable Soft Error Resistant 12T SRAM Cell for Space Applications. Microelectron. Reliab. 2023, 141, 114885. [Google Scholar] [CrossRef]

- Bai, N.; Zhou, Y.; Xu, Y.; Wang, Y.; Chen, Z. Highly Stable Soft-Error Immune SRAM with Multi-Node Upset Recovery for Aerospace Applications. Integration 2023, 92, 58–65. [Google Scholar] [CrossRef]

- Zhao, Q.; Dong, H.; Wang, X.; Hao, L.; Peng, C.; Lin, Z.; Wu, X. Novel Radiation-Hardened SRAM for Immune Soft-Error in Space-Radiation Environments. Microelectron. Reliab. 2023, 140, 114862. [Google Scholar] [CrossRef]

- Yan, A.; Xiang, J.; Cao, A.; He, Z.; Cui, J.; Ni, T.; Huang, Z.; Wen, X.; Girard, P. Quadruple and Sextuple Cross-Coupled SRAM Cell Designs with Optimized Overhead for Reliable Applications. IEEE Trans. Device Mater. Relib. 2022, 22, 282–295. [Google Scholar] [CrossRef]

- Sharma, R.; Mondal, D.; Shah, A.P. Radiation Hardened 12T SRAM Cell with Improved Writing Capability for Space Applications. Mem. Mater. Devices Circuits Syst. 2023, 5, 100071. [Google Scholar] [CrossRef]

- Li, H.; Xiao, L.; Qi, C.; Li, J. Design of High-Reliability Memory Cell to Mitigate Single Event Multiple Node Upsets. IEEE Trans. Circuits Syst. I 2021, 68, 4170–4181. [Google Scholar] [CrossRef]

- Kumar, S.; Mukherjee, A. High Performance Radiation-Hardened SRAM Cell Design for Robust Applications. Microelectron. J. 2023, 140, 105934. [Google Scholar] [CrossRef]

| Structure Name | HSNM /mV | RSNM /mV | WSNM /mV | Qc /fC | RAT /ps | WAT /ps | Hold Power /nW | FOM |

|---|---|---|---|---|---|---|---|---|

| RHBD-14T | 240 | 49 | 450 | 17.4 | 59.97 | 18.19 | 29.23 | 2.89 |

| HPHS-12T | 173 | 11 | 478 | 9.29 | 41.8 | 18.9 | 40.49 | 0.26 |

| NRHC-14T | 153 | 30 | 422 | >50 | 50.69 | 9.87 | 23.12 | 8.37 |

| QCCS-12T | 278 | 27 | 439 | 11.6 | 56.28 | 11.7 | 51.11 | 1.14 |

| RHMC-12T | 196 | 10 | 463 | 12 | 84.41 | 24.75 | 25.69 | 0.2 |

| RHWC-12T | 281 | 27 | 437 | 11.61 | 56.28 | 11.76 | 51.11 | 1.14 |

| SEA-14T | 222 | 18 | 376 | >50 | 143.63 | 44.3 | 47.74 | 0.25 |

| SIMR-18T | 137 | 18 | 459 | >50 | 156.99 | 34.26 | 3.07 | 3.43 |

| SERSC-16T | 211 | 1 | 302 | 11.25 | 118.45 | 10.94 | 66 | 0.01 |

| This work | 173 | 150 | 305 | 37.83 | 105.09 | 46.68 | 2.72 | 22.44 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.-G.; Jo, S.-H. RHLP-18T: A Radiation-Hardened 18T SRAM with Enhanced Read Stability and Low Power Consumption. Appl. Sci. 2025, 15, 5712. https://doi.org/10.3390/app15105712

Kim H-G, Jo S-H. RHLP-18T: A Radiation-Hardened 18T SRAM with Enhanced Read Stability and Low Power Consumption. Applied Sciences. 2025; 15(10):5712. https://doi.org/10.3390/app15105712

Chicago/Turabian StyleKim, Han-Gyeol, and Sung-Hun Jo. 2025. "RHLP-18T: A Radiation-Hardened 18T SRAM with Enhanced Read Stability and Low Power Consumption" Applied Sciences 15, no. 10: 5712. https://doi.org/10.3390/app15105712

APA StyleKim, H.-G., & Jo, S.-H. (2025). RHLP-18T: A Radiation-Hardened 18T SRAM with Enhanced Read Stability and Low Power Consumption. Applied Sciences, 15(10), 5712. https://doi.org/10.3390/app15105712