Decoupled Control for Double-T Dc-Dc MMC Topology for MT-HVdc/MVdc Grids

Abstract

Featured Application

Abstract

1. Introduction

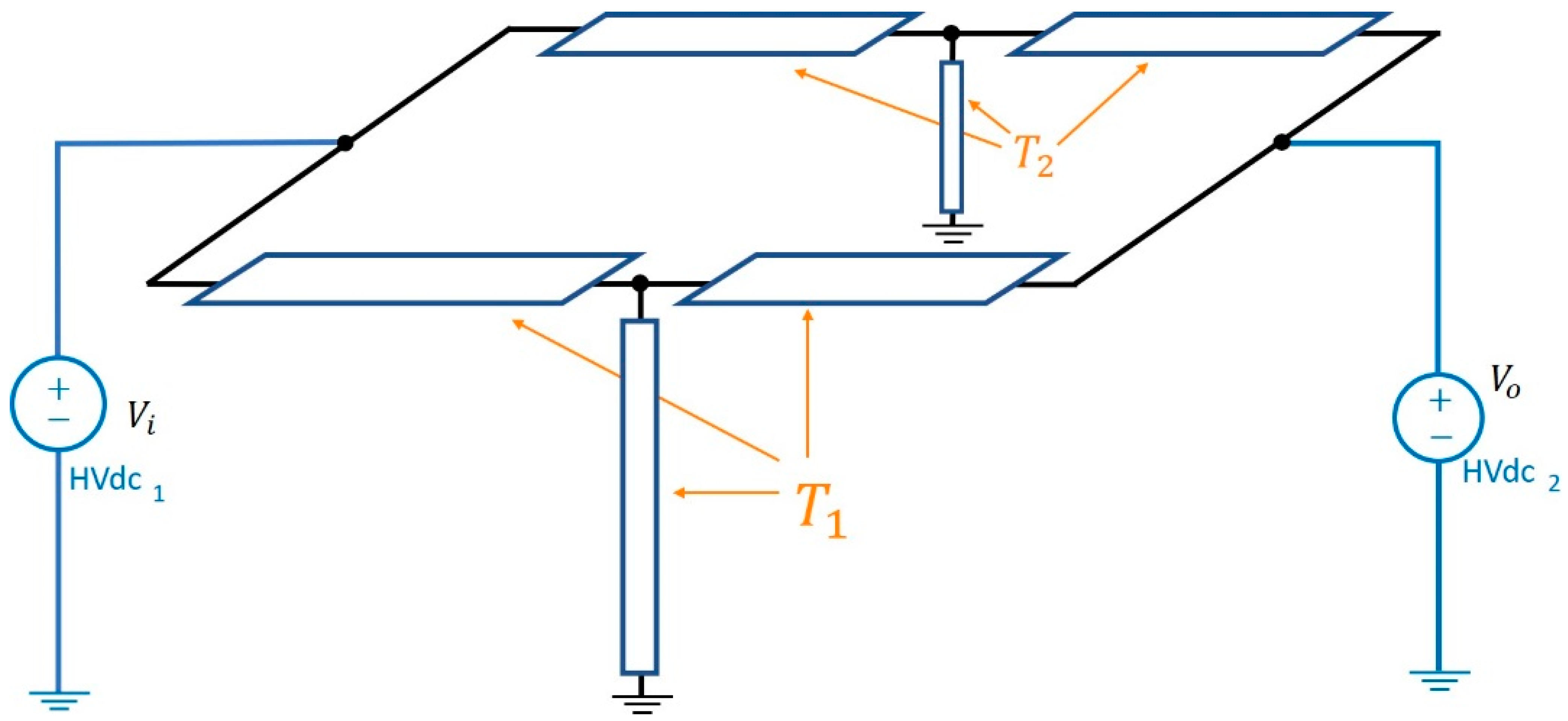

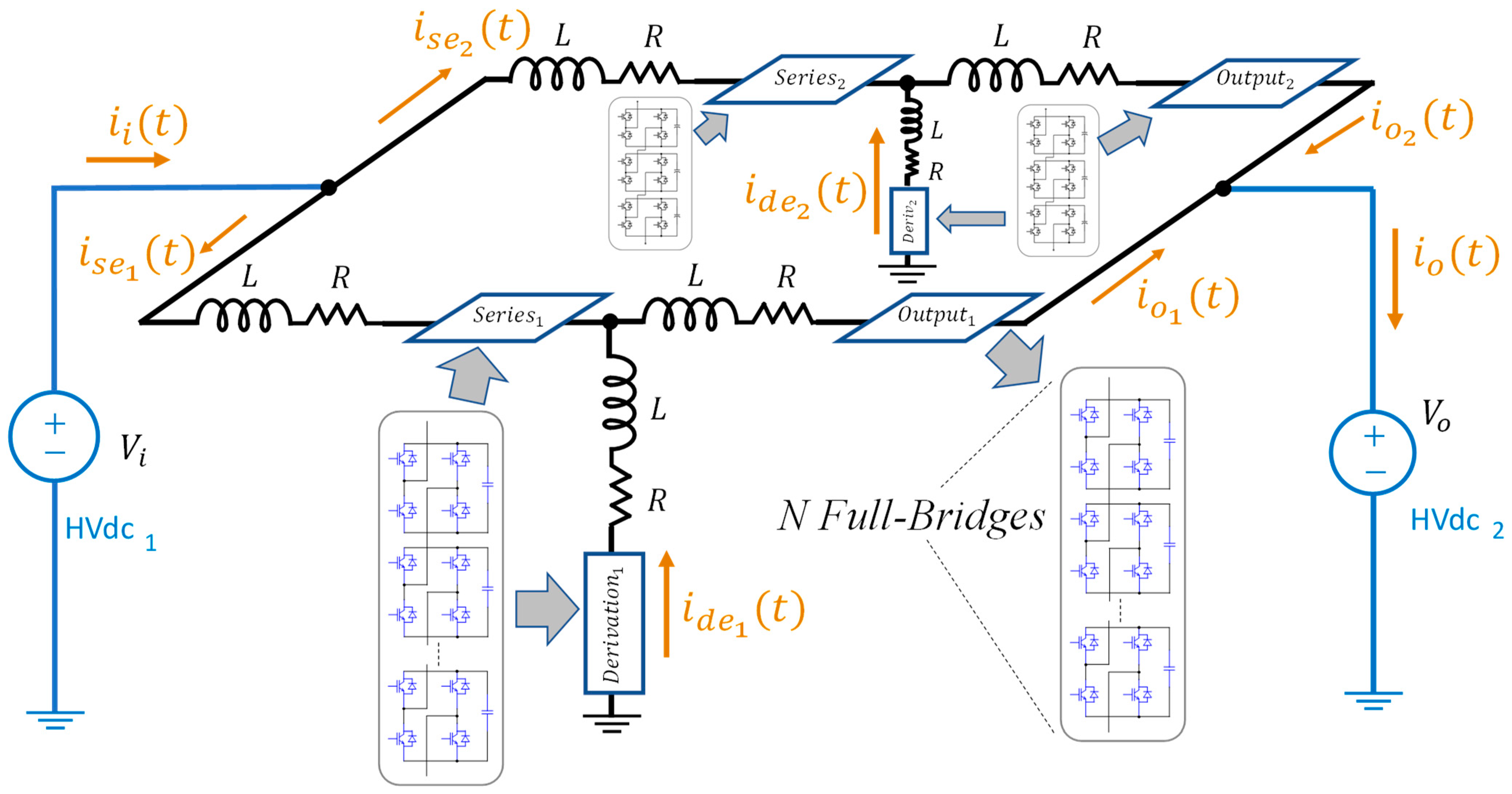

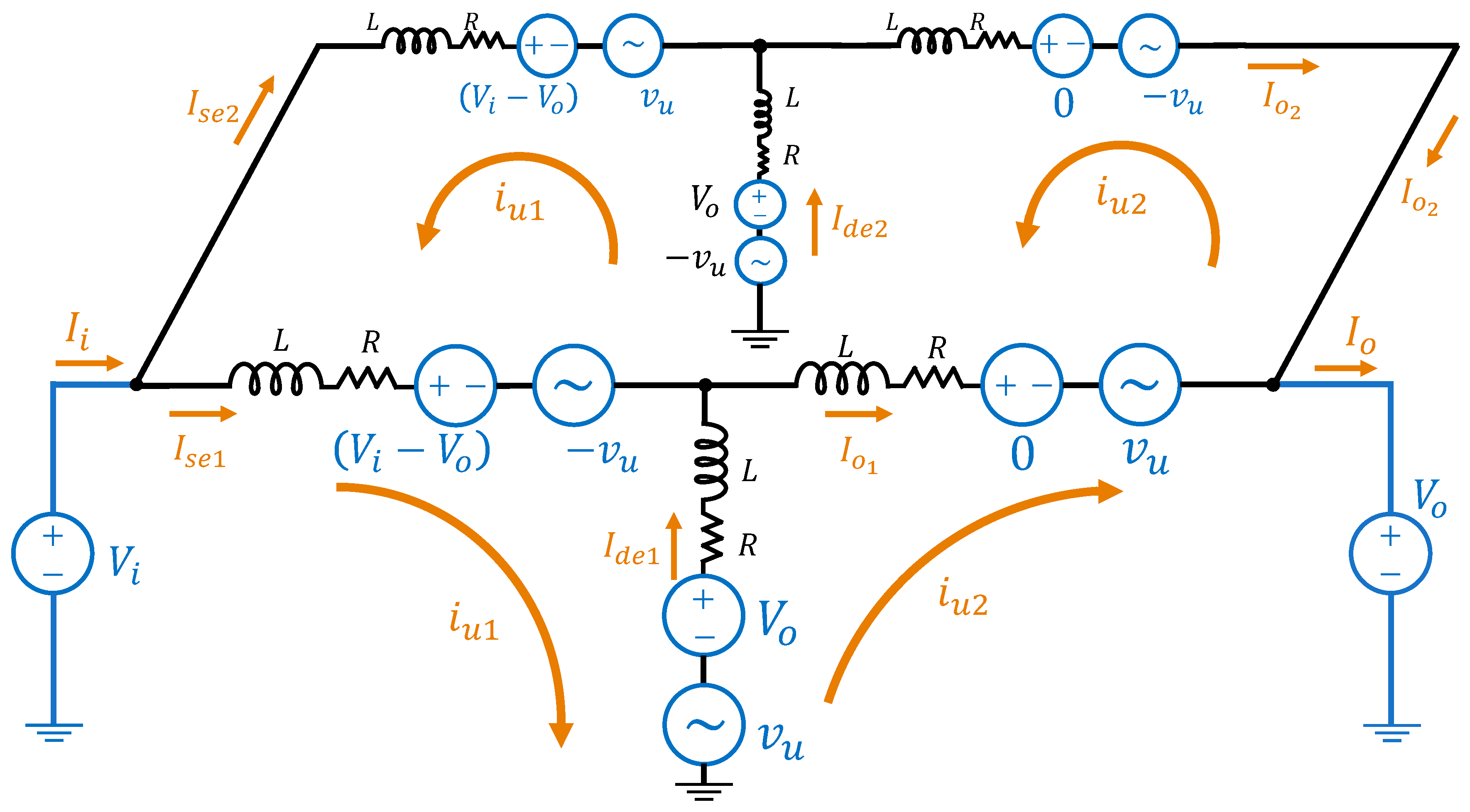

2. Converter Model

3. Operating Principle

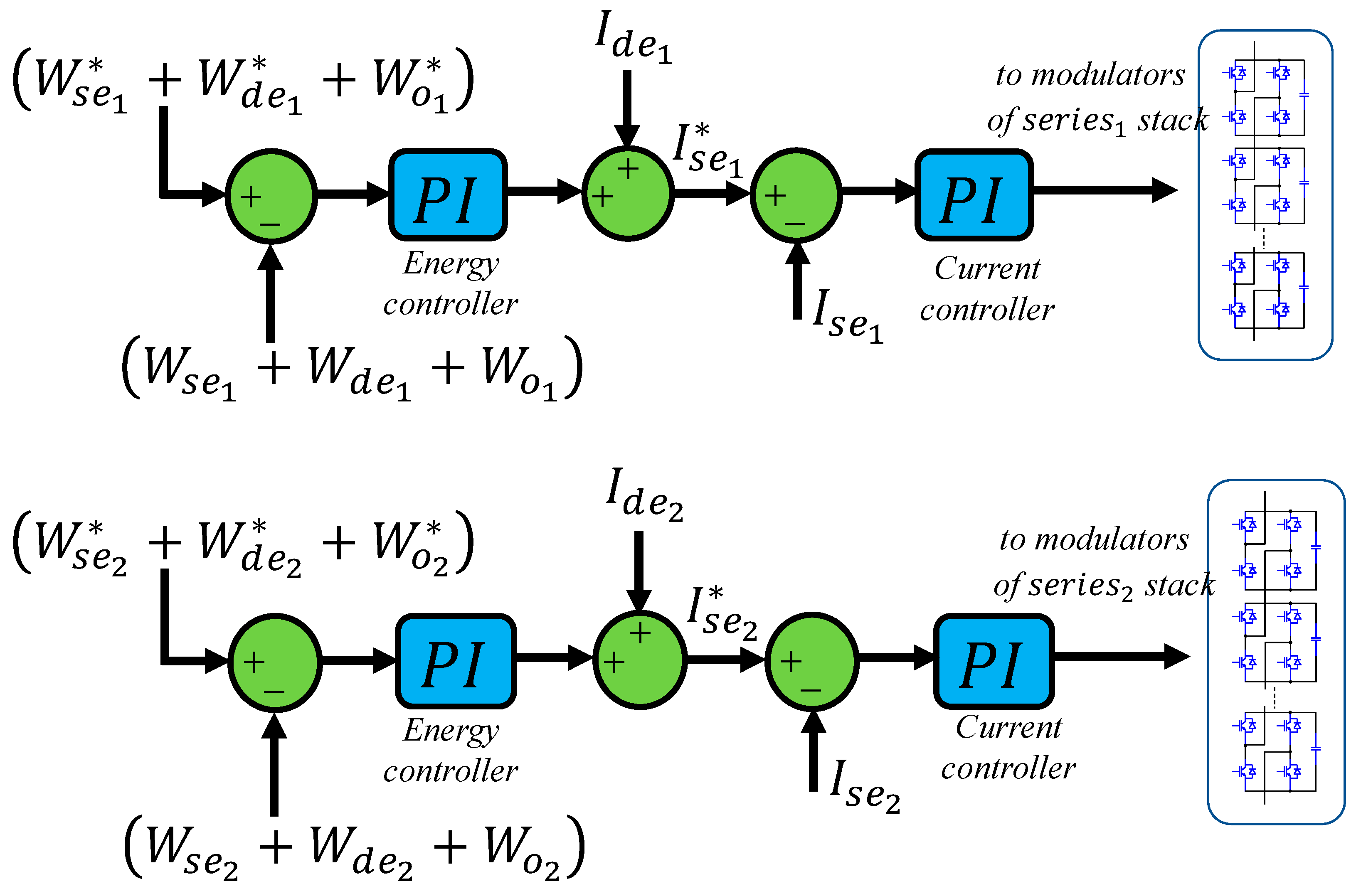

4. Control of the Double-T Converter

- A.

- Energy Balance of Stacks

- B.

- Intra-Stacks Voltage Balance

- C.

- Decoupling Energy Balance Control

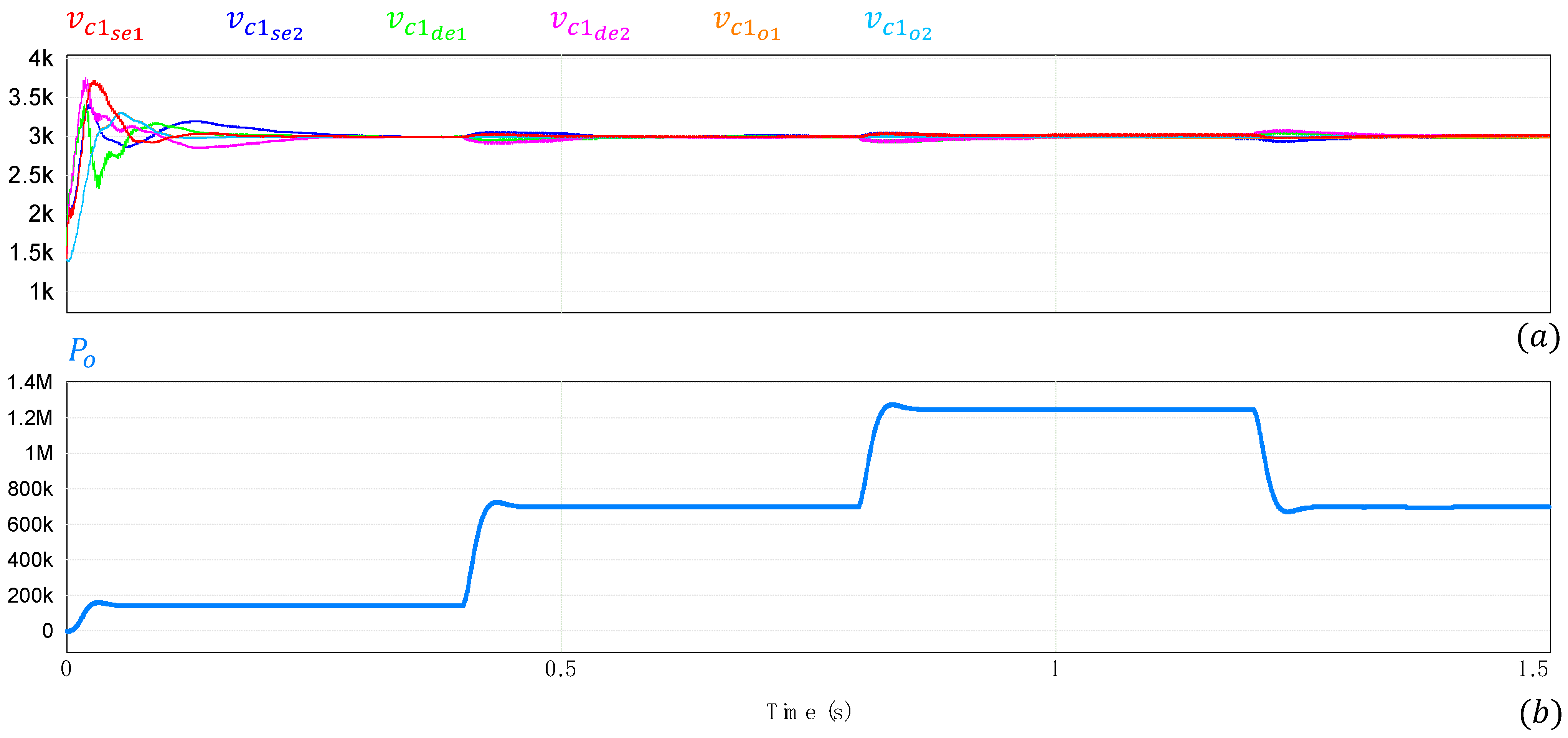

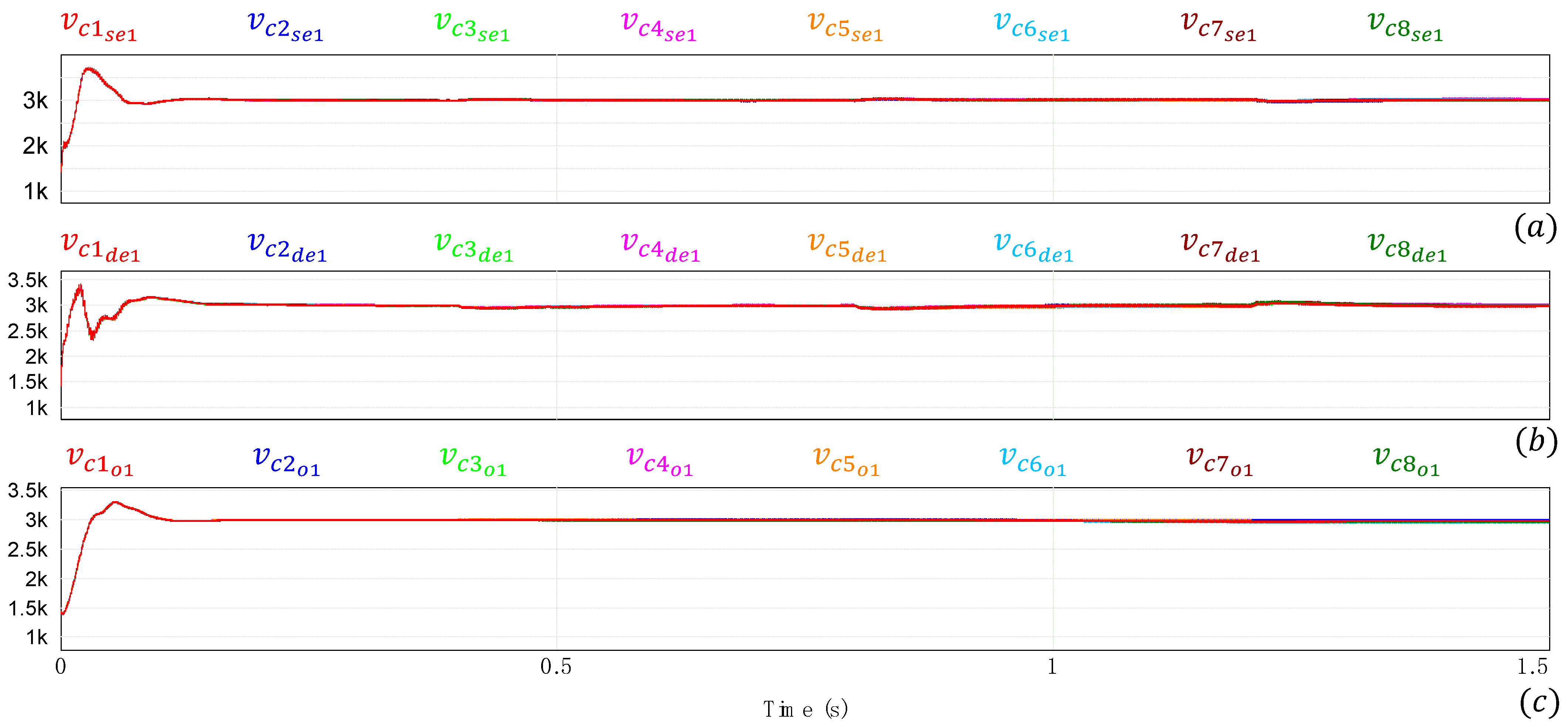

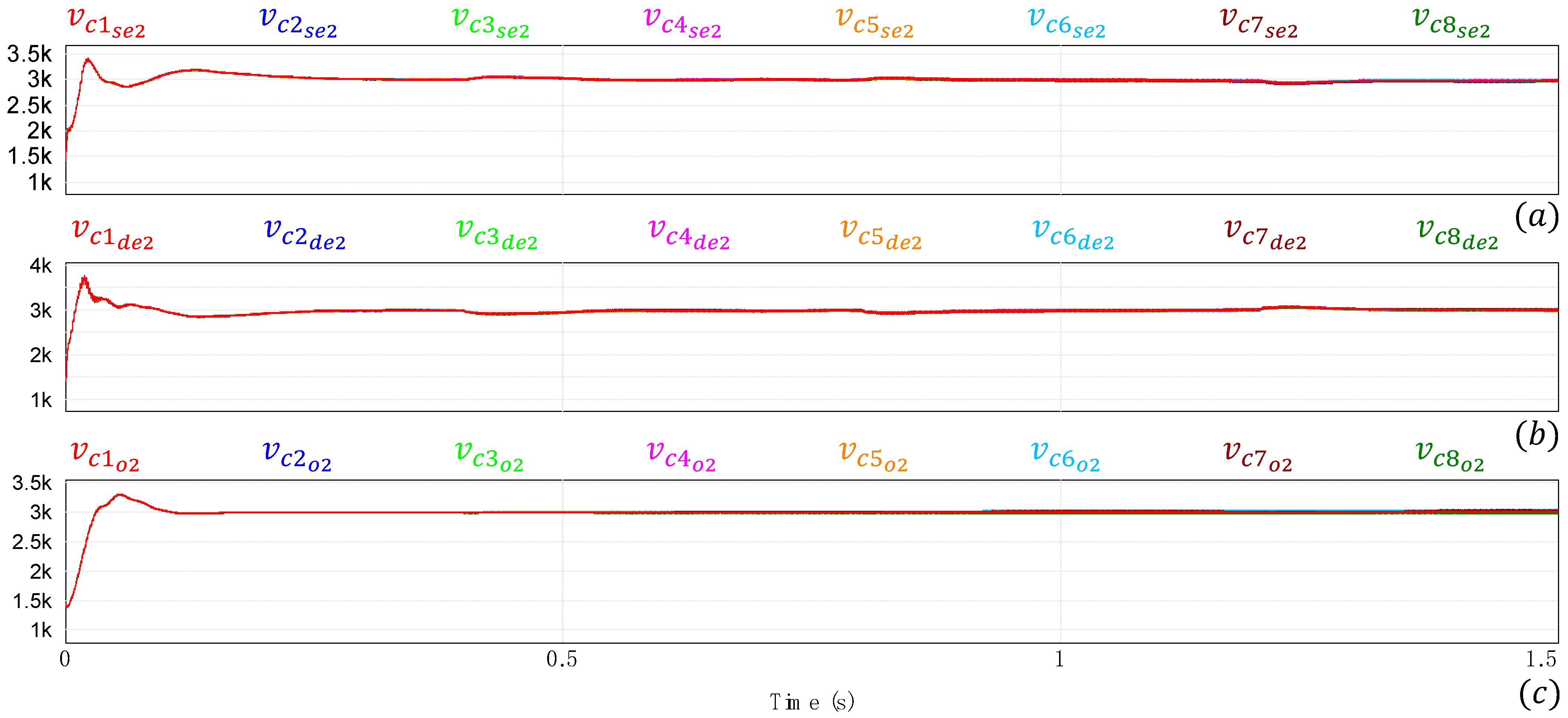

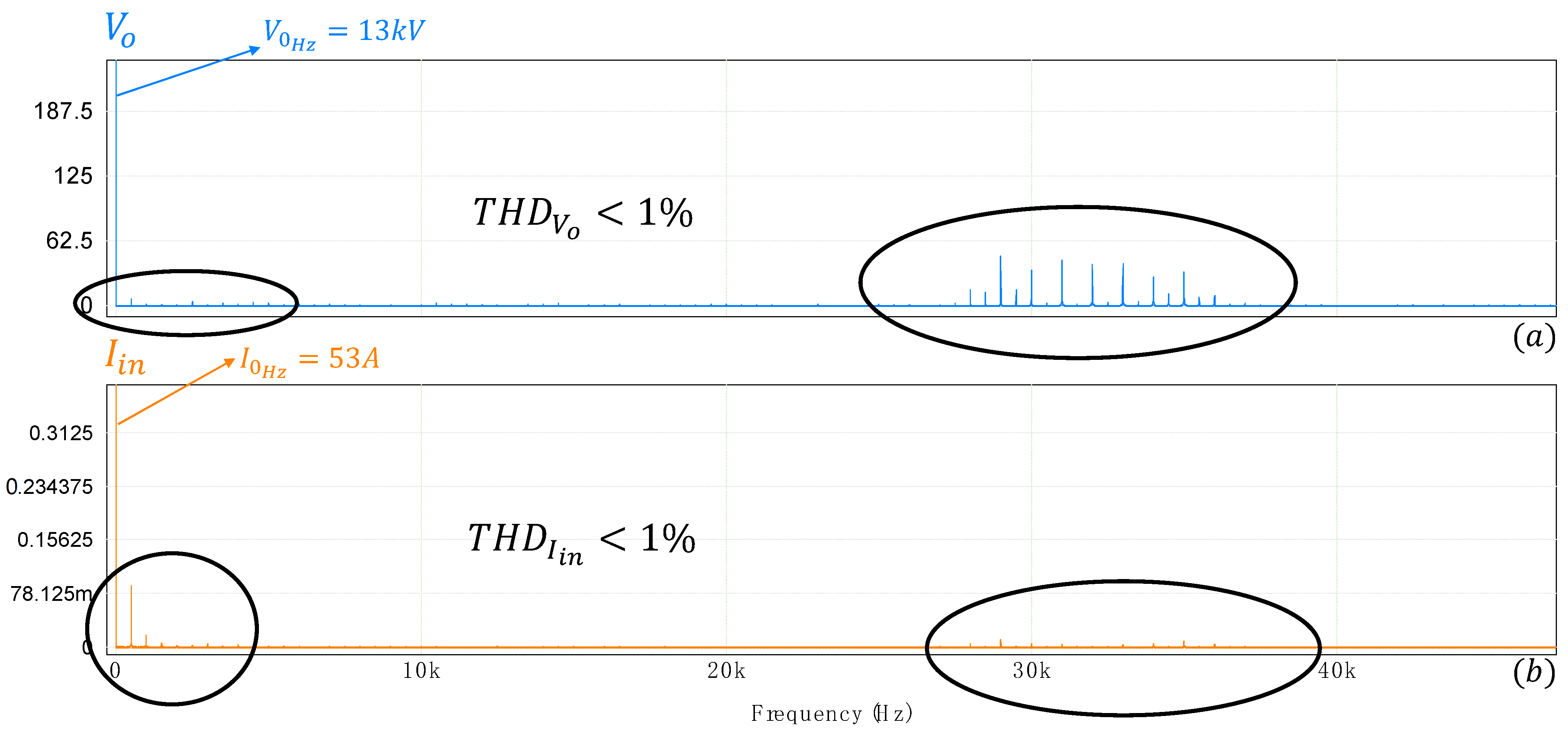

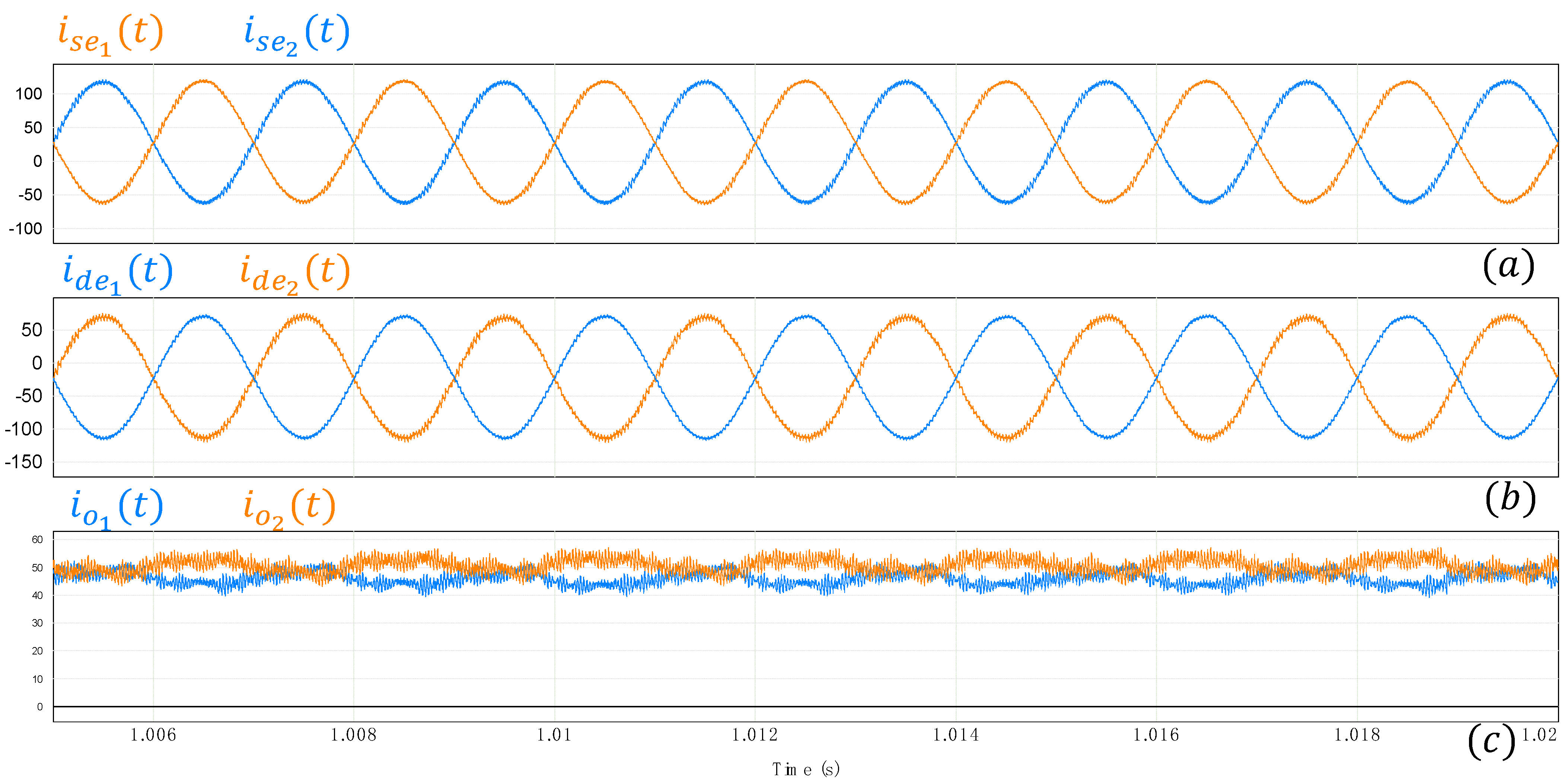

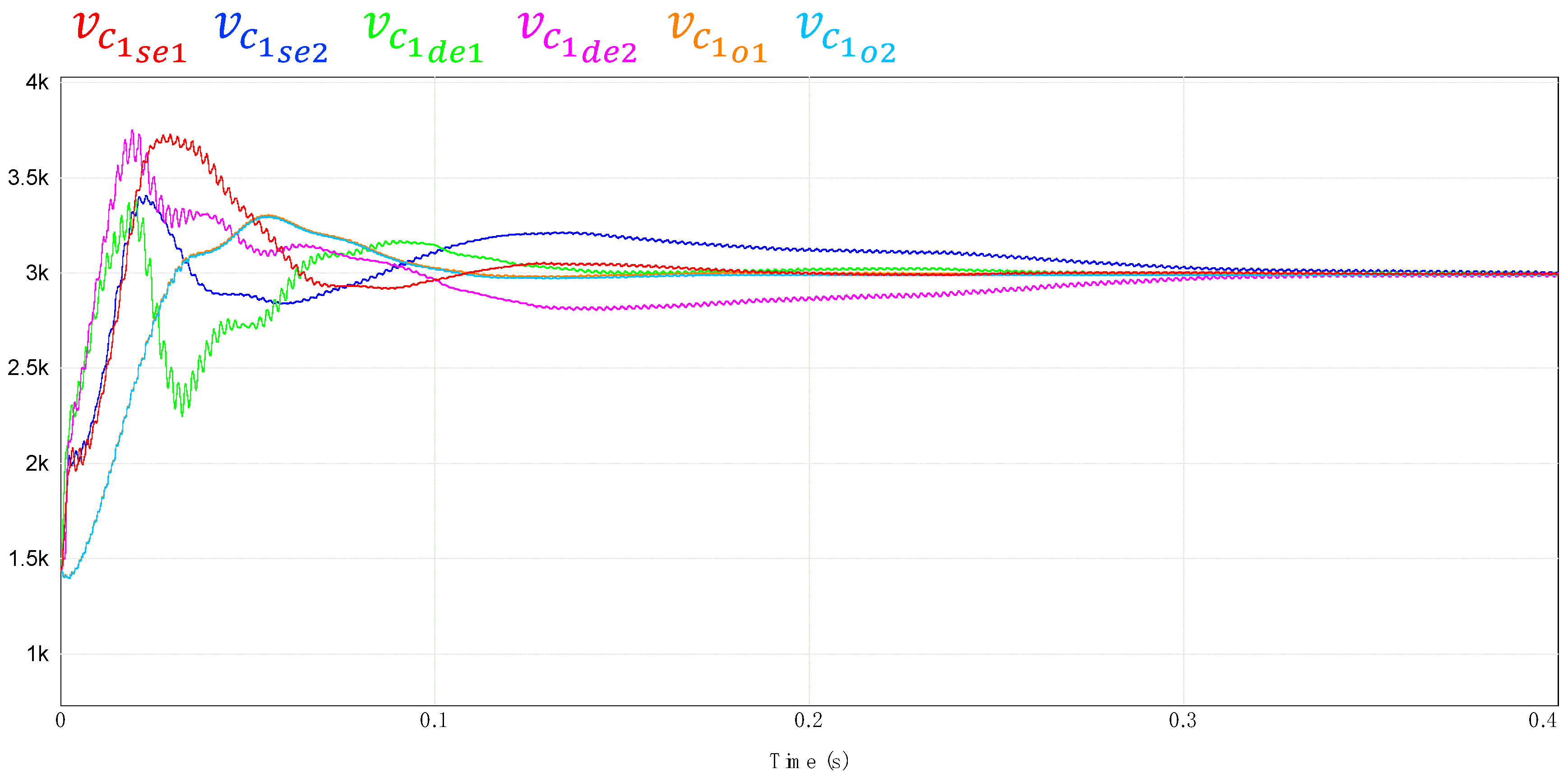

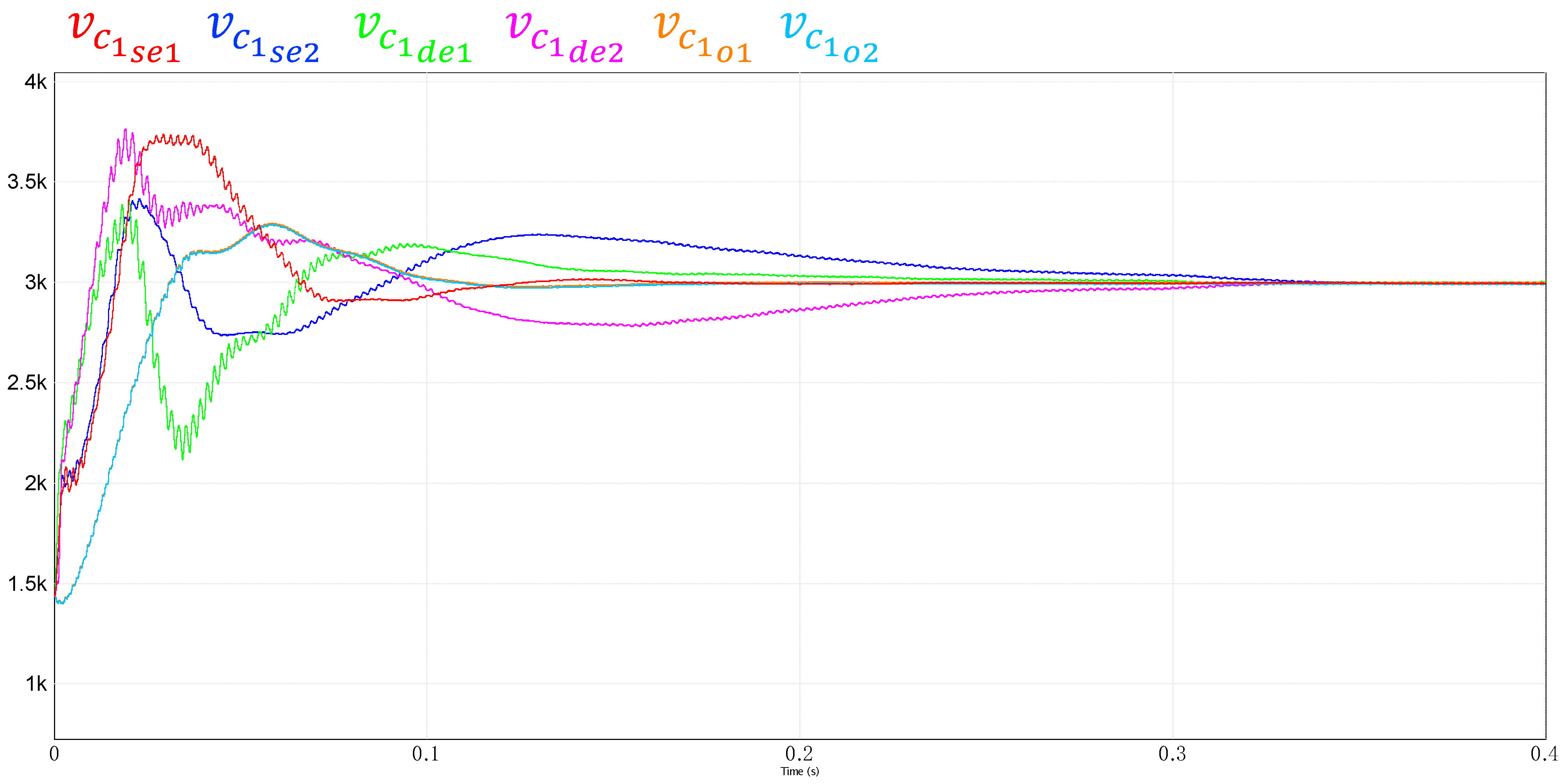

5. Simulations Results

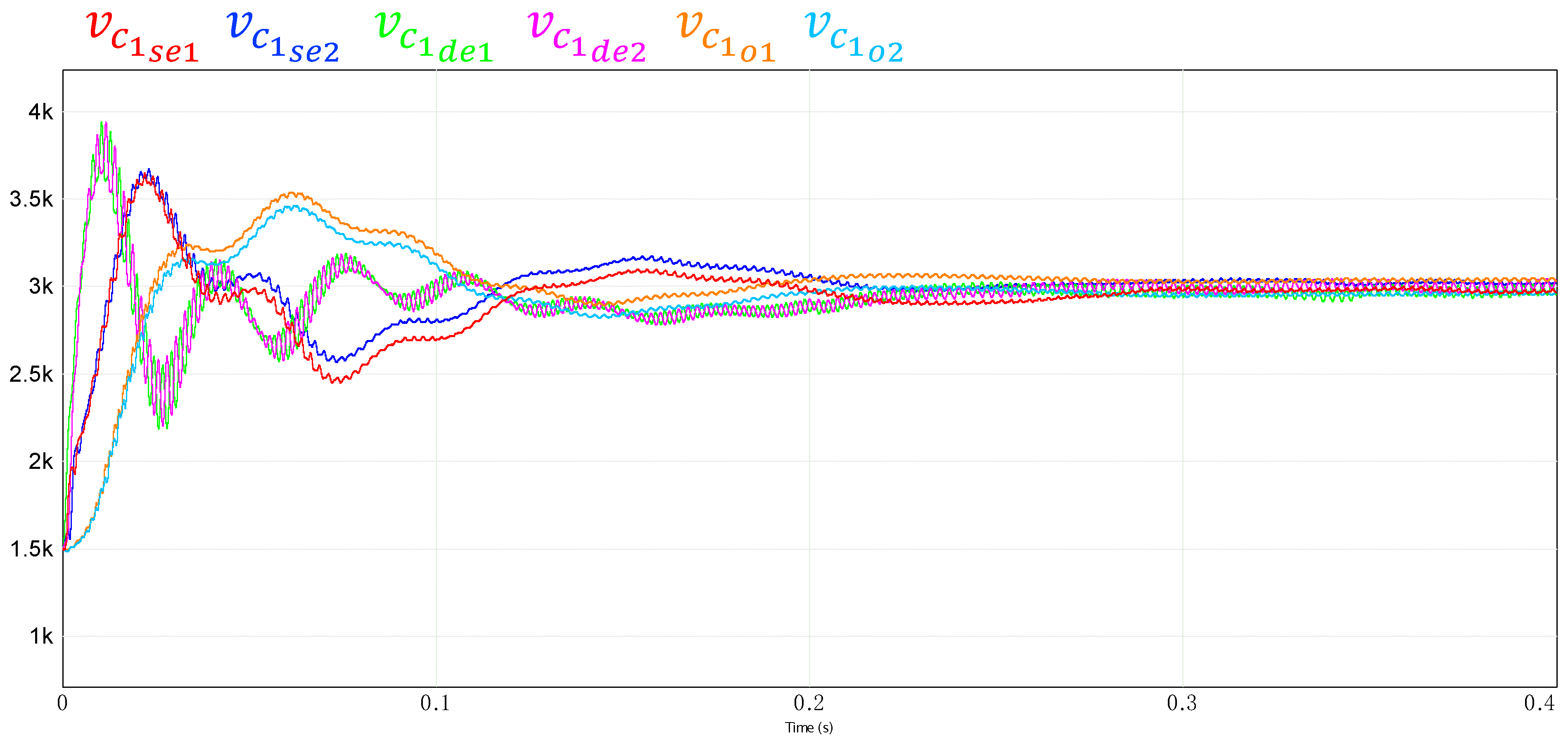

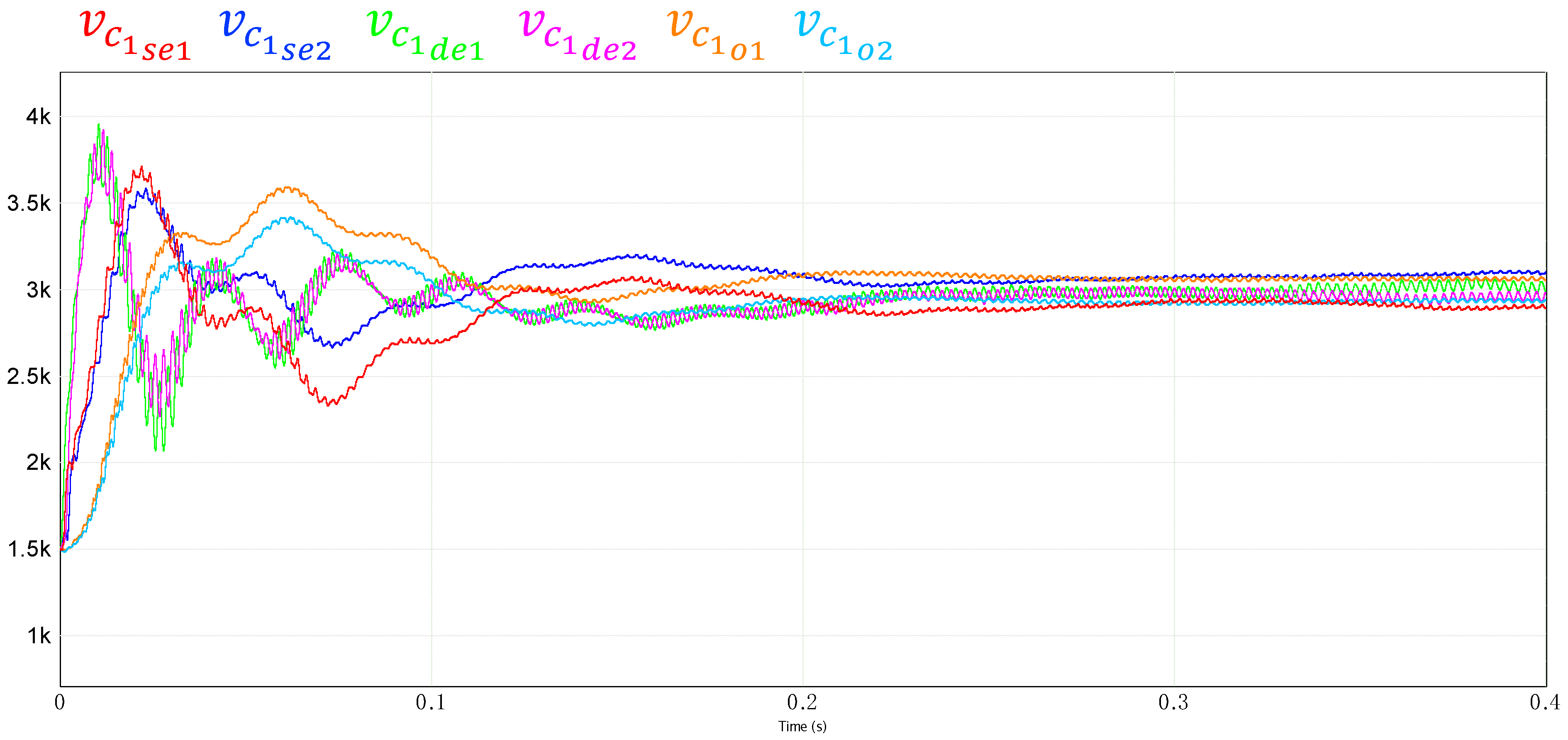

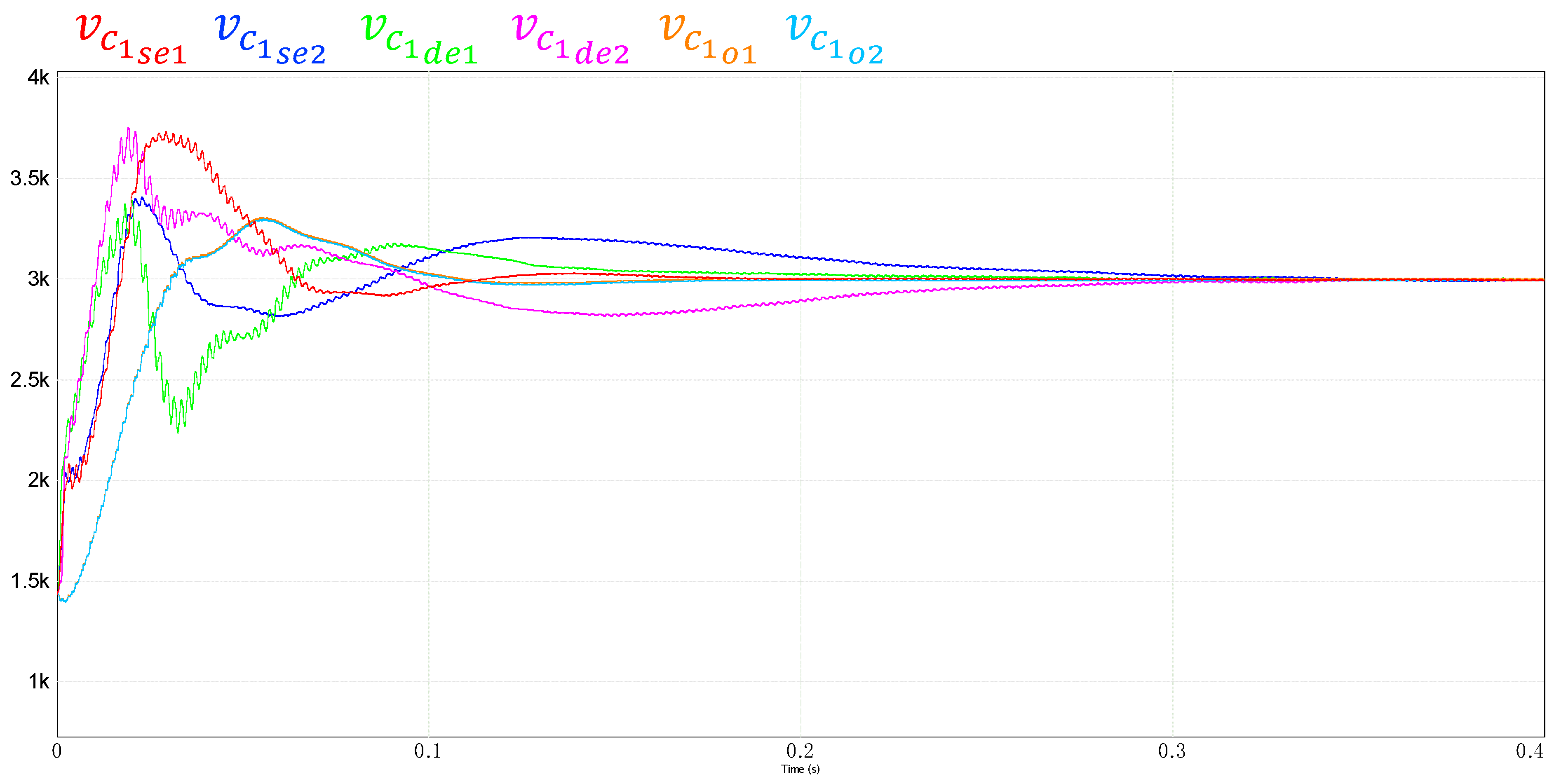

6. Brief Sensitivity Analysis

6.1. Case 1

6.2. Case 2

6.3. Case 3

6.4. Case 4

6.5. Case 5

6.6. Case 6

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Conflicts of Interest

References

- Liang, Y.; Ren, Y.; He, W. An Enhanced Current Differential Protection for AC Transmission Lines Connecting MMC-HVDC Stations. IEEE Syst. J. 2022, 17, 892–903. [Google Scholar] [CrossRef]

- Mehdi, A.; Kim, C.H.; Hussain, A.; Kim, J.S.; Hassan, S.J.U. A Comprehensive Review of Auto-Reclosing Schemes in AC, DC, and Hybrid (AC/DC) Transmission Lines. IEEE Access 2021, 9, 74325–74342. [Google Scholar] [CrossRef]

- Xu, X.; Meng, F.; Paramene, A.; Chen, X.; Qiu, L.; Zhou, W. Investigation on loss reduction strategies of single-core HVAC submarine cables. In Proceedings of the 22nd International Symposium on High Voltage Engineering (ISH 2021), Xi’an, China, 21–26 November 2021; pp. 44–48. [Google Scholar]

- Stanojev, O.; Garrison, J.; Hedtke, S.; Franck, C.M.; Demiray, T. Benefit Analysis of a Hybrid HVAC/HVDC Transmission Line: A Swiss Case Study. In Proceedings of the 2019 IEEE Milan PowerTech, Milan, Italy, 23–27 June 2019; pp. 1–6. [Google Scholar]

- Halder, T. Comparative Study of HVDC and HVAC for a bulk power Transmission. In Proceedings of the IEEE Power and Energy and Control (ICPEC), Dindigul, India, 6–8 February 2013; pp. 139–144. [Google Scholar]

- Meah, K.; Ula, S. Comparative Evaluation of HVDC and HVAC Transmission Systems. In Proceedings of the IEEE Power Engineering Society General Meeting, Tampa, FL, USA, 24–28 June 2007. [Google Scholar]

- Gumilar, L.; Sholeh, M.; Cahyani, D.E.; Kusumawardana, A.; Habibi, M.A.; Akhmadi, S.F. Comparison of Renewable Energy Output Power Transmission to Loads Via HVAC and HVDC. In Proceedings of the 2021 4th International Seminar on Research of Information Technology and Intelligent Systems (ISRITI), Yogyakarta, Indonesia, 16–17 December 2021; pp. 458–463. [Google Scholar]

- Apostolaki-Iosifidou, E.; Mccormack, R.; Kempton, W.; Mccoy, P.; Ozkan, D. Transmission Design and Analysis for Large-Scale Offshore Wind Energy Development. IEEE Power Energy Technol. Syst. J. 2019, 6, 22–31. [Google Scholar] [CrossRef]

- Hafeez, K.; Khan, S.A. High voltage direct current (HVDC) transmission: Future expectation for Pakistan. CSEE J. Power Energy Syst. 2019, 5, 82–86. [Google Scholar] [CrossRef]

- Migliori, M.; Lauria, S.; Michi, L.; Donnini, G.; Aluisio, B.; Vergine, C. Renewable sources integration using HVDC in parallel to AC traditional system: The Adriatic project. In Proceedings of the 2019 AEIT HVDC International Conference (AEIT HVDC), Florence, Italy, 9–10 May 2019; pp. 1–5. [Google Scholar]

- Wu, Y.; Yu, F.; Guo, J.; Shen, L. Research on the effects of different DC filter configurations in ±1100kV UHVDC transmission system. In Proceedings of the 16th IET International Conference on AC and DC Power Transmission (ACDC 2020), Online, 2–3 July 2020; pp. 758–761. [Google Scholar]

- Lange, J.; Neubert, R.; Alt, B.; Hussennether, V.; de Abreu, M.G.C. Innovative Converter Testing Technology and Overall Reliability and Availability Performance of HVDC Solutions. In Proceedings of the 2021 AEIT HVDC International Conference (AEIT HVDC), Genoa, Italy, 27–28 May 2021; pp. 1–6. [Google Scholar]

- Tecnología HVDC y su Integración al sen, Cigre-Chile, 2021. Available online: https://www.cigre.cl/2021/07/23/tecnologia-hvdc-y-su-integracion-al-sen/ (accessed on 1 February 2023).

- Sousa, T.; Santos, M.L.; Jardini, J.A.; Casolari, R.P.; Nicola, G.L.C. An evaluation of the HVDC and HVAC transmission economic. In Proceedings of the 2012 Sixth IEEE/PES Transmission and Distribution: Latin America Conference and Exposition (T&D-LA), Montevideo, Uruguay, 3–5 September 2012; pp. 1–6. [Google Scholar] [CrossRef]

- ABB and Aibel Technical News. Available online: https://www.4coffshore.com/news/abb-and-aibel-net-dogger-bank-bounty-nid14371.html (accessed on 1 February 2023).

- CIGRE Session 2022 28 August–02 September 2022 Paris, France. Available online: https://www.cigre.org/article/GB/news/the_latest_news/roadmaps-to-a-common-destination-decarbonization-of-energy-systems (accessed on 1 February 2023).

- Ma, K.; Annakkage, U.D.; Karawita, C. Development of a small-signal assessment tool for multi-terminal LCC schemes. In Proceedings of the 15th IET International Conference on AC and DC Power Transmission (ACDC 2019), Coventry, UK, 5–7 February 2019; pp. 1–7. [Google Scholar]

- Garces, A.; Sanchez, S.; Bergna, G.; Tedeschi, E. HVDC Meshed Multi-Terminal Networks for Offshore Wind Farms: Dynamic Model, Load Flow and Equilibrium. In Proceedings of the IEEE COMPEL, Stanford, CA, USA, 9–12 July 2017; pp. 1–6. [Google Scholar]

- Ambia, M.N.; Meng, K.; Xiao, W.; Al-Durra, A.; Dong, Z.Y. Adaptive Droop Control of Multi-Terminal HVDC Network for Frequency Regulation and Power Sharing. IEEE Trans. Power Syst. 2021, 36, 566–578. [Google Scholar] [CrossRef]

- Solhjoukhah, Z.; Egea-Alvarez, A.; Gomis-Bellmunt, O. Voltage Control of Offshore Load Connected to a Multi-Terminal HVDC Transmission System. In Proceedings of the 11th IET International Conference on AC and DC Power Transmission, Birmingham, UK, 10–12 February 2015; pp. 1–9. [Google Scholar]

- Alagab, S.M.; Tennakoon, S.; Gould, C. Comparison of Single-stage and Multi-stage Marx DC-DC converters for HVDC application. In Proceedings of the 2018 53rd International Universities Power Engineering Conference (UPEC), Glasgow, UK, 4–7 September 2018; pp. 1–6. [Google Scholar]

- Zhang, S.; Li, B.; Zhao, X.; Zhang, Y.; Wang, W.; Xu, D. A Transformerless Hybrid Modular Step-up DC/DC Converter for Bipolar and Symmetrical Monopolar HVDC Interconnection. In Proceedings of the 2019 4th IEEE Workshop on the Electronic Grid (eGRID), Xiamen, China, 11–14 November 2019; pp. 1–6. [Google Scholar]

- Liu, Y.; Lei, D.; Ning, Z.; Ren, Y.; Wang, Y.; Tian, J.; Wang, H.; Xu, R. A Novel Topology of Three-Port DC-DC Converter with Improved Carrier Phase-Shifted Control for MVDC Applictions. In Proceedings of the 2021 IEEE/IAS Industrial and Commercial Power System Asia (I&CPS Asia), Chengdu, China, 18–21 July 2021; pp. 74–78. [Google Scholar]

- Páez, J.D.; Frey, D.; Maneiro, J.; Bacha, S.; Dworakowski, P. Overview of DC–DC Converters Dedicated to HVdc Grids. IEEE Trans. Power Deliv. 2019, 34, 119–128. [Google Scholar] [CrossRef]

- Adam, G.P.; Gowaid, I.A.; Finney, S.J.; Holliday, D.; Williams, B.W. Review of dc-dc converters for multi-terminal hvdc transmission networks. IET Power Electron. 2016, 9, 281–296. [Google Scholar] [CrossRef]

- Cui, W.; Shao, S.; Zhang, J.; Li, Y.; Zhang, J. Bidirectional Modular Multilevel Resonant DC-DC Converter for Medium Voltage Power Conversion. In Proceedings of the 2020 IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020; pp. 4380–4385. [Google Scholar]

- Zhang, X.; Green, T.C. The Modular Multilevel Converter for High Step-Up Ratio DC–DC Conversion. IEEE Trans. Ind. Electron. 2015, 62, 4925–4936. [Google Scholar] [CrossRef]

- Shao, S.; Li, Y.; Sheng, J.; Li, C.; Li, W.; Zhang, J.; He, X. A Modular Multilevel Resonant DC–DC Converter. IEEE Trans. Power Electron. 2020, 35, 7921–7932. [Google Scholar] [CrossRef]

- Xiang, X.; Zhang, X.; Zhu, Y.; Chaffey, G.P.; Gu, Y.; Green, T.C. The Resonant Modular Multilevel DC Converters for High Step-ratio and Low Step-ratio Interconnection in MVDC Distribution Network. In Proceedings of the IECON 2019—45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019; pp. 5686–5693. [Google Scholar]

- Pineda, C.; Pereda, J.; Rojas, F.; Cerda, C.; Zhang, X.; Watson, A.J. Asymmetrical Triangular Current Mode (ATCM) for Bidirectional High Step Ratio Modular Multilevel Dc–Dc Converter. IEEE Trans. Power Electron. 2020, 35, 6906–6915. [Google Scholar] [CrossRef]

- Elgenedy, M.A.; Alhurayyis, I.; Elkhateb, A.; Ahmed, K.; Kroičs, K. A New DC-DC Converter Linking LCC-HVDC Transmission Networks. In Proceedings of the 2021 23rd European Conference on Power Electronics and Applications (EPE’21 ECCE Europe), Ghent, Belgium, 6–10 September 2021; pp. P.1–P.10. [Google Scholar]

- Vidal, R.; Belenguer, E.; Pesce, C.; Soto, D.; Pena, R.; Blasco-Gimenez, R.; Riedemann, J. Power flow control using a DC-DC MMC for HVdc grid connected wind power plants. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 005107–005112. [Google Scholar] [CrossRef]

- Klimczak, P.; Blaszczyk, P.; Jez, R.; Koska, K. Double wye Modular Multilevel Converter—Direct DC-DC topology. In Proceedings of the 8th IET International Conference on Power Electronics, Machines and Drives (PEMD 2016), Glasgow, UK, 19–21 April 2016; pp. 1–6. [Google Scholar]

- Shivashanker, K.; Janaki, M.; Thirumalaivasan, R. Design of Decoupled Current Controller for Back to Back Modular Multilevel Converter Based HVDC Transmission System. In Proceedings of the 2021 Innovations in Power and Advanced Computing Technologies (i-PACT), Kuala Lumpur, Malaysia, 27–29 November 2021. [Google Scholar]

- Oates, C. Modular multilevel converter design for VSC HVDC applications. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 3, 505–515. [Google Scholar] [CrossRef]

| Description | Value |

|---|---|

| Input voltage, | |

| Output voltage, | |

| Rated output power, | |

| Dc-links capacitors, | |

| Arm inductances, | |

| Series equivalent resistance of inductors, | |

| Dc-links reference voltage | |

| Frequency of ac circulating currents | |

| Number of H-bridges per stack | |

| Number of arms | |

| Switching frequency, |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pesce, C.; Riedemann, J.; Peña, R.; Andrade, I.; Jara, W.; Villalobos, R. Decoupled Control for Double-T Dc-Dc MMC Topology for MT-HVdc/MVdc Grids. Appl. Sci. 2023, 13, 3778. https://doi.org/10.3390/app13063778

Pesce C, Riedemann J, Peña R, Andrade I, Jara W, Villalobos R. Decoupled Control for Double-T Dc-Dc MMC Topology for MT-HVdc/MVdc Grids. Applied Sciences. 2023; 13(6):3778. https://doi.org/10.3390/app13063778

Chicago/Turabian StylePesce, Cristián, Javier Riedemann, Rubén Peña, Iván Andrade, Werner Jara, and Rodrigo Villalobos. 2023. "Decoupled Control for Double-T Dc-Dc MMC Topology for MT-HVdc/MVdc Grids" Applied Sciences 13, no. 6: 3778. https://doi.org/10.3390/app13063778

APA StylePesce, C., Riedemann, J., Peña, R., Andrade, I., Jara, W., & Villalobos, R. (2023). Decoupled Control for Double-T Dc-Dc MMC Topology for MT-HVdc/MVdc Grids. Applied Sciences, 13(6), 3778. https://doi.org/10.3390/app13063778