Variable Multiple Interleaved Bi-Directional DC/DC Converter with Current Ripple Optimization

Abstract

1. Introduction

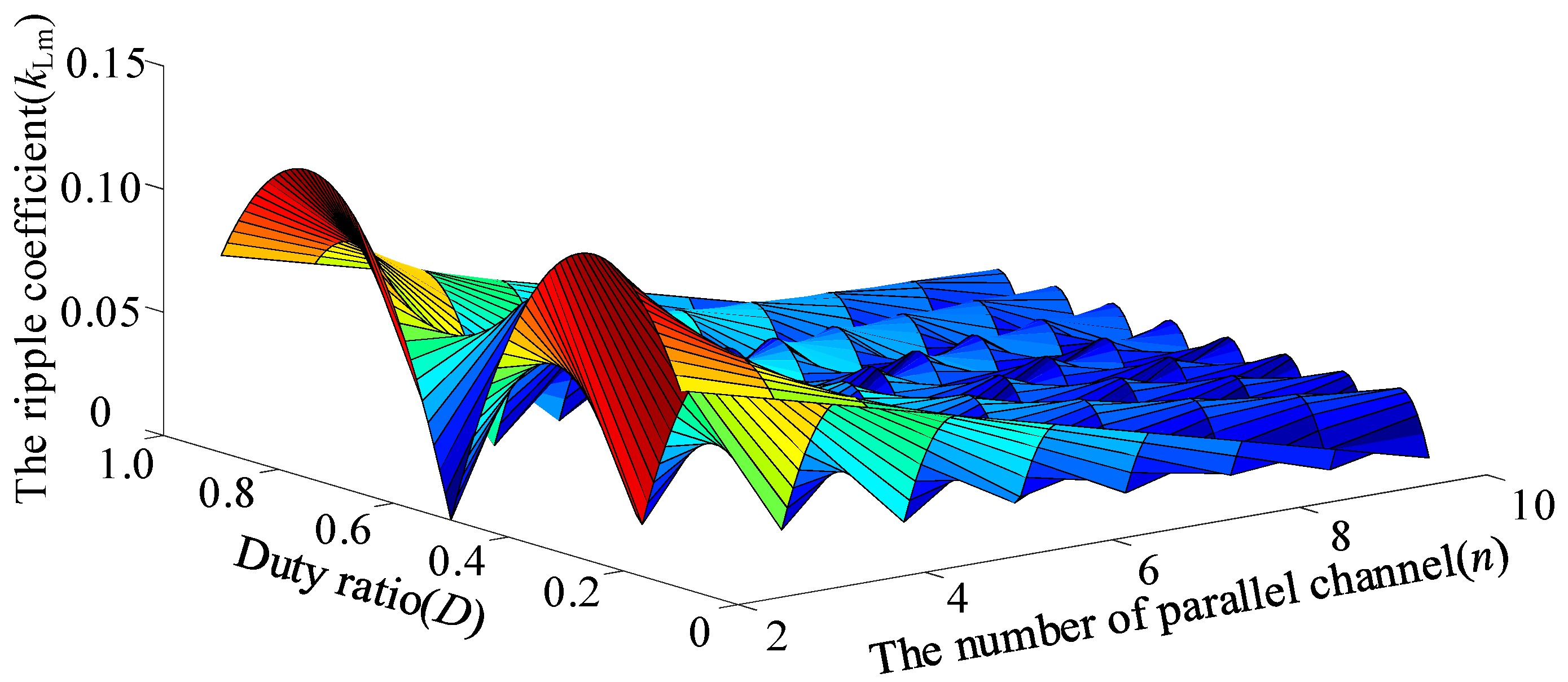

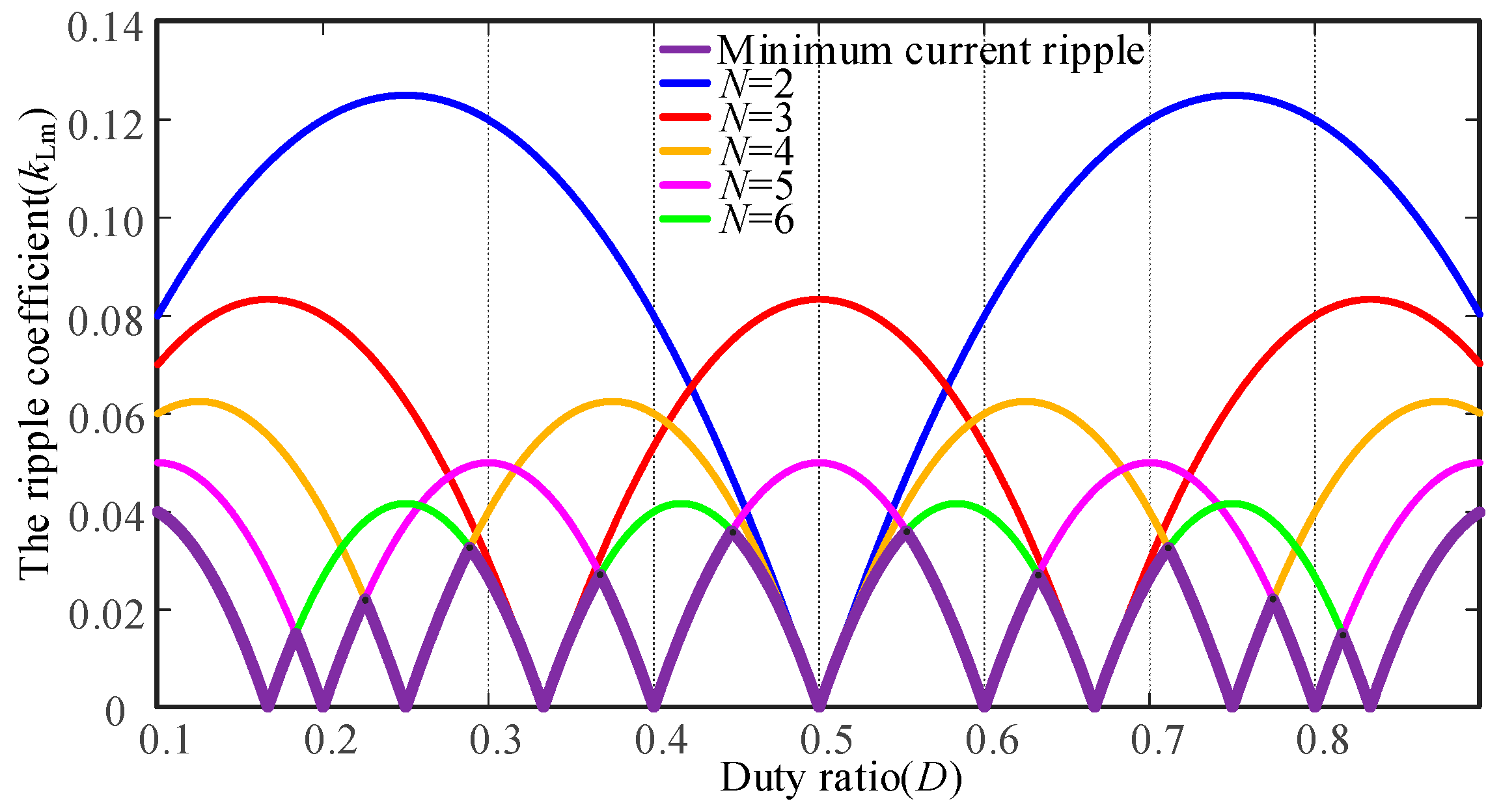

2. The Principle of Current Ripple Optimization

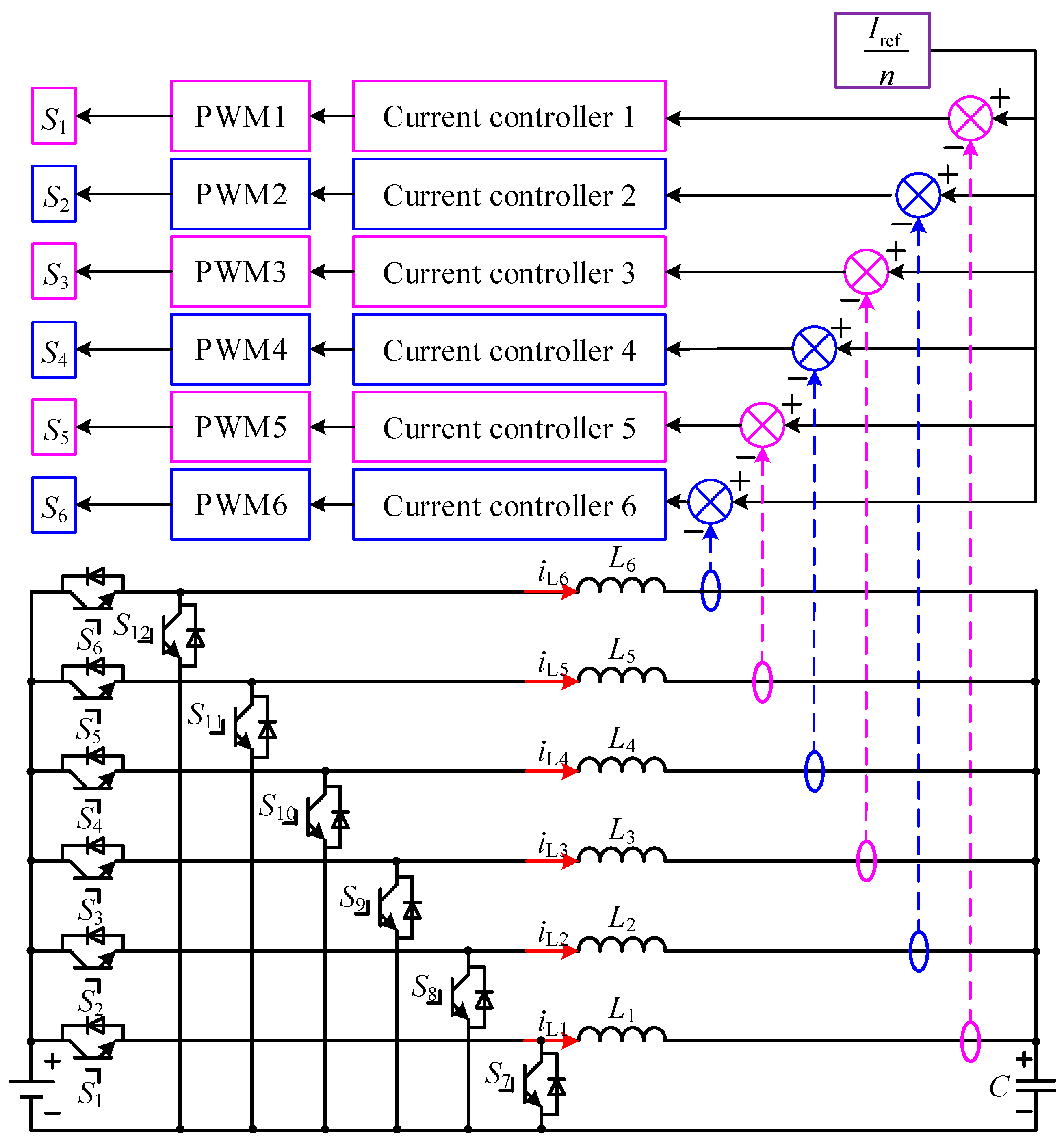

3. The Model of Variable Multiplicity Interleaving Bidirectional DC/DC Power Converter

3.1. The Mean Value Model

3.2. The AC Small Signal Model

4. The Design of Control Strategy for the Variable Multiplicity Interleaving Bidirectional DC/DC Power Converter

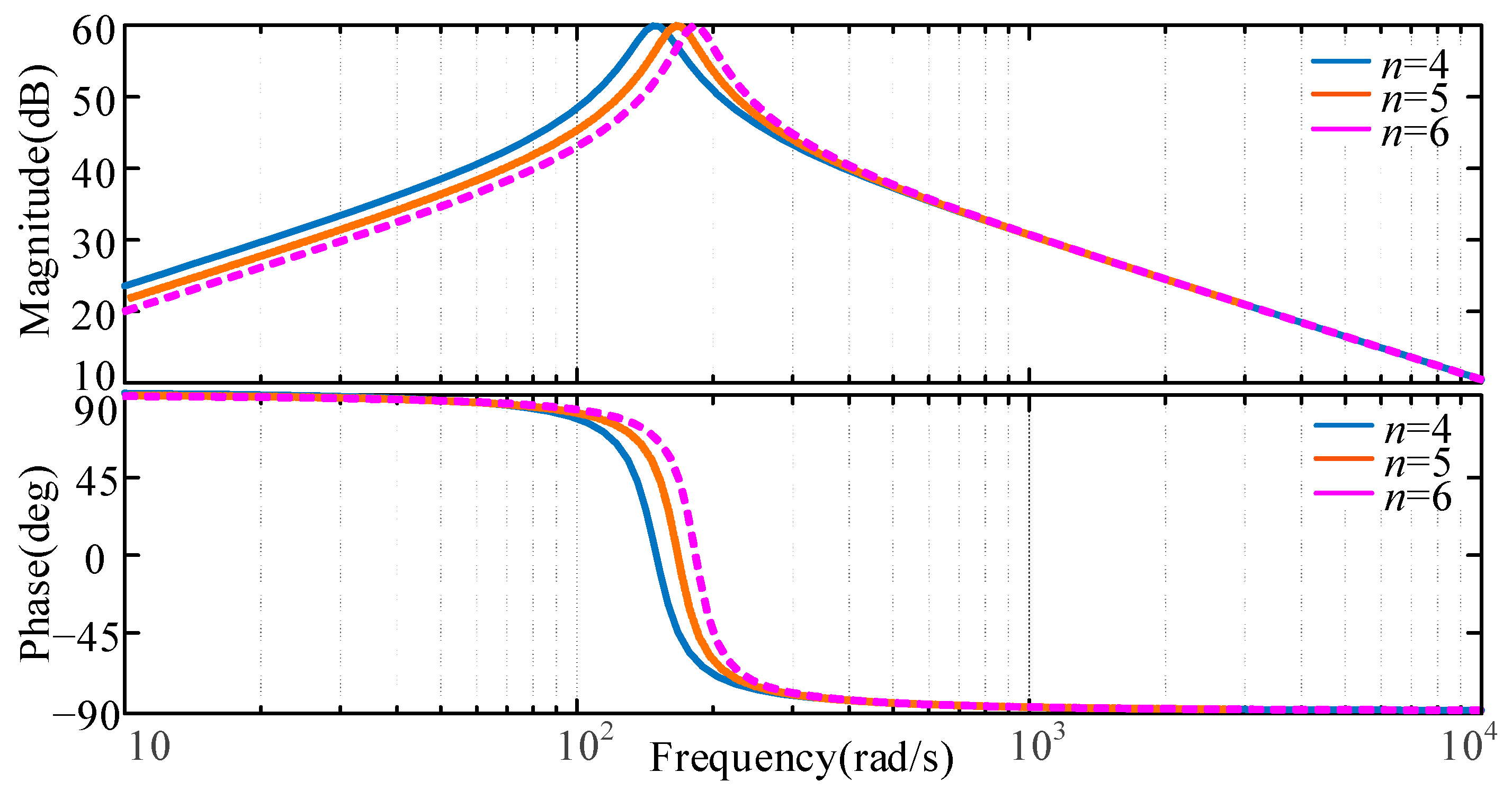

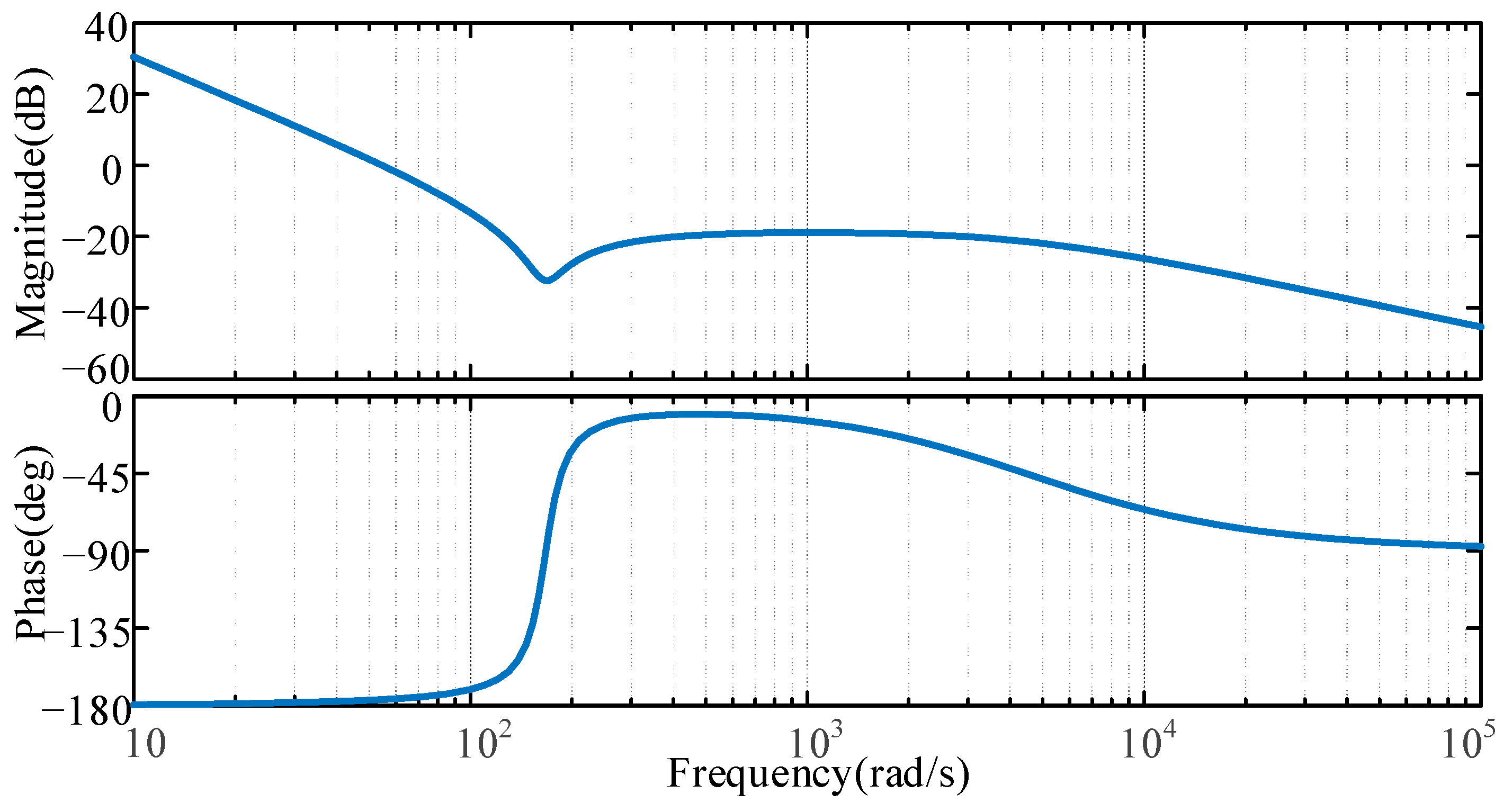

4.1. The Analysis of the Open-Loop Characteristic of the Variable Multiplicity Interleaving Bidirectional DC/DC Power Converter

4.2. The Design of the Current Compensation Network

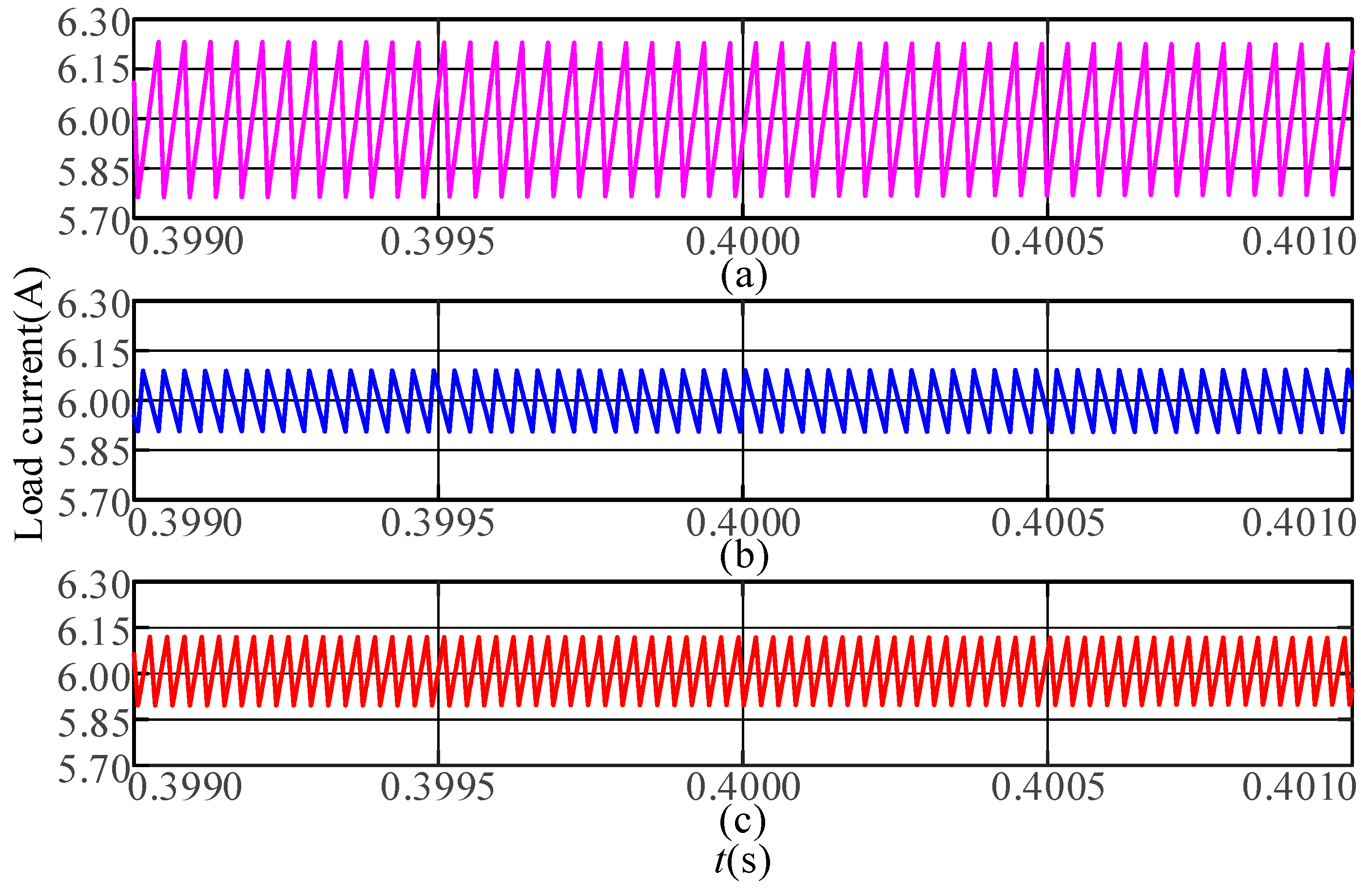

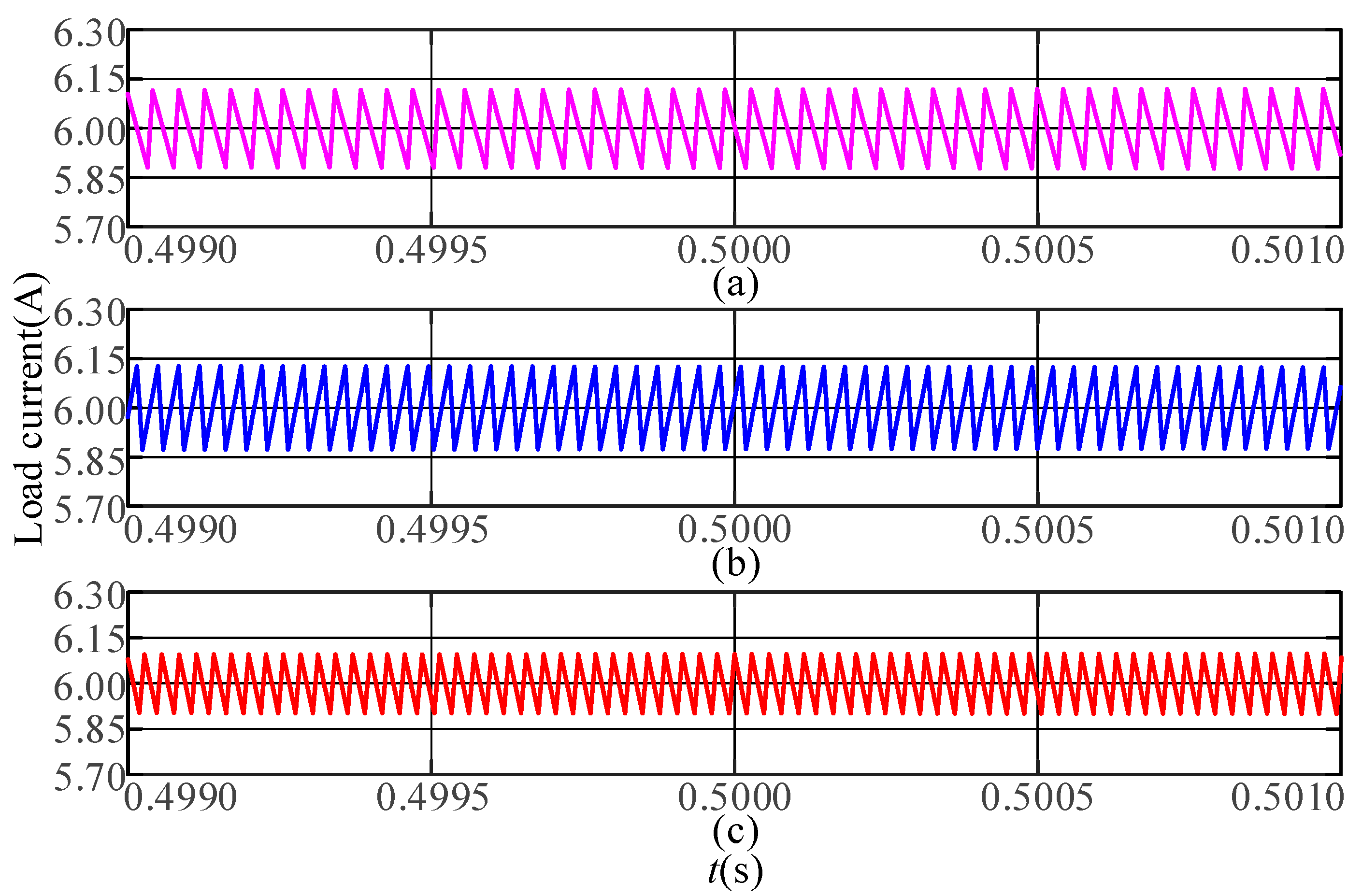

4.3. The Simulation of the Variable Multiplicity Interleaving Bidirectional DC/DC Power Converter

5. The Experiment and Results

5.1. Experimental Platform

5.2. The Experimental Results of the Current Ripple Optimization in Variable Channel Interleaving Bidirectional DC/DC Power Converter

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Hannan, M.A.; Wali, S.B.; Ker, P.J.; Abd Rahman, M.S.; Mansor, M.; Ramachandaramurthy, V.K.; Muttaqi, K.M.; Mahlia, T.M.I.; Dong, Z.Y. Battery energy-storage system: A review of technologies, optimization objectives, constraints, approaches, and outstanding issues. J. Energy Storage 2021, 42, 103–110. [Google Scholar] [CrossRef]

- Tong, Y.; Liang, J.; Liu, H.K.; Dou, S.X. Energy storage in Oceania. Energy Storage Mater. 2019, 20, 176–187. [Google Scholar] [CrossRef]

- Mahmoud, M.; Ramadan, M.; Olabi, A.G.; Pullen, K.; Naher, S. A review of mechanical energy storage systems combined with wind and solar applications. Energy Convers. Manag. 2020, 210, 112–125. [Google Scholar] [CrossRef]

- Babu, T.S.; Vasudevan, K.R.; Ramachandaramurthy, V.K.; Sani, S.B.; Chemud, S.; Lajim, R.M. A comprehensive review of hybrid energy storage systems: Converter topologies, control strategies and future prospects. IEEE Access 2020, 8, 148702–148721. [Google Scholar] [CrossRef]

- Lee, H.S.; Yun, J.J. High-efficiency bidirectional buck–boost converter for photovoltaic and energy storage systems in a smart grid. IEEE Trans. Power Electron. 2018, 34, 4316–4328. [Google Scholar] [CrossRef]

- Zhang, Y.; Cheng, X.F.; Yin, C.; Cheng, S. A soft-switching bidirectional DC–DC converter for the battery super-capacitor hybrid energy storage system. IEEE Trans. Ind. Electron. 2018, 65, 7856–7865. [Google Scholar] [CrossRef]

- Zhuo, S.; Gaillard, A.; Li, Q.; Ma, R.; Paire, D.; Gao, F. Current ripple optimization of four-phase floating interleaved DC–DC boost converter under switch fault. IEEE Trans. Ind. Appl. 2020, 56, 4214–4224. [Google Scholar] [CrossRef]

- Amiri, M.; Farzanehfard, H. A High-Efficiency Interleaved Ultra-High Step-Down DC–DC Converter with Very Low Output Current Ripple. IEEE Trans. Ind. Electron. 2018, 66, 5177–5185. [Google Scholar] [CrossRef]

- Nag, S.S.; Mishra, S.; Joshi, A. A passive filter building block for input or output current ripple cancellation in a power converter. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 4, 564–575. [Google Scholar] [CrossRef]

- Wang, Z.; Wang, P.; Li, B.; Ma, X.; Wang, P. A Bidirectional DC–DC Converter with High Voltage Conversion Ratio and Zero Ripple Current for Battery Energy Storage System. IEEE Trans. Power Electron. 2020, 36, 8012–8027. [Google Scholar] [CrossRef]

- Villarreal-Hernandez, C.A.; Ruiz-Martinez, O.F.; Mayo-Maldonado, J.C.; Escobar, G.; Valdez-Resendiz, J.E.; Rosas-Caro, J.C. Minimum Current Ripple Point Tracking Control for Interleaved Dual Switched-Inductor DC–DC Converters. IEEE Trans. Ind. Electron. 2020, 68, 175–185. [Google Scholar] [CrossRef]

- Hu, X.; Ma, P.; Wang, J.; Tan, G. A hybrid cascaded DC–DC boost converter with ripple reduction and large conversion ratio. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 8, 761–770. [Google Scholar] [CrossRef]

- Yuan, Z.; Xu, H. Pulse power supply with faster response and low ripple current using inductive storage and interleaving technology. CPSS Trans. Power Electron. Appl. 2020, 5, 54–62. [Google Scholar] [CrossRef]

- Lin, B.R.; Hsieh, F.Y.; Wang, D. Analysis, design and implementation of active clamp zero voltage switching converter with output ripple current cancellation. IEE Proc.-Electr. Power Appl. 2006, 153, 653–663. [Google Scholar] [CrossRef]

- Kumar, A.; Sensarma, P. Ripple-free input current high voltage gain DC–DC converters with coupled inductors. IEEE Trans. Power Electron. 2018, 34, 3418–3428. [Google Scholar] [CrossRef]

- Azer, P.; Emadi, A. Generalized state space average model for multi-phase interleaved buck, boost and buck-boost DC-DC converters: Transient, steady-state and switching dynamics. IEEE Access 2020, 8, 77735–77745. [Google Scholar] [CrossRef]

- Kanzian, M.; Agostinelli, M.; Huemer, M. Digital hysteresis sliding mode control for interleaved DC–DC converters. Control Eng. Pract. 2019, 90, 148–159. [Google Scholar] [CrossRef]

- Hu, R.; Yan, Z.; Wang, L.; Wong, M.C.; Zeng, J.; Liu, J.; Hu, B. An Interleaved Bidirectional Coupled-Inductor Based DC–DC Converter with High Conversion Ratio for Energy Storage System. IEEE Trans. Ind. Electron. 2021, 69, 5648–5659. [Google Scholar] [CrossRef]

- Alghaythi, M.L.; O’Connell, R.M.; Islam, N.E.; Khan, M.M.S.; Guerrero, J.M. A high step-up interleaved DC-DC converter with voltage multiplier and coupled inductors for renewable energy systems. IEEE Access 2020, 8, 123165–123174. [Google Scholar] [CrossRef]

- Ni, L.; Patterson, D.J.; Hudgins, J.L. High power current sensorless bidirectional 16-phase interleaved DC-DC converter for hybrid vehicle application. IEEE Trans. Power Electron. 2011, 27, 1141–1151. [Google Scholar] [CrossRef]

- Alzahrani, A.; Ferdowsi, M.; Shamsi, P. A family of scalable non-isolated interleaved DC-DC boost converters with voltage multiplier cells. IEEE Access 2019, 7, 11707–11721. [Google Scholar] [CrossRef]

- Kabalo, M.; Paire, D.; Blunier, B.; Bouquain, D.; Simoes, M.G.; Miraoui, A. Experimental validation of high-voltage-ratio low-input-current-ripple converters for hybrid fuel cell supercapacitor systems. IEEE Trans. Veh. Technol. 2012, 61, 3430–3440. [Google Scholar] [CrossRef]

- Mayer, R.; El Kattel, M.B.; Oliveira, S.V.G. Multiphase interleaved bidirectional DC/DC converter with coupled inductor for electrified-vehicle applications. IEEE Trans. Power Electron. 2020, 36, 2533–2547. [Google Scholar] [CrossRef]

- Yan, H.; Xu, Y.; Zou, J.; Wang, B.; Jiang, S. A maximum current sharing method for dual-redundancy brushless DC Motor control. In Proceedings of the 17th International Conference on Electrical Machines and Systems (ICEMS), Hangzhou, China, 22–25 October 2014; pp. 1057–1061. [Google Scholar] [CrossRef]

- Gu, L.; Li, P. Hybrid PWM Control of Bidirectional DC/DC Resonant Converter for Low-Current-Ripple and Wide-Voltage-Gain Application. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 2158–2162. [Google Scholar] [CrossRef]

- Chakraborty, S.; Hasan, M.M.; McGahan, P.; Tran, D.D.; Geury, T.; Davari, P.; Blaabjerg, F.; EI Baghdadi, M.; Hegazy, O. Real-life mission profile oriented lifetime estimation of a SiC interleaved bidirectional HV DC/DC converter for electric vehicle drivetrains. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5142–5167. [Google Scholar] [CrossRef]

- Elserougi, A.; Abdelsalam, I.; Massoud, A.; Ahmed, S. A non-isolated hybrid-modular DC-DC converter for DC grids: Small-signal modeling and control. IEEE Access 2019, 7, 132459–132471. [Google Scholar] [CrossRef]

- Ayachit, A.; Kazimierczuk, M.K. Averaged small-signal model of PWM DC-DC converters in CCM including switching power loss. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 262–266. [Google Scholar] [CrossRef]

- Alvarez-Ramirez, J.; Cervantes, I.; Espinosa-Perez, G.; Maya, P.; Morales, A. A stable design of PI control for DC-DC converters with an RHS zero. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2001, 48, 103–106. [Google Scholar] [CrossRef]

| Range of Duty Cycles | Number of Parallel Multiplicities |

|---|---|

| 0.1000~0.1835 | 6 |

| 0.1835~0.2254 | 5 |

| 0.2254~0.2887 | 4 |

| 0.2887~0.3675 | 6 |

| 0.3675~0.4772 | 5 |

| 0.4772~0.5528 | 6 |

| 0.5528~0.6324 | 5 |

| 0.6324~0.7113 | 6 |

| 0.7113~0.7746 | 4 |

| 0.7746~0.8165 | 5 |

| 0.8165~0.9000 | 6 |

| Parameter | Value |

|---|---|

| DC voltage VDC | 30 V |

| Switching period TS | 0.0001 s (10 kHz) |

| Inductance L | 3 mH |

| Inductance resistance R | 0.1 |

| Load capacitance C | 0.06 F |

| Initial voltage of load capacitor | 5 V |

| Load current ILoad | 6 A |

| Maximum number of parallel channels | 6 |

| Duty Cycles | The Maximum Current Ripple of the Number of N Multiple Parallel Channels/mA | The Number of Parallel Channels to Be Used | ||

|---|---|---|---|---|

| N = 4 | N = 5 | N = 6 | ||

| 0.25 | 80 | 100 | 120 | 4 |

| 0.33 | 160 | 145 | 65 | 6 |

| 0.40 | 200 | 90 | 100 | 5 |

| 0.50 | 130 | 140 | 120 | 6 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Duan, J.; Wang, S.; Xu, Y.; Fan, S.; Zhao, K.; Sun, L. Variable Multiple Interleaved Bi-Directional DC/DC Converter with Current Ripple Optimization. Appl. Sci. 2023, 13, 1744. https://doi.org/10.3390/app13031744

Duan J, Wang S, Xu Y, Fan S, Zhao K, Sun L. Variable Multiple Interleaved Bi-Directional DC/DC Converter with Current Ripple Optimization. Applied Sciences. 2023; 13(3):1744. https://doi.org/10.3390/app13031744

Chicago/Turabian StyleDuan, Jiandong, Shuai Wang, Yiming Xu, Shaogui Fan, Ke Zhao, and Li Sun. 2023. "Variable Multiple Interleaved Bi-Directional DC/DC Converter with Current Ripple Optimization" Applied Sciences 13, no. 3: 1744. https://doi.org/10.3390/app13031744

APA StyleDuan, J., Wang, S., Xu, Y., Fan, S., Zhao, K., & Sun, L. (2023). Variable Multiple Interleaved Bi-Directional DC/DC Converter with Current Ripple Optimization. Applied Sciences, 13(3), 1744. https://doi.org/10.3390/app13031744