Design Techniques for Low-Voltage RF/mm-Wave Circuits in Nanometer CMOS Technologies

Abstract

:1. Introduction

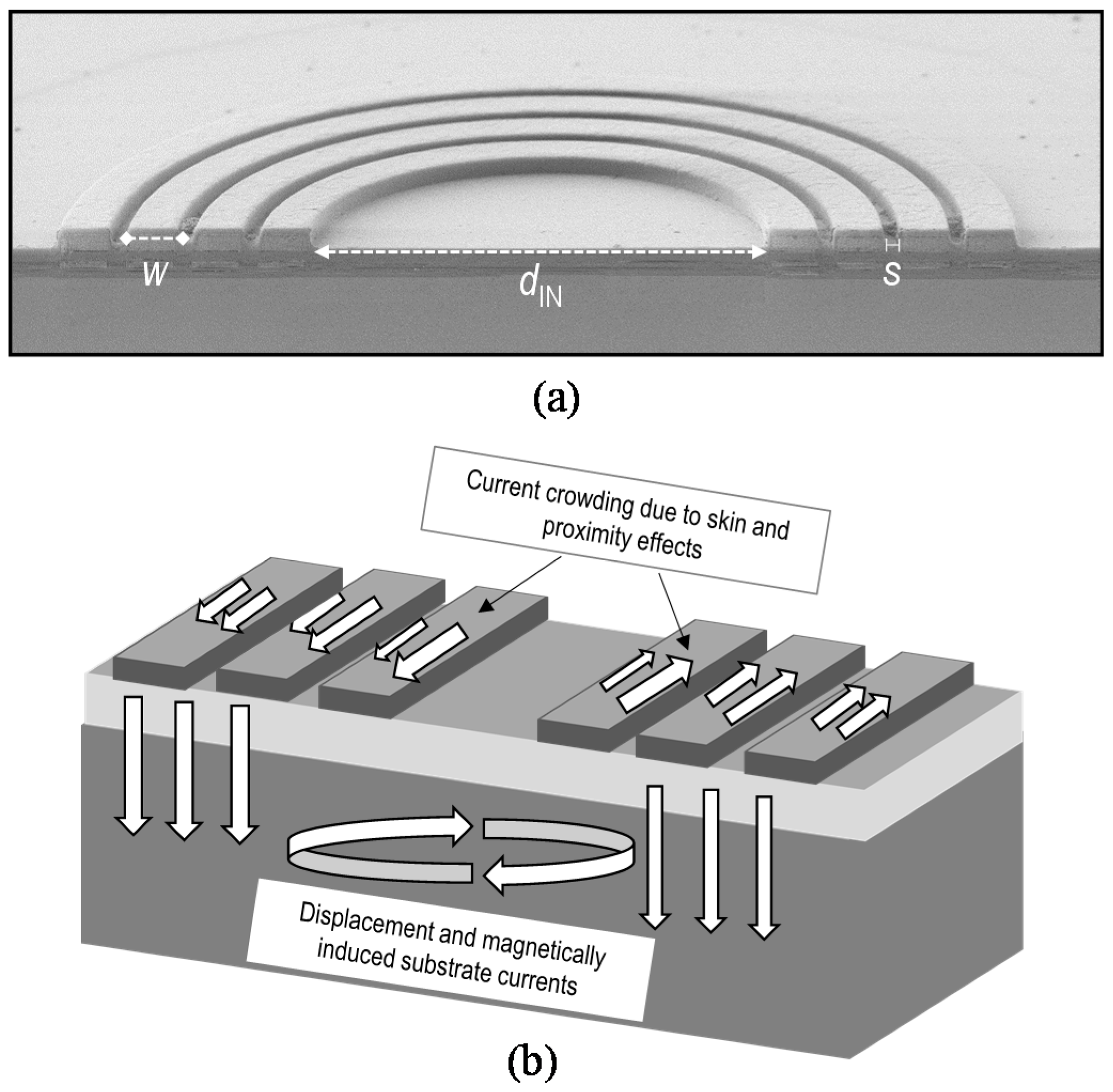

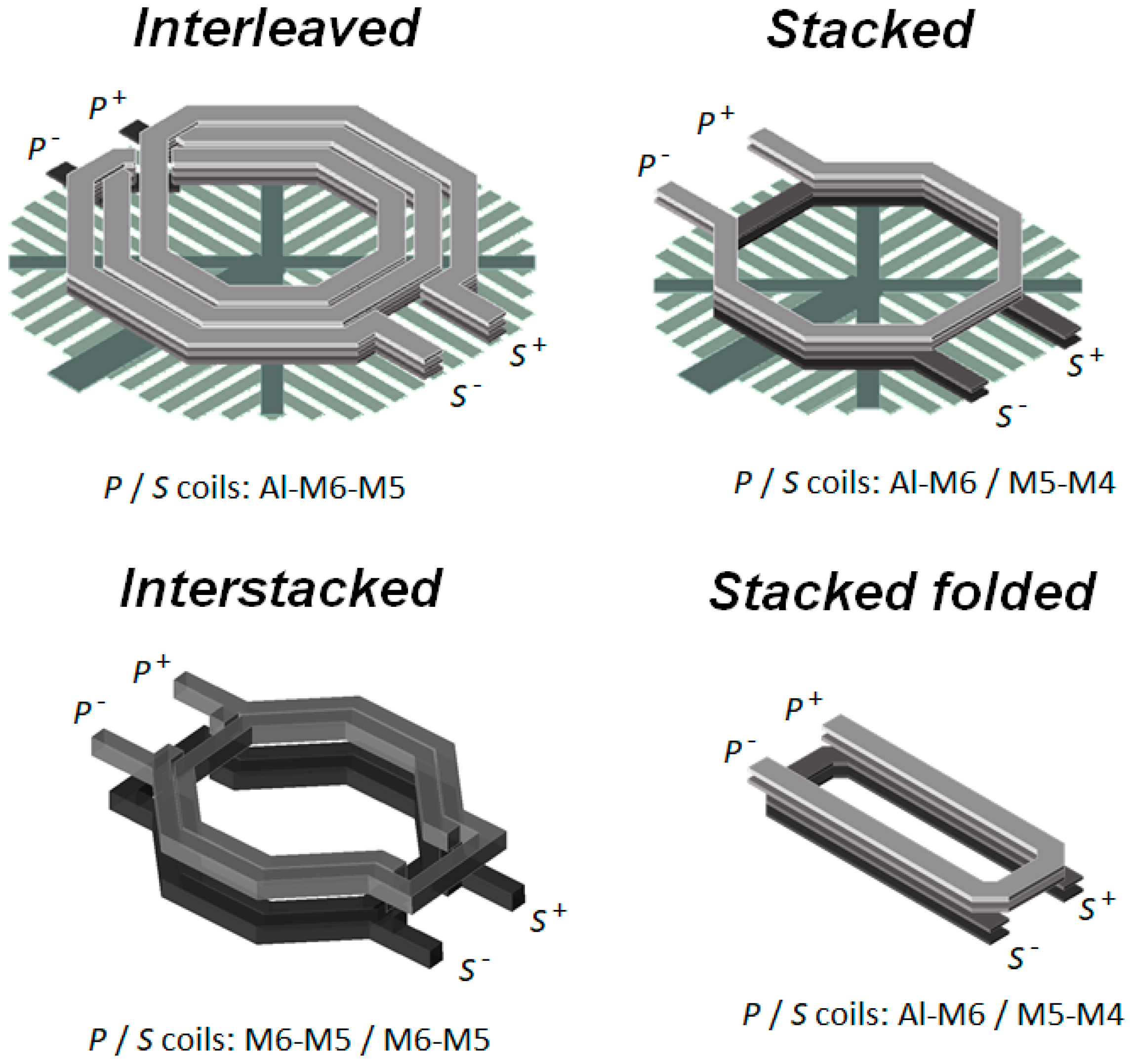

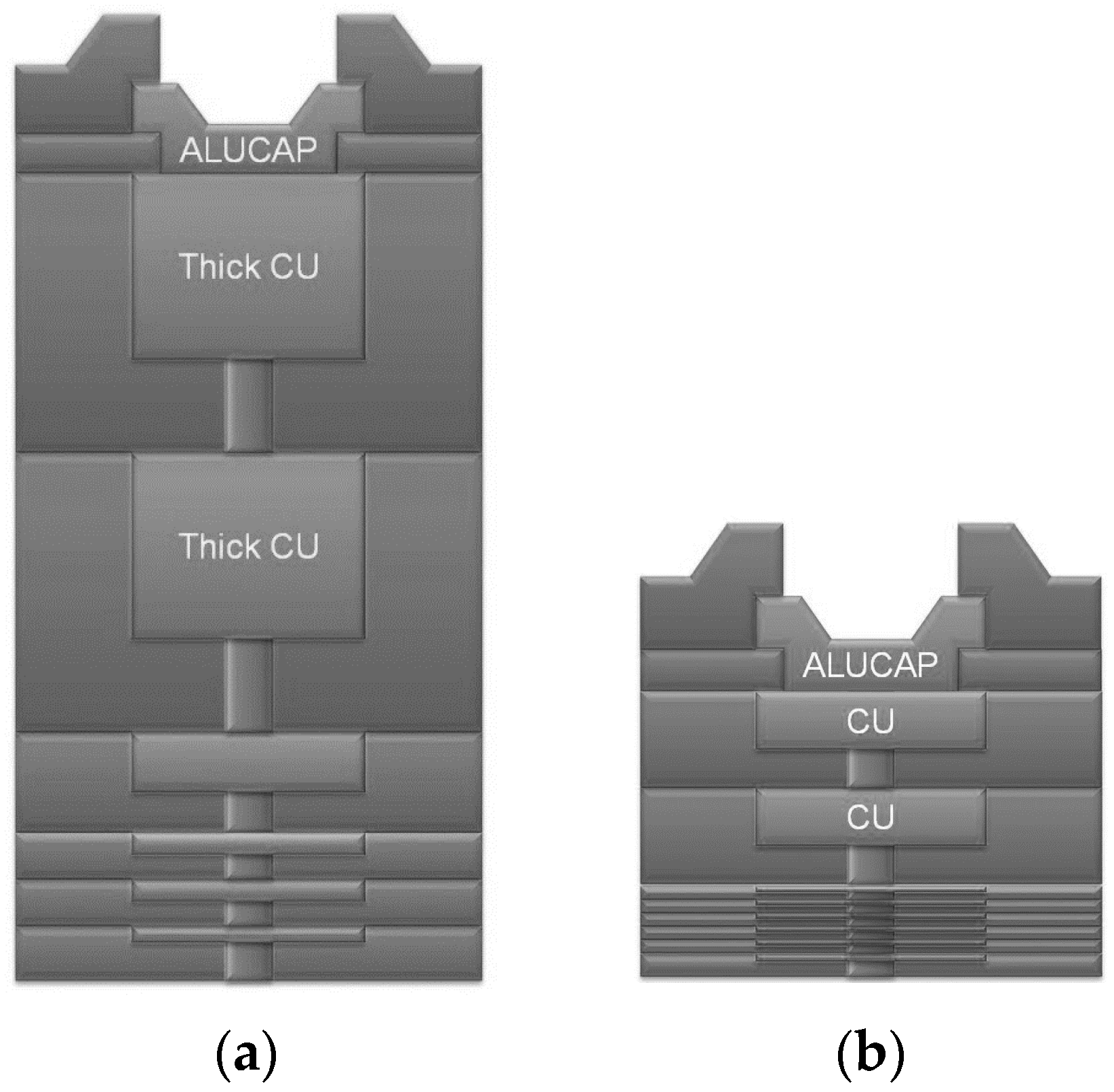

2. Integrated Inductive Components: Loss Phenomena and Main Design Guidelines

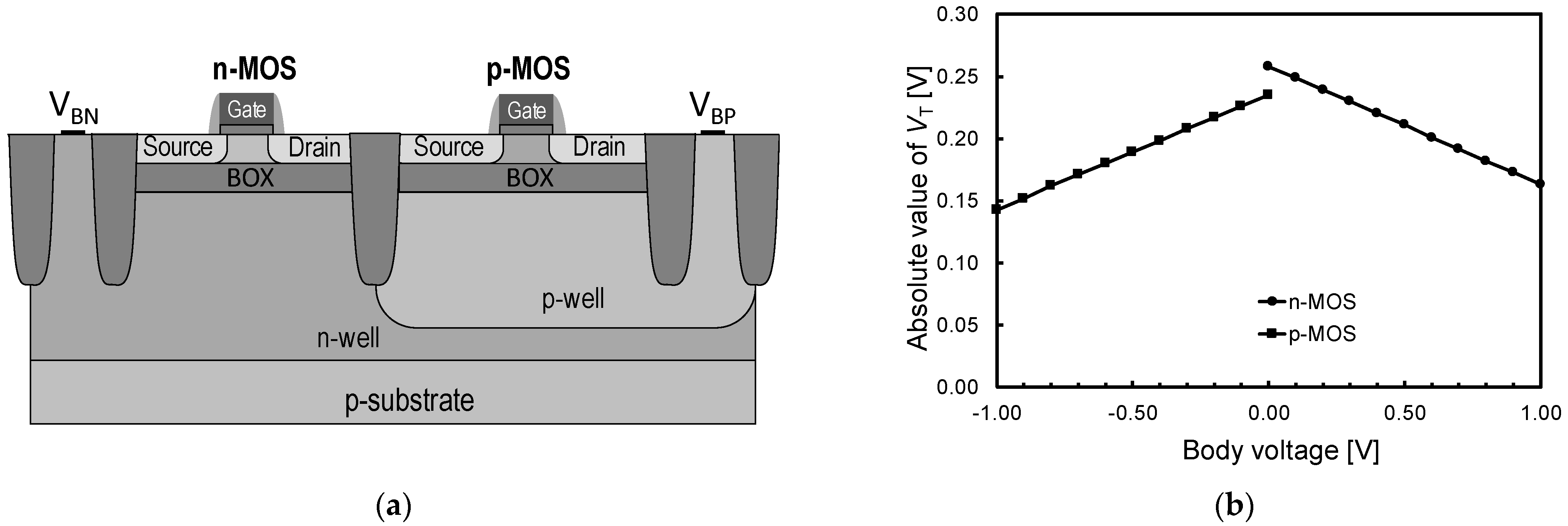

3. The Body Biasing Technique

4. Circuit Topologies for Low-Voltage Operation of RF/mm-Wave Blocks

- ▪

- Reduce the operative threshold voltage, VT;

- ▪

- Increase the transconductance, gm, by means of positive feedback;

- ▪

- Use only one transistor between the supply voltage, VDD, and ground;

- ▪

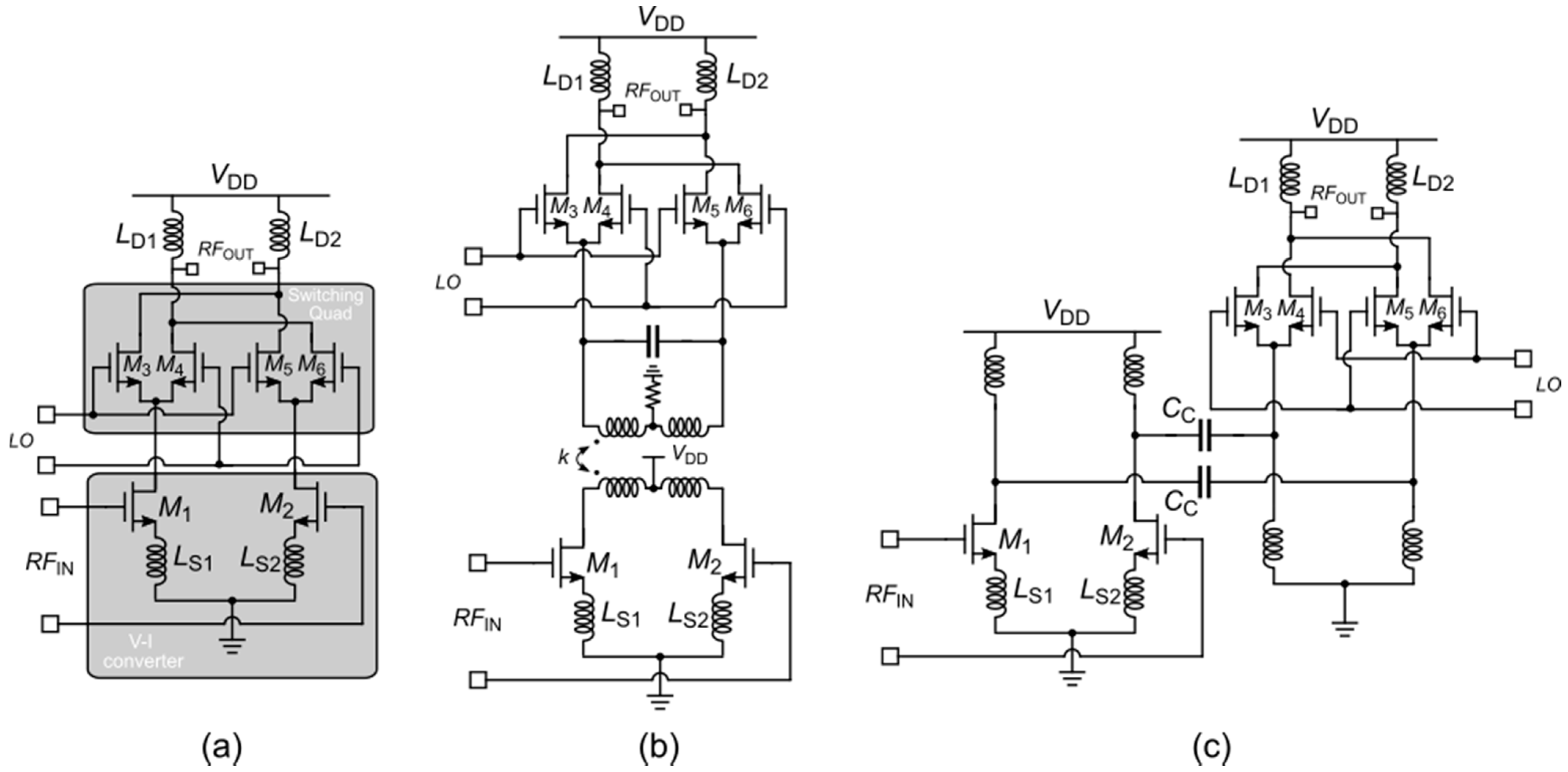

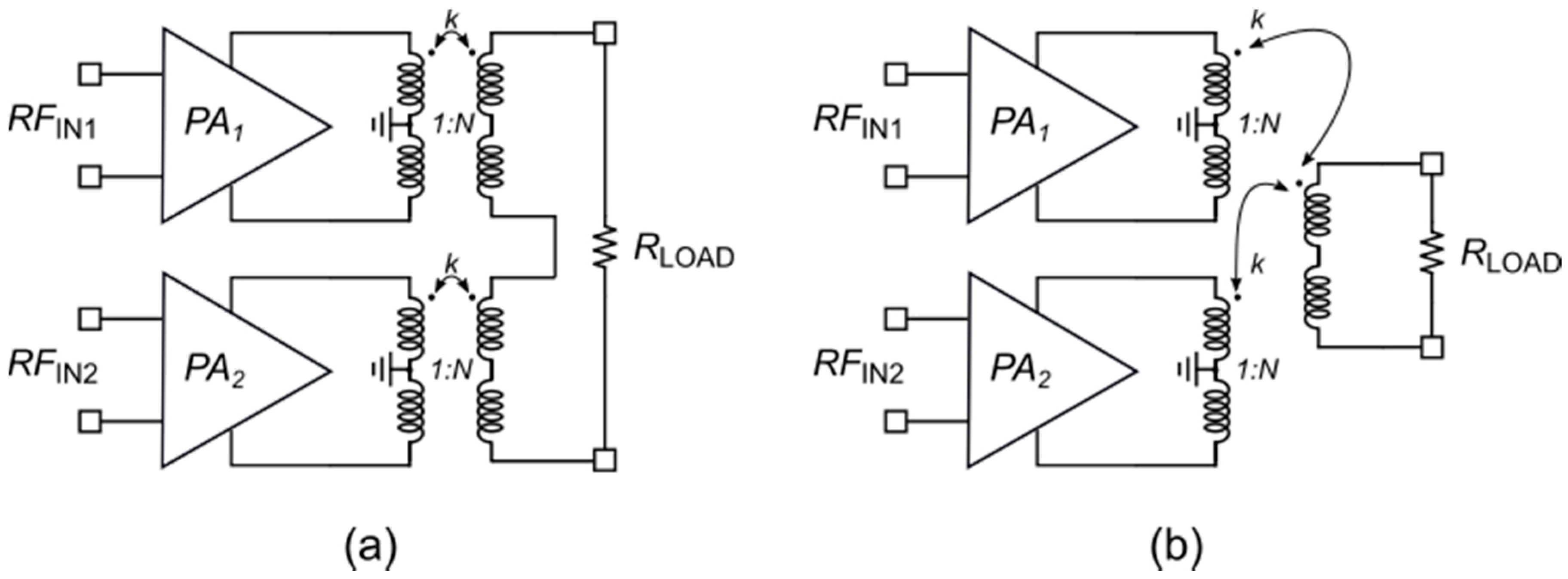

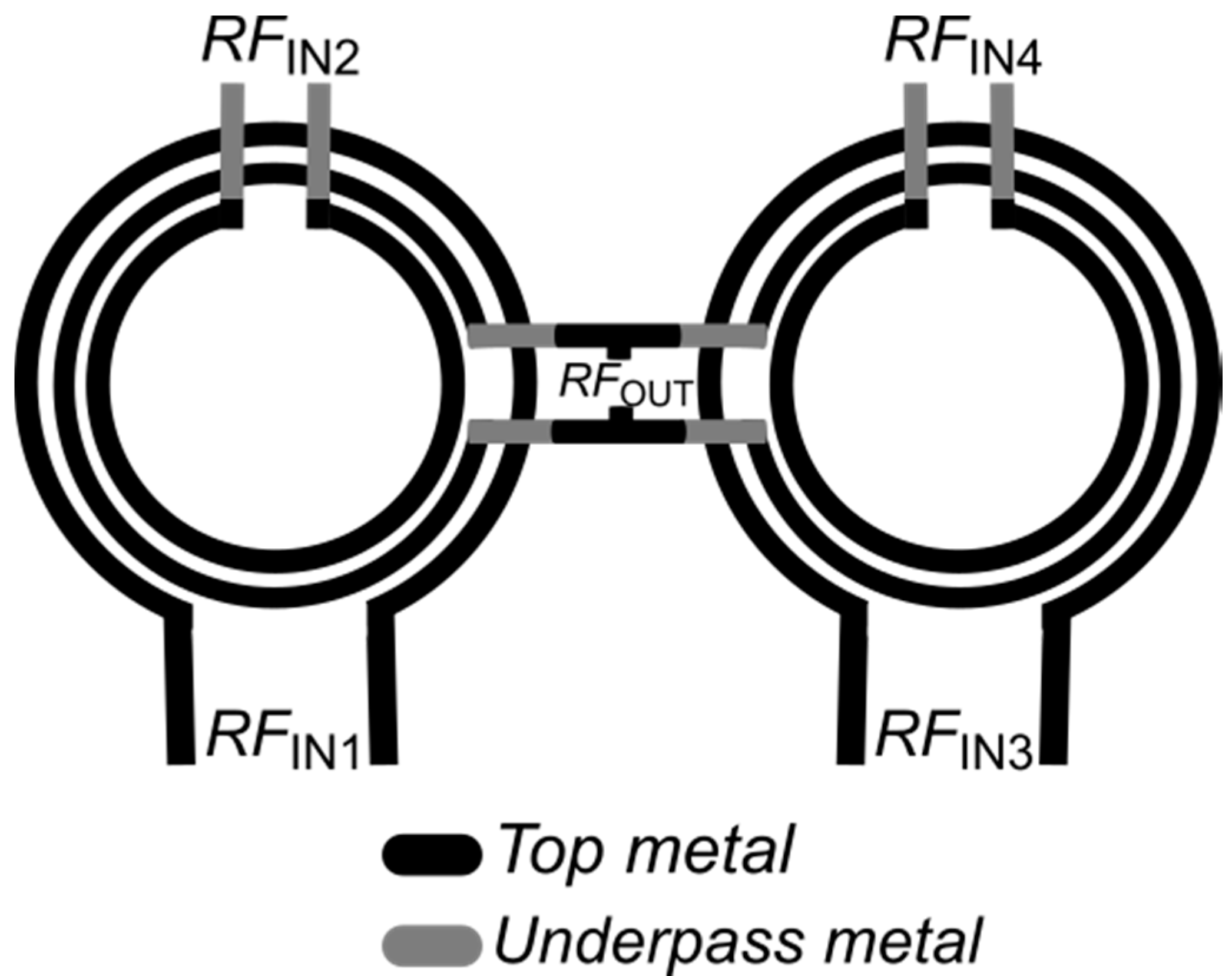

- Adopt transformer-based power combining techniques.

- ▪

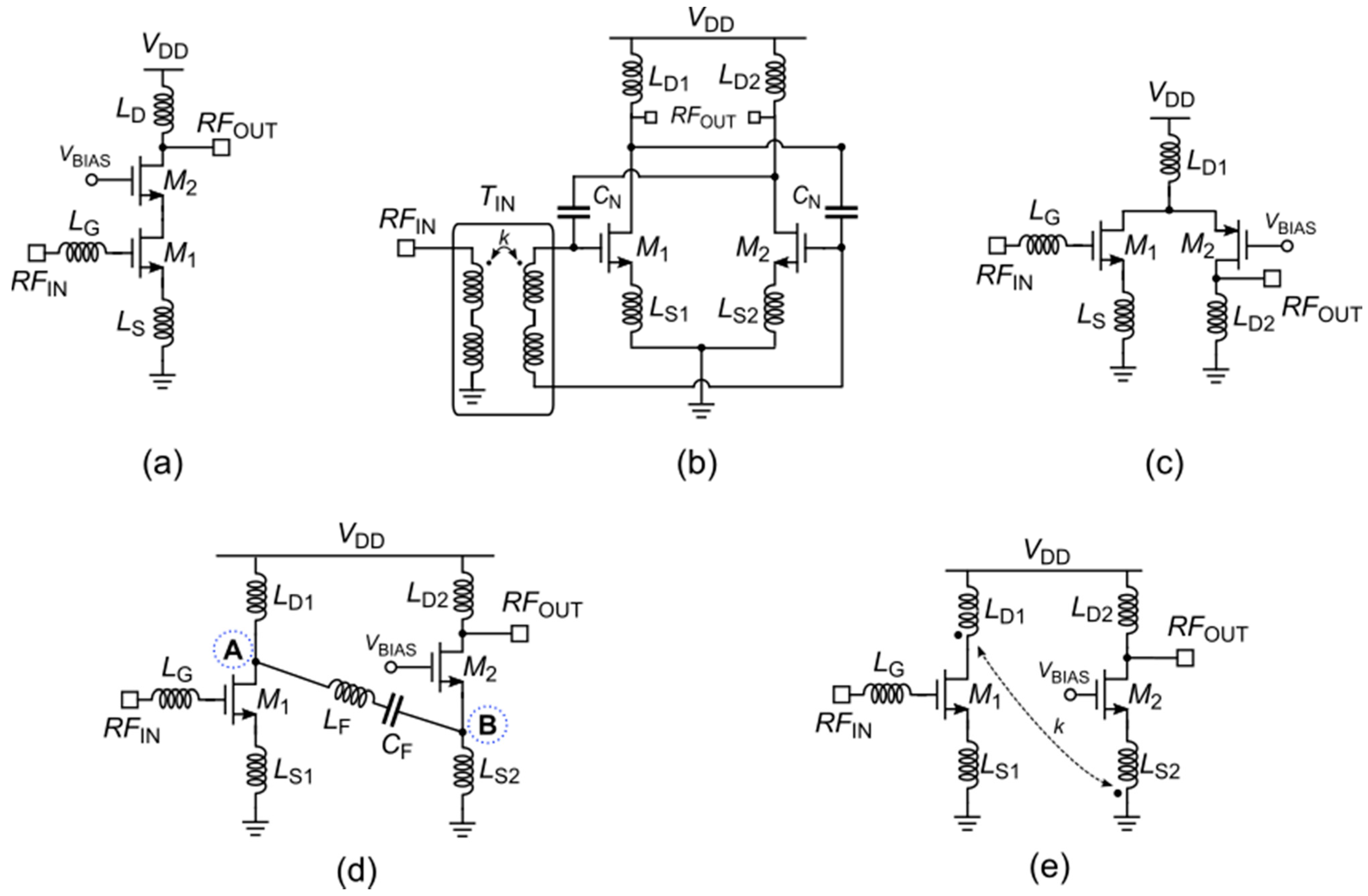

- Neutralized common source (CS) topology;

- ▪

- Folded cascode topology;

- ▪

- Reactive resonant coupling: capacitive coupling;

- ▪

- Reactive resonant coupling: transformer coupling.

- ▪

- Implement single-ended-to-differential and differential-to-single-ended conversions, providing inherent virtual ground for differential operations;

- ▪

- Transform impedance for impedance matching and output power matching;

- ▪

- Provide simple DC biasing of power devices via the center tap, avoiding the use of RF chokes and DC blocks.

5. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Joseph, A.; Jain, V.; Ong, S.N.; Wolf, R.; Lim, S.F.; Singh, J. Technology Positioning for Mm Wave Applications: 130/90nm SiGe BiCMOS vs. 28nm RFCMOS. In Proceedings of the 2018 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), San Diego, CA, USA, 15–17 October 2018; pp. 18–21. [Google Scholar]

- Cathelin, A. Fully Depleted Silicon on Insulator Devices CMOS: The 28-Nm Node Is the Perfect Technology for Analog, RF, MmW, and Mixed-Signal System-on-Chip Integration. IEEE Solid-State Circuits Mag. 2017, 9, 18–26. [Google Scholar] [CrossRef]

- Girlando, G.; Ragonese, E.; Palmisano, G. Silicon Bipolar LNAs in the X and Ku Bands. Analog. Integr. Circuits Signal Process. 2004, 41, 119–127. [Google Scholar] [CrossRef]

- Ragonese, E.; Scuderi, A.; Giammello, V.; Palmisano, G. A SiGe BiCMOS 24-GHz Receiver Front-End for Automotive Short-Range Radar. Analog. Integr. Circuits Signal Process. 2011, 67, 121–130. [Google Scholar] [CrossRef]

- Sapone, G.; Ragonese, E.; Italia, A.; Palmisano, G. A 0.13-µm SiGe BiCMOS Colpitts-Based VCO for W-Band Radar Transmitters. IEEE Trans. Microw. Theory Tech. 2013, 61, 185–194. [Google Scholar] [CrossRef]

- Giammello, V.; Ragonese, E.; Palmisano, G. A Transformer-Coupling Current-Reuse SiGe HBT Power Amplifier for 77-GHz Automotive Radar. IEEE Trans. Microw. Theory Tech. 2012, 60, 1676–1683. [Google Scholar] [CrossRef]

- Giammello, V.; Ragonese, E.; Palmisano, G. A 24/77-GHz SiGe BiCMOS Transmitter Chipset for Automotive Radar. Microw. Opt. Technol. Lett. 2013, 55, 782–786. [Google Scholar] [CrossRef]

- Scuderi, A.; Ragonese, E.; Biondi, T.; Palmisano, G. Integrated Inductors and Transformers: Characterization, Design and Modeling for RF and mm-Wave Applications; CRC Press: Boca Raton, FL, USA, 2010. [Google Scholar]

- Spataro, S.; Ragonese, E. Design and Optimization of Silicon-Integrated Inductive Components for Automotive Radar Applications in K- and W-Bands. In Proceedings of the 2020 AEIT International Conference of Electrical and Electronic Technologies for Automotive (AEIT AUTOMOTIVE), Turin, Italy, 18–20 November 2020; pp. 1–6. [Google Scholar]

- Craninckx, J.; Steyaert, M.S.J. A 1.8-GHz Low-Phase-Noise CMOS VCO Using Optimized Hollow Spiral Inductors. IEEE J. Solid-State Circuits 1997, 32, 736–744. [Google Scholar] [CrossRef] [Green Version]

- Yim, S.M.; Chen, T. The Effects of a Ground Shield on the Characteristics and Performance of Spiral Inductors. IEEE J. Solid-State Circuits 2002, 37, 237–244. [Google Scholar] [CrossRef]

- Spataro, S.; Salerno, N.; Papotto, G.; Ragonese, E. The Effect of a Metal PGS on the Q-Factor of Spiral Inductors for RF and mm-Wave Applications in a 28-nm CMOS Technology. Int. J. RF Microw. Comput.-Aided Eng. 2020, 30, e22368. [Google Scholar] [CrossRef]

- Bevilacqua, A. Fundamentals of Integrated Transformers: From Principles to Applications. IEEE Solid-State Circuits Mag. 2020, 12, 86–100. [Google Scholar] [CrossRef]

- Ragonese, E.; Sapone, G.; Palmisano, G. High-Performance Interstacked Transformers for mm-Wave ICs. Microw. Opt. Technol. Lett. 2010, 52, 2160–2163. [Google Scholar] [CrossRef]

- Ragonese, E.; Sapone, G.; Giammello, V.; Palmisano, G. Analysis and Modeling of Interstacked Transformers for Mm-Wave Applications. Analog. Integr. Circuits Signal Process. 2012, 72, 121–128. [Google Scholar] [CrossRef]

- Giammello, V.; Ragonese, E.; Palmisano, G. A 77-GHz PA with Ground-Plane Parasitic Cancellation in a SiGe HBT BiCMOS Technology. Microw. Opt. Technol. Lett. 2011, 53, 1413–1416. [Google Scholar] [CrossRef]

- Avenier, G.; Diop, M.; Chevalier, P.; Troillard, G.; Loubet, N.; Bouvier, J.; Depoyan, L.; Derrier, N.; Buczko, M.; Leyris, C.; et al. 0.13 m SiGe BiCMOS Technology Fully Dedicated to mm-Wave Applications. IEEE J. Solid State Circuits 2009, 44, 2312–2321. [Google Scholar] [CrossRef]

- Ragonese, E.; Nocera, C.; Cavarra, A.; Papotto, G.; Spataro, S.; Palmisano, G. A Comparative Analysis between Standard and mm-Wave Optimized BEOL in a Nanoscale CMOS Technology. Electronics 2020, 9, 2124. [Google Scholar] [CrossRef]

- Lin, W.; Tsai, J.; Jen, Y.; Huang, T.; Wang, H. A 0.7-V 60-GHz Low-Power LNA with Forward Body Bias Technique in 90 nm CMOS Process. In Proceedings of the 2009 European Microwave Conference (EuMC), Rome, Italy, 29 September–1 October 2009; pp. 393–396. [Google Scholar]

- Dehqan, A.; Kargaran, E.; Mafinezhad, K.; Nabovati, H. Design of 0.45V, 1.3mW Ultra High Gain CMOS LNA Using Gm-Boosting and Forward Body Biasing Technique. In Proceedings of the 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWSCAS), Boise, ID, USA, 5–8 August 2012; pp. 722–725. [Google Scholar]

- Chou, H.; Ke, Z.; Chiou, H. A Low Power Compact Size Forward Body-Biased K-Band CMOS Low Noise Amplifier. In Proceedings of the Asia-Pacific Microwave Conference 2011, Melbourne, VIC, Australia, 5–8 December 2011; pp. 494–497. [Google Scholar]

- Parvizi, M.; Allidina, K.; El-Gamal, M.N. Short Channel Output Conductance Enhancement through Forward Body Biasing to Realize a 0.5 V 250 μW 0.6–4.2 GHz Current-Reuse CMOS LNA. IEEE J. Solid-State Circuits 2016, 51, 574–586. [Google Scholar] [CrossRef]

- Tochou, G.; Cathelin, A.; Frappé, A.; Kaiser, A.; Rabaey, J. Impact of Forward Body-Biasing on Ultra-Low Voltage Switched-Capacitor RF Power Amplifier in 28 nm FD-SOI. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 50–54. [Google Scholar] [CrossRef]

- Kane, O.M.; Lucci, L.; Scheiblin, P.; Poiroux, T.; Barbé, J.-C.; Danneville, F. Back Gate Impact on the Noise Performances of 22FDX Fully-Depleted SOI CMOS. In Proceedings of the 2020 15th European Microwave Integrated Circuits Conference (EuMIC), Utrecht, The Netherlands, 10–15 January 2021; pp. 81–84. [Google Scholar]

- Finocchiaro, A.; Papotto, G.; Ragonese, E.; Palmisano, G. A 28-nm FD-SOI CMOS Variable-Gain Amplifier with Body-Bias-Based DC-Offset Cancellation for Automotive Radars. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1693–1697. [Google Scholar] [CrossRef]

- El-Aassar, O.; Rebeiz, G.M. Design of Low-Power Sub-2.4 dB Mean NF 5G LNAs Using Forward Body Bias in 22 nm FDSOI. IEEE Trans. Microw. Theory Tech. 2020, 68, 4445–4454. [Google Scholar] [CrossRef]

- Justo, D.; Cavalheiro, D.; Moll, F. Body Bias Generators for Ultra Low Voltage Circuits in FDSOI Technology. In Proceedings of the 2017 32nd Conference on Design of Circuits and Integrated Systems (DCIS), Barcelona, Spain, 22–24 November 2017; pp. 1–6. [Google Scholar]

- Wang, L.; Wu, C.; Feng, L.; Chang, A.; Lian, Y. A Low-Power Forward and Reverse Body Bias Generator in CMOS 40 nm. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 1403–1407. [Google Scholar] [CrossRef]

- Gomez, R.; Dutto, C.; Huard, V.; Clerc, S.; Bano, E.; Flatresse, P. Design Methodology with Body Bias: From Circuit to Engineering. In Proceedings of the 2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Burlingame, CA, USA, 16–19 October 2017; pp. 1–4. [Google Scholar]

- de Streel, G.; Stas, F.; Gurné, T.; Durant, F.; Frenkel, C.; Cathelin, A.; Bol, D. SleepTalker: A ULV 802.15.4a IR-UWB Transmitter SoC in 28-nm FDSOI Achieving 14 PJ/b at 27 Mb/s With Channel Selection Based on Adaptive FBB and Digitally Programmable Pulse Shaping. IEEE J. Solid-State Circuits 2017, 52, 1163–1177. [Google Scholar] [CrossRef]

- Kihara, T.; Park, H.-J.; Takobe, I.; Yamashita, F.; Matsuoka, T.; Taniguchi, K. A 0.5 V Area-Efficient Transformer Folded-Cascode Low-Noise Amplifier in 90 nm CMOS. In Proceedings of the 2008 IEEE International Conference on Integrated Circuit Design and Technology and Tutorial, Grenoble, France, 2–4 June 2008; pp. 21–24. [Google Scholar]

- Kundu, S.; Khairi, A.; Paramesh, J. A Supply-Voltage Scalable, 45 nm CMOS Ultra-Wideband Receiver for mm-Wave Ranging and Communication. In Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012; pp. 1–4. [Google Scholar]

- Lin, Y.-H.; Hsiao, S.-C.; Tsai, J.-H.; Huang, T.-W. A 0.7-mW V-Band Transformer-Based Positive- Feedback Receiver Front-End in a 65-nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 613–616. [Google Scholar] [CrossRef]

- Liang, C.-J.; Chiang, C.-W.; Zhou, J.; Huang, R.; Wen, K.-A.; Chang, M.-C.F.; Kuan, Y.-C. A 0.6-V VDD W-Band Neutralized Differential Low Noise Amplifier in 28-nm Bulk CMOS. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 481–484. [Google Scholar] [CrossRef]

- Asada, H.; Matsushita, K.; Bunsen, K.; Okada, K.; Matsuzawa, A. A 60GHz CMOS Power Amplifier Using Capacitive Cross-Coupling Neutralization with 16% PAE. In Proceedings of the 2011 41st European Microwave Conference, Manchester, UK, 10–11 October 2011; pp. 1115–1118. [Google Scholar]

- Chen, L.; Zhang, L.; Wang, Y.; Yu, Z. A Compact E-Band Power Amplifier with Gain-Boosting and Efficiency Enhancement. IEEE Trans. Microw. Theory Tech. 2020, 68, 4620–4630. [Google Scholar] [CrossRef]

- Nocera, C.; Papotto, G.; Cavarra, A.; Ragonese, E.; Palmisano, G. A 13.5-dBm 1-V Power Amplifier for W-Band Automotive Radar Applications in 28-Nm FD-SOI CMOS Technology. IEEE Trans. Microw. Theory Tech. 2021, 69, 1654–1660. [Google Scholar] [CrossRef]

- Kargaran, E.; Nabovati, G.; Mafinezhad, K.; Nabovati, H. An Ultra Low Voltage Ultra Low Power Folded Cascode CMOS LNA Using Forward Body Bias Technology for GPS Application. In Proceedings of the 2011 19th Iranian Conference on Electrical Engineering, Tehran, Iran, 17–19 May 2011; pp. 1–11. [Google Scholar]

- Manku, T.; Beck, G.; Shin, E.J. A Low-Voltage Design Technique for RF Integrated Circuits. IEEE Trans. Circuits Syst. II Analog. Digit. Signal Process. 1998, 45, 1408–1413. [Google Scholar] [CrossRef]

- Giammello, V.; Ragonese, E.; Palmisano, G. Transformer-Coupled Cascode Stage for mm-Wave Power Amplifiers in Sub-mm CMOS Technology. Analog. Integr. Circuits Signal Process. 2011, 66, 449–453. [Google Scholar] [CrossRef]

- Hanay, O.; Negra, R. 0.33 mm2 13.3 dB Gain Sub-6 GHz to 28 GHz Transformer-Coupled Low-Voltage Upconversion Mixer for 5G Applications. In Proceedings of the ESSCIRC 2021—IEEE 47th European Solid State Circuits Conference (ESSCIRC), Grenoble, France, 13–22 September 2021; pp. 373–376. [Google Scholar]

- Nocera, C.; Cavarra, A.; Ragonese, E.; Palmisano, G.; Papotto, G. Down-Converter Solutions for 77-GHz Automotive Radar Sensors in 28-Nm FD-SOI CMOS Technology. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018; pp. 153–156. [Google Scholar]

- Papotto, G.; Nocera, C.; Finocchiaro, A.; Parisi, A.; Cavarra, A.; Castorina, A.; Ragonese, E.; Palmisano, G. A 27-mW W-Band Radar Receiver with Effective TX Leakage Suppression in 28-nm FD-SOI CMOS. IEEE Trans. Microw. Theory Tech. 2021, 69, 4132–4141. [Google Scholar] [CrossRef]

- Kim, Y.; Kwon, Y. Analysis and Design of Millimeter-Wave Power Amplifier Using Stacked-FET Structure. IEEE Trans. Microw. Theory Tech. 2015, 63, 691–702. [Google Scholar] [CrossRef]

- Manente, D.; Padovan, F.; Seebacher, D.; Bassi, M.; Bevilacqua, A. A 28-GHz Stacked Power Amplifier with 20.7-dBm Output P1dB in 28-nm Bulk CMOS. IEEE Solid-State Circuits Lett. 2020, 3, 170–173. [Google Scholar] [CrossRef]

- Niknejad, A.M.; Chowdhury, D. Transforming RF and mm-Wave CMOS Circuits. In Proceedings of the 2009 International Symposium on VLSI Design, Automation and Test, Hsinchu, Taiwan, 28–30 April 2009; pp. 138–141. [Google Scholar]

- Zhou, P.; Chen, J.; Hong, W.; Gao, H. A 77-GHz Fully Integrated Power Amplifier for Automotive Radar Application in 40-nm CMOS. In Proceedings of the 2021 IEEE MTT-S International Wireless Symposium (IWS), Nanjing, China, 23–26 May 2021; pp. 1–3. [Google Scholar]

- An, K.H.; Lee, O.; Kim, H.; Lee, N.H.; Han, J.; Yang, K.S.; Kim, Y.; Chang, J.J.; Woo, W.; Lee, C.-H.; et al. Power-Combining Transformer Techniques for Fully-Integrated CMOS Power Amplifiers. IEEE J. Solid State Circuits 2008, 43, 1064–1075. [Google Scholar] [CrossRef]

- Sandstrom, D.; Martineau, B.; Varonen, M.; Karkkainen, M.; Cathelin, A.; Halonen, K.A.I. 94 GHz power-combining power amplifier with +13 dBm saturated output power in 65 nm CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symp, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar]

- Gu, Q.J.; Xu, Z.; Chang, M.F. Two-Way Current-Combining W-Band Power Amplifier in 65-Nm CMOS. IEEE Trans. Microw. Theory Tech. 2012, 60, 1365–1374. [Google Scholar] [CrossRef]

- Comeau, J.P.; Thoenes, E.W.; Imhoff, A.; Morton, M.A. X-Band +24 dBm CMOS Power Amplifier with Transformer Power Combining. In Proceedings of the 2011 IEEE 11th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Glendale, AZ, USA, 17–19 January 2011; pp. 49–52. [Google Scholar]

- Chen, J.; Niknejad, A.M. A Compact 1V 18.6dBm 60GHz Power Amplifier in 65nm CMOS. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 432–433. [Google Scholar]

- Trinh, V.-S.; Park, J.-D. A 25.1 dBm 25.9-dB Gain 25.4% PAE X-Band Power Amplifier Utilizing Voltage Combining Transformer in 65-nm CMOS. IEEE Access 2021, 9, 6513–6521. [Google Scholar] [CrossRef]

- Li, S.; Rebeiz, G.M. A 130–151 GHz 8-Way Power Amplifier with 16.8–17.5 dBm Psat and 11.7–13.4% PAE Using CMOS 45 nm RFSOI. In Proceedings of the 2021 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Atlanta, GA, USA, 7–9 June 2021; pp. 115–118. [Google Scholar]

- Trinh, V.-S.; Park, J.-D. An 85-GHz Power Amplifier Utilizing a Transformer-Based Power Combiner Operating Beyond the Self-Resonance Frequency. IEEE J. Solid-State Circuits 2021, 1. [Google Scholar] [CrossRef]

- Yang, B.; Qian, H.J.; Wang, T.; Luo, X. 1.2–3.6 GHz 32.67 dBm 4096-QAM Digital PA Using Reconfigurable Power Combining Transformer for Wireless Communication. In Proceedings of the 2020 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Los Angeles, CA, USA, 4–6 August 2020; pp. 123–126. [Google Scholar]

| Inductor Parameters | Peak Q-Factor (QMAX) | Low-Frequency Inductance (LDC) | Self-Resonance Frequency (SRF) | |

|---|---|---|---|---|

| Number of turns, n | ▲ | ▼ | ▲ | ▼ |

| Metal width, w | ▲ | ▲ | ▼ | ▼ |

| Metal spacing, s | ▲ | ▼ | ▼ | ▼ |

| Fill ratio, ρ | ▲ | ▲▼ | ▲▼ | ▼ |

| Metal thickness, t | ▲ | ▲ | ▼ | ▲ |

| Oxide thickness tox | ▲ | ▲ | — | ▲ |

| Substrate resistivity, ρSI | ▲ | ▲ | ▲ | ▲ |

| Performance Parameters | Transformer Structures | |||

|---|---|---|---|---|

| Interleaved | Stacked | Interstacked | Stacked Folded | |

| Magnetic coupling factor, k | + | ++ | +++ | ++ |

| Winding Q-factors | +++ | + | ++ | + |

| Self-resonance frequency (SRF) | +++ | + | + | ++ |

| Turn ratio, N | ++ | + | - | - |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ragonese, E. Design Techniques for Low-Voltage RF/mm-Wave Circuits in Nanometer CMOS Technologies. Appl. Sci. 2022, 12, 2103. https://doi.org/10.3390/app12042103

Ragonese E. Design Techniques for Low-Voltage RF/mm-Wave Circuits in Nanometer CMOS Technologies. Applied Sciences. 2022; 12(4):2103. https://doi.org/10.3390/app12042103

Chicago/Turabian StyleRagonese, Egidio. 2022. "Design Techniques for Low-Voltage RF/mm-Wave Circuits in Nanometer CMOS Technologies" Applied Sciences 12, no. 4: 2103. https://doi.org/10.3390/app12042103

APA StyleRagonese, E. (2022). Design Techniques for Low-Voltage RF/mm-Wave Circuits in Nanometer CMOS Technologies. Applied Sciences, 12(4), 2103. https://doi.org/10.3390/app12042103