Improvement of Heat Transfer Properties through TiO2 Nanosphere Monolayer Embedded Polymers as Thermal Interface Materials

Abstract

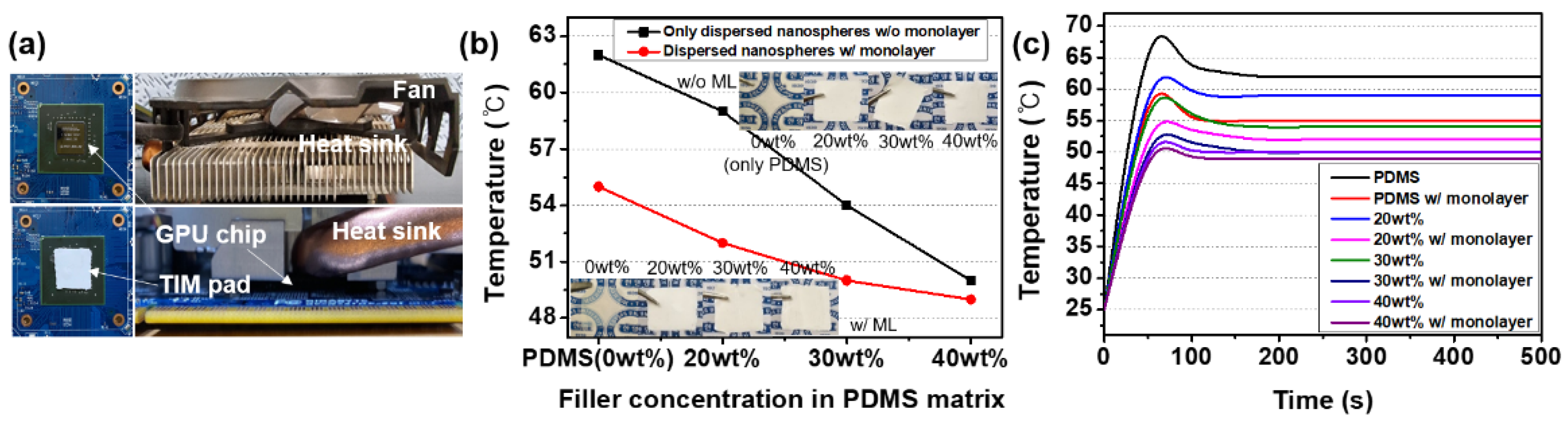

:1. Introduction

2. Materials and Methods

2.1. Materials

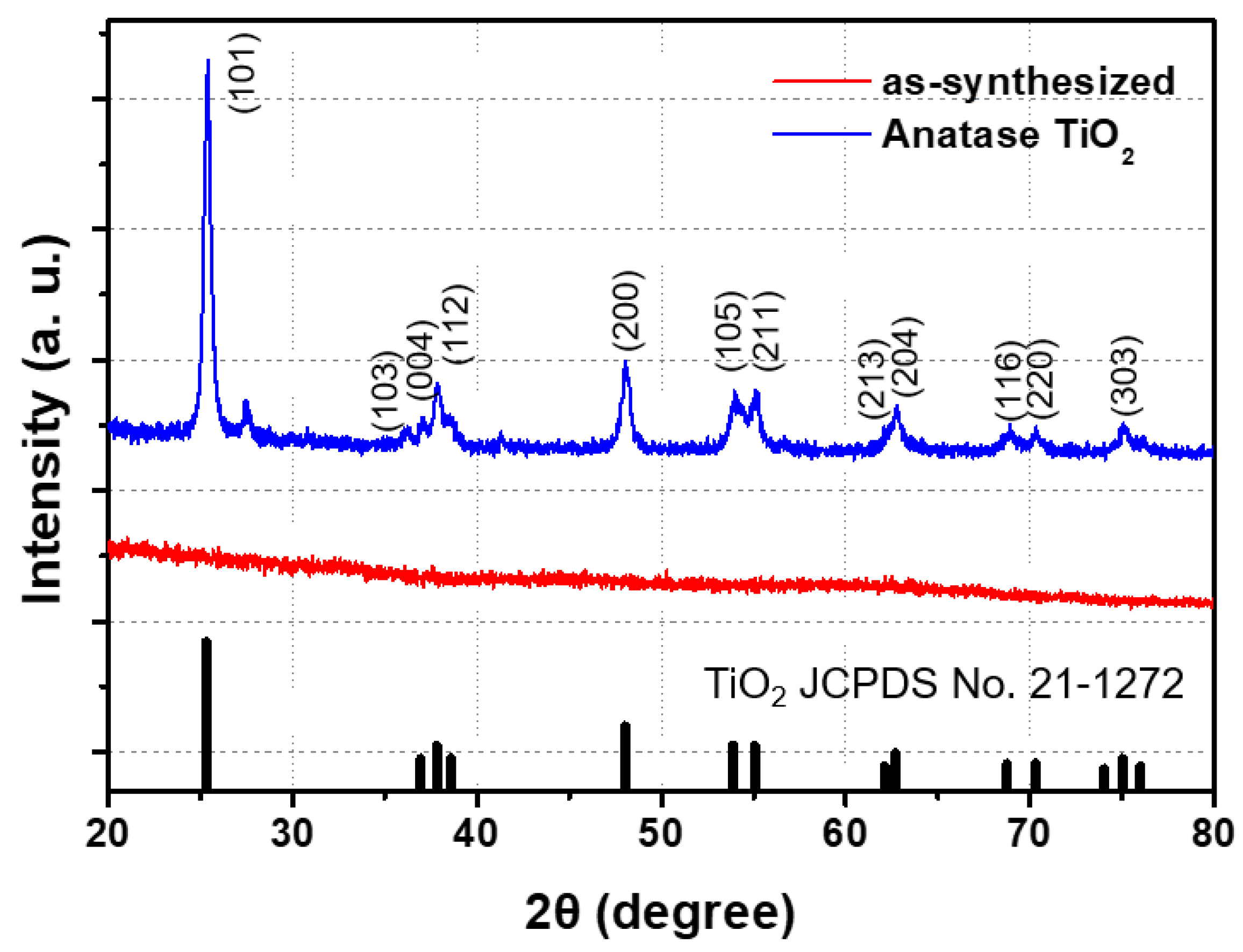

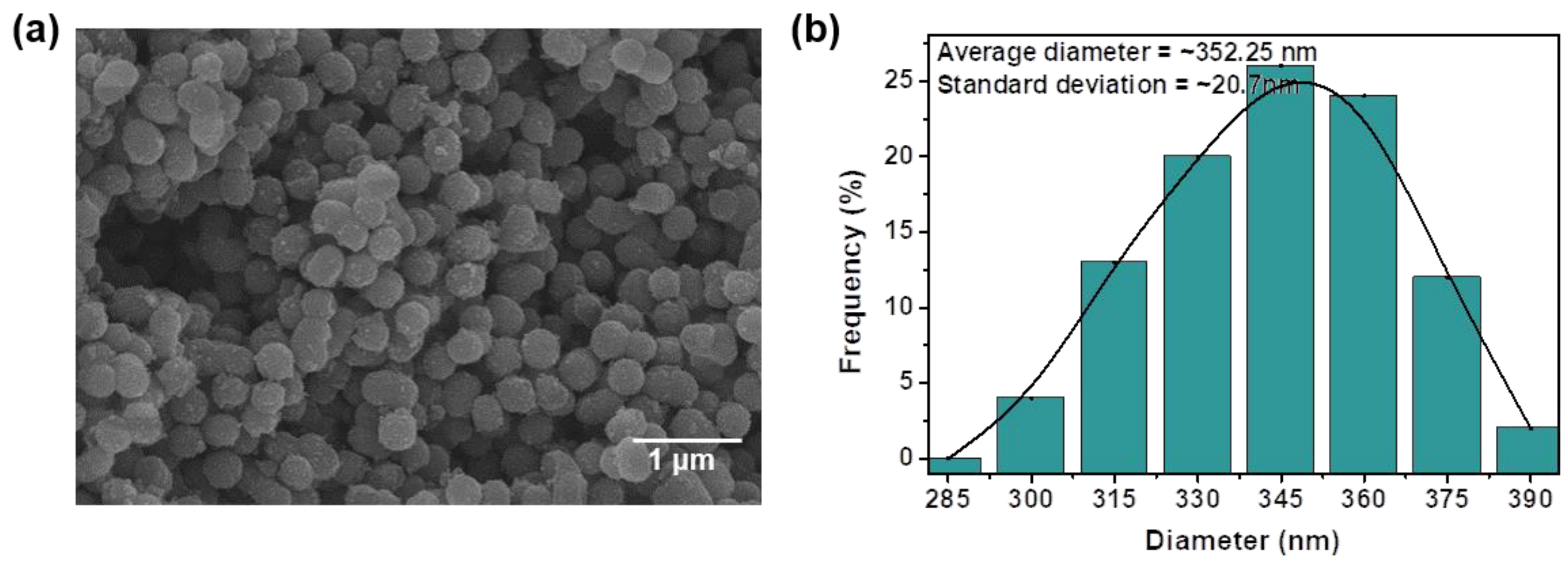

2.2. Synthesis of TiO2 NSs

2.3. Characterization

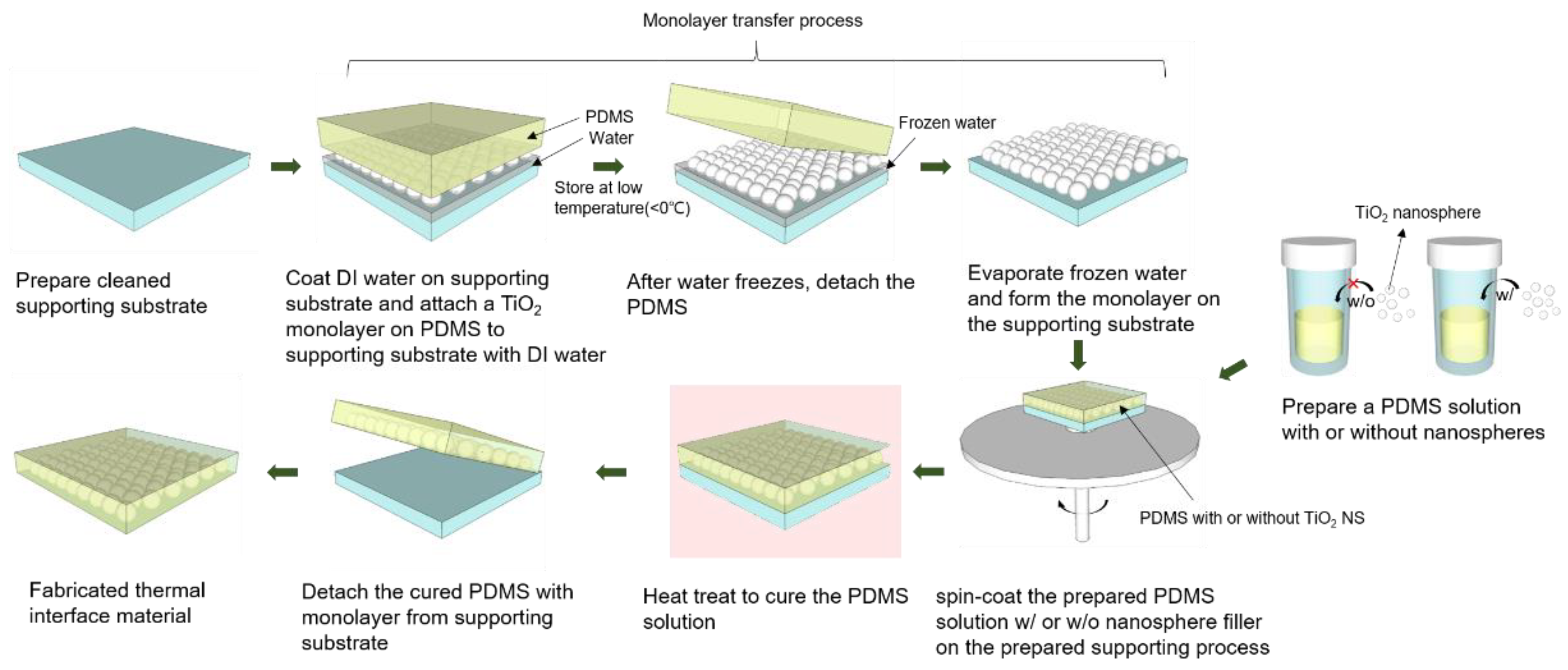

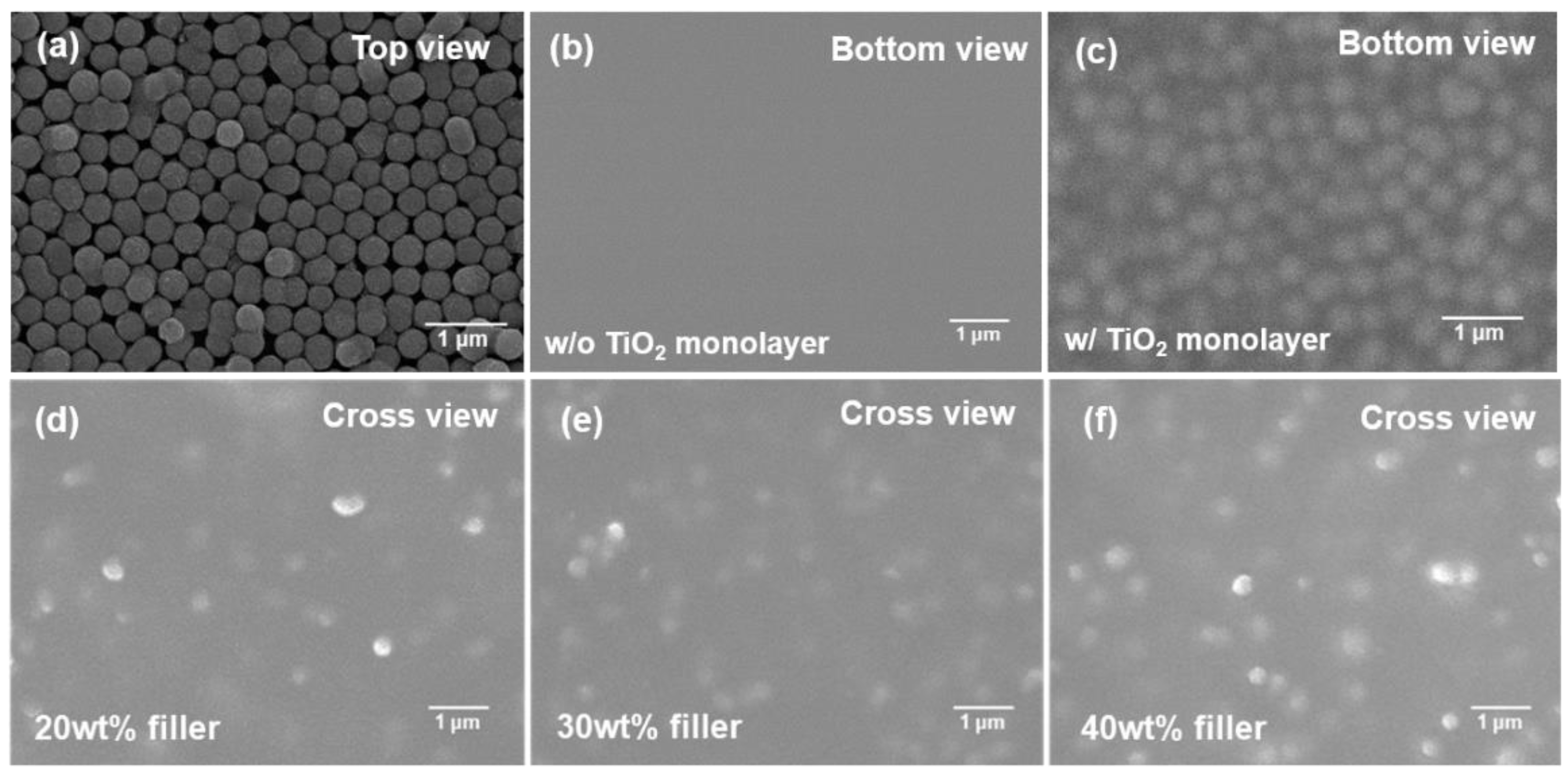

2.4. TIM Fabrication Process

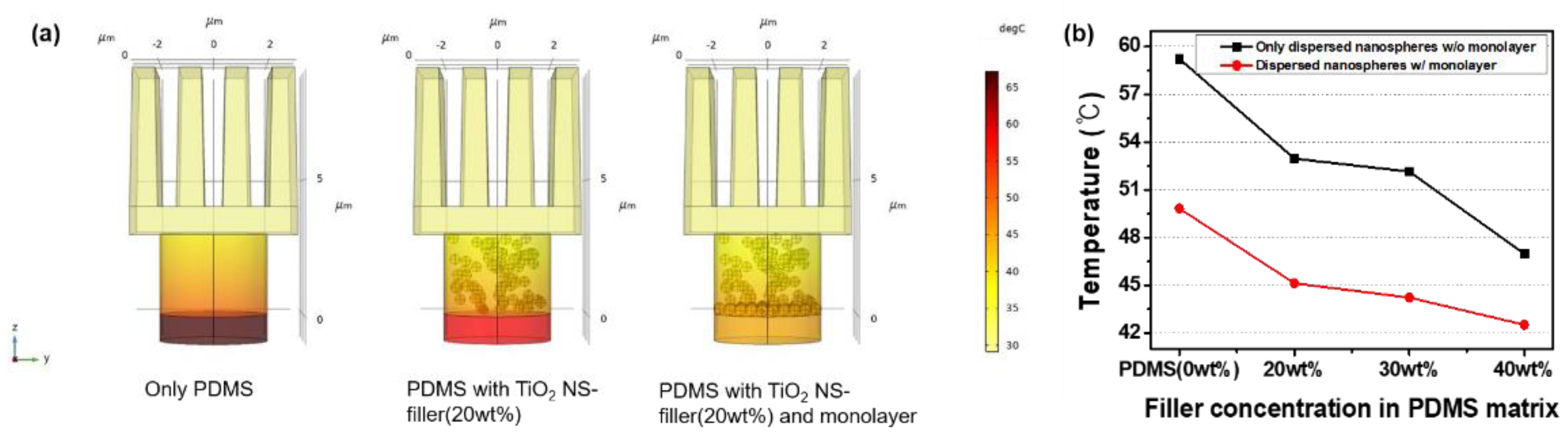

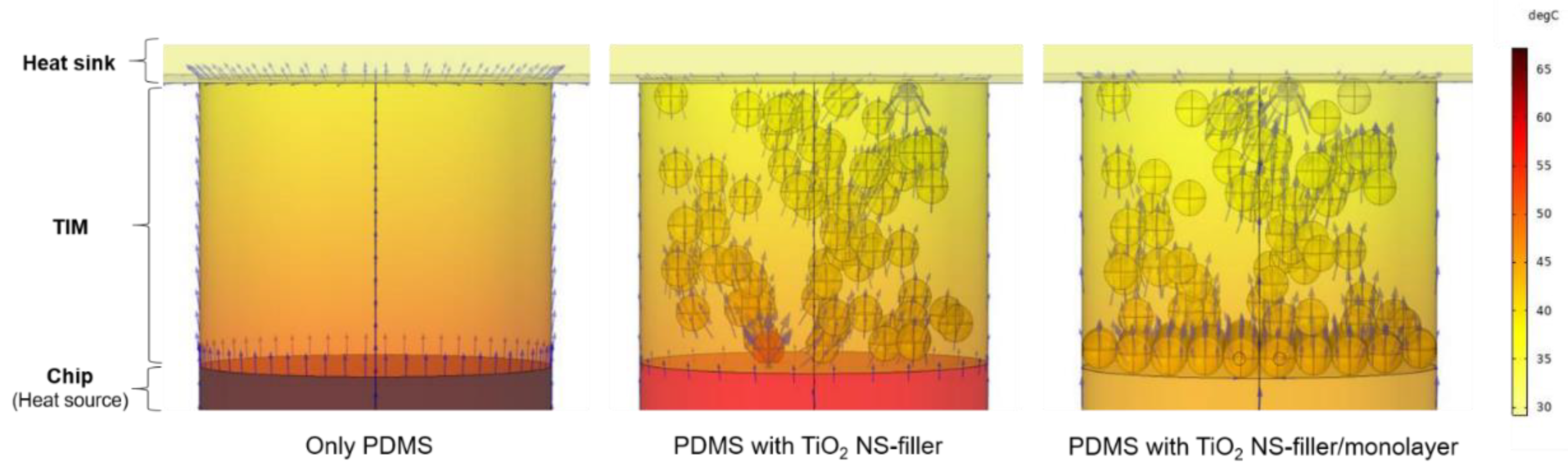

2.5. Simulation

2.6. Measurement and Analysis Conditions

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Waldrop, M.M. The chips are down for Moore’s law. Nat. News 2016, 530, 144. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Moore, A.L.; Shi, L. Emerging challenges and materials for thermal management of electronics. Mater. Today 2014, 17, 163–174. [Google Scholar] [CrossRef]

- Chen, H.; Ginzburg, V.V.; Yang, J.; Yang, Y.; Liu, W.; Huang, Y.; Du, L.; Chen, B. Thermal conductivity of polymer-based composites: Fundamentals and applications. Prog. Polym. Sci. 2016, 59, 41–85. [Google Scholar] [CrossRef]

- Chung, D. Thermal interface materials. J. Mater. Eng. Perform. 2001, 10, 56–59. [Google Scholar] [CrossRef]

- Prasher, R. Thermal interface materials: Historical perspective, status, and future directions. Proc. IEEE 2006, 94, 1571–1586. [Google Scholar] [CrossRef]

- Zhou, Y.; Wu, S.; Long, Y.; Zhu, P.; Wu, F.; Liu, F.; Murugadoss, V.; Winchester, W.; Nautiyal, A.; Wang, Z. Recent advances in thermal interface materials. ES Mater. Manuf. 2020, 7, 4–24. [Google Scholar] [CrossRef]

- Zhang, Y.; Ma, J.; Wei, N.; Yang, J.; Pei, Q.-X. Recent progress in the development of thermal interface materials: A review. Phys. Chem. Chem. Phys. 2021, 23, 753–776. [Google Scholar] [CrossRef]

- Razeeb, K.M.; Dalton, E.; Cross, G.L.W.; Robinson, A.J. Present and future thermal interface materials for electronic devices. Int. Mater. Rev. 2018, 63, 1–21. [Google Scholar] [CrossRef]

- Ma, H.; Gao, B.; Wang, M.; Yuan, Z.; Shen, J.; Zhao, J.; Feng, Y. Strategies for enhancing thermal conductivity of polymer-based thermal interface materials: A review. J. Mater. Sci. 2021, 56, 1064–1086. [Google Scholar] [CrossRef]

- Hansson, J.; Nilsson, T.M.; Ye, L.; Liu, J. Novel nanostructured thermal interface materials: A review. Int. Mater. Rev. 2018, 63, 22–45. [Google Scholar] [CrossRef]

- Tan, X.; Ying, J.; Gao, J.; Yan, Q.; Lv, L.; Nishimura, K.; Wei, Q.; Li, H.; Du, S.; Wu, B. Rational design of high-performance thermal interface materials based on gold-nanocap-modified vertically aligned graphene architecture. Compos. Commun. 2021, 24, 100621. [Google Scholar] [CrossRef]

- Zhao, M.; Feng, X.; Zhu, W.; Guo, W.; Wang, G.; Liu, Z.; Guo, Q.; Chen, D. 2D Graphene in Interface Engineering of 3D Graphene-Based Thermal Management. Phys. Status Solidi 2021, 218, 2000576. [Google Scholar] [CrossRef]

- Loeblein, M.; Tsang, S.H.; Pawlik, M.; Phua, E.J.R.; Yong, H.; Zhang, X.W.; Gan, C.L.; Teo, E.H.T. High-density 3D-boron nitride and 3D-graphene for high-performance nano–thermal interface material. ACS Nano 2017, 11, 2033–2044. [Google Scholar] [CrossRef] [PubMed]

- Song, Q.; Zhu, W.; Deng, Y.; Hai, F.; Wang, Y.; Guo, Z. Enhanced through-plane thermal conductivity and high electrical insulation of flexible composite films with aligned boron nitride for thermal interface material. Compos. Part A Appl. Sci. Manuf. 2019, 127, 105654. [Google Scholar] [CrossRef]

- Zhang, W.; Kong, Q.Q.; Tao, Z.; Wei, J.; Xie, L.; Cui, X.; Chen, C.M. 3D thermally cross-linked graphene aerogel–enhanced silicone rubber elastomer as thermal interface material. Adv. Mater. Interfaces 2019, 6, 1900147. [Google Scholar] [CrossRef]

- Ouyang, Y.; Bai, L.; Tian, H.; Li, X.; Yuan, F. Recent progress of thermal conductive ploymer composites: Al2O3 fillers, properties and applications. Compos. Part A Appl. Sci. Manuf. 2022, 152, 106685. [Google Scholar] [CrossRef]

- Ma, J.; Shang, T.; Ren, L.; Yao, Y.; Zhang, T.; Xie, J.; Zhang, B.; Zeng, X.; Sun, R.; Xu, J.-B. Through-plane assembly of carbon fibers into 3D skeleton achieving enhanced thermal conductivity of a thermal interface material. Chem. Eng. J. 2020, 380, 122550. [Google Scholar] [CrossRef]

- Tavman, I.; Turgut, A. An investigation on thermal conductivity and viscosity of water based nanofluids. In Microfluidics Based Microsystems; Springer: Dordrecht, The Netherlands, 2010; pp. 139–162. [Google Scholar]

- Dette, C.; Pérez-Osorio, M.A.; Kley, C.S.; Punke, P.; Patrick, C.E.; Jacobson, P.; Giustino, F.; Jung, S.J.; Kern, K. TiO2 anatase with a bandgap in the visible region. Nano Lett. 2014, 14, 6533–6538. [Google Scholar] [CrossRef]

- Yu, W.; Yuan, S.; Li, Y.; Zhang, Q.; Wang, H. Preparation of TiO2 nanoparticle/nanotube composites via a vapor hydrolysis method and their photocatalytic activities. Int. Sch. Res. Not. 2011, 2011, 582534. [Google Scholar] [CrossRef] [Green Version]

- Moon, J.T.; Lee, S.K.; Joo, J.B. Controllable one-pot synthesis of uniform colloidal TiO2 particles in a mixed solvent solution for photocatalysis. Beilstein J. Nanotechnol. 2018, 9, 1715–1727. [Google Scholar] [CrossRef] [Green Version]

- Yang, T.; Park, S.-j.; Kim, T.G.; Shin, D.S.; Park, J. Ultraviolet photodetector using pn junction formed by transferrable hollow n-TiO2 nano-spheres monolayer. Opt. Express 2017, 25, 30843–30850. [Google Scholar] [CrossRef] [PubMed]

- Dong, Y.; Fei, X.; Liu, Z.; Zhou, Y.; Cao, L. Synthesis and photocatalytic redox properties of anatase TiO2 single crystals. Appl. Surf. Sci. 2017, 394, 386–393. [Google Scholar] [CrossRef]

- Narumanchi, S.; Mihalic, M.; Kelly, K.; Eesley, G. Thermal interface materials for power electronics applications. In Proceedings of the 2008 11th Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems, Orlando, FL, USA, 28–31 May 2008; pp. 395–404. [Google Scholar]

- Swartz, E.; Pohl, R. Thermal resistance at interfaces. Appl. Phys. Lett. 1987, 51, 2200–2202. [Google Scholar] [CrossRef]

- Zhao, J.-W.; Zhao, R.; Huo, Y.-K.; Cheng, W.-L. Effects of surface roughness, temperature and pressure on interface thermal resistance of thermal interface materials. Int. J. Heat Mass Transf. 2019, 140, 705–716. [Google Scholar] [CrossRef]

- Xue, L.; Keblinski, P.; Phillpot, S.; Choi, S.-S.; Eastman, J. Two regimes of thermal resistance at a liquid–solid interface. J. Chem. Phys. 2003, 118, 337–339. [Google Scholar] [CrossRef]

- Maruyama, S.; Kimura, T. A study on thermal resistance over a solid-liquid interface by the molecular dynamics method. Therm. Sci. Eng 1999, 7, 63–68. [Google Scholar]

- Grujicic, M.; Zhao, C.; Dusel, E. The effect of thermal contact resistance on heat management in the electronic packaging. Appl. Surf. Sci. 2005, 246, 290–302. [Google Scholar] [CrossRef]

- Kumar, D.H.; Patel, H.E.; Kumar, V.R.; Sundararajan, T.; Pradeep, T.; Das, S.K. Model for heat conduction in nanofluids. Phys. Rev. Lett. 2004, 93, 144301. [Google Scholar] [CrossRef] [Green Version]

- Bergles, A.E. Recent developments in enhanced heat transfer. Heat Mass Transf. 2011, 47, 1001–1008. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Moon, J.; Jung, U.; Jung, B.; Park, J. Improvement of Heat Transfer Properties through TiO2 Nanosphere Monolayer Embedded Polymers as Thermal Interface Materials. Appl. Sci. 2022, 12, 1348. https://doi.org/10.3390/app12031348

Moon J, Jung U, Jung B, Park J. Improvement of Heat Transfer Properties through TiO2 Nanosphere Monolayer Embedded Polymers as Thermal Interface Materials. Applied Sciences. 2022; 12(3):1348. https://doi.org/10.3390/app12031348

Chicago/Turabian StyleMoon, Jinuk, Uijin Jung, Bomseumin Jung, and Jinsub Park. 2022. "Improvement of Heat Transfer Properties through TiO2 Nanosphere Monolayer Embedded Polymers as Thermal Interface Materials" Applied Sciences 12, no. 3: 1348. https://doi.org/10.3390/app12031348

APA StyleMoon, J., Jung, U., Jung, B., & Park, J. (2022). Improvement of Heat Transfer Properties through TiO2 Nanosphere Monolayer Embedded Polymers as Thermal Interface Materials. Applied Sciences, 12(3), 1348. https://doi.org/10.3390/app12031348