Towards Trust Hardware Deployment of Edge Computing: Mitigation of Hardware Trojans Based on Evolvable Hardware

Abstract

:1. Introduction

- It is the first time employing an EA-based mitigation method against HTs attack in PE of CGRA;

- A method to optimize the evolvable region is proposed for reducing the evolution time;

- The experimental results show the effectiveness of the proposed scheme for mitigating HT attacks and confirm that optimizing the evolvable region can accelerate the evolution efficiency at the edge.

2. Preliminaries

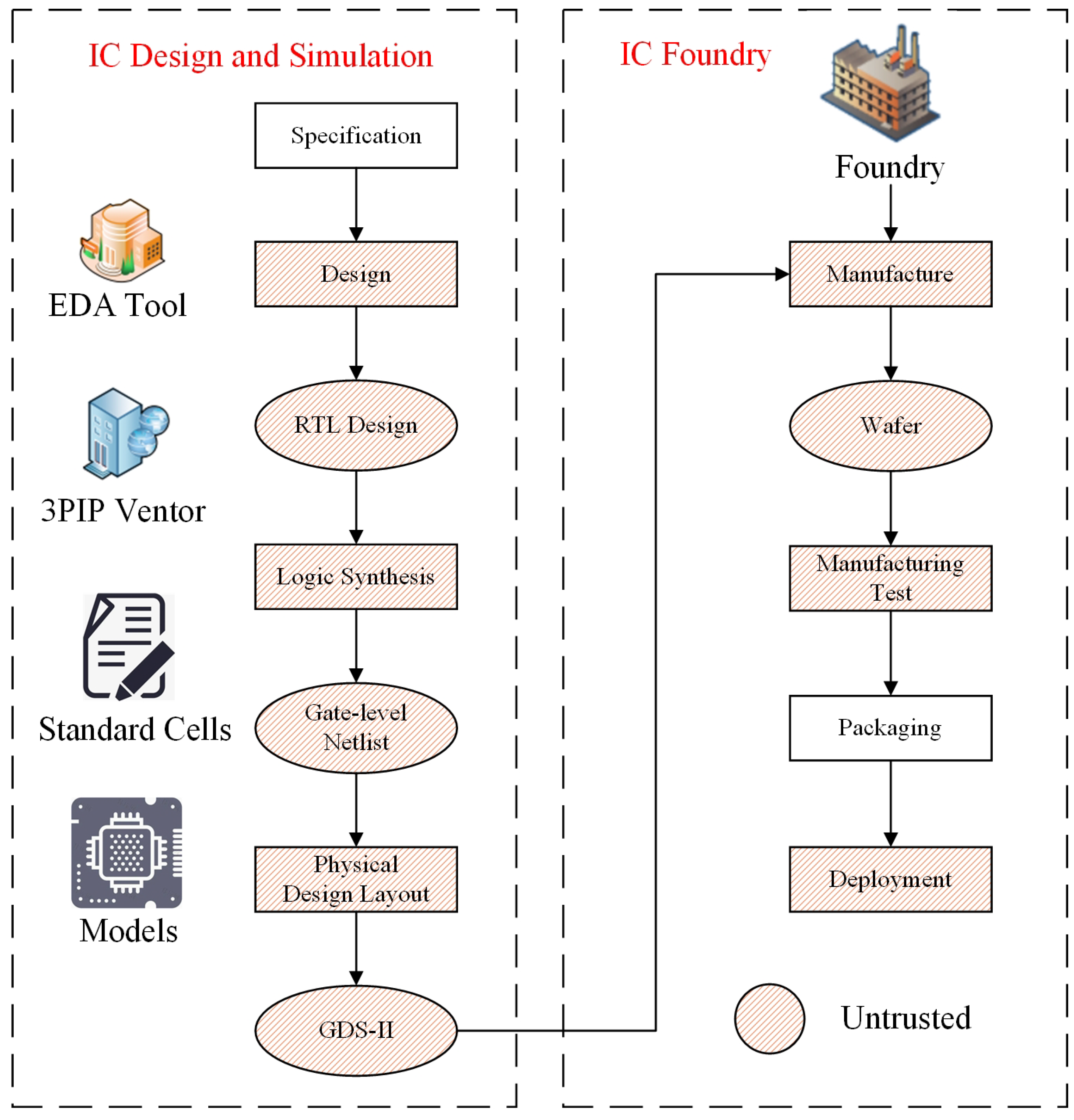

2.1. Hardware Trojans

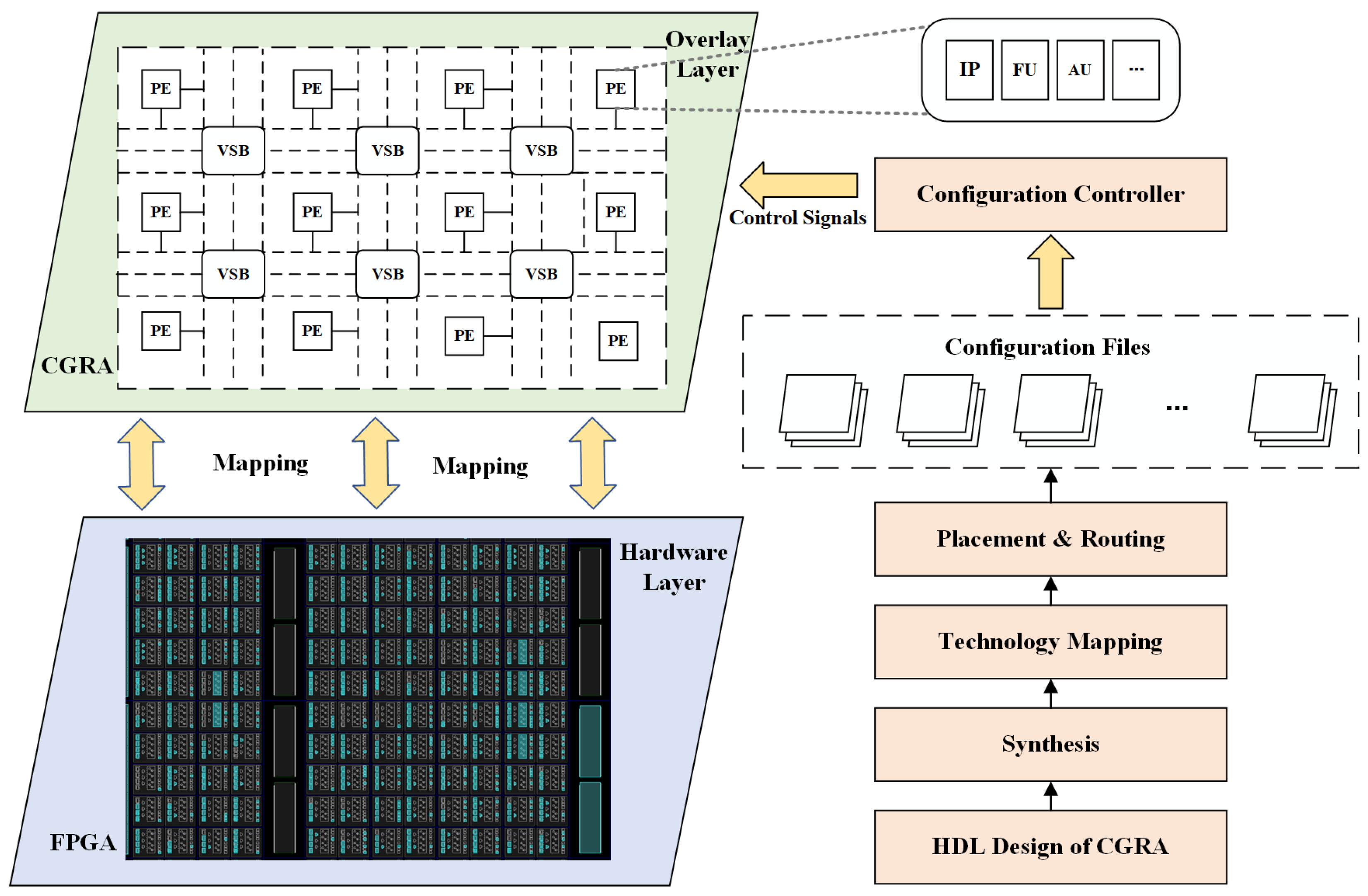

2.2. Coarse-Grained Reconfigurable Array

2.3. Evolutionary Algorithms and Evolvable Hardware

3. Proposed HT Mitigation Method

3.1. Overview

3.2. Optimization of Evolvable Regions

| Algorithm 1 Optimization of Evolvable Region Algorithm |

Input:All PEs on the CGRA Output:Optimized Evolvable Region (); List_PEs:all PEs; ListC_PEs:PEs used in the current evolutionary circuit.

|

3.3. Evolutionary Algorithm

4. Evaluation Results

4.1. The Target Circuit and the Expected Behavior of the HT Mitigation Mechanism

4.2. Experimental Results

5. Conclusions and Future Work

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Huang, Z.; Wang, Q.; Yang, P. Hardware trojan: Research progress and new trends on key problems. J. Comput. 2019, 42, 993–1017. [Google Scholar]

- Sharma, R.; Rathor, V.S.; Sharma, G.; Pattanaik, M. A new hardware Trojan detection technique using deep convolutional neural network. Integration 2021, 79, 1–11. [Google Scholar] [CrossRef]

- Deng, D.; Wang, Y.; Guo, Y. Novel Design Strategy Toward A2 Trojan Detection Based on Built-In Acceleration Structure. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2020, 39, 4496–4509. [Google Scholar] [CrossRef]

- Amelian, A.; Borujeni, S.E. A side-channel analysis for hardware Trojan detection based on path delay measurement. J. Circuits Syst. Comput. 2018, 27, 1850138. [Google Scholar] [CrossRef]

- Nguyen, L.N.; Yilmaz, B.B.; Prvulovic, M.; Zajic, A. A Novel Golden-Chip-Free Clustering Technique Using Backscattering Side Channel for Hardware Trojan Detection. In Proceedings of the 2020 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), San Jose, CA, USA, 7–11 December 2020; pp. 1–12. [Google Scholar]

- Rajendran, J.; Zhang, H.; Zhang, C.; Rose, G.S.; Pino, Y.; Sinanoglu, O.; Karri, R. Fault analysis-based logic encryption. IEEE Trans. Comput. 2013, 64, 410–424. [Google Scholar] [CrossRef]

- Samimi, M.S.; Aerabi, E.; Kazemi, Z.; Fazeli, M.; Patooghy, A. Hardware enlightening: No where to hide your hardware trojans! In Proceedings of the 22nd International Symposium on On-Line Testing and Robust System Design (IOLTS), Sant Feliu de Guixols, Spain, 4–6 July 2016; pp. 251–256. [Google Scholar]

- Dong, C.; He, G.; Liu, X.; Yang, Y.; Guo, W. A multi-layer hardware trojan protection framework for IoT chips. IEEE Access 2019, 7, 23628–23639. [Google Scholar] [CrossRef]

- Chen, J.; Dong, C.; Zhang, F.; He, G. A Hardware-Trojans detection approach based on eXtreme Gradient Boosting. In Proceedings of the 2nd International Conference on Computer and Communication Engineering Technology (CCET), Beijing, China, 16–18 August 2019; pp. 69–73. [Google Scholar]

- Vijayan, A.; Tahoori, M.B.; Chakrabarty, K. Runtime identification of hardware Trojans by feature analysis on gate-level unstructured data and anomaly detection. ACM Trans. Des. Autom. Electron. Syst. (TODAES) 2020, 25, 1–23. [Google Scholar] [CrossRef]

- Inoue, T.; Hasegawa, K.; Kobayashi, Y.; Yanagisawa, M.; Togawa, N. Designing subspecies of hardware Trojans and their detection using neural network approach. In Proceedings of the 8th International Conference on Consumer Electronics-Berlin (ICCE-Berlin), Berlin, Germany, 2–5 September 2018; pp. 1–4. [Google Scholar]

- Yingjian, Y.; Min, L.; Zhaoyang, Q. Design and Implementation of Hardware Trojan Detection Algorithm for Coarse-grained Reconfigurable Arrays. J. Electron. Inf. 2019, 41, 1257–1264. [Google Scholar]

- Huang, Z.; Wang, Q.; Chen, Y.; Jiang, X. A survey on machine learning against hardware trojan attacks: Recent advances and challenges. IEEE Access 2020, 8, 10796–10826. [Google Scholar] [CrossRef]

- Huang, Z.; Xie, C.; Li, Z.; Du, M.; Wang, Q. A Hardware Trojan Detection and Diagnosis Method for Gate-Level Netlists Based on Different Machine Learning Algorithms. J. Circuits Syst. Comput. 2022, 31, 2250135. [Google Scholar] [CrossRef]

- Jian, G.; Mengfei, Y. Evolutionary fault tolerance method based on virtual reconfigurable circuit with neural network architecture. IEEE Trans. Evol. Comput. 2017, 22, 949–960. [Google Scholar] [CrossRef]

- Sekanina, L.; Friedl, Š. An evolvable combinational unit for FPGAs. Comput. Inform. 2004, 23, 461–486. [Google Scholar]

- Aravind, A.R.; Kesavaraman, S.R.; Balasubramanian, K.; Yamuna, B.; Lingasubramaniam, K. Effect of hardware Trojans on the performance of a coded communication system. In Proceedings of the 2018 IEEE International Conference on Consumer Electronics (ICCE), Las Vegas, NV, USA, 12–14 January 2018; pp. 1–6. [Google Scholar]

- Labafniya, M.; Picek, S.; Borujeni, S.E.; Mentens, N. On the feasibility of using evolvable hardware for hardware Trojan detection and prevention. Appl. Soft Comput. 2020, 91, 106247. [Google Scholar] [CrossRef]

- Liu, L.; Zhou, Z.; Wei, S.; Zhu, M.; Yin, S.; Mao, S. DRMaSV: Enhanced Capability against Hardware Trojans in Coarse Grained Reconfigurable Architectures. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2017, 37, 782–795. [Google Scholar] [CrossRef]

- Hubner, M.; Figuli, P.; Girardey, R.; Soudris, D.; Siozios, K.; Becker, J. A Heterogeneous Multicore System on Chip with Run-Time Reconfigurable Virtual FPGA Architecture. In Proceedings of the 2011 IEEE International Parallel and Distributed Processing Workshops and PhD Forum (IPDPSW), Anchorage, AK, USA, 16–20 May 2011; pp. 143–149. [Google Scholar]

- Heyse, K.; Davidson, T.; Vansteenkiste, E.; Bruneel, K.; Stroobandt, D. Efficient implementation of virtual coarse grained reconfigurable arrays on FPGAs. In Proceedings of the 23rd International Conference on Field Programmable Logic and Applications, Porto, Portugal, 2–4 September 2013; pp. 1–8. [Google Scholar]

- Kulkarni, A.; Vasteenkiste, E.; Stroobandt, D.; Brokalakis, A.; Nikitakis, A. A Fully Parameterized Virtual Coarse Grained Reconfigurable Array for High Performance Computing Applications. In Proceedings of the 2016 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), Chicago, IL, USA, 23–27 May 2016; pp. 265–270. [Google Scholar]

- Fricke, F.; Werner, A.; Shahin, K.; Werner, F.; Hübner, M. Automatic Tool-Flow for Mapping Applications to an Application-Specific CGRA Architecture. In Proceedings of the 2019 IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), Rio de Janeiro, Brazil, 20–24 May 2019; pp. 147–154. [Google Scholar]

- Engelbrecht, A.P. Computational Intelligence: Introduction to Evolutionary Computation; Wiley: Hoboken, HJ, USA, 2007; pp. 127–175. [Google Scholar]

- Wang, J.; Piao, C.H.; Lee, C.H. Implementing Multi-VRC Cores to Evolve Combinational Logic Circuits in Parallel. In Proceedings of the International Conference on Evolvable Systems: From Biology to Hardware, Wuhan, China, 21–23 September 2007; Volume 91, pp. 23–24. [Google Scholar]

- Swarnalatha, A.; Shanthi, A.P. Complete hardware evolution based SoPC for evolvable hardware. Appl. Soft Comput. 2014, 18, 314–322. [Google Scholar] [CrossRef]

- López, B.; Valverde, J.; de la Torre, E.; Riesgo, T. Power-aware multi-objective evolvable hardware system on an FPGA. In Proceedings of the 2014 NASA/ESA Conference on Adaptive Hardware and Systems (AHS), Leicester, UK, 14–17 July 2014; pp. 61–68. [Google Scholar]

- Bao, Z.G.; Watanabe, T. A New Approach for Circuit Design Optimization using Genetic Algorithm. In Proceedings of the 2008 International SoC Design Conference, Busan, Korea, 24–25 November 2008; pp. 383–386. [Google Scholar]

- Hadjam, F.Z.; Moraga, C.; Rahmouni, M.K. Evolutionary Design of Digital Circuits Using Improved Multi Expression Programming (IMEP). Univ. Politècnica Catalunya Secció Matemàtiques Inf. 2007, 14, 103–123. [Google Scholar]

- Ashraf, R.; Luna, F.; Dechev, D.; DeMara, R. Designing digital circuits for FPGAs using parallel genetic algorithms (WIP). In Proceedings of the Symposium on Theory of Modeling and Simulation-DEVS Integrative M&S Symposium, Orlando, FL, USA, 26–30 March 2012; Volume 44. [Google Scholar]

- Drimer, S. Volatile FPGA Design Security—A Survey. 2008, pp. 1–51. Available online: http://citeseerx.ist.psu.edu/viewdoc/summary?doi=10.1.1.105.3354 (accessed on 25 April 2022).

| HR Times | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | Avg. |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 9 | 0.620 | 0.609 | 0.634 | 0.679 | 0.653 | 0.638 | 0.625 | 0.607 | 0.595 | 0.681 | 0.634 |

| 6 | 0.595 | 0.643 | 0.65 | 0.606 | 0.63 | 0.646 | 0.625 | 0.618 | 0.666 | 0.631 | 0.631 |

| HR Times | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | Avg. |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 25 | 39.005 | 31.358 | 30.015 | 38.237 | 28.374 | 27.899 | 52.490 | 28.959 | 41.799 | 29.215 | 34.735 |

| 20 | 40.617 | 42.806 | 25.90 | 30.681 | 29.353 | 28.797 | 34.881 | 35.472 | 32.108 | 34.291 | 33.490 |

| 16 | 31.718 | 30.817 | 29.173 | 24.520 | 28.182 | 19.431 | 28.276 | 25.473 | 27.261 | 18.815 | 26.367 |

| 15 | 23.446 | 25.119 | 28.843 | 28.530 | 25.919 | 13.493 | 25.618 | 27.922 | 28.135 | 8.293 | 23.532 |

| 12 | 0.121 | 0.098 | 0.274 | 0.126 | 0.157 | 0.769 | 0.263 | 0.277 | 0.416 | 0.126 | 0.262 |

| 10 | 0.075 | 0.103 | 0.098 | 0.100 | 0.074 | 0.101 | 0.078 | 0.098 | 0.068 | 0.076 | 0.087 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Z.; Wang, J.; Huang, Z.; Luo, N.; Wang, Q. Towards Trust Hardware Deployment of Edge Computing: Mitigation of Hardware Trojans Based on Evolvable Hardware. Appl. Sci. 2022, 12, 6601. https://doi.org/10.3390/app12136601

Li Z, Wang J, Huang Z, Luo N, Wang Q. Towards Trust Hardware Deployment of Edge Computing: Mitigation of Hardware Trojans Based on Evolvable Hardware. Applied Sciences. 2022; 12(13):6601. https://doi.org/10.3390/app12136601

Chicago/Turabian StyleLi, Zeyu, Junjie Wang, Zhao Huang, Nan Luo, and Quan Wang. 2022. "Towards Trust Hardware Deployment of Edge Computing: Mitigation of Hardware Trojans Based on Evolvable Hardware" Applied Sciences 12, no. 13: 6601. https://doi.org/10.3390/app12136601

APA StyleLi, Z., Wang, J., Huang, Z., Luo, N., & Wang, Q. (2022). Towards Trust Hardware Deployment of Edge Computing: Mitigation of Hardware Trojans Based on Evolvable Hardware. Applied Sciences, 12(13), 6601. https://doi.org/10.3390/app12136601