Process Corresponding Implications Associated with a Conclusive Model-Fit Current-Voltage Characteristic Curves

Abstract

:1. Introduction

2. Preparation and Measurements

2.1. Preparation

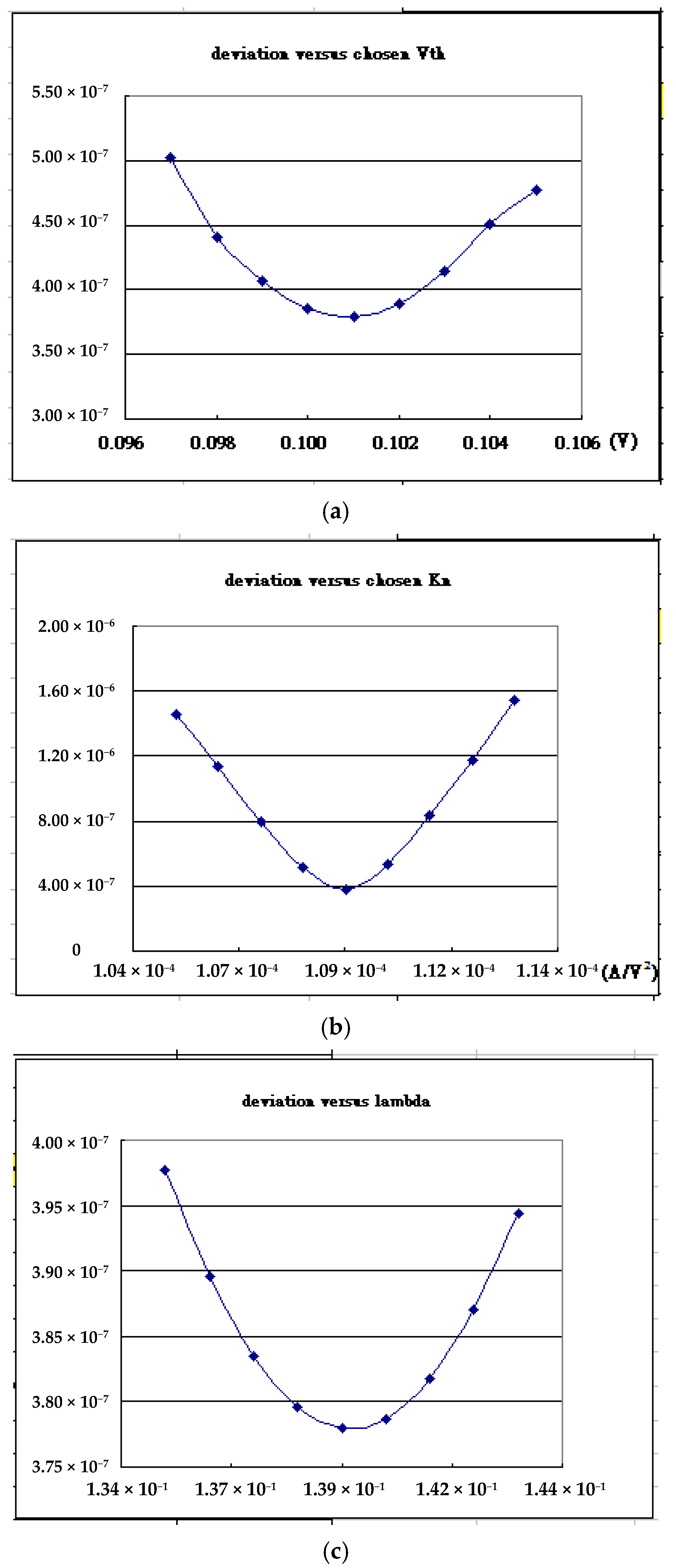

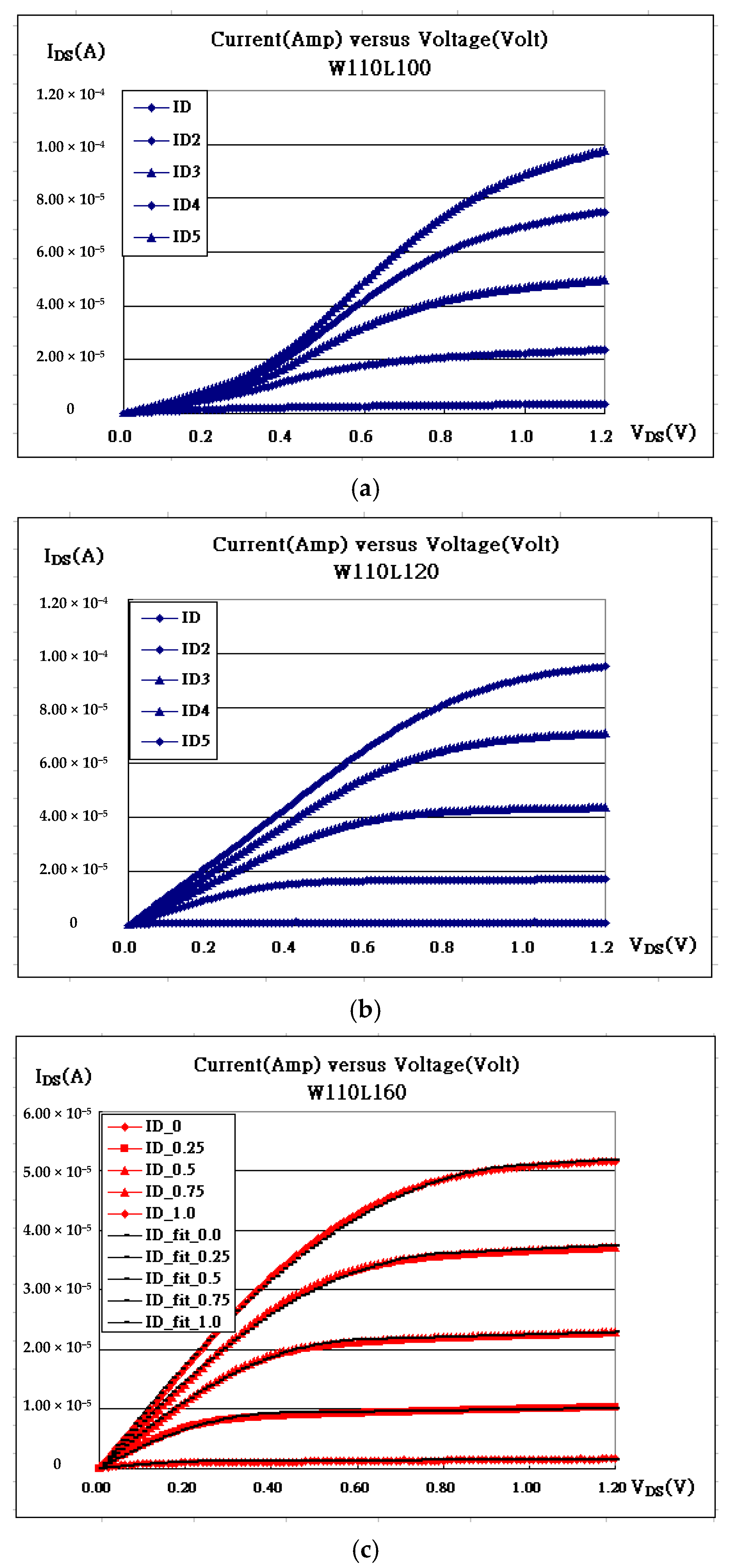

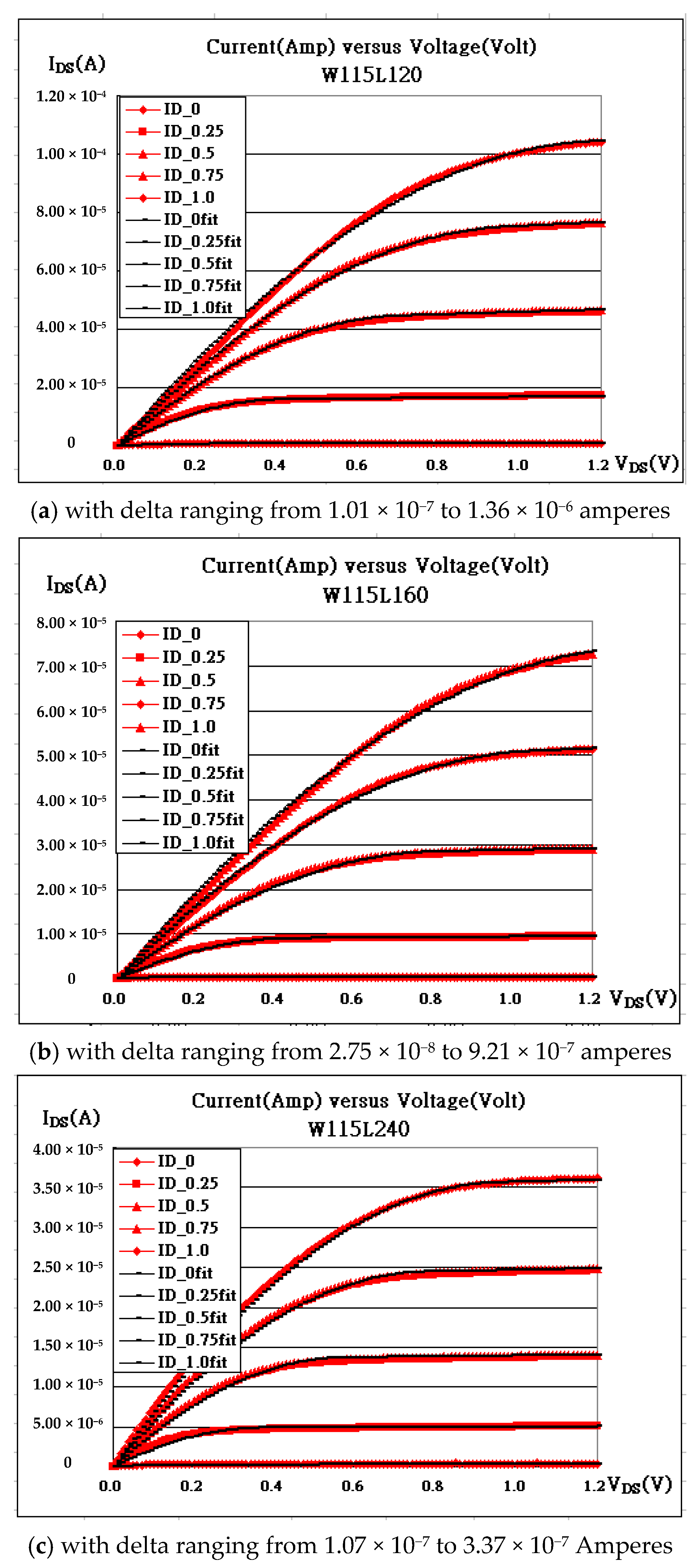

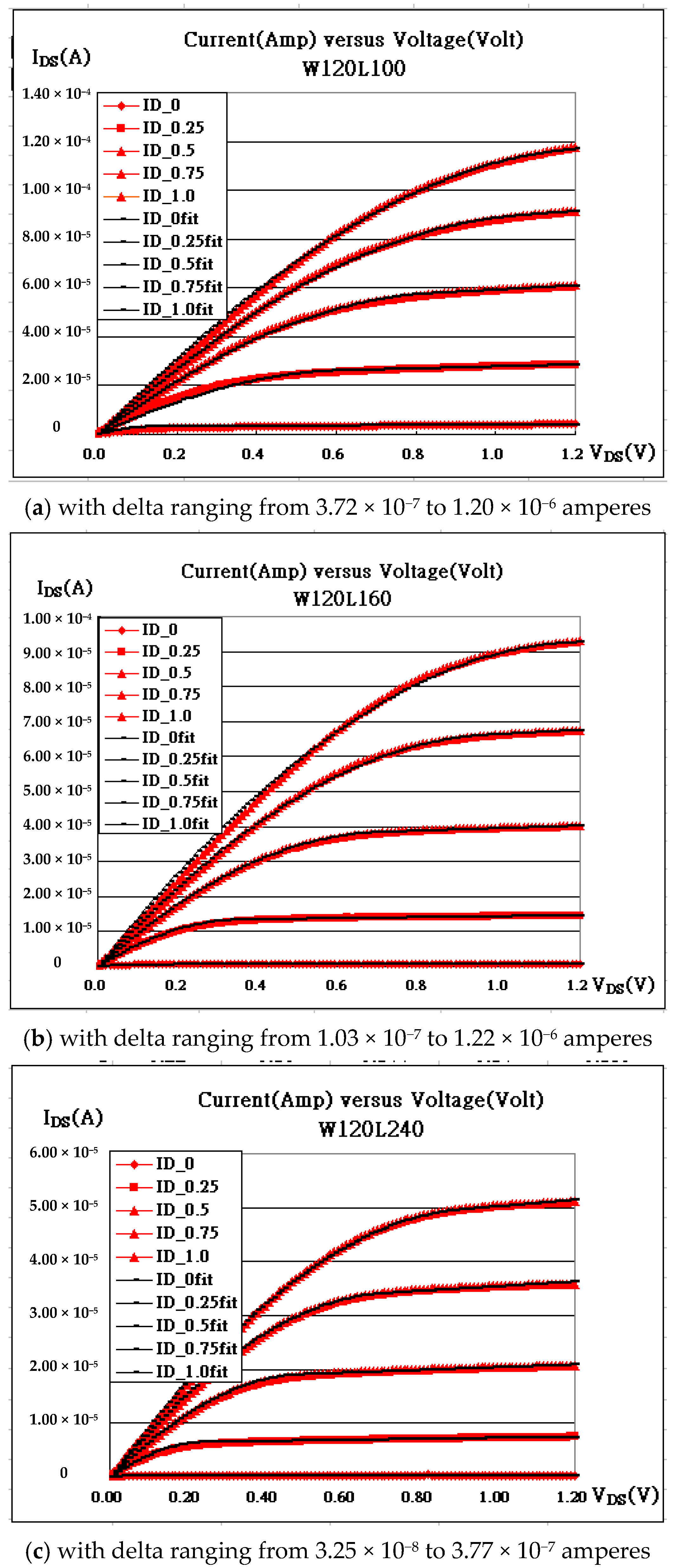

2.2. Fitting IDS-VDS and IDS-VGS

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Huang, X.; Lee, W.-C.; Kuo, C.; Hisamoto, D.; Chang, L.; Kedzierski, J.; Anderson, E.; Takeuchi, H.; Choi, Y.-K.; Asano, K.; et al. Sub-50 nm P-channel FinFET. IEEE Trans. Electron. Devices 2001, 48, 880. [Google Scholar] [CrossRef] [Green Version]

- Wang, F.; Xie, Y.; Bernstein, K.; Luo, Y. Dependability analysis of nano-scale FinFET circuits. In Proceedings of the IEEE Computer Society Annual Symposium on Emerging VLSI Technologies and Architectures (ISVLSI’06), Karlsruhe, Germany, 2–3 March 2006; pp. 6, 399. [Google Scholar]

- Takahashi, T.; Beppu, N.; Chen, K.; Oda, S.; Uchida, K. Self-heating effects and analog performance optimization of Fin-type field-effect transistors. Jpn. J. Appl. Phys. 2013, 52, 04CC03. [Google Scholar] [CrossRef]

- Diab, A.; Torres Sevilla, G.-A.; Christoloveanu, S.; Hussain, M.-M. Room to high temperature measurements of flexible SOI FinFETs with sub-20-nm fins. IEEE Trans. Electron. Devices 2014, 61, 3978. [Google Scholar] [CrossRef]

- Chen, C.W.; Wang, S.J.; Hsieh, W.C.; Chen, J.M.; Jong, T.; Lan, W.H.; Wang, M.C. Q-factor Performance of 28 nm-node High-k Gate Dielectric under DPN Treatment at Different Annealing Temperatures. Electronics 2020, 9, 2086. [Google Scholar] [CrossRef]

- Lu, P.; Yang, C.; Li, Y.; Li, B.; Han, Z. Three-Dimensional TID Hardening Design for 14 nm Node SOI FinFETs. Eng 2021, 2, 620–631. [Google Scholar] [CrossRef]

- Wang, S.J.; Sung, S.P.; Wang, M.C.; Huang, H.S.; Chen, S.Y.; Fan, S.K. Electrical stress probing recovery efficiency of 28 nm HK/MG nMOSFETs using decoupled plasma nitridation treatment. Vacuum 2018, 153, 117–121. [Google Scholar] [CrossRef]

- Huang, P.; Ma, C.; Wu, Z. Fast Dynamic IR-Drop Prediction Using Machine Learning in Bulk FinFET Technologies. Symmetry 2021, 13, 1807. [Google Scholar] [CrossRef]

- Crupi, G.; Schreurs, D.M.M.-P.; Caddemi, A.; Angelov, I.; Homayouni, M.; Raffo, A.; Vannini, G.; Parvais, B. Purely analytical extraction of an improved nonlinear FinFET model including non-quasi-static effects. Microelectron. Eng. 2009, 86, 2283–2289. [Google Scholar] [CrossRef]

- Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Zan, Y.; Li, J.; Zhang, Q.; Wu, Z.; Luo, J.; Wang, W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials 2021, 11, 1689. [Google Scholar] [CrossRef] [PubMed]

- Zhao, E.; Zhang, J.; Salman, A.; Subba, N.; Chan, J.; Marathe, A.; Beebe, S.; Taylor, K. Reliability challenges of high performance PD SOI CMOS with ultra-thin gate dielectrics. Solid State Electron. 2004, 48, 1703–1708. [Google Scholar] [CrossRef]

- Zhao, Z.Q.; Li, Y.; Zan, Y.; Li, Y.L.; Li, J.J.; Cheng, X.H.; Wang, G.L.; Liu, H.Y.; Wang, H.X.; Zhang, Q.Z.; et al. Fabrication technique of the Si0.5Ge0.5 Fin for the high mobility channel FinFET device. Semicond. Sci. Technol. 2020, 35, 045015. [Google Scholar] [CrossRef]

- Yang, H.C.; Liao, K.F.; Tsai, C.Y.; Liao, W.S.; Hsu, F.; Chi, S.C. An Alternative Algorithm to Demonstrate Electrical Characteristics of N/P-Channel Fin-FET Devices. In Proceedings of the 2014 International Conference on Information Science, Electronics and Electrical Engineering, Sapporo, Japan, 26–28 April 2014; pp. 2088–2091. [Google Scholar]

- Wang, M.-C.; Hsieh, W.-C.; Lin, C.-R.; Chu, W.-L.; Liao, W.-S.; Lan, W.-H. High-Drain Field Impacting Channel-Length Modulation Effect for Nano-Node N-Channel FinFETs. Crystals 2021, 11, 262. [Google Scholar] [CrossRef]

- Yang, H.C.; Lu, T.W.; Chang, T.Y.; Chi, S.C. The variation of threshold voltages associated with various applied gate voltages at different temperatures on FinFET devices. In Proceedings of the 2017 International Conference on Applied System Innovation (ICASI), Sapporo, Japan, 13–17 May 2017; pp. 799–801. [Google Scholar]

- Yang, H.C.; Chen, R.S.; Yang, Y.Y.; Tseng, C.K.; Tsai, C.J.; Tseng, J.J.; Chi, S.C.; Liao, Y.J. Electrical Performances of NFinFET and PFinFET Transistors Correlating Processing Conditions and Scales of the Fin Structure. In Proceedings of the 2019 8th International Conference on Innovation, Communication and Engineering (ICICE), Zhengzhou, China, 25–30 October 2019; pp. 55–58. [Google Scholar]

- Lee, J.; Park, T.; Ahn, H.; Kwak, J.; Moon, T.; Shin, C. Prediction Model for Random Variation in FinFET Induced by Line-Edge-Roughness (LER). Electronics 2021, 10, 455. [Google Scholar] [CrossRef]

- Yang, H.C.; Yang, P.J.; Lin, C.C.; Chen, K.H.; Lin, Y.S.; Chi, S.C. Current Voltage Characteristic Curves Addressing Non-Linear Kink-like Effects. In Proceedings of the 2021 7th International Conference on Applied System Innovation (ICASI), Chiayi, Taiwan, 24–25 September 2021; pp. 112–114. [Google Scholar]

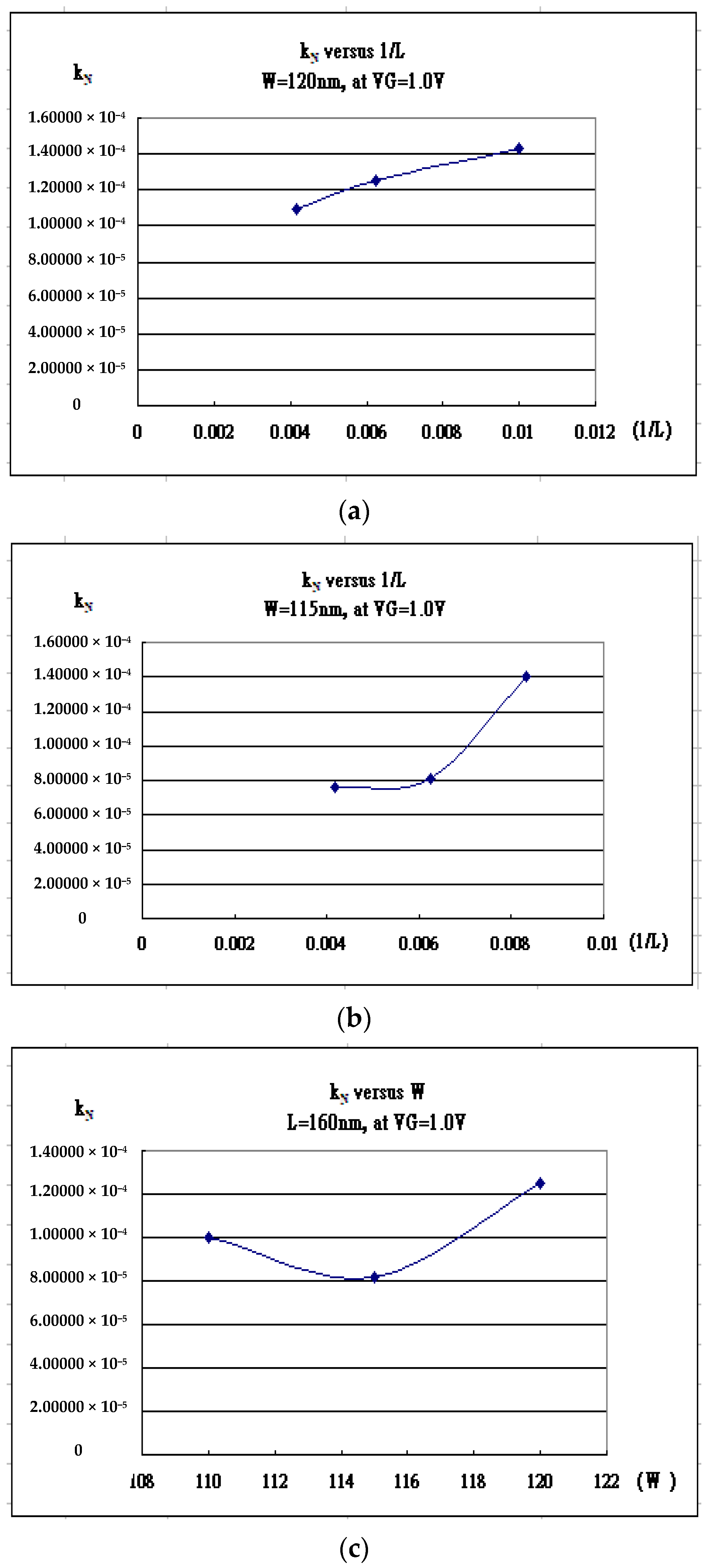

| Gate Bias | W120L240_fit | w120L160_fit | W120L100_fit |

|---|---|---|---|

| VG = 1.00 V | 1.09000 × 10−4 | 1.25000 × 10−4 | 1.43000 × 10−4 |

| VG = 0.75 V | 1.27000 × 10−4 | 1.30000 × 10−4 | 1.40000 × 10−4 |

| VG = 0.50 V | 1.48000 × 10−4 | 1.48000 × 10−4 | 1.46000 × 10−4 |

| VG = 0.25 V | 2.10000 × 10−4 | 2.10000 × 10−4 | 1.27000 × 10−4 |

| VG = 0.00 V | 8.70000 × 10−4 | 8.80000 × 10−5 | 3.10000 × 10−4 |

| Gate Bias | W115L240_fit | W115L160_fit | W115L120_fit |

|---|---|---|---|

| VG = 1.00 V | 7.60000 × 10−5 | 8.14000 × 10−5 | 1.40000 × 10−4 |

| VG = 0.75 V | 8.00000 × 10−5 | 8.65000 × 10−5 | 1.50000 × 10−4 |

| VG = 0.50 V | 8.18000 × 10−5 | 8.40000 × 10−5 | 1.70000 × 10−4 |

| VG = 0.25 V | 7.00000 × 10−5 | 9.00000 × 10−5 | 1.90000 × 10−4 |

| VG = 0.00 V | 1.00000 × 10−5 | 1.00000 × 10−5 | 1.00000 × 10−5 |

| Gate Bias | w120L160_fit | W115L160_fit | W110L160_fit |

|---|---|---|---|

| VG = 1.00 V | 1.25000 × 10−4 | 8.14000 × 10−5 | 1.00000 × 10−4 |

| VG = 0.75 V | 1.30000 × 10−4 | 8.65000 × 10−5 | 1.03000 × 10−4 |

| VG = 0.50 V | 1.48000 × 10−4 | 8.40000 × 10−5 | 1.10000 × 10−4 |

| VG = 0.25 V | 2.10000 × 10−4 | 9.00000 × 10−5 | 1.00000 × 10−4 |

| VG = 0.00 V | 8.80000 × 10−5 | 1.00000 × 10−5 | 2.50000 × 10−5 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, H.-C.; Chi, S.-C. Process Corresponding Implications Associated with a Conclusive Model-Fit Current-Voltage Characteristic Curves. Appl. Sci. 2022, 12, 462. https://doi.org/10.3390/app12010462

Yang H-C, Chi S-C. Process Corresponding Implications Associated with a Conclusive Model-Fit Current-Voltage Characteristic Curves. Applied Sciences. 2022; 12(1):462. https://doi.org/10.3390/app12010462

Chicago/Turabian StyleYang, Hsin-Chia, and Sung-Ching Chi. 2022. "Process Corresponding Implications Associated with a Conclusive Model-Fit Current-Voltage Characteristic Curves" Applied Sciences 12, no. 1: 462. https://doi.org/10.3390/app12010462

APA StyleYang, H.-C., & Chi, S.-C. (2022). Process Corresponding Implications Associated with a Conclusive Model-Fit Current-Voltage Characteristic Curves. Applied Sciences, 12(1), 462. https://doi.org/10.3390/app12010462