Monolithic 3D Inverter with Interface Charge: Parameter Extraction and Circuit Simulation

Abstract

1. Introduction

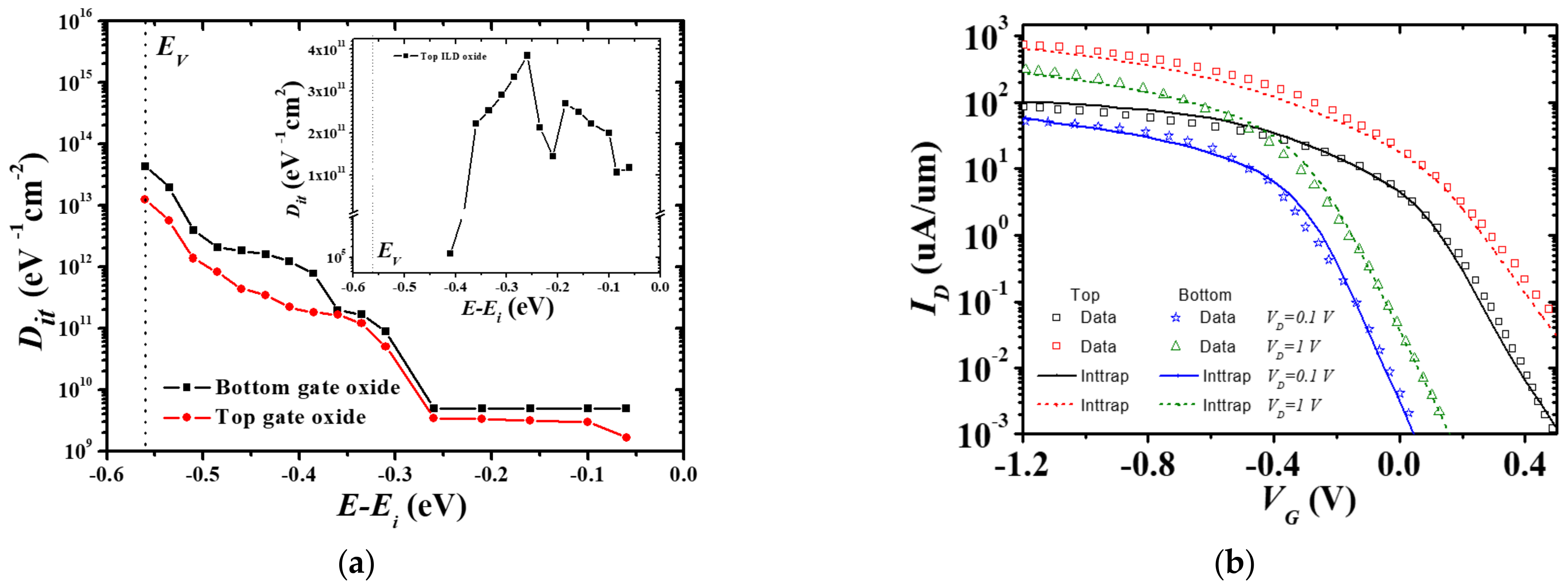

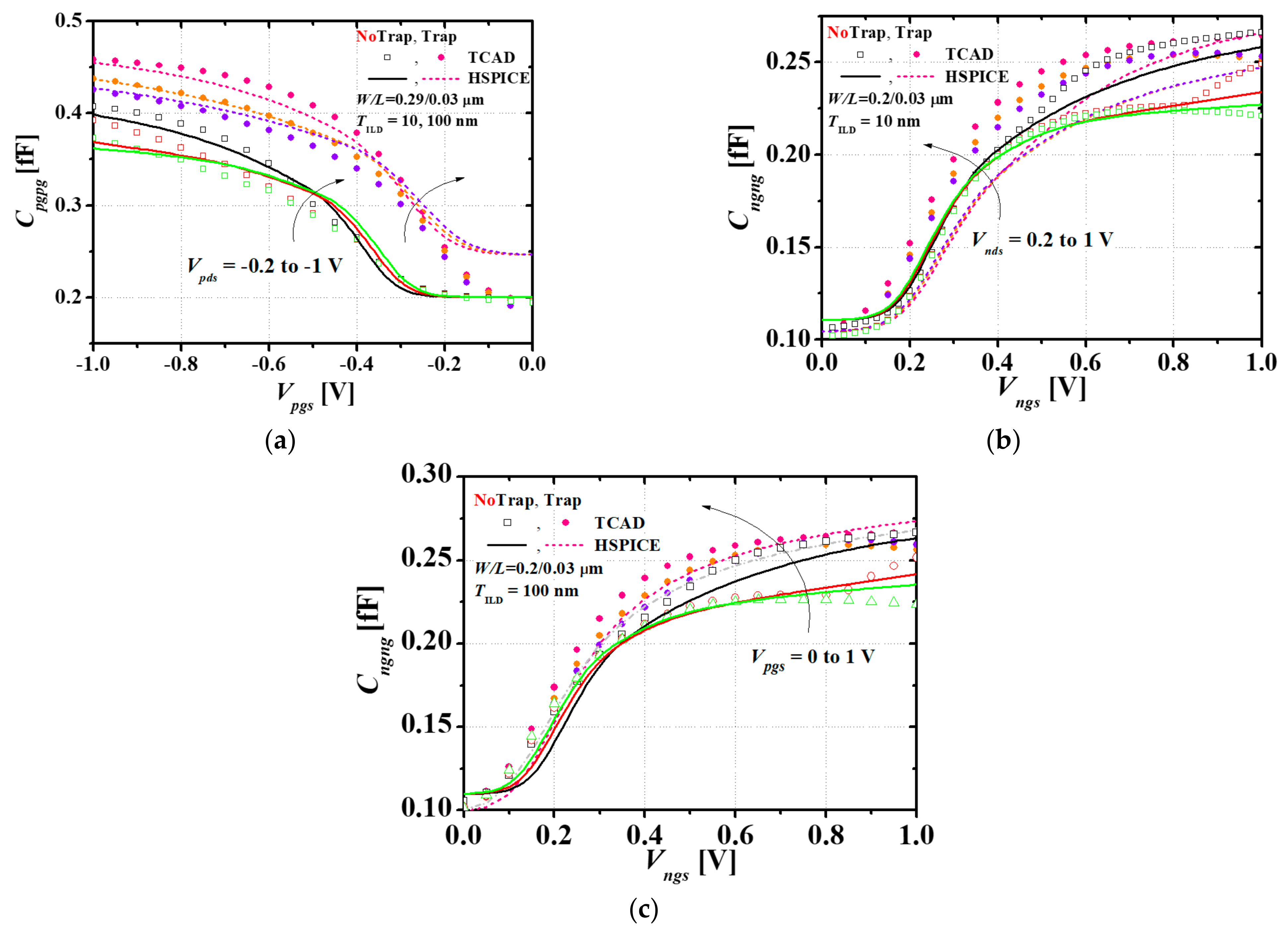

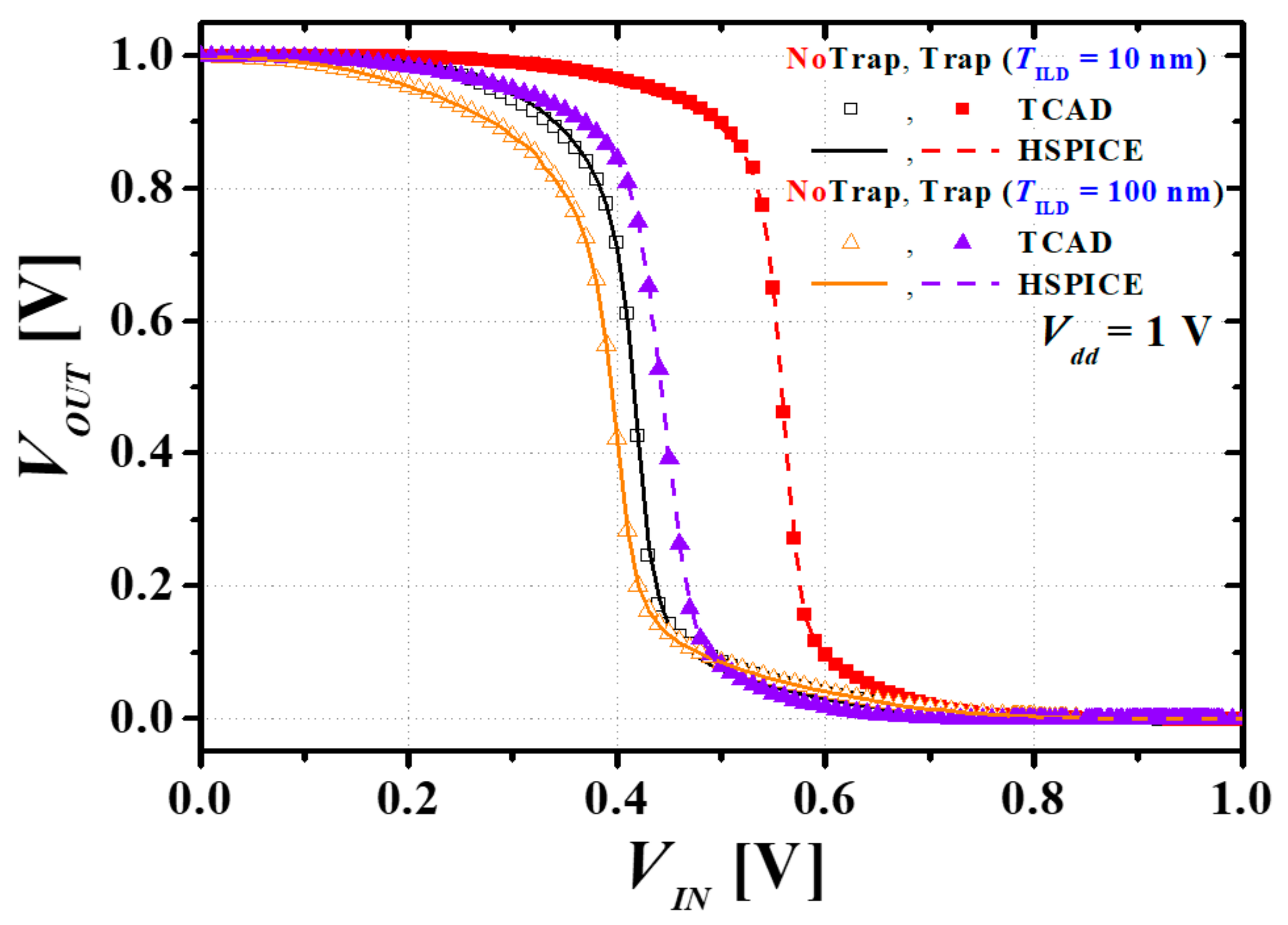

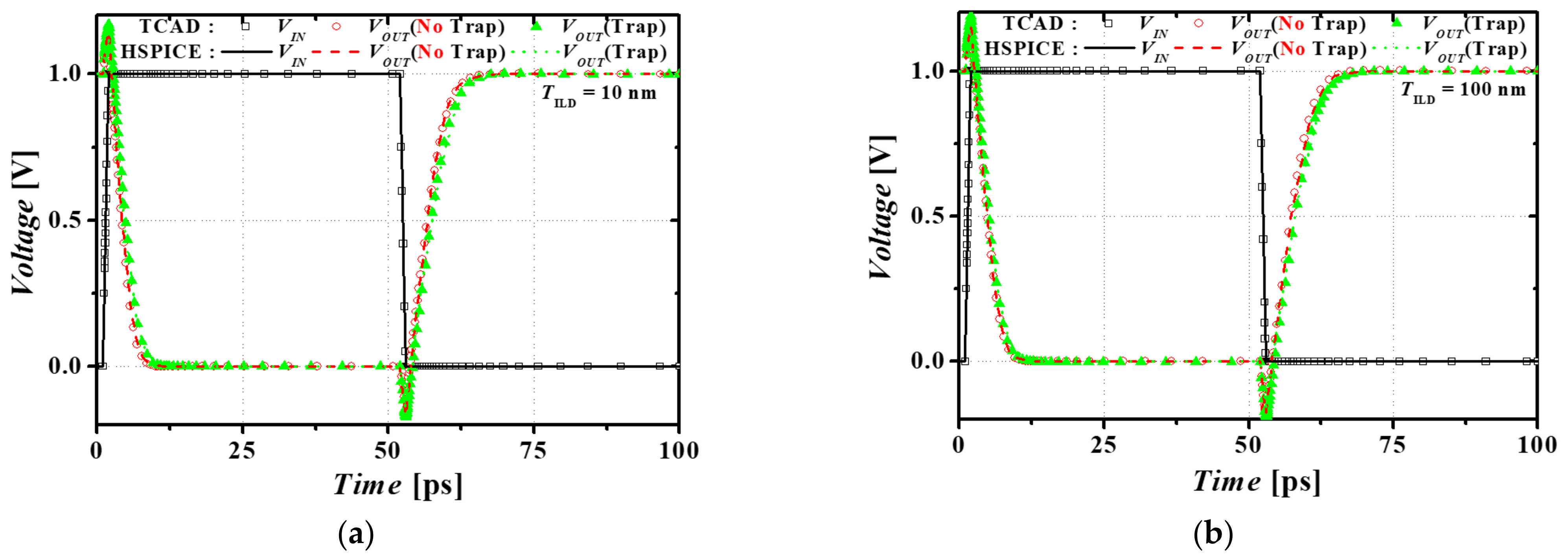

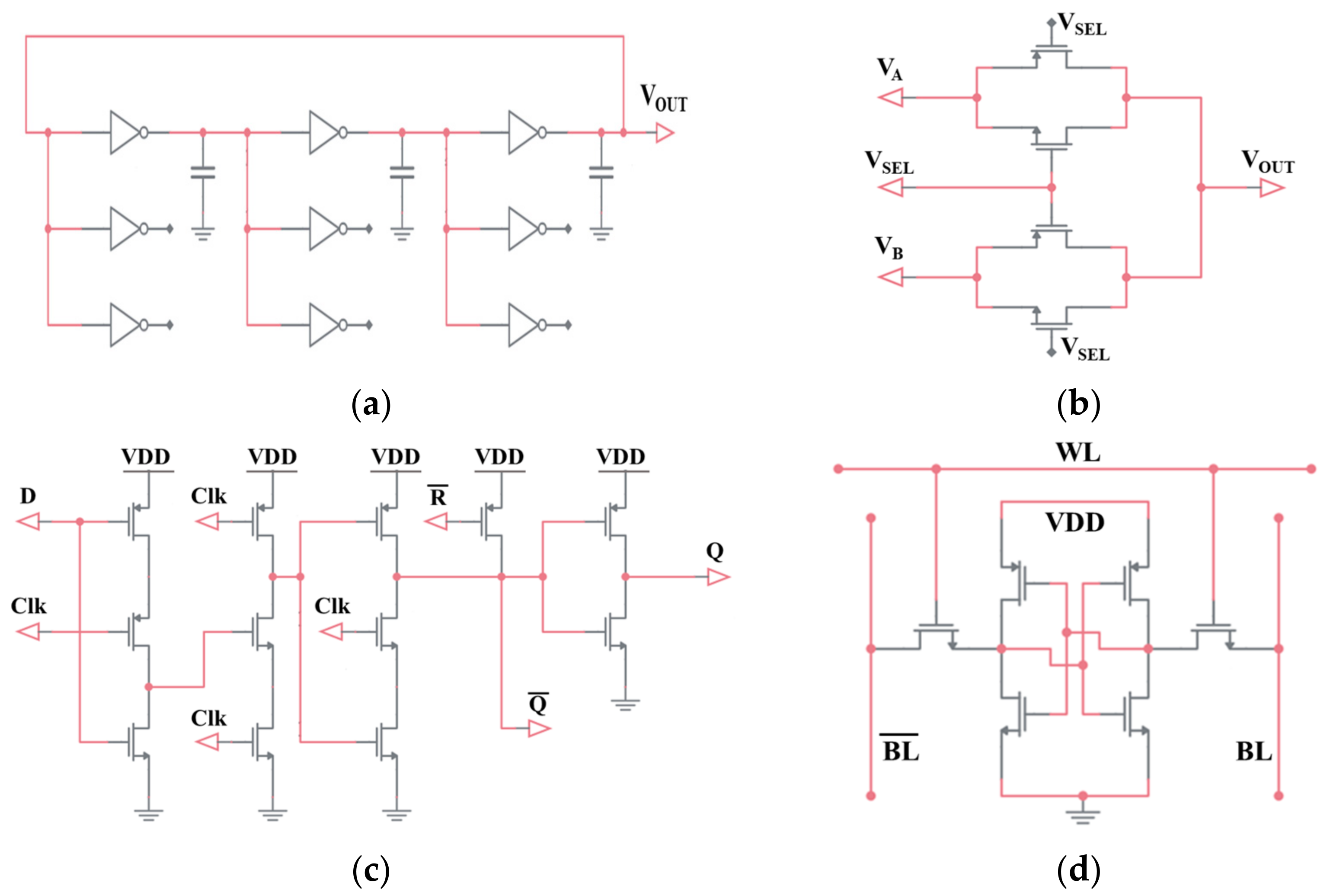

2. Interface Trap Charges in M3DINV

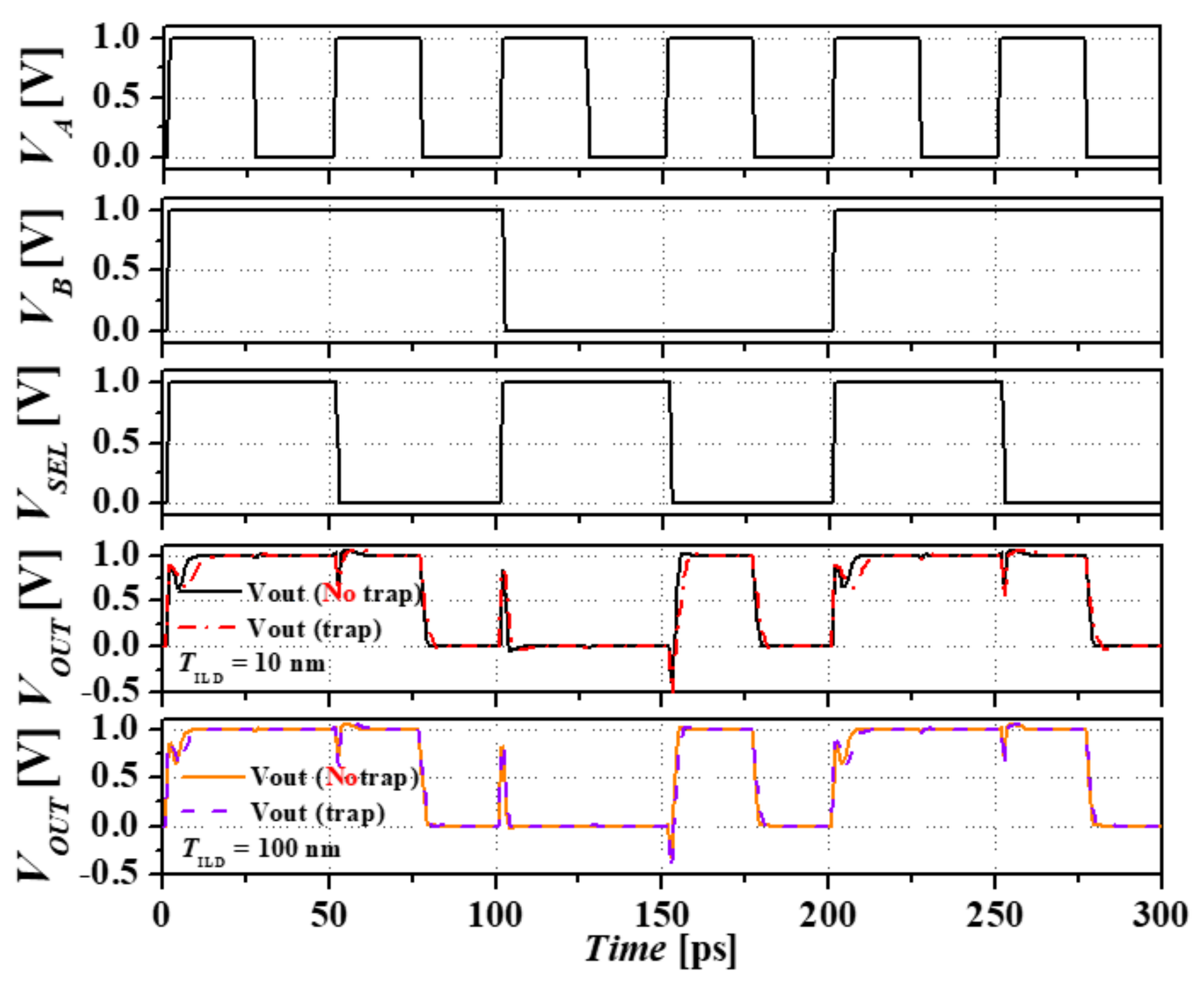

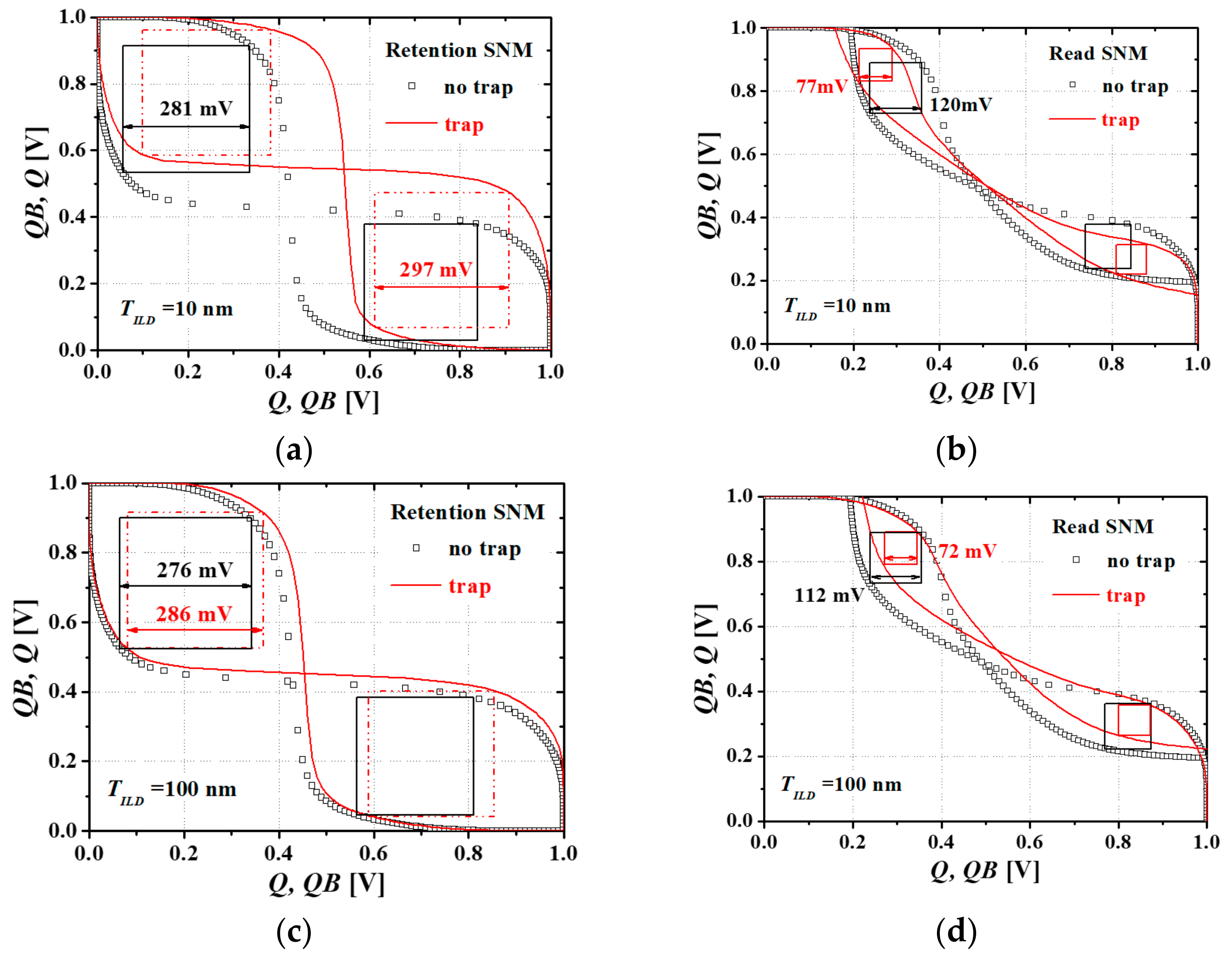

3. Parameter Extraction for Circuit Simulation

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Acknowledgments

Conflicts of Interest

References

- Thompson, S.E.; Parthasarathy, S. Moore’s law: The future of Si microelectronics. Mater. Today 2006, 9, 20–25. [Google Scholar] [CrossRef]

- Vinet, M.; Batude, P.; Fenouillet-Beranger, C.; Clermidy, F.; Brunet, L.; Rozeau, O.; Hartmannn, J.; Billoint, O.; Cibrario, G.; Previtali, B.; et al. Monolithic 3D integration: A powerful alternative to classical 2D scaling. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–3. [Google Scholar]

- Turkyilmaz, O.; Cibrario, G.; Rozeau, O.; Batude, P.; Clermidy, F. 3D FPGA using high-density interconnect Monolithic Integration. In Proceedings of the 2014 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 24–28 March 2014; pp. 1–4. [Google Scholar] [CrossRef]

- Santos, C.; Vivet, P.; Thuries, S.; Billoint, O.; Colonna, J.P.; Coudrain, P.; Wang, L. Thermal performance of CoolCube™ monolithic and TSV-based 3D integration processes. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 8–11 November 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Llorente, C.D.; Le Royer, C.; Batude, P.; Fenouillet-Beranger, C.; Martinie, S.; Lu, C.-M.; Allain, F.; Colinge, J.-P.; Cristoloveanu, S.; Ghibaudo, G.; et al. New insights on SOI Tunnel FETs with low-temperature process flow for CoolCube™ integration. Solid-State Electron. 2018, 144, 78–85. [Google Scholar] [CrossRef]

- Coudrain, P.; Batude, P.; Gagnard, X.; Leyris, C.; Ricq, S.; Vinet, M.; Pouydebasque, A.; Moussy, N.; Cazaux, Y.; Giffard, B.; et al. Setting up 3D Sequential Integration for Back-Illuminated CMOS Image Sensors with Highly Miniaturized Pixels with low temperature Fully Depleted SOI transistors. In Proceedings of the IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Batude, P.; Jaud, M.-A.; Thomas, O.; Clavelier, L.; Pouydebasque, A.; Vinet, M.; Deleonibus, S.; Amara, A. 3D CMOS integration: Introduction of dynamic coupling and application to compact and robust 4T SRAM. In Proceedings of the 2008 IEEE International Conference on Integrated Circuit Design and Technology and Tutorial, Grenoble, France, 2–4 June 2008; pp. 281–284. [Google Scholar] [CrossRef]

- Sideris, P.; Lugo-Alvarez, J.; Batude, P.; Brunet, L.; Acosta-Alba, P.; Kerdiles, S.; Fenouillet-Beranger, C.; Sicard, G.; Rozeau, O.; Andrieu, F.; et al. Inter-tier Dynamic Coupling and RF Crosstalk in 3D Sequential Integration. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 3.4.1–3.4.4. [Google Scholar] [CrossRef]

- Lim, S.K. Bringing 3D ICs to Aerospace: Needs for design tools and methodologies. J. Inf. Commun. Converg. Eng. 2017, 15, 117–122. [Google Scholar] [CrossRef]

- Yu, Y.S.; Panth, S.; Lim, S.K. Electrical coupling of monolithic 3-D inverters. IEEE Trans. Electron Devices 2016, 63, 3346–3349. [Google Scholar] [CrossRef]

- Ahn, T.J.; Choi, B.H.; Lim, S.K.; Yu, Y.S. Electrical coupling and simulation of monolithic 3D logic circuits and static random access memory. Micromachines 2019, 10, 637. [Google Scholar] [CrossRef] [PubMed]

- Ahn, T.J.; Perumal, R.; Lim, S.K.; Yu, Y.S. Parameter extraction and power/performance analysis of Monolithic 3-D Inverter (M3INV). IEEE Trans. Electron Devices 2019, 66, 1006–1011. [Google Scholar] [CrossRef]

- Ahn, T.; Lee, S.H.; Yu, Y. Interface trap density distribution in 3D sequential Integrated-Circuit and its effect. J. Korea Inst. Inf. Commun. Eng. 2015, 19, 2899–2904. [Google Scholar] [CrossRef][Green Version]

- Batude, P.; Vinet, M.; Xu, C.; Previtali, B.; Tabone, C.; Le Royer, C.; Sanchez, L.; Baud, L.; Brunet, L.; Toffoli, A.; et al. Demonstration of low temperature 3D sequential FDSOI integration down to 50 nm gate length. In Proceedings of the 2011 Symposium on VLSI Technology—Digest of Technical Papers, Kyoto, Japan, 14–16 June 2011; pp. 158–159. [Google Scholar]

- Silvaco Int. ATLAS ver. 5. 20. R Manual; Silvaco Int.: Santa Clara, CA, USA, 2015. [Google Scholar]

- Rozeau, O.; Jaud, M.-A.; Poiroux, T.; Benosman, M. UTSOI Model 1.1.3 Laboratoire d’Électronique et de Technologie de l’Information (Leti). Available online: http://www-leti.cea.fr (accessed on 25 May 2012).

- Poiroux, T.; Rozeau, O.; Scheer, P.; Martinie, S.; Jaud, M.A.; Minondo, M.; Juge, A.; Barbe, J.C.; Vinet, M. Leti-UTSOI2.1: A compact model for UTBB-FDSOI technologies—Part I: Interface potentials analytical model. IEEE Trans. Electron Devices 2015, 62, 2751–2759. [Google Scholar] [CrossRef]

- Poiroux, T.; Rozeau, O.; Scheer, P.; Martinie, S.; Jaud, M.-A.; Minondo, M.; Juge, A.; Barbe, J.C.; Vinet, M. Leti-UTSOI2.1: A compact model for UTBB-FDSOI technologies—Part II: DC and AC model description. IEEE Trans. Electron Devices 2015, 62, 2760–2768. [Google Scholar] [CrossRef]

- HSPICE. Reference Manual: MOSFET Models; Synopsys, Inc.: Mountain View, CA, USA, 2016. [Google Scholar]

- Planes, N.; Weber, O.; Barral, V.; Haendler, S.; Noblet, D.; Croain, D.; Bocat, M.; Sassoulas, P.-O.; Federspiel, X.; Cros, A.; et al. 28 nm FDSOI technology platform for high-speed low-voltage digital applications. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 133–134. [Google Scholar] [CrossRef]

- Rani, T.E.; Rani, M.A.; Rao, R. AREA optimized low power arithmetic and logic unit. In Proceedings of the International Conference on Electronics Computer Technology, Kanyakumari, India, 8–10 April 2011; pp. 224–228. [Google Scholar] [CrossRef]

- Nasrollahpour, M.; Sreekumar, R.; Hajilou, F.; Aldacher, M.; Hamedi-Hagh, S. Low-power bluetooth receiver front end design with oscillator leakage reduction technique. J. Low Power Electron. 2018, 14, 179–184. [Google Scholar] [CrossRef]

- Arandilla, C.D.; Alvarez, A.B.; Roque, C.R.K. Static noise margin of 6T SRAM cell in 90-nm CMOS. In Proceedings of the UkSim 13th International Conference on Computer Modelling and Simulation, Cambridge, UK, 30 March–1 April 2011; pp. 534–539. [Google Scholar] [CrossRef]

- Thomas, O.; Vinet, M.; Rozeau, O.; Batude, P.; Valentian, A. Compact 6T SRAM cell with robust read/write stabilizing design in 45nm Monolithic 3D IC technology. In Proceedings of the 2009 IEEE International Conference on IC Design and Technology, Austin, TX, USA, 18–20 May 2009; pp. 195–198. [Google Scholar] [CrossRef]

| Parameter | Unit | Description | Value |

|---|---|---|---|

| DLQ | m | Effective channel length offset CV | 4 × 10−8 |

| VFBO | V | Geometry-independent flat-band voltage | 0.3 |

| CTO | - | Interface states factor | 0.4 |

| CICO | - | Geometry-independent part of substrate bias dependence factor of interface coupling | 2.2 |

| CFL | V−1 | Length dependence of DIBL | 1.3 |

| UO | m2/V/s | Zero-field mobility | 1.9 × 10−3 |

| MUEO | m/V | Mobility reduction coefficient | 4.3 |

| THEMUO | - | Mobility reduction exponent | 1 |

| FETAO | - | Effective field parameter | 3 |

| PSCEL | - | Length dependence of short channel effect above threshold | 0.15 |

| THESATO | V−1 | Geometry-independent velocity saturation parameter | 3 |

| AXO | - | Geometry-independent of linear/saturation transition factor | 0 |

| ALPL1 | - | Length dependence of CLM pre-factor ALP | 0.0005 |

| VPO | V | CLM logarithm dependence factor | 0.04 |

| CGBOVL | F | Oxide capacitance for gate-substrate overlap | 9 × 10−16 |

| CFRW | F | Outer fringe capacitance | 2.8 × 10−16 |

| Parameter | Unit | Description | Value (TILD) | |

|---|---|---|---|---|

| 10 nm | 100 nm | |||

| DLQ | m | Effective channel length offset CV | 4 × 10−8 | 4 × 10−8 |

| VFBO | V | Geometry-independent flat-band voltage | −0.175 | −0.26 |

| CTO | - | Interface states factor | 0.4 | 0.4 |

| CICO | - | Geometry-independent part of substrate bias dependence factor of interface coupling | 0.2 | 0.2 |

| CFL | V−1 | Length dependence of DIBL | 0.4 | 1 |

| UO | m2/V/s | Zero-field mobility | 1.8 × 10−2 | 3.5 × 10−2 |

| MUEO | m/V | Mobility reduction coefficient | 1.5 | 7 |

| THEMUO | - | Mobility reduction exponent | 0.1 | 0.2 |

| FETAO | - | Effective field parameter | 1 | 0 |

| PSCEL | - | Length dependence of short channel effect above threshold | 0.14 | 0.06 |

| THESATO | V−1 | Geometry-independent velocity saturation parameter | 7 | 1 |

| AXO | - | Geometry-independent of linear/saturation transition factor | 6 | 0.5 |

| ALPL1 | - | Length dependence of CLM pre-factor ALP | 0.0002 | 0.002 |

| VPO | V | CLM logarithm dependence factor | 0.04 | 2 |

| CGBOVL | F | Oxide capacitance for gate-substrate overlap | 0 | 14 × 10−16 |

| CFRW | F | Outer fringe capacitance | 2.5 × 10−16 | 2.2 × 10−16 |

| RSGO | - | Gate-bias dependence of RS | 0.2 | 0.5 |

| Stages | Power [μW] | Frequency [GHz] | Delay per Stage [ps] | |||

|---|---|---|---|---|---|---|

| 10 nm | 100 nm | 10 nm | 100 nm | 10 nm | 100 nm | |

| 3 | 281 | 274 | 18.7 | 22.1 | 9.04 | 7.59 |

| 19 | 279 | 272 | 2.88 | 3.37 | 9.16 | 7.81 |

| 101 | 281 | 276 | 0.52 | 0.62 | 9.28 | 7.93 |

| Stages | Power [μW] | Frequency [GHz] | Delay per Stage [ps] | |||

|---|---|---|---|---|---|---|

| 10 nm | 100 nm | 10 nm | 100 nm | 10 nm | 100 nm | |

| 3 | 283 | 283 | 14.2 | 15.8 | 11.71 | 10.33 |

| 19 | 282 | 278 | 2.38 | 2.73 | 11.93 | 10.67 |

| 101 | 284 | 283 | 0.408 | 0.45 | 12.13 | 10.98 |

| 2 × 1 MUX | D Flip-Flop | |||||||

|---|---|---|---|---|---|---|---|---|

| No-trap [10] | Trap | No-trap [10] | Trap | |||||

| TILD [nm] | 10 | 100 | 10 | 100 | 10 | 100 | 10 | 100 |

| Propagation delay [ps] | 2.3 | 1.95 | 4.1 | 3.75 | 10.2 | 8.35 | 16.2 | 13.7 |

| Power Consumption [μW] | 22.6 | 18.4 | 29.7 | 27.8 | 41.9 | 39.3 | 47.4 | 45.1 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahn, T.J.; Lim, S.K.; Yu, Y.S. Monolithic 3D Inverter with Interface Charge: Parameter Extraction and Circuit Simulation. Appl. Sci. 2021, 11, 12151. https://doi.org/10.3390/app112412151

Ahn TJ, Lim SK, Yu YS. Monolithic 3D Inverter with Interface Charge: Parameter Extraction and Circuit Simulation. Applied Sciences. 2021; 11(24):12151. https://doi.org/10.3390/app112412151

Chicago/Turabian StyleAhn, Tae Jun, Sung Kyu Lim, and Yun Seop Yu. 2021. "Monolithic 3D Inverter with Interface Charge: Parameter Extraction and Circuit Simulation" Applied Sciences 11, no. 24: 12151. https://doi.org/10.3390/app112412151

APA StyleAhn, T. J., Lim, S. K., & Yu, Y. S. (2021). Monolithic 3D Inverter with Interface Charge: Parameter Extraction and Circuit Simulation. Applied Sciences, 11(24), 12151. https://doi.org/10.3390/app112412151