Co-Package Technology Platform for Low-Power and Low-Cost Data Centers

Abstract

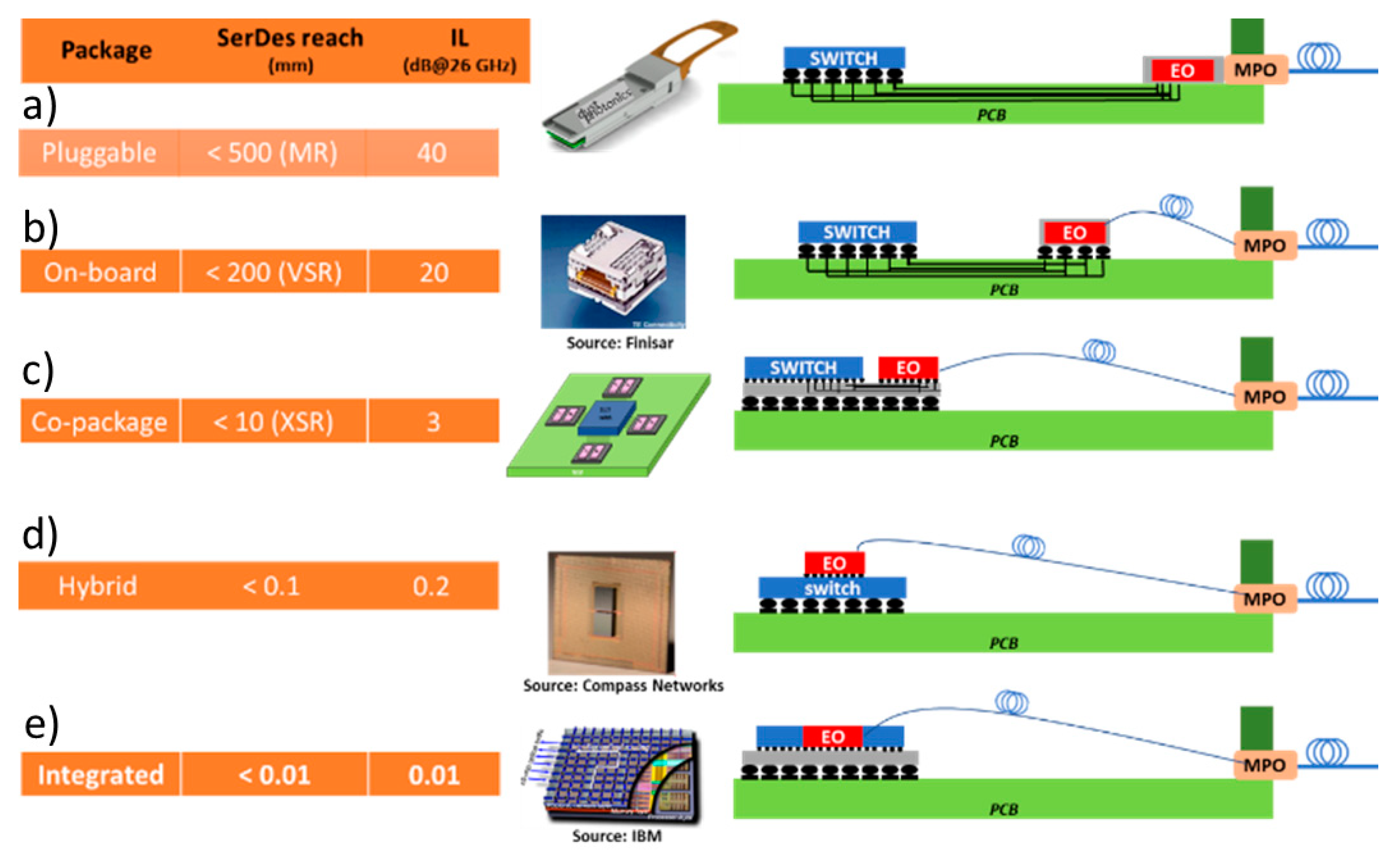

1. Introduction

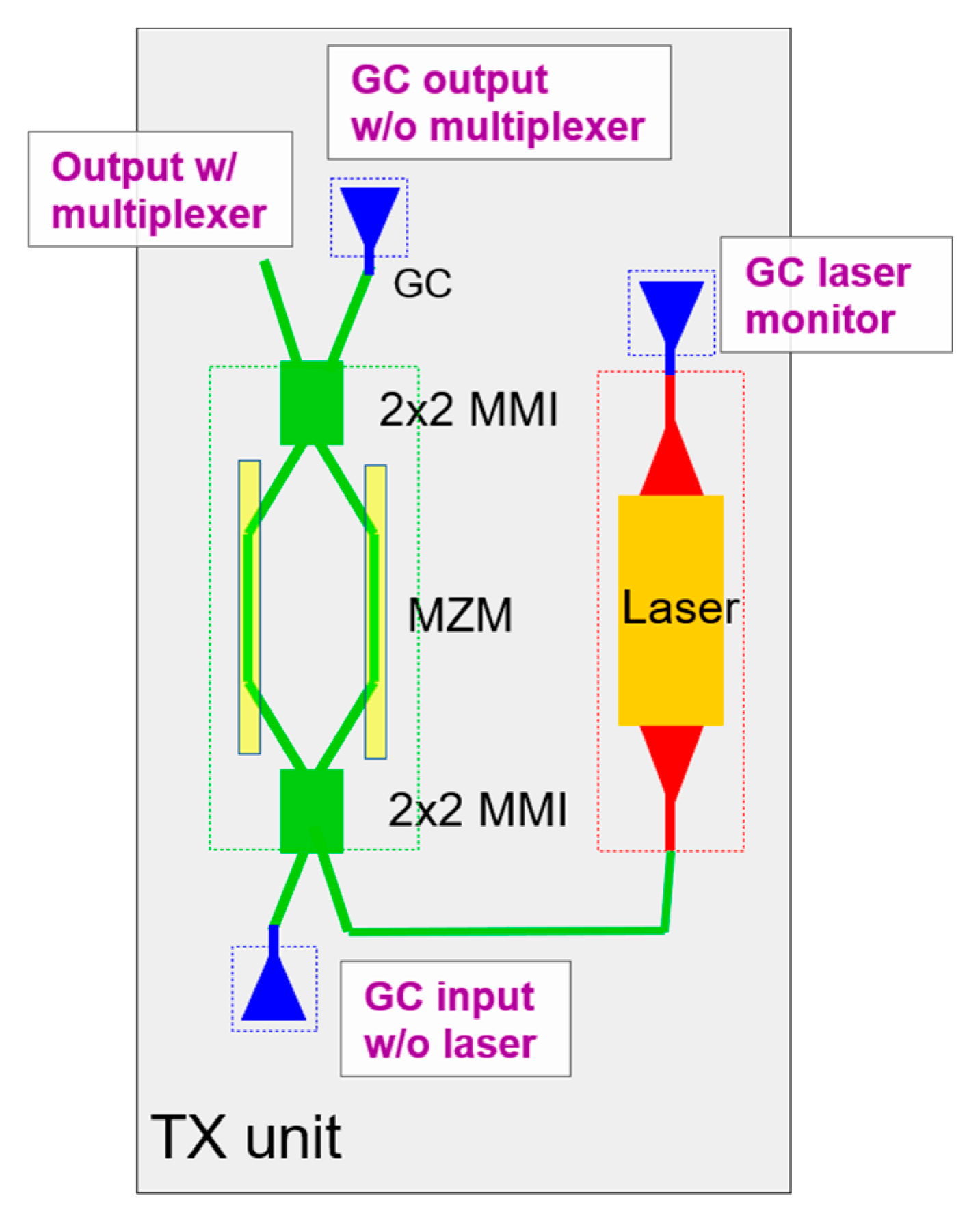

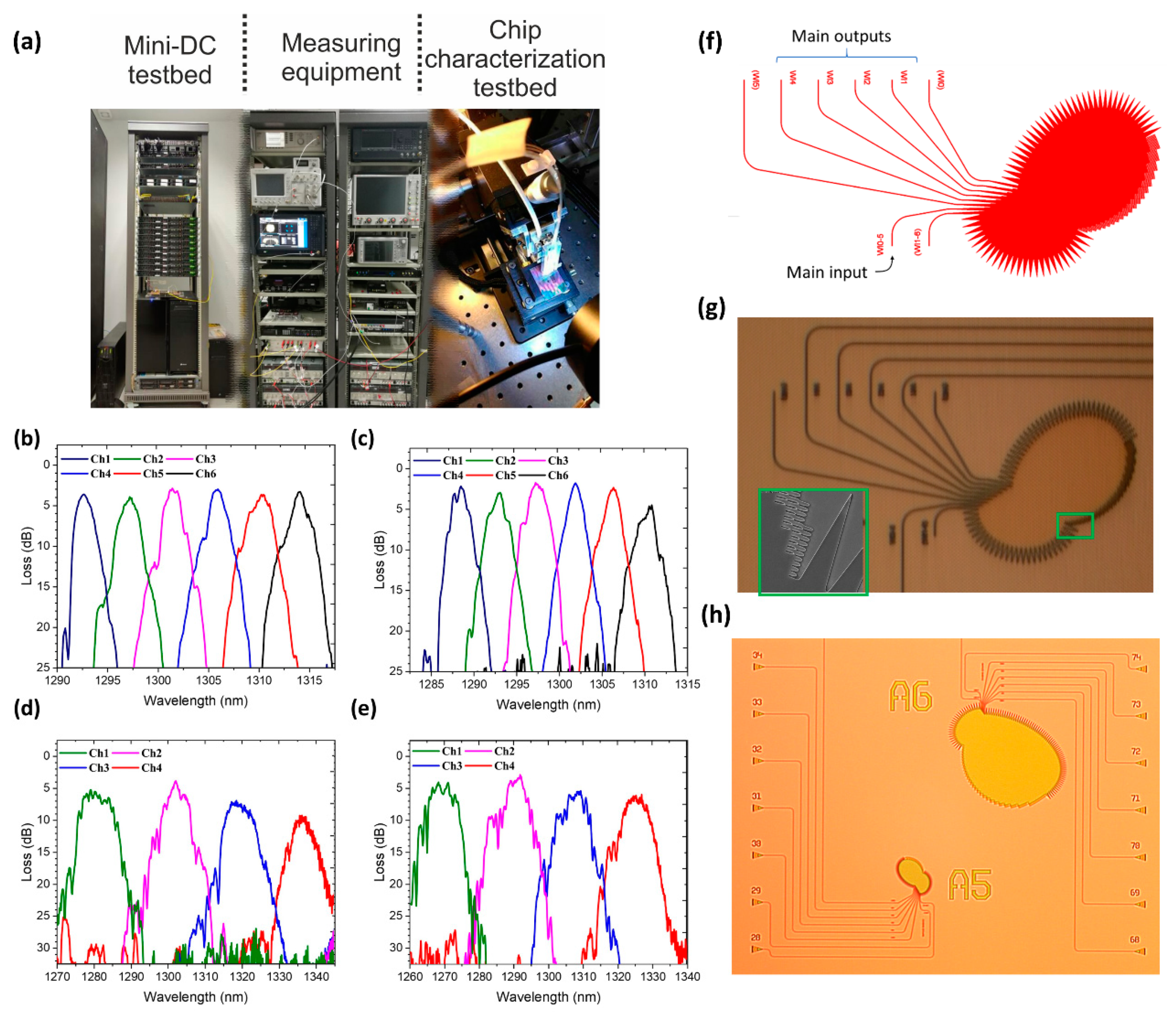

2. System Architecture and Design

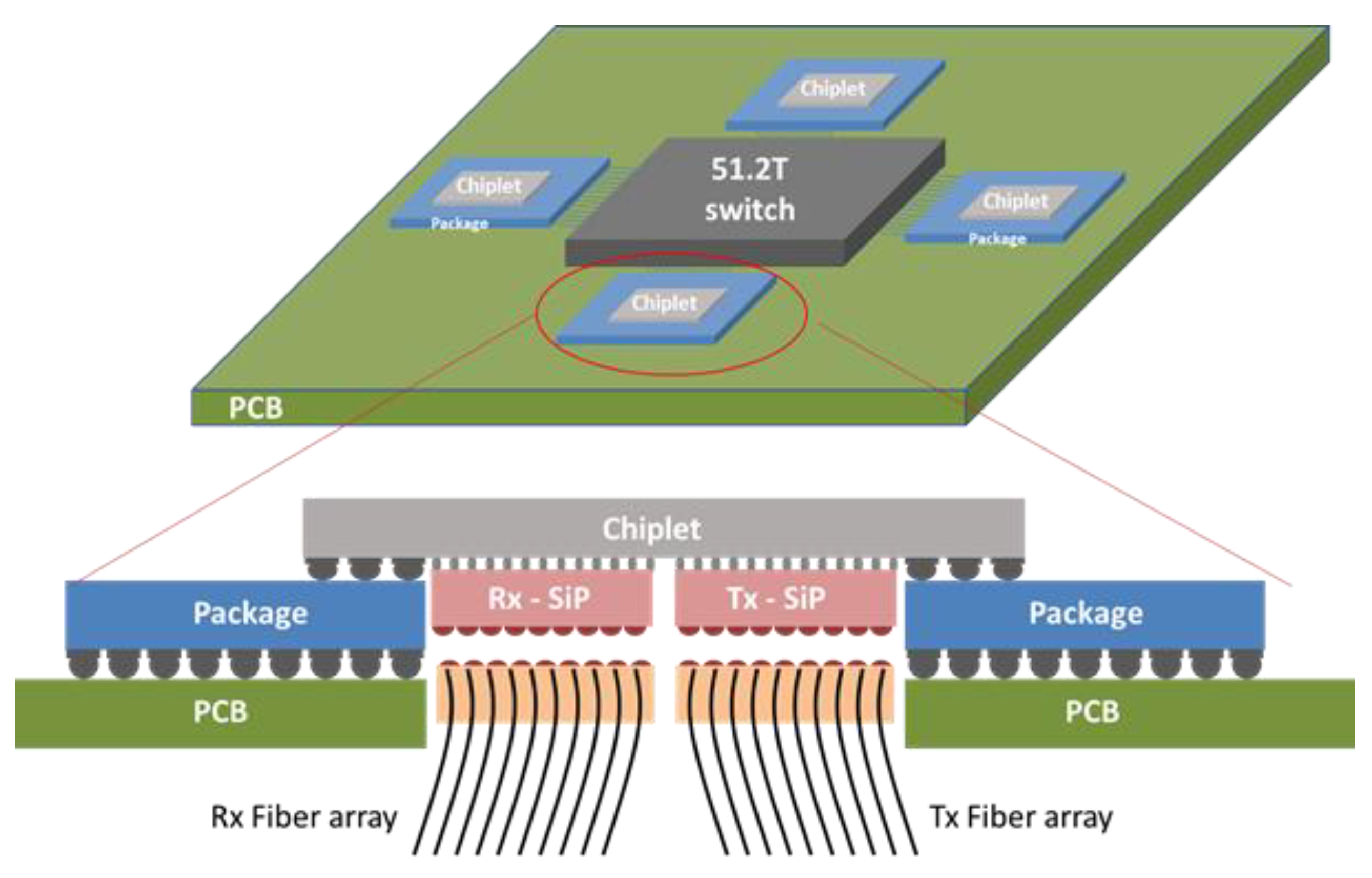

2.1. System Architecture

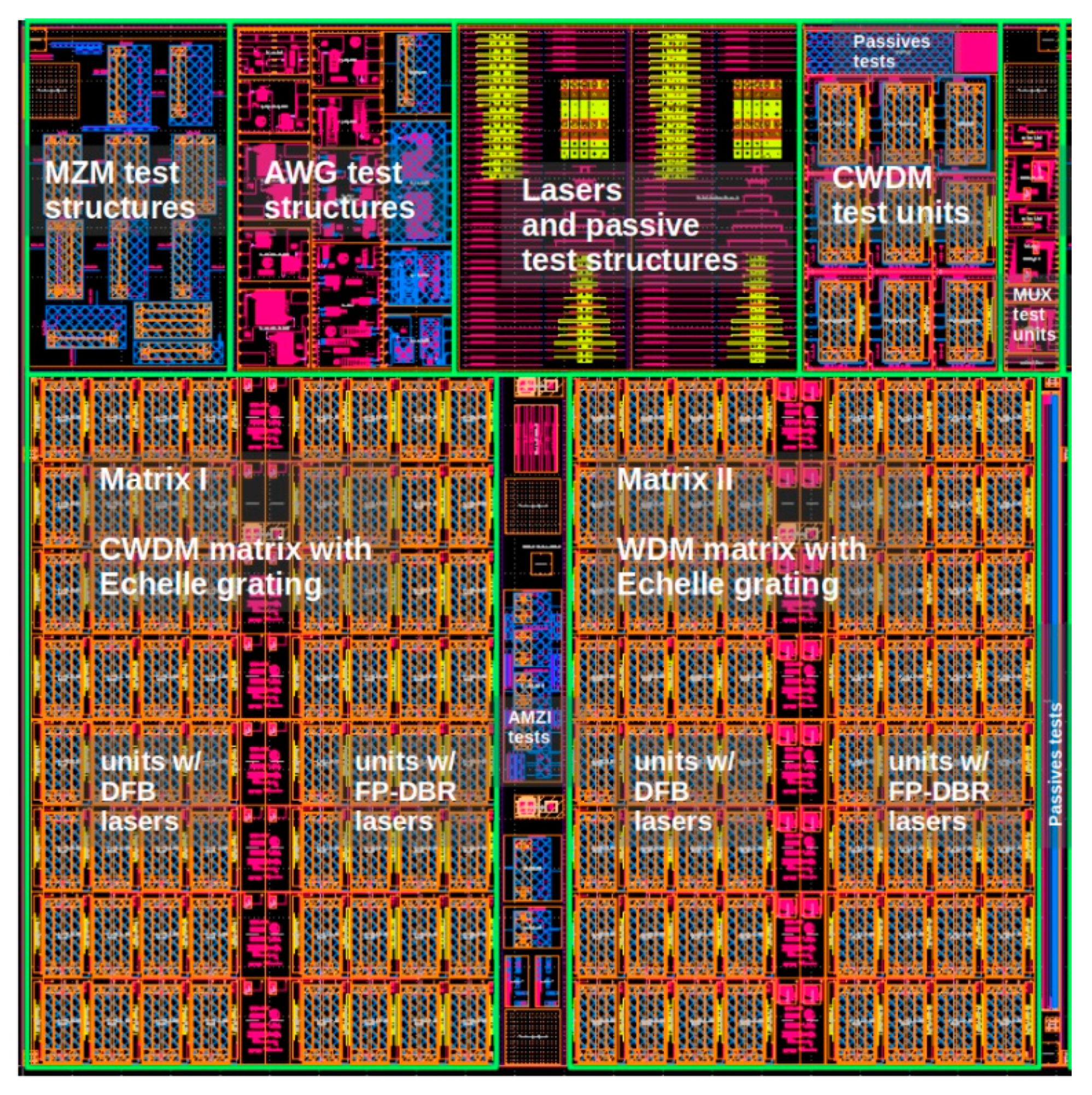

2.2. Mask Layout Integration and Design Methodology

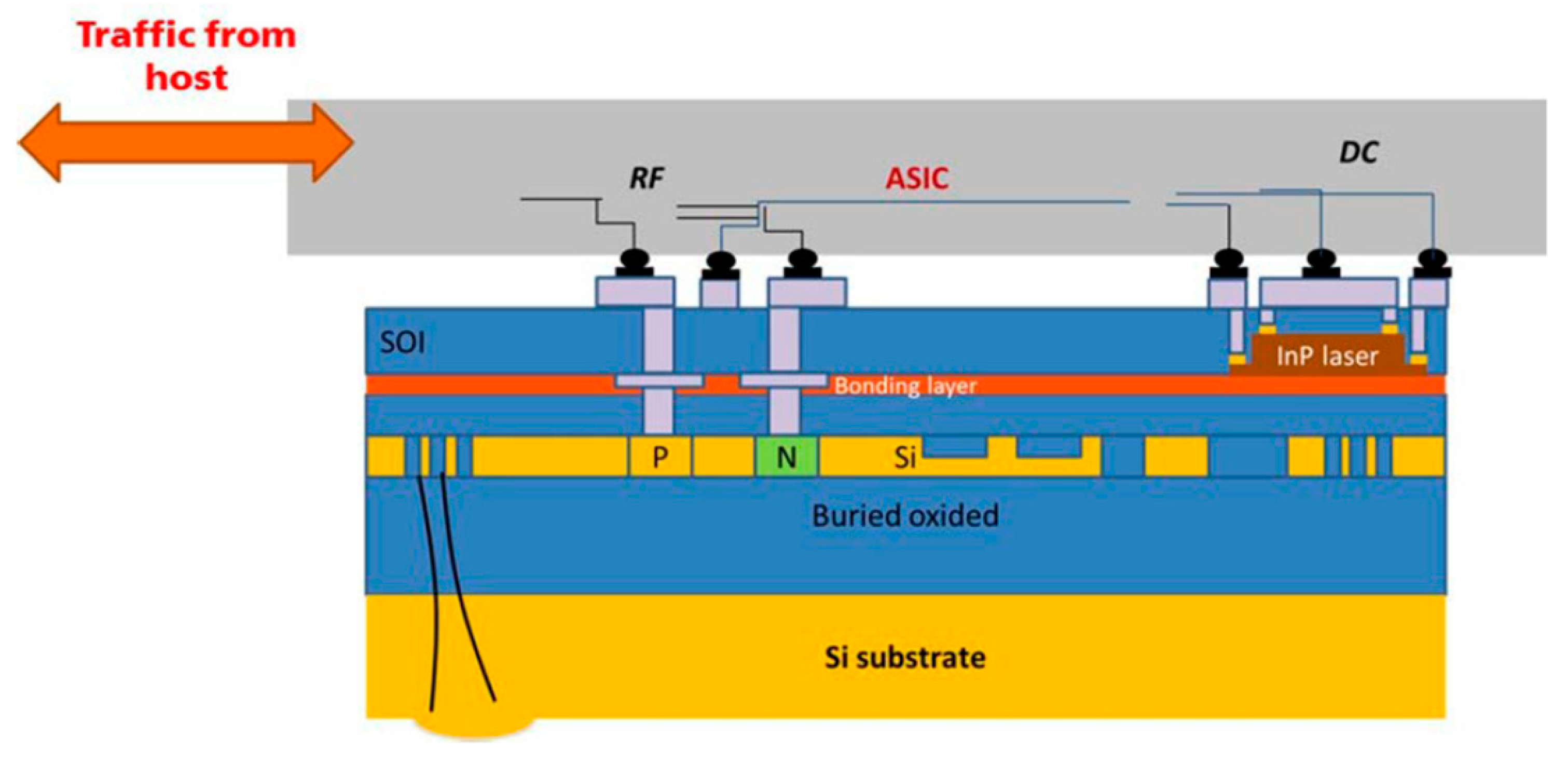

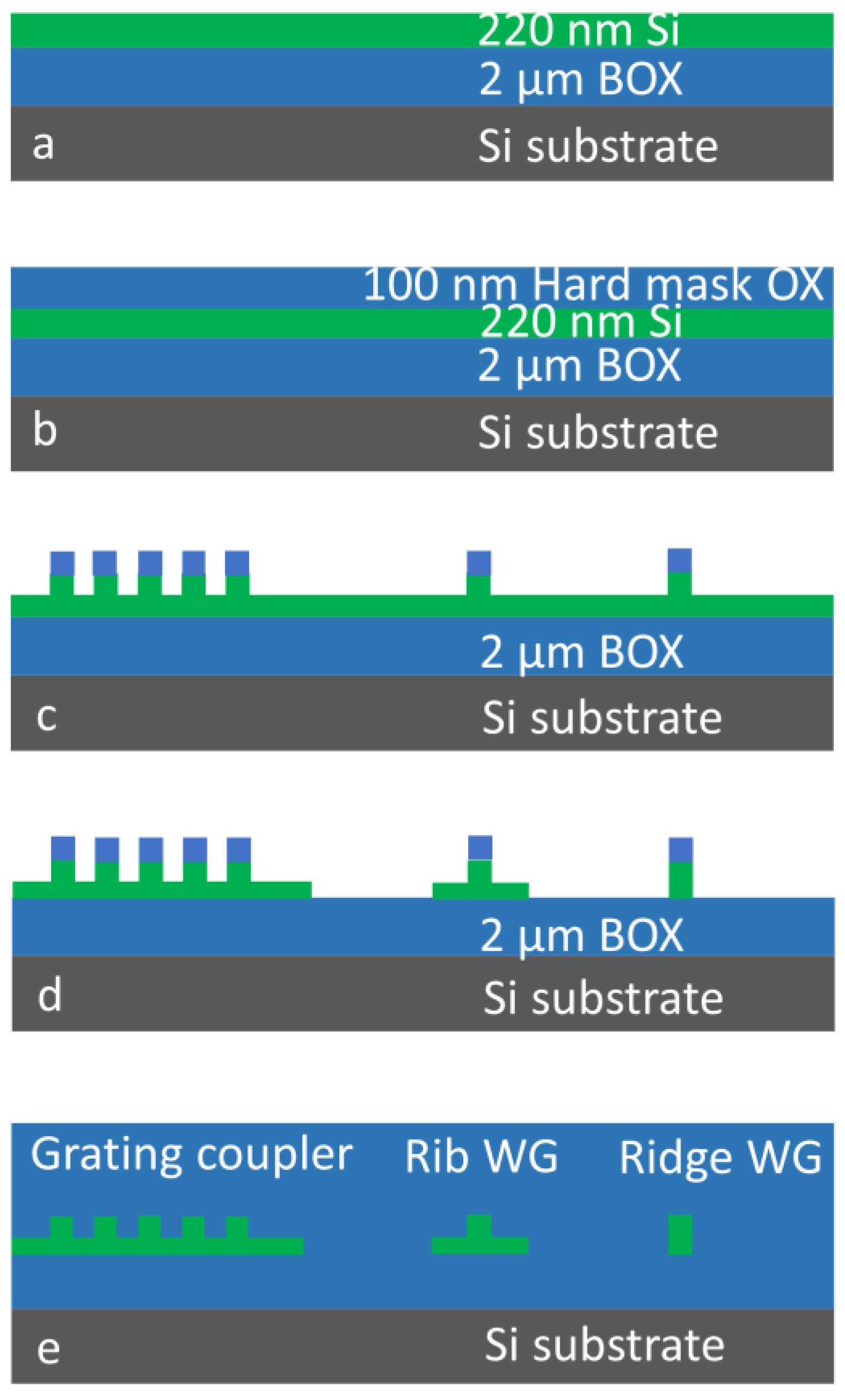

3. Silicon Photonics

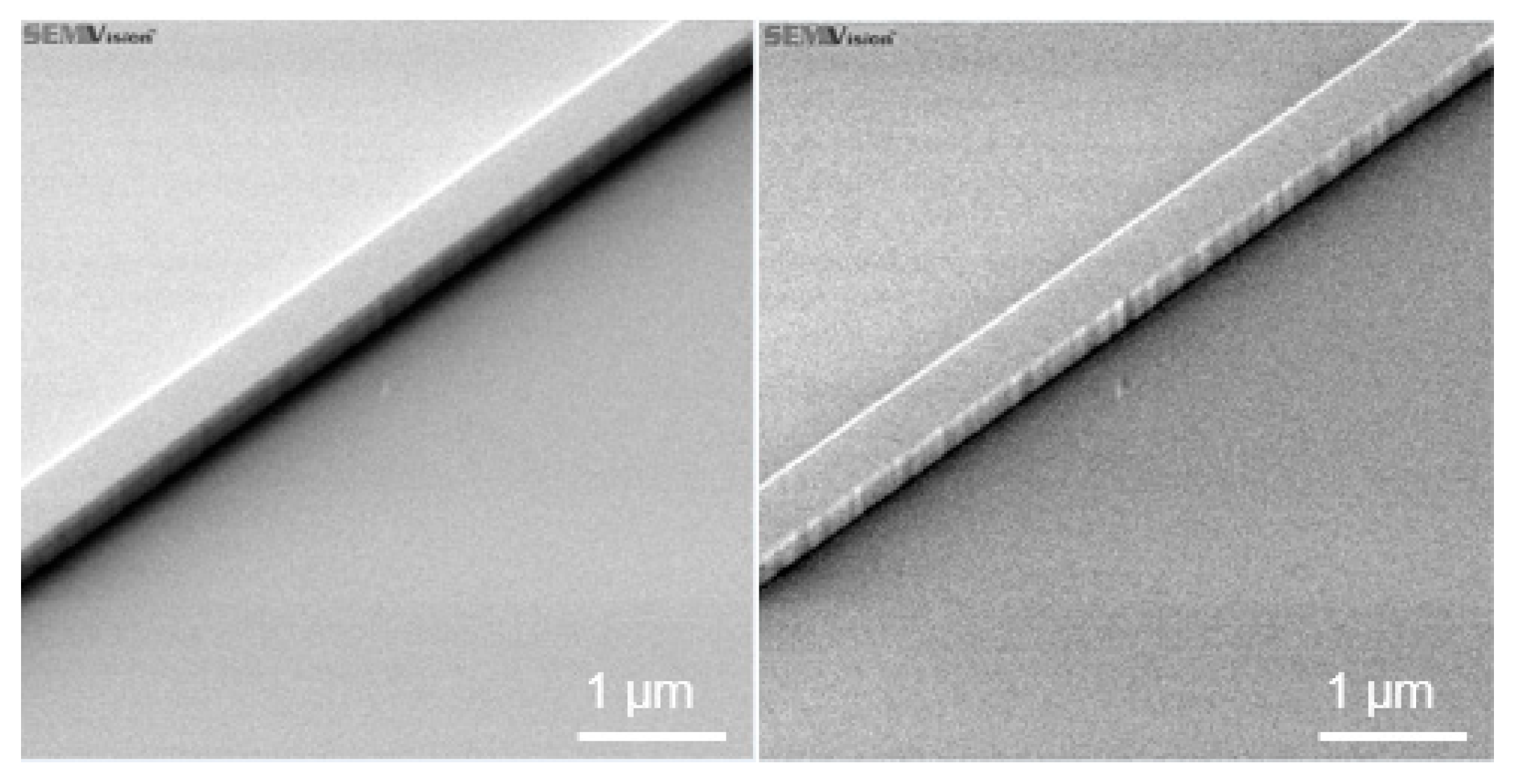

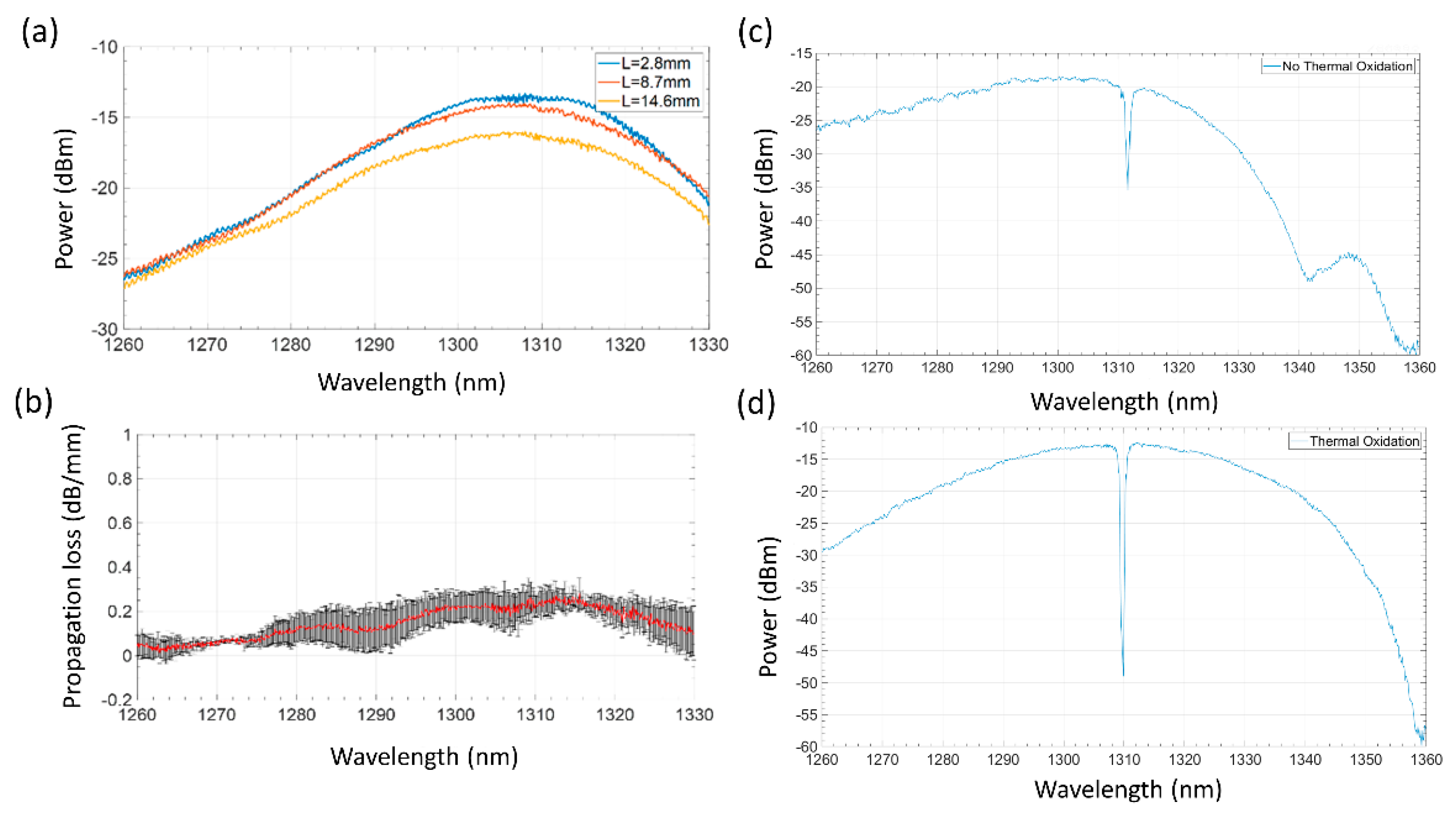

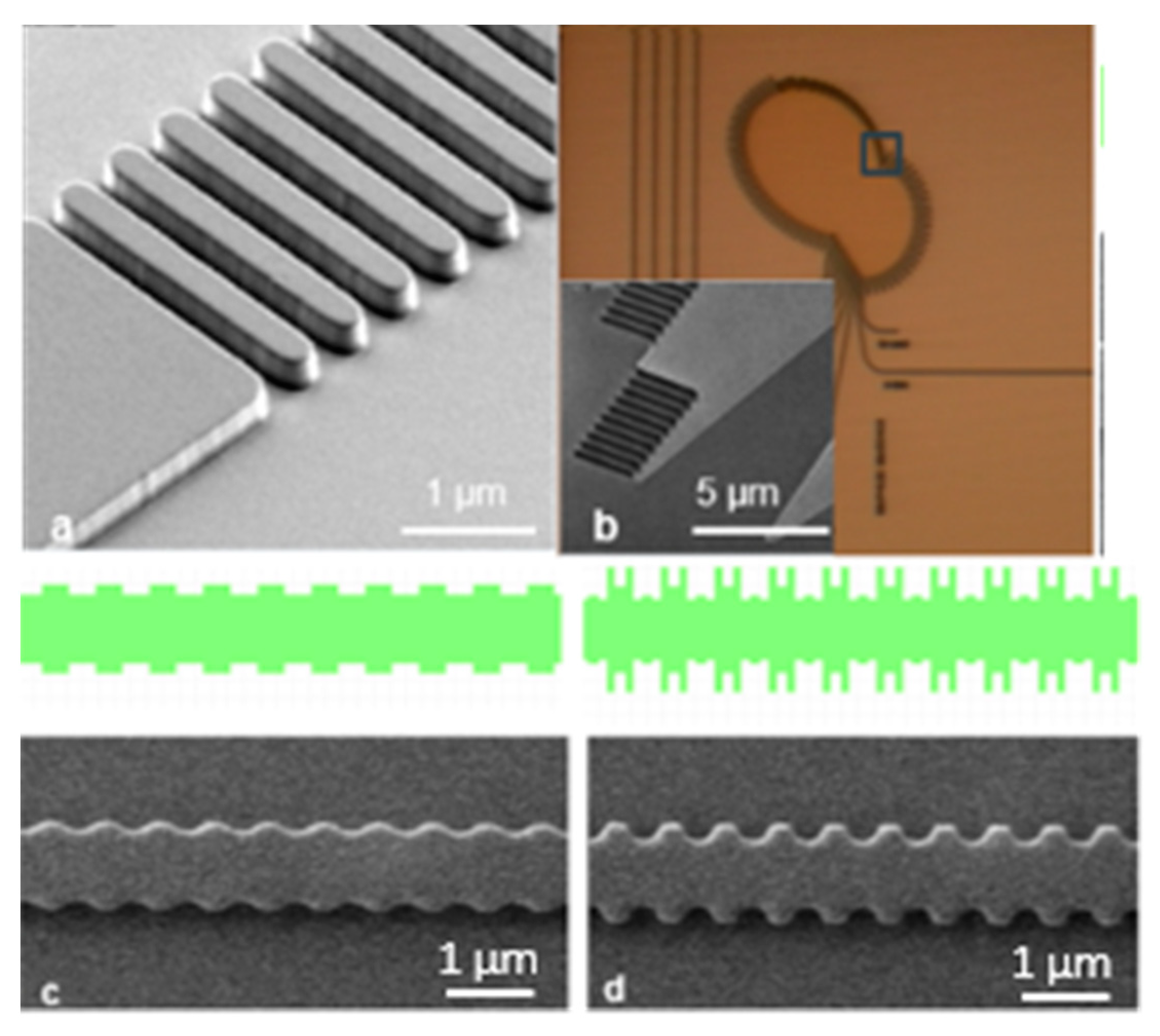

3.1. Waveguides

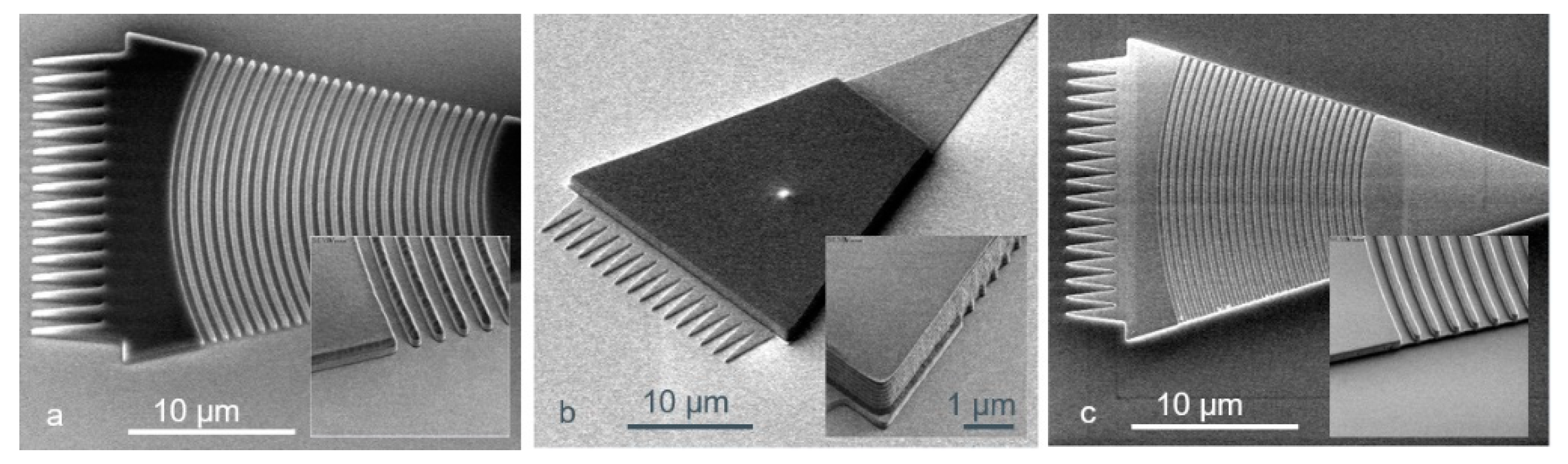

3.2. Gratings

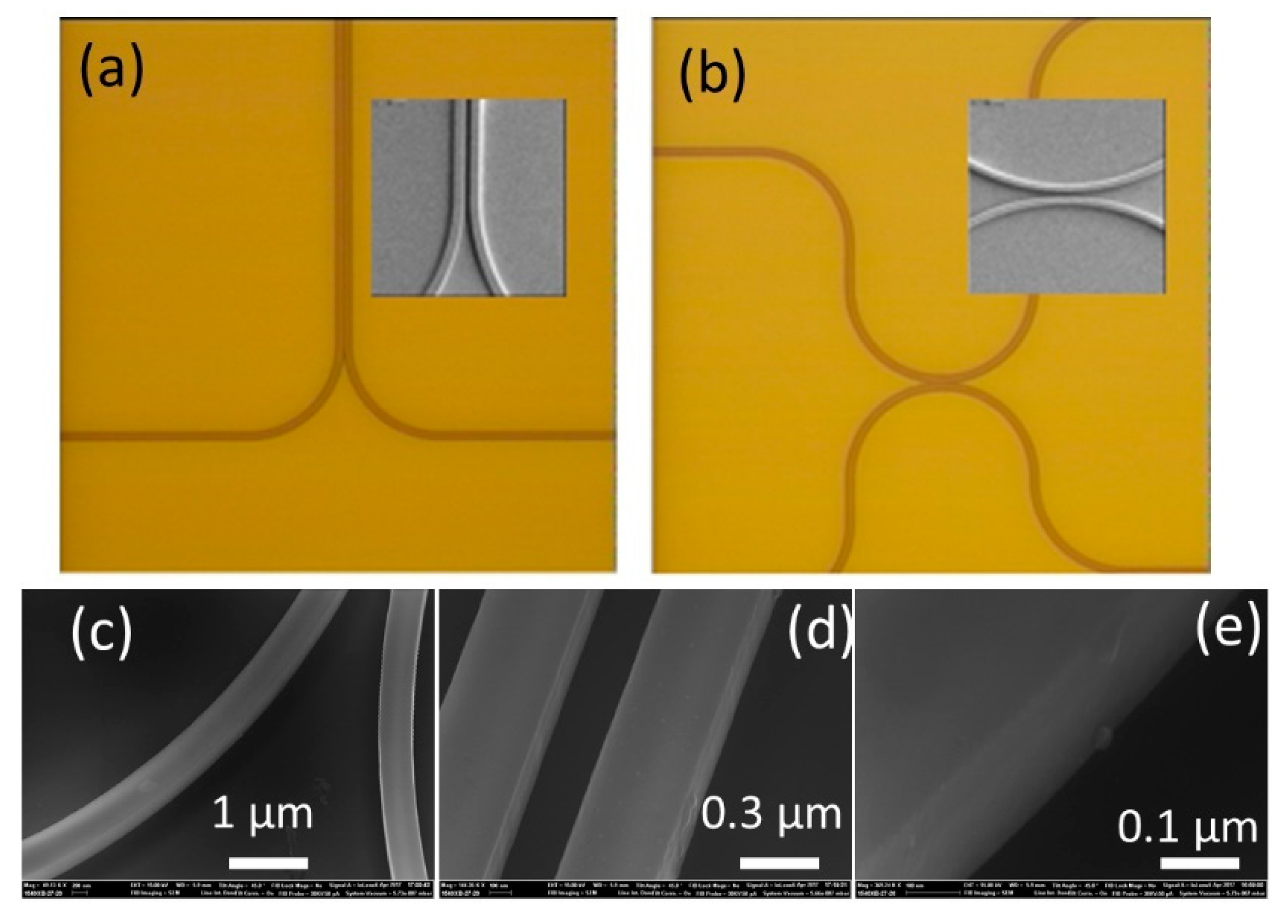

3.3. Directional Couplers

3.4. Grating Coupler

3.5. System Testing

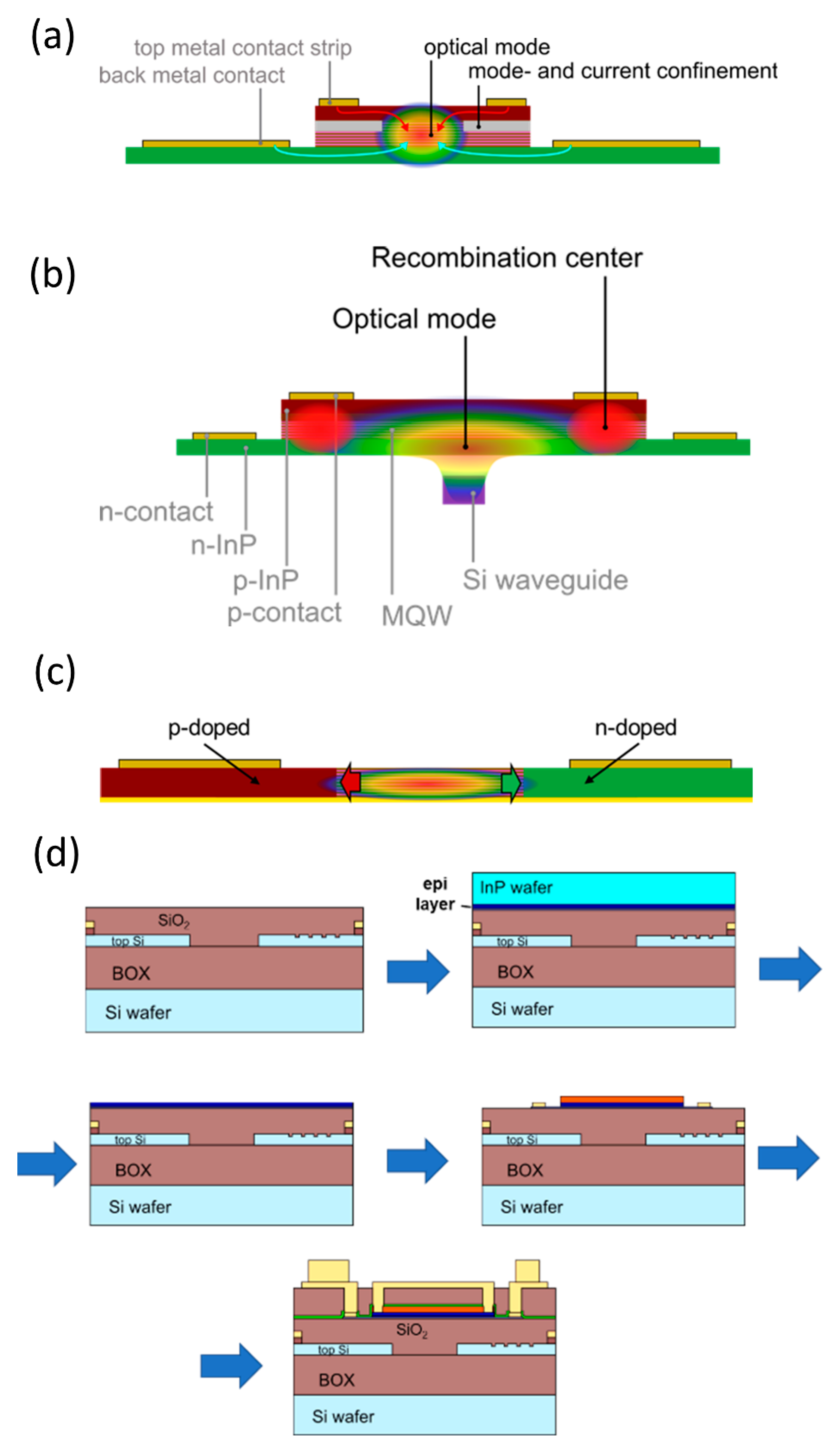

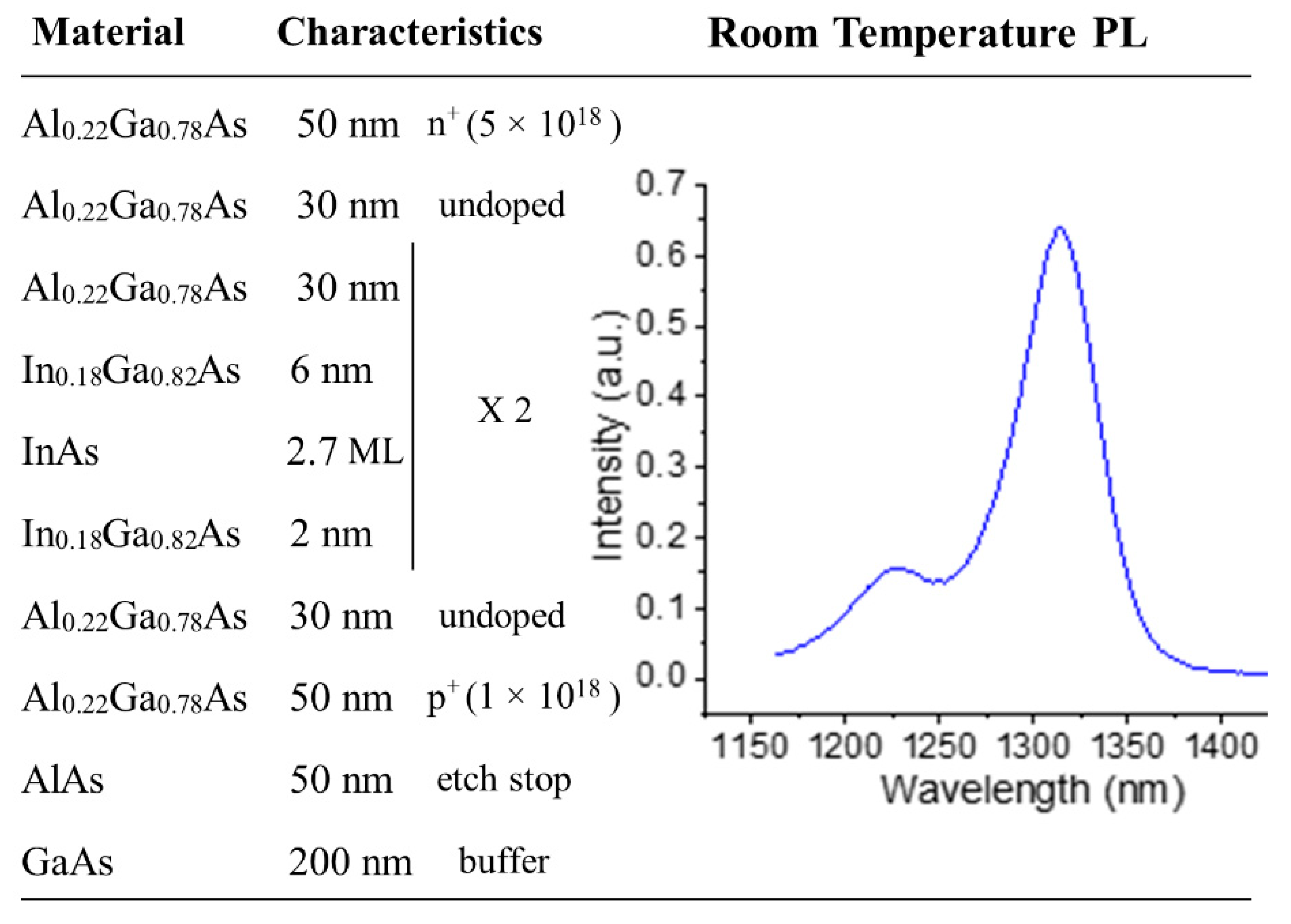

4. Light Sources

5. Modulators

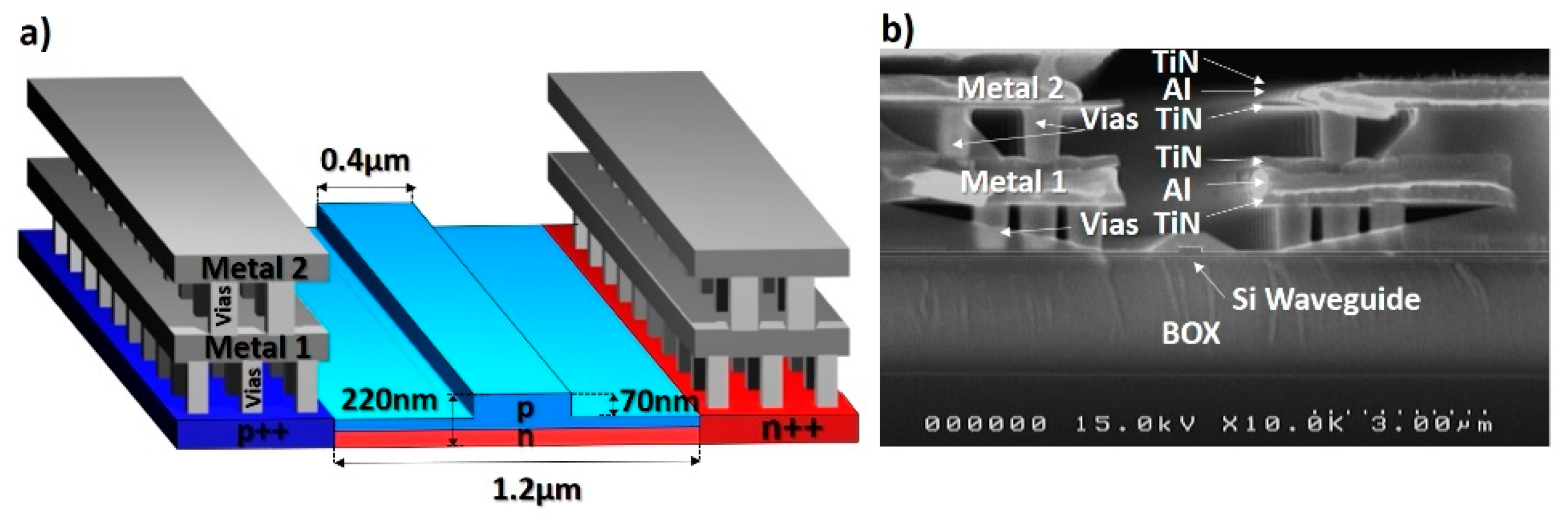

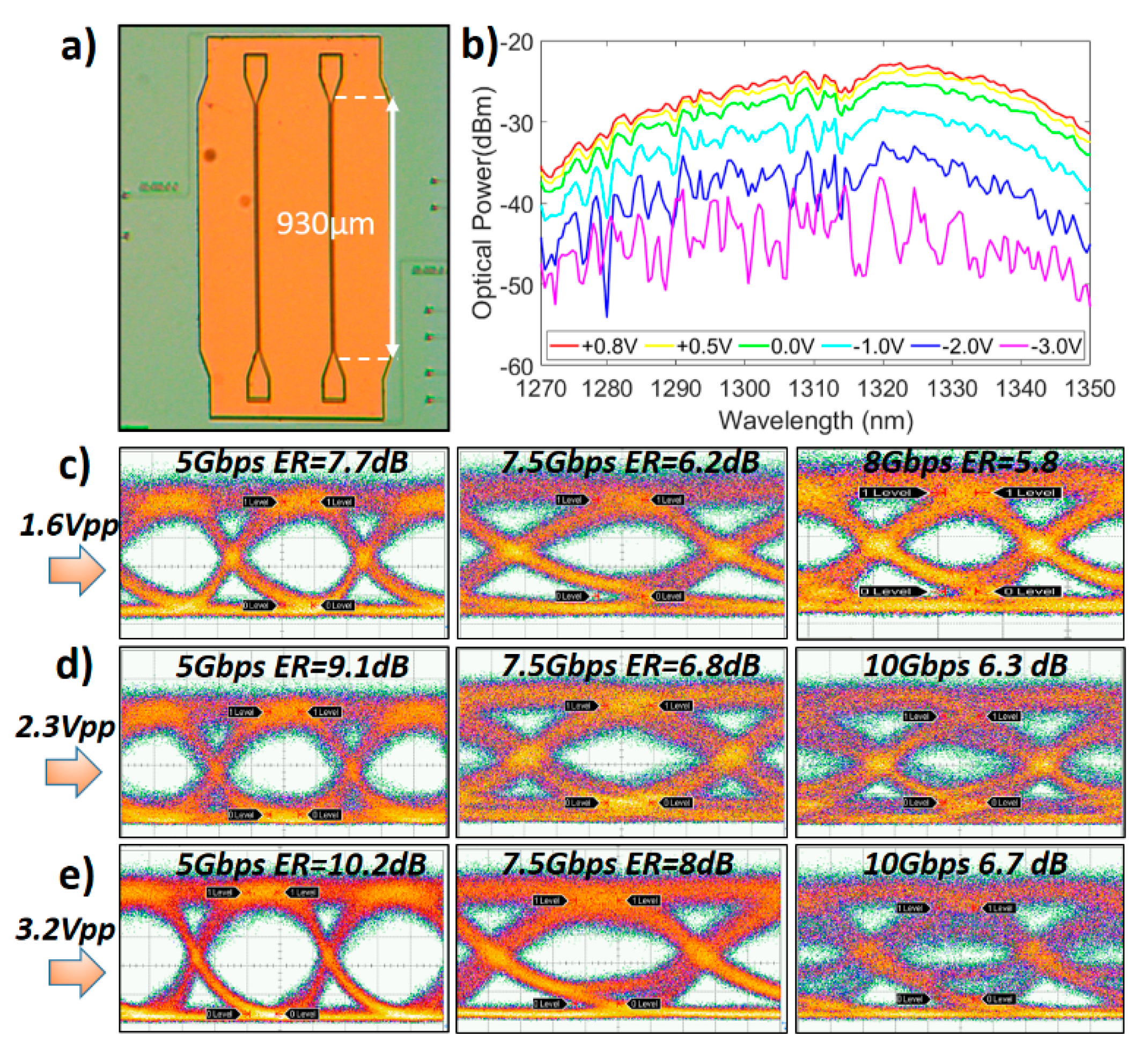

5.1. Conventional Modulators

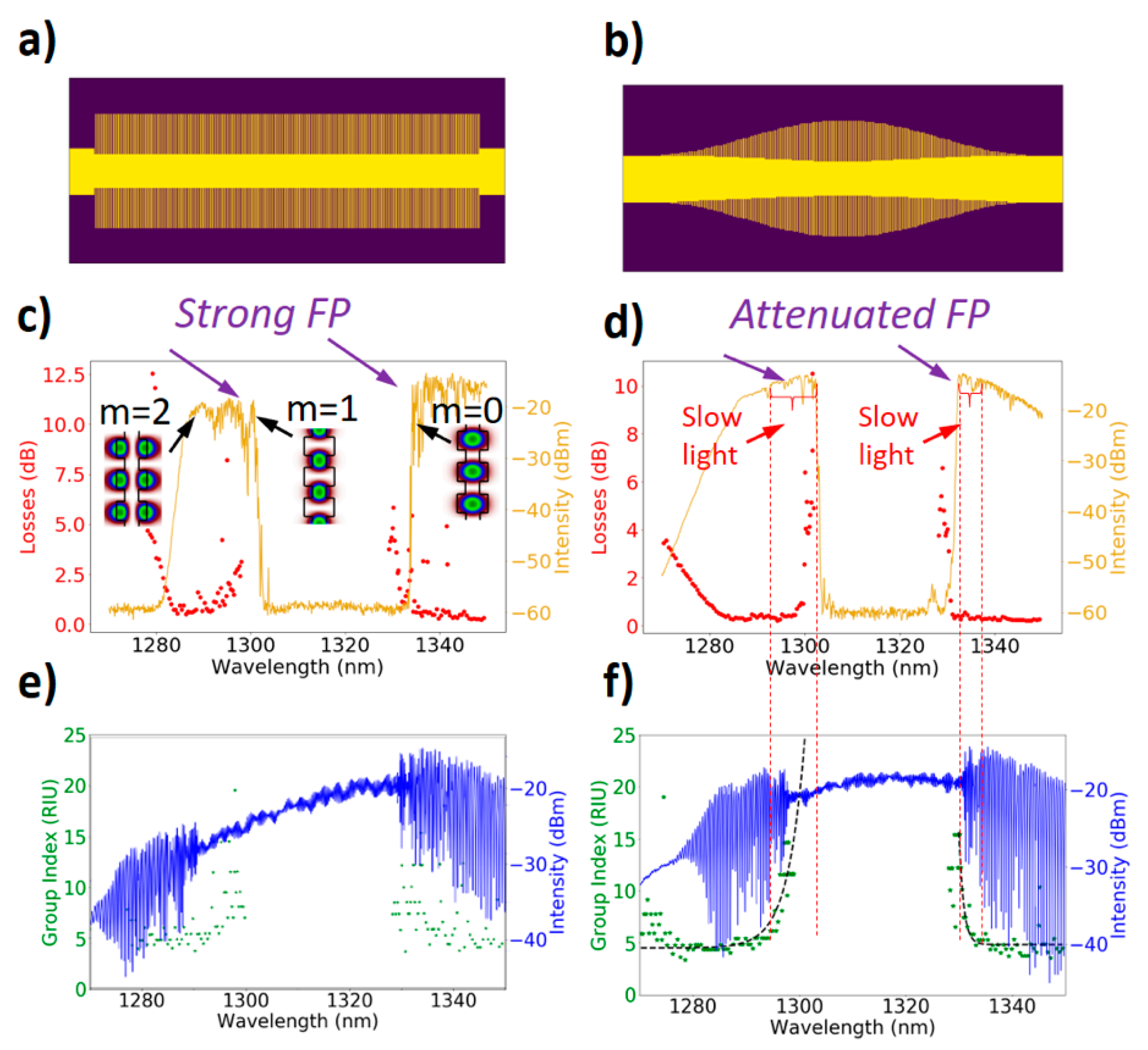

5.2. Slow Light Modulators

6. 3D Integration and Assembly

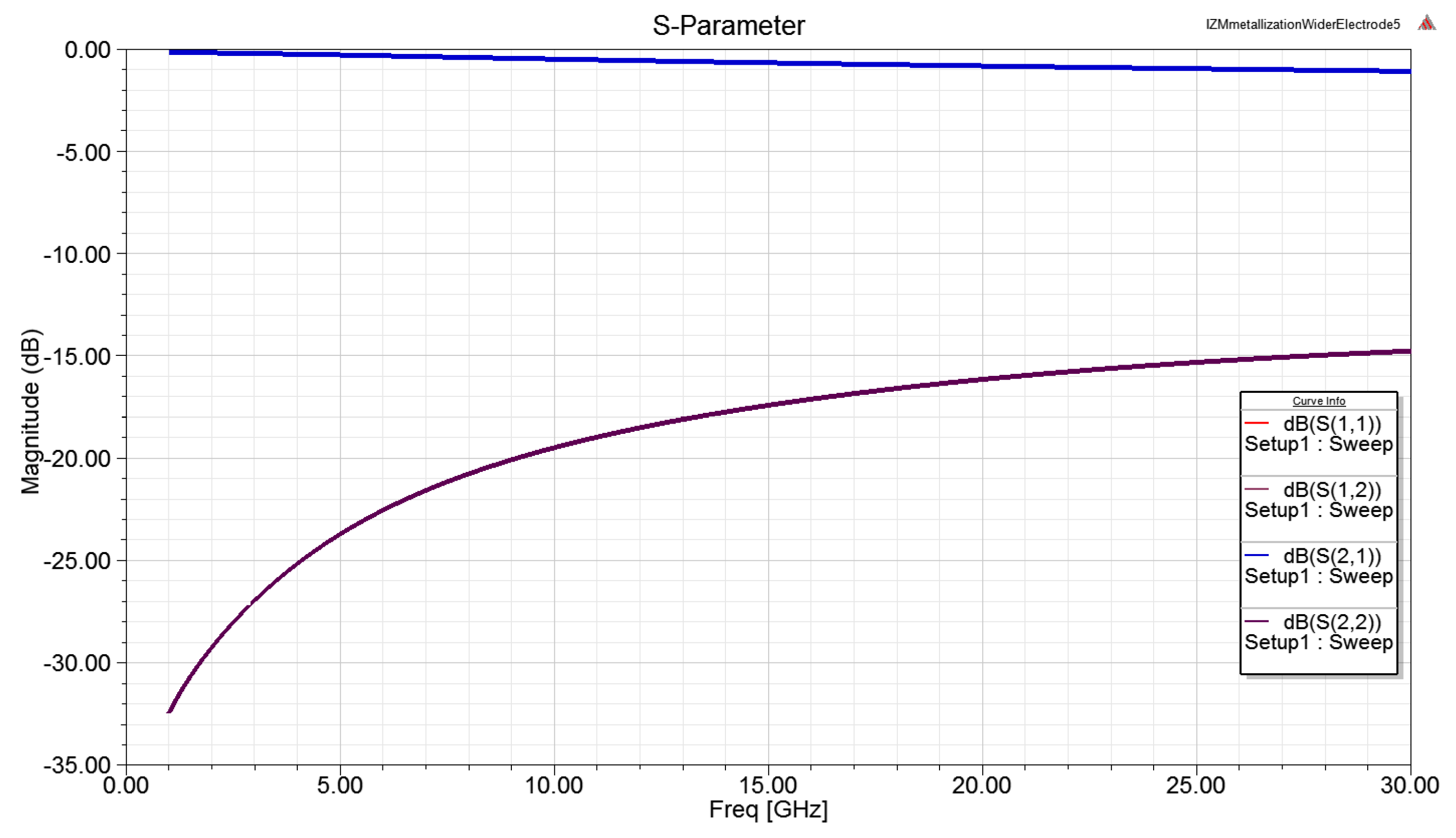

6.1. RF Modulator Electrodes Design

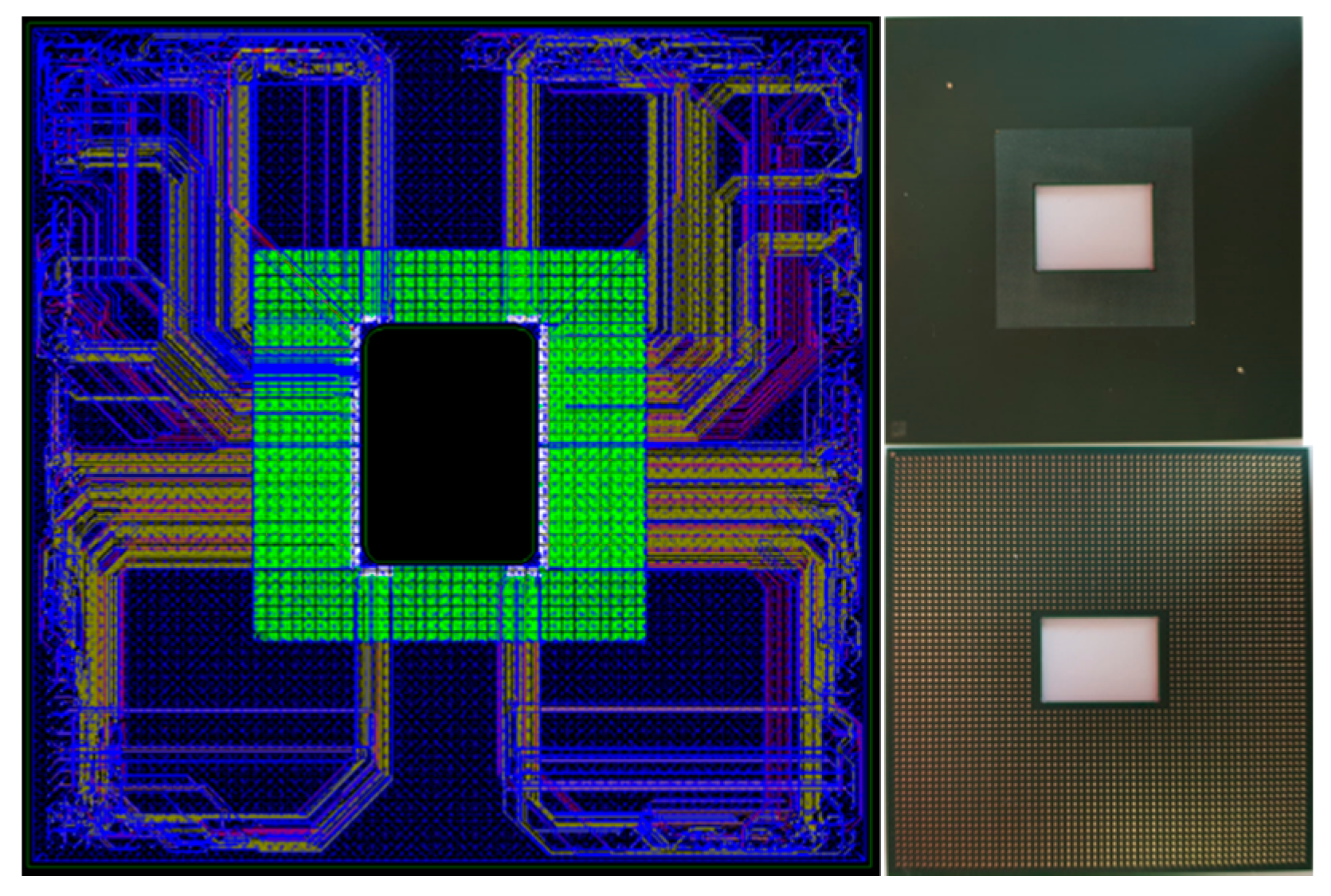

6.2. SiP Chip Assembly on a Silicon Interposer

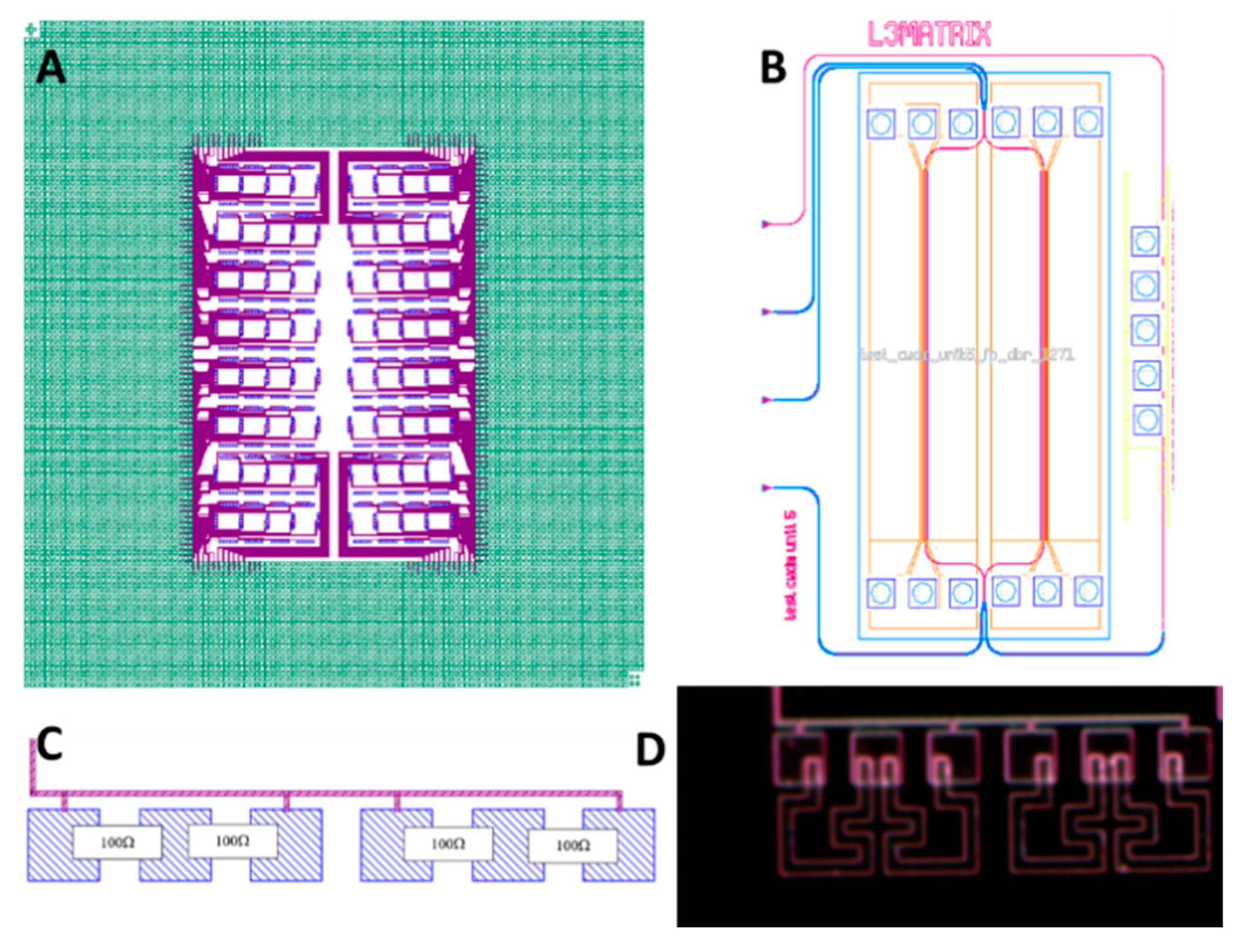

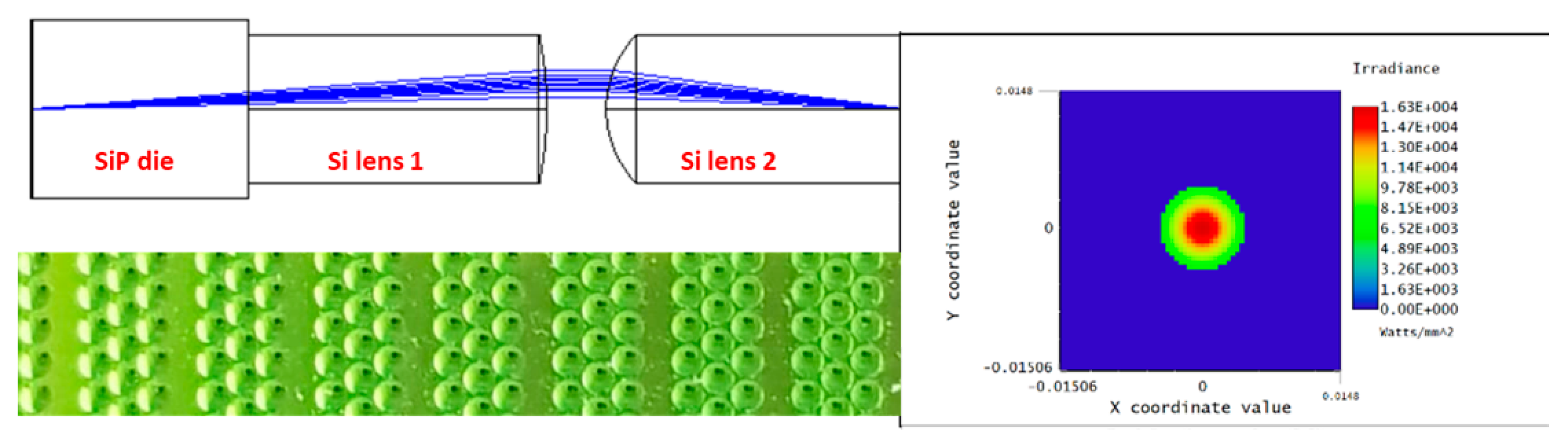

6.3. Matrix Vertical Fiber Coupling

7. Discussion and Future Perspective

7.1. Photonic Device

7.2. Device Package

8. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Greenberg, A.; Hamilton, J.R.; Jain, N.; Kandula, S.; Kim, C.; Lahiri, P.; Maltz, D.A.; Patel, P.; Sengupta, S. VL2: A scalable and flexible data center network. SIGCOMM Comput. Commun. Rev. 2009, 39, 51–62. [Google Scholar] [CrossRef]

- Cheng, Q.; Bahadori, M.; Glick, M.; Rumley, S.; Bergman, K. Recent advances in optical technologies for data centers: A review. Optica 2018, 5, 1354–1370. [Google Scholar] [CrossRef]

- Buscaino, B.; Taylor, B.D.; Kahn, J.M. Multi-Tb/s-per-Fiber Coherent Co-Packaged Optical Interfaces for Data Center Switches. J. Light. Technol. 2019, 37, 3401–3412. [Google Scholar] [CrossRef]

- Al-Fares, M.; Loukissas, A.; Vahdat, A. A scalable, commodity data center network architecture. ACM SIGCOMM Comput. Commun. Rev. 2008, 38, 63–74. [Google Scholar] [CrossRef]

- Bernabé, S.; Wilmart, Q.; Hasharoni, K.; Hassan, K.; Thonnart, Y.; Tissier, P.; Désières, Y.; Olivier, S.; Tekin, T.; Szelag, B. Silicon photonics for terabit/s communication in data centers and exascale computers. Solid-State Electron. 2021, 179, 107928. [Google Scholar] [CrossRef]

- Hasharoni, K.; Benjamin, S.; Geron, A.; Stepanov, S.; Katz, G.; Epstein, I.; Margalit, N.; Chairman, D.; Mesh, M. A 1.3 Tb/s parallel optics VCSEL link. In Optical Interconnects XIV; SPIE Press–International Society for Optics and Photonics: Bellingham, WA, USA, 2014; p. 89910C. [Google Scholar]

- Minkenberg, C.; Farrington, N.; Zilkie, A.; Nelson, D.; Lai, C.P.; Brunina, D.; Byrd, J.; Chowdhuri, B.; Kucharewski, N.; Muth, K.; et al. Reimagining datacenter topologies with integrated silicon photonics. J. Opt. Commun. Netw. 2018, 10, B126–B139. [Google Scholar] [CrossRef]

- Aoki, T.; Sekiguchi, S.; Simoyama, T.; Tanaka, S.; Nishizawa, M.; Hatori, N.; Sobu, Y.; Sugama, A.; Akiyama, T.; Hayakawa, A.; et al. Low-Crosstalk Simultaneous 16-Channel × 25 Gb/s Operation of High-Density Silicon Photonics Optical Transceiver. J. Light. Technol. 2018, 36, 1262–1267. [Google Scholar] [CrossRef]

- De Dobbelaere, P.; Dahl, A.; Mekis, A.; Chase, B.; Weber, B.; Welch, B.; Foltz, D.; Armijo, G.; Masini, G.; McGee, G.; et al. Advanced silicon photonics technology platform leveraging a semiconductor supply chain. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 34.1.1–34.1.4. [Google Scholar]

- Stojanović, V.; Ram, R.J.; Popović, M.; Lin, S.; Moazeni, S.; Wade, M.; Sun, C.; Alloatti, L.; Atabaki, A.; Pavanello, F.; et al. Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes. Opt. Express 2018, 26, 13106–13121. [Google Scholar] [CrossRef]

- L3MATRIX. Available online: https://l3matrix.eu/ (accessed on 1 June 2021).

- Shen, X.; Chen, B.; Zhu, Y.; Shi, W. Silicon photonic integrated circuits and its application in data center. In Proceedings of the 7th Symposium on Novel Photoelectronic Detection Technology and Applications, Kunming, China, 5–7 November 2020; Volume 11763, p. 1176380. [Google Scholar]

- Luxtera (Now Cisco). Mid-Board Optic Transceivers. Available online: http://www.luxtera.com/embedded-optics/ (accessed on 1 June 2021).

- Maniotis, P.; Terzenidis, N.; Siokis, A.; Christodoulopoulos, K.; Varvarigos, E.; Immonen, M.; Yan, H.J.; Zhu, L.X.; Hasharoni, K.; Pitwon, R.; et al. Application-Oriented On-Board Optical Technologies for HPCs. J. Light. Technol. 2017, 35, 3197–3213. [Google Scholar] [CrossRef]

- Bernabe, S.; Rida, K.; Pares, G.; Castany, O.; Fowler, D.; Kopp, C.; Waltener, G.; Jimenez, J.L.G.; Menezo, S. On-Board Silicon Photonics-Based Transceivers With 1-Tb/s Capacity. IEEE Trans. Compon. Packag. Manuf. Technol. 2016, 6, 1018–1025. [Google Scholar] [CrossRef]

- Bogaerts, W.; Chrostowski, L. Silicon photonics circuit design: Methods, tools and challenges. Laser Photonics Rev. 2018, 12, 1700237. [Google Scholar] [CrossRef]

- Nazca-Design. Available online: Nazca-design.org (accessed on 9 April 2021).

- Papakonstantinou, I.; James, R.; Selviah, D.R. Radiation and bound-mode propagation in rectangular, multimode dielectric, channel waveguides with sidewall roughness. J. Light. Technol. 2009, 27, 4151–4163. [Google Scholar] [CrossRef]

- Cai, J.; Lim, P.H.; Ishikawa, Y.; Wada, K. Silicon waveguide sidewall smoothing by resist reflowing. J. Nonlinear Opt. Phys. Mater. 2010, 19, 801–809. [Google Scholar] [CrossRef]

- Gao, F.; Wang, Y.; Cao, G.; Jia, X.; Zhang, F. Improvement of sidewall surface roughness in silicon-on-insulator rib waveguides. Appl. Phys. A 2005, 81, 691–694. [Google Scholar] [CrossRef]

- Wang, P.; Michael, A.; Kwok, C.Y. Fabrication of sub-micro silicon waveguide with vertical sidewall and reduced roughness for low loss applications. Procedia Eng. 2014, 87, 979–982. [Google Scholar] [CrossRef][Green Version]

- Horst, F.; Green, W.; Offrein, B.; Vlasov, Y. Silicon-on-Insulator Echelle Grating WDM Demultiplexers with Two Stigmatic Points. IEEE Photonics Technol. Lett. 2009, 21, 1743–1745. [Google Scholar] [CrossRef]

- Fang, A.W.; Park, H.; Cohen, O.; Jones, R.; Paniccia, M.J.; Bowers, J.E. Electrically pumped hybrid AlGaInAs-silicon evanescent laser. Opt. Express 2006, 14, 9203–9210. [Google Scholar] [CrossRef]

- Seifried, M.; Villares, G.; Baumgartner, Y.; Hahn, H.; Halter, M.; Horst, F.; Caimi, D.; Caër, C.; Sousa, M.; Dangel, R.F.; et al. Monolithically Integrated CMOS-Compatible III–V on Silicon Lasers. IEEE J. Sel. Top. Quantum Electron. 2018, 24, 1–9. [Google Scholar] [CrossRef]

- Hahn, H.; Sousa, M.; Czornomaz, L. Low-resistive, CMOS-compatible ohmic contact schemes to moderately doped n-InP. J. Phys. D Appl. Phys. 2017, 50, 235102. [Google Scholar] [CrossRef]

- Batude, P.; Fenouillet-Beranger, C.; Pasini, L.; Lu, V.; Deprat, F.; Brunet, L.; Sklenard, B.; Piegas-Luce, F.; Casse, M.; Mathieu, B.; et al. 3DVLSI with CoolCube process: An alternative path to scaling. In Proceedings of the 2015 Symposium on VLSI Technology, Kyoto, Japan, 15–18 June 2015; pp. T48–T49. [Google Scholar]

- Fujii, T.; Takeda, K.; Diamantopoulos, N.-P.; Kanno, E.; Hasebe, K.; Nishi, H.; Nakao, R.; Kakitsuka, T.; Matsuo, S. Heterogeneously Integrated Membrane Lasers on Si Substrate for Low Operating Energy Optical Links. IEEE J. Sel. Top. Quantum Electron. 2017, 24, 1–8. [Google Scholar] [CrossRef]

- Baumgartner, Y.; Seifried, M.; Caër, C.; Stark, P.; Caimi, D.; Faist, J.; Offrein, B.; Czornomaz, L. Novel CMOS-Compatible Ultralow Capacitance Hybrid III-V/Si Photodetectors Tested up to 32 Gbps NRZ. In Proceedings of the Optical Fiber Communication Conference (OFC), San Diego, CA, USA, 3–7 March 2019; pp. 1–3. [Google Scholar]

- Papatryfonos, K.; Rodary, G.; David, C.; Lelarge, F.; Ramdane, A.; Girard, J.-C. One-Dimensional Nature of InAs/InP Quantum Dashes Revealed by Scanning Tunneling Spectroscopy. Nano Lett. 2015, 15, 4488–4497. [Google Scholar] [CrossRef]

- Papatryfonos, K.; Saladukha, D.; Merghem, K.; Joshi, S.; Lelarge, F.; Bouchoule, S.; Kazazis, D.; Guilet, S.; Le Gratiet, L.; Ochalski, T.J.; et al. Laterally coupled distributed feedback lasers emitting at 2 μm with quantum dash active region and high-duty-cycle etched semiconductor gratings. J. Appl. Phys. 2017, 121, 053101. [Google Scholar] [CrossRef]

- Papatryfonos, K.; Joshi, S.; Merghem, K.; Bouchoule, S.; Guilet, S.; Le Gratiet, L.; Martinez, A.; Ramdane, A. Quantum dash based lasers for gas sensing. In Proceedings of the 26th International Conference on Indium Phosphide and Related Materials (IPRM), Montpellier, France, 11–15 May 2014; pp. 1–2. [Google Scholar]

- Mukai, K.; Nakata, Y.; Otsubo, K.; Sugawara, M.; Yokoyama, N.; Ishikawa, H. 1.3-/spl mu/m CW lasing characteristics of self-assembled InGaAs-GaAs quantum dots. IEEE J. Quantum Electron. 2000, 36, 472–478. [Google Scholar] [CrossRef]

- Gerschutz, F.; Fischer, M.; Koeth, J.; Chacinski, M.; Schatz, R.; Kjebon, O.; Kovsh, A.; Krestnikov, I.; Forchel, A. Temperature insensitive 1.3 µm InGaAs/GaAs quantum dot distributed feedback lasers for 10 Gbit/s transmission over 21 km. Electron. Lett. 2006, 42, 1457. [Google Scholar] [CrossRef]

- Hu, Y.; Liang, D.; Mukherjee, K.; Li, Y.; Zhang, C.; Kurczveil, G.; Huang, X.; Beausoleil, R.G. III/V-on-Si MQW lasers by using a novel photonic integration method of regrowth on a bonding template. Light Sci. Appl. 2019, 8, 1–9. [Google Scholar] [CrossRef]

- Chen, S.; Li, W.; Wu, J.; Jiang, Q.; Tang, M.; Shutts, S.; Elliott, S.N.; Sobiesierski, A.; Seeds, A.; Ross, I.; et al. Electrically pumped continuous-wave III–V quantum dot lasers on silicon. Nat. Photonics 2016, 10, 307–311. [Google Scholar] [CrossRef]

- Zhou, T.; Tang, M.; Xiang, G.; Xiang, B.; Hark, S.; Martin, M.; Baron, T.; Pan, S.; Park, J.-S.; Liu, Z.; et al. Continuous-wave quantum dot photonic crystal lasers grown on on-axis Si(001). Nat. Commun. 2020, 11, 1–7. [Google Scholar] [CrossRef]

- Wang, J.; Bai, Y.; Liu, H.; Cheng, Z.; Tang, M.; Chen, S.; Wu, J.; Papatryfonos, K.; Liu, Z.; Huang, Y. Optimization of 1.3 μm InAs/GaAs quantum dot lasers epitaxially grown on silicon: Taking the optical loss of metamorphic epilayers into account. Laser Phys. 2018, 28, 126206. [Google Scholar] [CrossRef]

- D’Auria, M.; Otter, W.J.; Hazell, J.; Gillatt, B.T.W.; Long-Collins, C.; Ridler, N.M.; Lucyszyn, S. 3-D Printed Metal-Pipe Rectangular Waveguides. IEEE Trans. Compon. Packag. Manuf. Technol. 2015, 5, 1339–1349. [Google Scholar] [CrossRef]

- Papatryfonos, K.; Angelova, T.; Brimont, A.; Reid, B.; Guldin, S.; Smith, P.R.; Tang, M.; Li, K.; Seeds, A.J.; Liu, H.; et al. Refractive indices of MBE-grown AlxGa(1−x) As ternary alloys in the transparent wavelength region. AIP Adv. 2021, 11, 025327. [Google Scholar] [CrossRef]

- Watts, M.R.; Zortman, W.A.; Trotter, D.C.; Young, R.W.; Lentine, A.L. Low-voltage, compact, depletion-mode, silicon machzehnder modulator. IEEE J. Sel. Top. Quantum Electron. 2010, 16, 159–164. [Google Scholar] [CrossRef]

- Zanzi, A.; Vagionas, C.; Griol, A.; Rosa, A.; Lechago, S.; Moralis-Pegios, M.; Vyrsokinos, K.; Pleros, N.; Kraft, J.; Sidorov, V.; et al. Alignment tolerant low voltage 0.23 V.cm push-pull silicon photonic switches based on a vertical pn junction. Opt. Express 2019, 27, 32409–32426. [Google Scholar] [CrossRef] [PubMed]

- Liu, A.; Liao, L.; Rubin, D.; Nguyen, H.; Ciftcioglu, B.; Chetrit, Y.; Izhaky, N.; Paniccia, M. High-speed optical modulation based on carrier depletion in a silicon waveguide. Opt. Express 2007, 15, 660–668. [Google Scholar] [CrossRef]

- Yong, Z.; Sacher, W.D.; Huang, Y.; Mikkelsen, J.C.; Yang, Y.; Luo, X.; Dumais, P.; Goodwill, D.; Bahrami, H.; Lo, P.G.-Q.; et al. U-shaped PN junctions for efficient silicon Mach-Zehnder and microring modulators in the O-band. Opt. Express 2017, 25, 8425–8439. [Google Scholar] [CrossRef]

- Streshinsky, M.; Ding, R.; Liu, Y.; Novack, A.; Yang, Y.; Ma, Y.; Tu, X.; Chee, E.K.S.; Lim, A.E.-J.; Lo, P.G.-Q.; et al. Low power 50 Gb/s silicon traveling wave Mach-Zehnder modulator near 1300 nm. Opt. Express 2013, 21, 30350–30357. [Google Scholar] [CrossRef] [PubMed]

- Perez-Galacho, D.; Baudot, C.; Hirtzlin, T.; Messaoudène, S.; Vulliet, N.; Crozat, P.; Boeuf, F.; Vivien, L.; Marris-Morini, D. Low voltage 25 Gbps silicon Mach-Zehnder modulator in the O-band. Opt. Express 2017, 25, 11217–11222. [Google Scholar] [CrossRef]

- O’Faolain, L.; White, T.; O’Brien, D.; Yuan, X.; Settle, M.D.; Krauss, T.F. Dependence of extrinsic loss on group velocity in photonic crystal waveguides. Opt. Express 2007, 15, 13129–13138. [Google Scholar] [CrossRef]

- Rosa, A.; Verstuyft, S.; Brimont, A.; Van Thourhout, D.; Sanchis, P. Microwave index engineering for slow-wave coplanar waveguides. Sci. Rep. 2018, 8, 5672. [Google Scholar] [CrossRef] [PubMed]

- Hui, Y.; Bogaerts, W. An equivalent circuit model of the traveling wave electrode for carrier-depletion-based silicon optical modulators. J. Light. Technol. 2012, 30, 1602–1609. [Google Scholar] [CrossRef]

- Pitwon, R.C.A.; Kai, W.; Graham-Jones, J.; Papakonstantinou, I.; Baghsiahi, H.; Offrein, B.J.; Dangel, R.; Milward, D.; Selviah, D.R. FirstLight: Pluggable optical interconnect technologies for polymeric electro-optical printed circuit boards in data centers. J. Light. Technol. 2012, 30, 3316–3329. [Google Scholar] [CrossRef]

- Papakonstantinou, I.; Selviah, D.R.; Pitwon, R.C.A.; Milward, D. Low-cost, precision, self-alignment technique for coupling laser and photodiode arrays to polymer waveguide arrays on multilayer PCBs. IEEE Trans. Adv. Packag. 2008, 31, 502–511. [Google Scholar] [CrossRef]

- Terzenidis, N.; Moralis-Pegios, M.; Mourgias-Alexandris, G.; Vyrsokinos, K.; Pleros, N. High-port low-latency optical switch architecture with optical feed-forward buffering for 256-node disaggregated data centers. Opt. Express 2018, 26, 8756–8766. [Google Scholar] [CrossRef]

- Spanke, R.A. Architectures for large nonblocking optical space switches. IEEE J. Quantum Electron. 1986, 22, 964–967. [Google Scholar] [CrossRef]

- Moralis-Pegios, M.; Moralis-Pegios, M.; Mourgias-Alexandris, G.; Terzenidis, N.; Cherchi, M.; Harjanne, M.; Aalto, T.; Miliou, A.; Pleros, N.; Vyrsokinos, K. On-chip SOI delay line bank for optical buffers and time slot interchangers. IEEE Photonics Technol. Lett. 2017, 30, 31–34. [Google Scholar] [CrossRef]

- Spyropoulou, M.; Pleros, N.; Vyrsokinos, K.; Apostolopoulos, D.; Bougioukos, M.; Petrantonakis, D.; Miliou, A.; Avramopoulos, H. 40 Gb/s NRZ Wavelength Conversion using a Differentially-Biased SOA-MZI: Theory and Experiment. J. Light. Technol. 2011, 29, 1489–1499. [Google Scholar] [CrossRef]

- Terzenidis, N.; Moralis-Pegios, M.; Mourgias-Alexandris, G.; Alexoudi, T.; Vyrsokinos, K.; Pleros, N. High-Port and Low-Latency Optical Switches for Disaggregated Data Centers: The Hipoλaos Switch Architecture. J. Opt. Commun. Netw. 2018, 10, B102–B116. [Google Scholar] [CrossRef]

- Moralis-Pegios, M.; Terzenidis, N.; Mourgias-Alexandris, G.; Vyrsokinos, K.; Pleros, N. A 1024-port Optical Uni- and Multicast Packet Switch Fabric. J. Light. Technol. 2019, 37, 1415–1423. [Google Scholar] [CrossRef]

- Moralis-Pegios, M.; Terzenidis, N.; Mourgias-Alexandris, G.; Vyrsokinos, K.; Pleros, N. Multicast-Enabling Optical Switch Design Employing Si Buffering and Routing Elements. IEEE Photonics Technol. Lett. 2018, 30, 712–715. [Google Scholar] [CrossRef]

- Terzenidis, N.; Moralis-Pegios, M.; Mourgias-Alexandris, G.; Vyrsokinos, K.; Pleros, N. Multicasting in a High-Port Sub-μsec Latency Hipoλaos Optical Packet Switch. IEEE Photonics Technol. Lett. 2018, 30, 1535–1538. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Papatryfonos, K.; Selviah, D.R.; Maman, A.; Hasharoni, K.; Brimont, A.; Zanzi, A.; Kraft, J.; Sidorov, V.; Seifried, M.; Baumgartner, Y.; et al. Co-Package Technology Platform for Low-Power and Low-Cost Data Centers. Appl. Sci. 2021, 11, 6098. https://doi.org/10.3390/app11136098

Papatryfonos K, Selviah DR, Maman A, Hasharoni K, Brimont A, Zanzi A, Kraft J, Sidorov V, Seifried M, Baumgartner Y, et al. Co-Package Technology Platform for Low-Power and Low-Cost Data Centers. Applied Sciences. 2021; 11(13):6098. https://doi.org/10.3390/app11136098

Chicago/Turabian StylePapatryfonos, Konstantinos, David R. Selviah, Avi Maman, Kobi Hasharoni, Antoine Brimont, Andrea Zanzi, Jochen Kraft, Victor Sidorov, Marc Seifried, Yannick Baumgartner, and et al. 2021. "Co-Package Technology Platform for Low-Power and Low-Cost Data Centers" Applied Sciences 11, no. 13: 6098. https://doi.org/10.3390/app11136098

APA StylePapatryfonos, K., Selviah, D. R., Maman, A., Hasharoni, K., Brimont, A., Zanzi, A., Kraft, J., Sidorov, V., Seifried, M., Baumgartner, Y., Horst, F., Offrein, B. J., Lawniczuk, K., Broeke, R. G., Terzenidis, N., Mourgias-Alexandris, G., Tang, M., Seeds, A. J., Liu, H., ... Tekin, T. (2021). Co-Package Technology Platform for Low-Power and Low-Cost Data Centers. Applied Sciences, 11(13), 6098. https://doi.org/10.3390/app11136098