Independent Double-Boost Interleaved Converter with Three-Level Output

Abstract

:1. Introduction

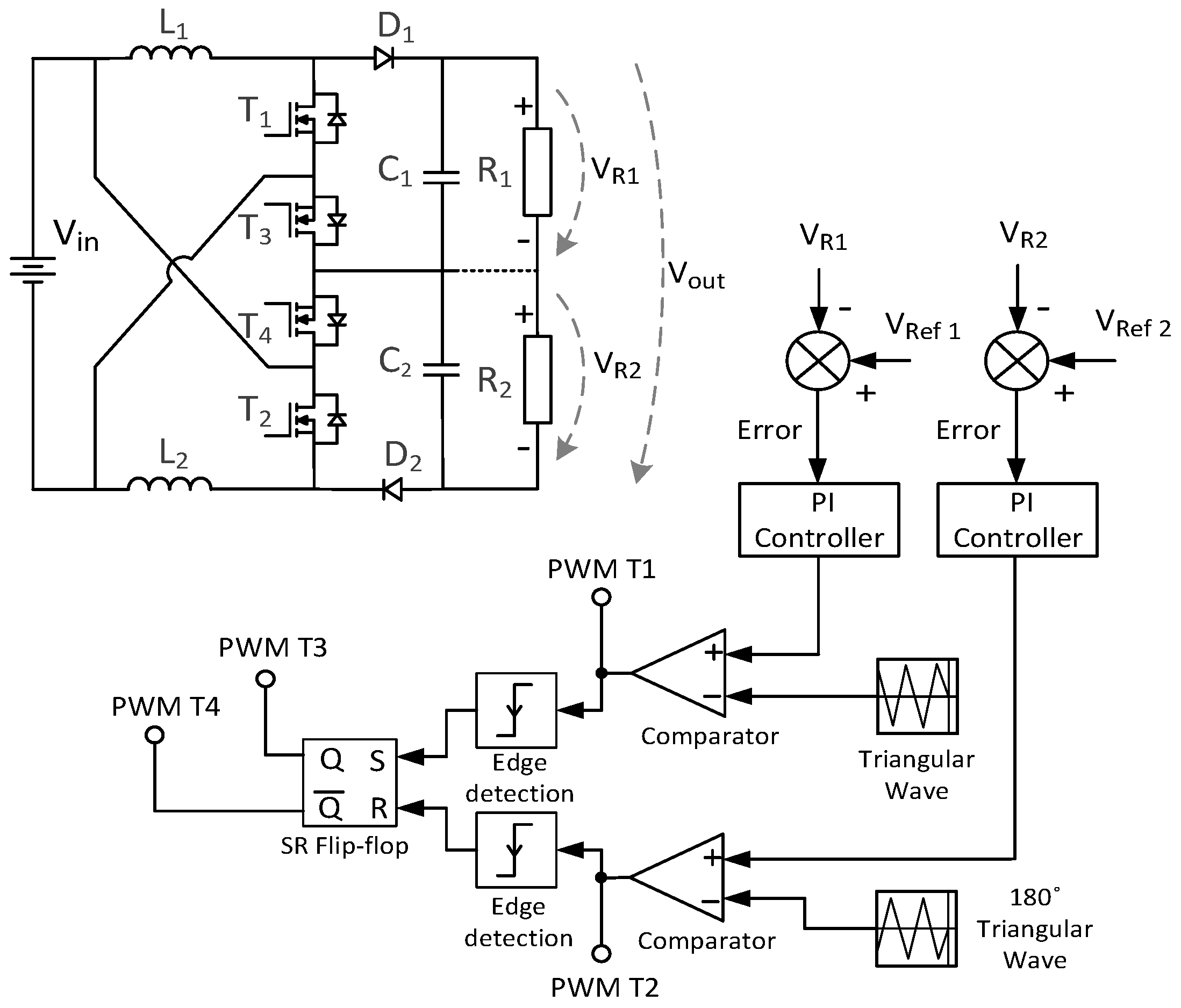

2. Converter Topology Analysis

2.1. Converter Topology, Switching States, and Presumptive Waveforms

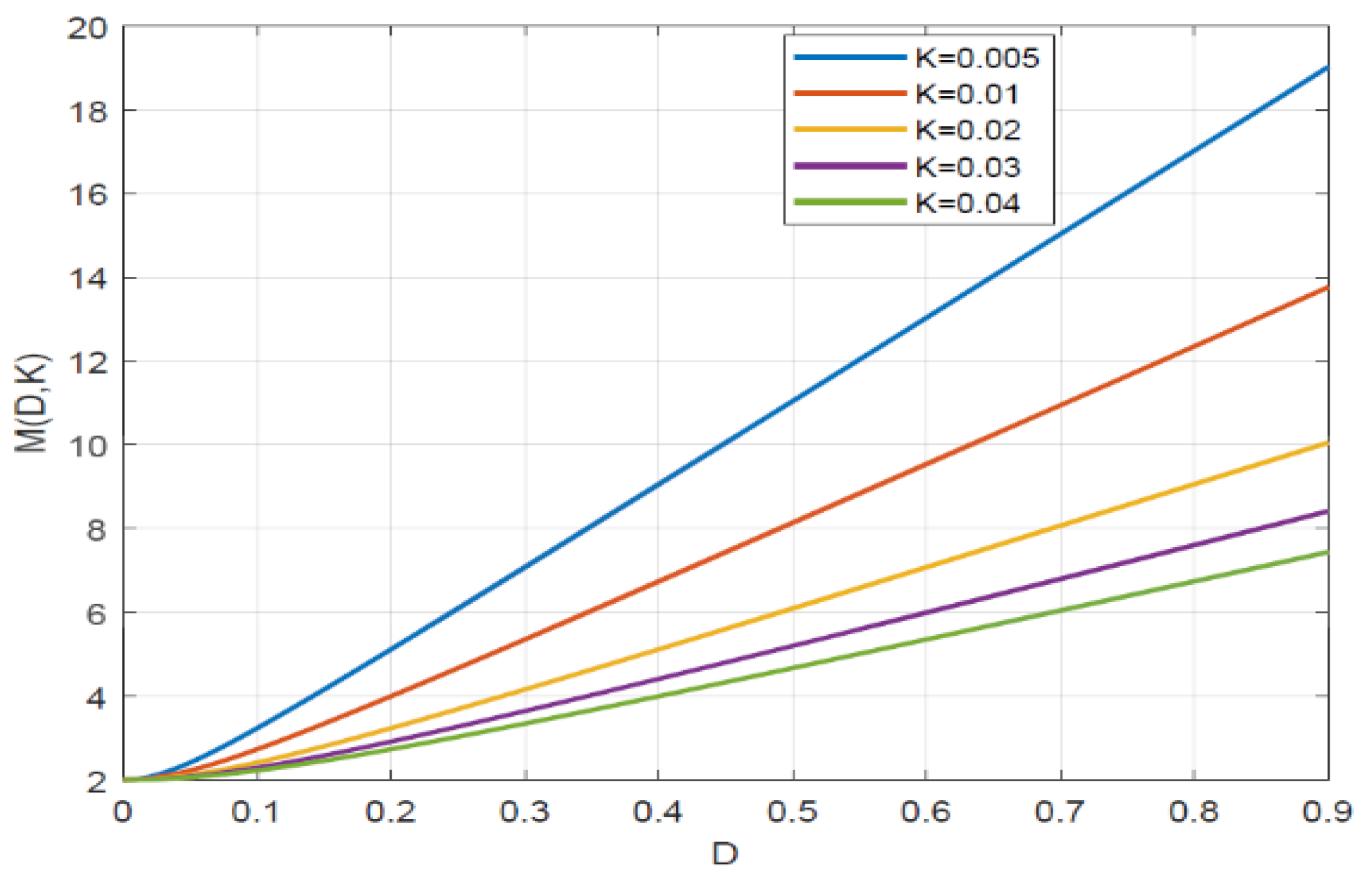

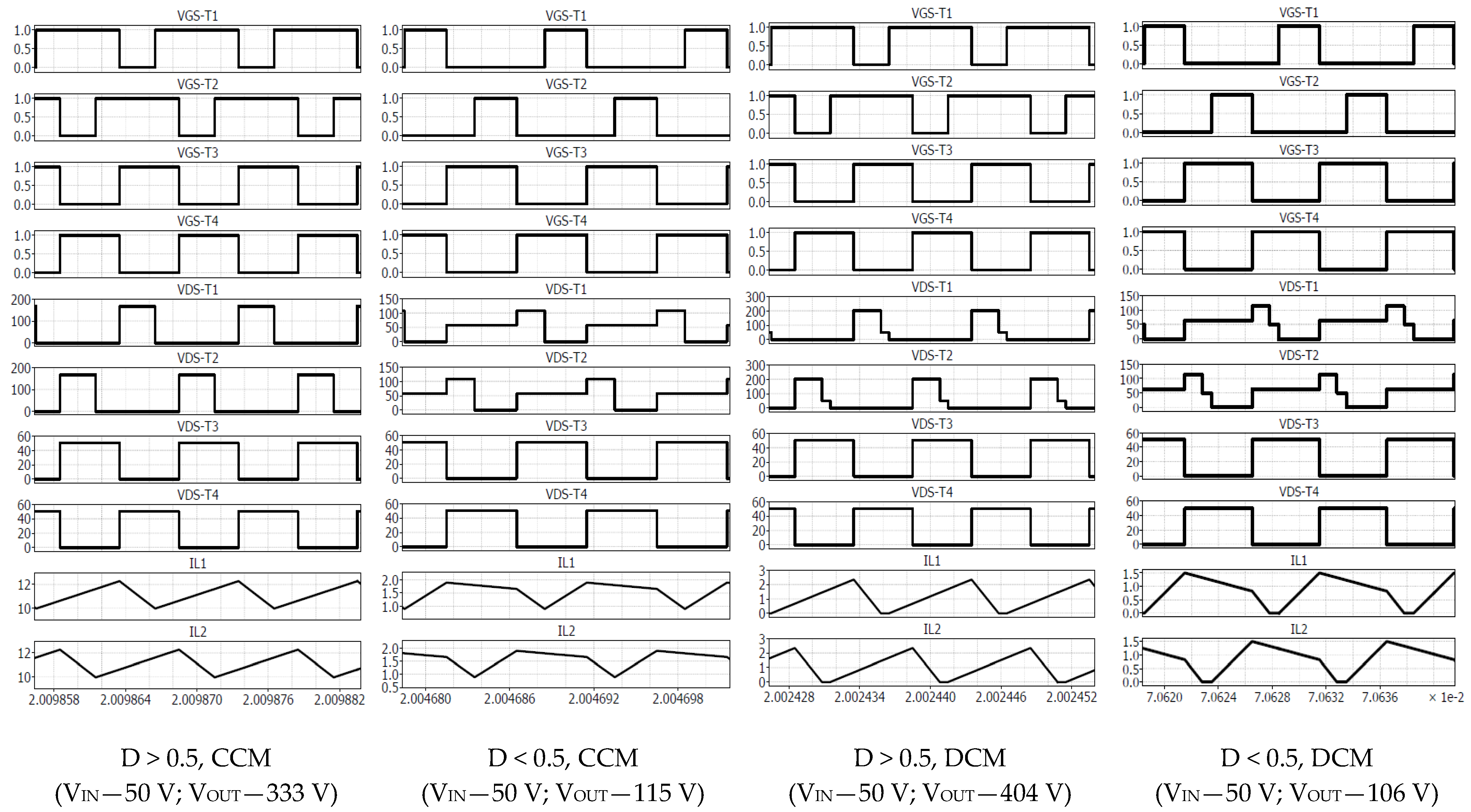

2.2. CCM Operation of the Proposed Converter

2.3. DCM Operation of the Proposed Converter

2.3.1. Case 1

2.3.2. Case 2

2.4. DCM–CCM Boudary Limit

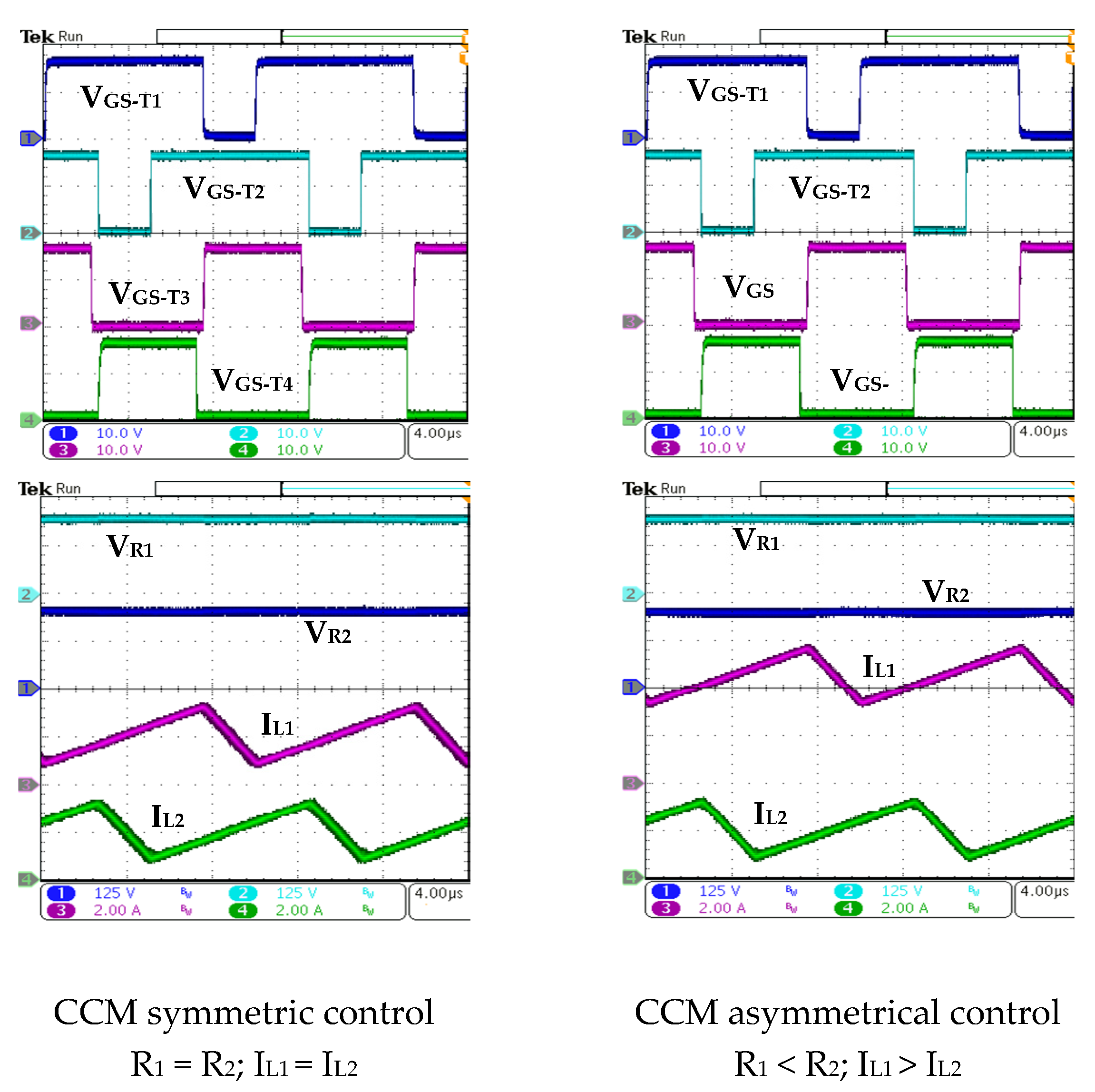

3. Simulation and Practical Implementation

4. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Tostado-Veliz, M.; Leon-Japa, R.S.; Jurado, F. Optimal electrification of off-grid smart homes considering flexible demand and vehicle-to-home capabilities. Appl. Energy 2021, 298, 117184. [Google Scholar] [CrossRef]

- Diaz-Saldierna, L.; Leyva-Ramos, J. High Step-Up Converter Based on Non-Series Energy Transfer Structure for Renewable Power Applications. Micromachines 2021, 12, 689. [Google Scholar] [CrossRef]

- Zhang, H.; Chen, Y.; Park, S.-J.; Kim, D.-H. A Family of Bidirectional DC–DC Converters for Battery Storage System with High Voltage Gain. Energies 2019, 12, 1289. [Google Scholar] [CrossRef] [Green Version]

- Ahmad, J.; Zaid, M.; Sarwar, A.; Lin, C.-H.; Ahmad, S.; Sharaf, M.; Zaindin, M.; Firdausi, M. A Voltage Multiplier Circuit Based Quadratic Boost Converter for Energy Storage Application. Appl. Sci. 2020, 10, 8254. [Google Scholar] [CrossRef]

- Lai, C.-M.; Yang, M.-J. A High-Gain Three-Port Power Converter with Fuel Cell, Battery Sources and Stacked Output for Hybrid Electric Vehicles and DC-Microgrids. Energies 2016, 9, 180. [Google Scholar] [CrossRef] [Green Version]

- Huang, H.; Balasubramaniam, S.; Todeschini, G.; Santoso, S. A Photovoltaic-Fed DC-Bus Islanded Electric Vehicles Charging System Based on a Hybrid Control Scheme. Electronics 2021, 10, 1142. [Google Scholar] [CrossRef]

- Malik, M.Z.; Chen, H.; Nazir, M.S.; Khan, I.; Abdalla, A.N.; Ali, A.; Chen, W. A New Efficient Step-Up Boost Converter with CLD Cell for Electric Vehicle and New Energy Systems. Energies 2020, 13, 1791. [Google Scholar] [CrossRef] [Green Version]

- Revathi, B.S.; Mahalingam, P.; Gonzalez-Longatt, F. Interleaved high gain DC–DC converter for integrating solar PV source to DC bus. Sol. Energy 2019, 188, 924–934. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Hu, X.; Li, L.; Li, Y.; Wu, G. Input-parallel output-series DC–DC converter for non-isolated high step-up applications. Electron. Lett. 2016, 52, 1715–1717. [Google Scholar] [CrossRef]

- Yan, Z.; Zeng, J.; Lin, W.; Liu, J. A Novel Interleaved Nonisolated Bidirectional DC–DC Converter with High Voltage-Gain and Full-Range ZVS. IEEE Trans. Power Electron. 2019, 35, 7191–7203. [Google Scholar] [CrossRef]

- Ahmad, J.; Zaid, M.; Sarwar, A.; Lin, C.-H.; Asim, M.; Yadav, R.; Tariq, M.; Satpathi, K.; Alamri, B. A New High-Gain DC–DC Converter with Continuous Input Current for DC Microgrid Applications. Energies 2021, 14, 2629. [Google Scholar] [CrossRef]

- Frivaldsky, M.; Hanko, B.; Prazenica, M.; Morgos, J. High Gain Boost Interleaved Converters with Coupled Inductors and with Demagnetizing Circuits. Energies 2018, 11, 130. [Google Scholar] [CrossRef] [Green Version]

- Choi, S.; Agelidis, V.; Yang, J.; Coutellier, D.; Marabeas, P. Analysis, design and experimental results of a floating-output interleaved-input boost-derived DC–DC high-gain transformer-less converter. IET Power Electron. 2011, 4, 168. [Google Scholar] [CrossRef]

- Li, Q.; Huangfu, Y.; Xu, L.; Wei, J.; Ma, R.; Zhao, D.; Gao, F. An Improved Floating Interleaved Boost Converter with the Zero-Ripple Input Current for Fuel Cell Applications. IEEE Trans. Energy Convers. 2019, 34, 2168–2179. [Google Scholar] [CrossRef]

- Dusmez, S.; Hasanzadeh, A.; Khaligh, A. Comparative Analysis of Bidirectional Three-Level DC–DC Converter for Automo-tive Applications. IEEE Trans. Ind. Electron. 2015, 62, 3305–3315. [Google Scholar] [CrossRef]

- Ganjavi, A.; Ghoreishy, H.; Ahmad, A.A. A Novel Single-Input Dual-Output Three-Level DC–DC Converter. IEEE Trans. Ind. Electron. 2018, 65, 8101–8111. [Google Scholar] [CrossRef]

- Chen, J.; Hou, S.; Sun, T.; Deng, F.; Chen, Z. A New Interleaved Double-Input Three-Level Boost Converter. J. Power Electron. 2016, 16, 925–935. [Google Scholar] [CrossRef]

- Tang, Y.; Wang, T.; He, Y. A Switched-Capacitor-Based Active-Network Converter Wit High Voltage Gain. IEEE Trans. Power Electron. 2014, 29, 2959–2968. [Google Scholar] [CrossRef]

- Marzang, V.; Hosseini, S.H.; Rostami, N.; Alavi, P.; Mohseni, P.; Hashemzadeh, S.M. A High Step-Up Nonisolated DC–DC Converter with Flexible Voltage Gain. IEEE Trans. Power Electron. 2020, 35, 10489–10500. [Google Scholar] [CrossRef]

- Maheri, H.M.; Babaei, E.; Sabahi, M.; Hosseini, S.H. High Step-Up DC–DC Converter with Minimum Output Voltage Ripple. IEEE Trans. Ind. Electron. 2017, 64, 3568–3575. [Google Scholar] [CrossRef]

- Zhang, Y.; Gao, Y.; Zhou, L.; Sumner, M. A Switched-Capacitor Bidirectional DC–DC Converter with Wide Voltage Gain Range for Electric Vehicles with Hybrid Energy Sources. IEEE Trans. Power Electron. 2018, 33, 9459–9469. [Google Scholar] [CrossRef]

- Haji-Esmaeili, M.M.; Babaei, E.; Sabahi, M. High Step-Up Quasi-Z Source DC–DC Converter. IEEE Trans. Power Electron. 2018, 33, 10563–10571. [Google Scholar] [CrossRef]

- Li, K.; Hu, Y.; Ioinovici, A. Generation of the Large DC Gain Step-Up Nonisolated Converters in Conjunction with Renewable Energy Sources Starting from a Proposed Geometric Structure. IEEE Trans. Power Electron. 2017, 32, 5323–5340. [Google Scholar] [CrossRef]

- Salvador, M.A.; Lazzarin, T.B.; Coelho, R.F. High Step-Up DC–DC Converter with Active Switched-Inductor and Passive Switched-Capacitor Networks. IEEE Trans. Ind. Electron. 2018, 65, 5644–5654. [Google Scholar] [CrossRef]

- Salvador, M.A.; De Andrade, J.M.; Lazzarin, T.B.; Coelho, R.F. Nonisolated High-Step-Up DC–DC Converter Derived from Switched-Inductors and Switched-Capacitors. IEEE Trans. Ind. Electron. 2019, 67, 8506–8516. [Google Scholar] [CrossRef]

- Maroti, P.K.; Ranjana, M.S.B.; Prabhakar, D.K. A novel high gain switched inductor multilevel buck-boost DC–DC converter for solar applications. In Proceedings of the 2014 IEEE 2nd International Conference on Electrical Energy Systems (ICEES), Chennai, India, 7–9 January 2014; Institute of Electrical and Electronics Engineers (IEEE): Piscataway, NJ, USA, 2014; pp. 152–156. [Google Scholar]

- Lakshmi, M.; Hemamalini, S. Nonisolated High Gain DC–DC Converter for DC Microgrids. IEEE Trans. Ind. Electron. 2018, 65, 1205–1212. [Google Scholar] [CrossRef]

- Baskar, M.S.; Meraj, M.; Iqbal, A.; Padmanaban, S.; Maroti, P.K.; Alammari, R. High Gain Transformer-Less Dou-ble-Duty-Triple-Mode DC/DC Converter for DC Microgrid. IEEE Access 2019, 7, 36353–36370. [Google Scholar] [CrossRef]

- Maroti, P.K.; Al-Ammari, R.; Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Padmanaban, S.; Rahman, S. A new Tri-Switching State Non-Isolated High Gain DC–DC Boost Converter for Microgrid Application. IET Power Electron. 2019, 12, 2741–2750. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Alammari, R.; Meraj, M.; Padmanaban, S.; Iqbal, A. A New Triple-Switched-Triple-Mode High Step-up Con-verter with Wide Range of Duty Cycle for DC Microgrid Applications. IEEE Trans. Ind. Appl. 2019, 55, 7425–7441. [Google Scholar] [CrossRef]

- Wang, F.; Lei, Z.; Xu, X.; Shu, X. Topology Deduction and Analysis of Voltage Balancers for DC Microgrid. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 5, 672–680. [Google Scholar] [CrossRef]

- Teodosescu, P.D.; Suciu, V.M.; Szekely, N.C.; Pacuraru, A.M.; Bojan, M. Interleaved Buck-Boost Voltage Converter. OSIM Patent Application A2019 00915, 19 December 2019. [Google Scholar]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics, 2nd ed.; Kluwer: Norwell, MA, USA, 2001. [Google Scholar]

| Parameters | Values |

|---|---|

| Input Voltage—VIN | 50 V–100 V |

| Output Voltage—VOUT | 400 V |

| Switching frequency—fs | 100 kHz |

| Max. Output Power—POUT | 480 W |

| Switches (T1–T4) | C2M0280120D |

| Diodes (D1, D2) | C3D02060A |

| Inductors (L1, L2) | 50 µH, RL = 21 mΩ |

| Capacitors (C1, C2) | 100 µF |

| Ref. | Voltage Gain (M) | Normalized Voltage Stress across the Power | Pout [W] | Efficiency [%] at Vin [V] | Components S*/D*/L*/ C*/C.I*/T* | |

|---|---|---|---|---|---|---|

| Switches VS/VO | Diodes VD/VO | |||||

| IDBIC | 2/(1 − d) | 1/M + 0.5 1/M | 0.5 | 240 | 94.25 @ 50 V 95.95 @100 V | 4/2/2/ 2/-/10 |

| [15] | (1 + d)/ (1 − d) | (M + 1)/2M | (M + 1)/2M | 240 | 91.7 @ 24 V | 2/2/2/ 4/2/10 |

| [17] | 1/(1 − d) | 0.5 | 0.5 | 300 | 95.9 @ 60 V | 4/2/2/ 3/-/11 |

| [18] | 2/(1 − d) | 0.5 | 0.5 | 320 | 90.2 @ 48 V 95 @ 80 V | 2/3/2/ 3/-/10 |

| [20] | (3 + d1 − d2)/(1 − d1 − d2) | (M + 1)/4M (M − 1)/2M | (M + 1)2M | 500 | 93.4 @ 20 V 95.85 @ 30 V | 3/4/2/ 3/-/12 |

| [21] | (1 + 5d)/ (1 − d) | (1 + 5M)/6M | (M + 1)/M | 200 | 95.9 @ 30 V | 6/9/6/ 1/-/22 |

| [22] | 2/(1 − d) | 0.5 | - | 300 | 91.3 @ 50 V 94.3 @ 100 V | 4/0/1/ 4/0/9 |

| [23] | 3/(1 − d) | 0.33 | 0.33 | 150 | 93.9 @30 V | 1/5/1/ 5/0/12 |

| [26] | (3 + d)/ (1 − d) | (M + 1)/4M | (M + 1)/2M | 200 | 96 @ 30 V | 2/3/-/ 3/1/9 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Suciu, V.M.; Salcu, S.I.; Pacuraru, A.M.; Pintilie, L.N.; Szekely, N.C.; Teodosescu, P.D. Independent Double-Boost Interleaved Converter with Three-Level Output. Appl. Sci. 2021, 11, 5993. https://doi.org/10.3390/app11135993

Suciu VM, Salcu SI, Pacuraru AM, Pintilie LN, Szekely NC, Teodosescu PD. Independent Double-Boost Interleaved Converter with Three-Level Output. Applied Sciences. 2021; 11(13):5993. https://doi.org/10.3390/app11135993

Chicago/Turabian StyleSuciu, Vasile Mihai, Sorin Ionut Salcu, Alexandru Madalin Pacuraru, Lucian Nicolae Pintilie, Norbert Csaba Szekely, and Petre Dorel Teodosescu. 2021. "Independent Double-Boost Interleaved Converter with Three-Level Output" Applied Sciences 11, no. 13: 5993. https://doi.org/10.3390/app11135993

APA StyleSuciu, V. M., Salcu, S. I., Pacuraru, A. M., Pintilie, L. N., Szekely, N. C., & Teodosescu, P. D. (2021). Independent Double-Boost Interleaved Converter with Three-Level Output. Applied Sciences, 11(13), 5993. https://doi.org/10.3390/app11135993