A Novel Cross-Latch Shift Register Scheme for Low Power Applications

Abstract

1. Introduction

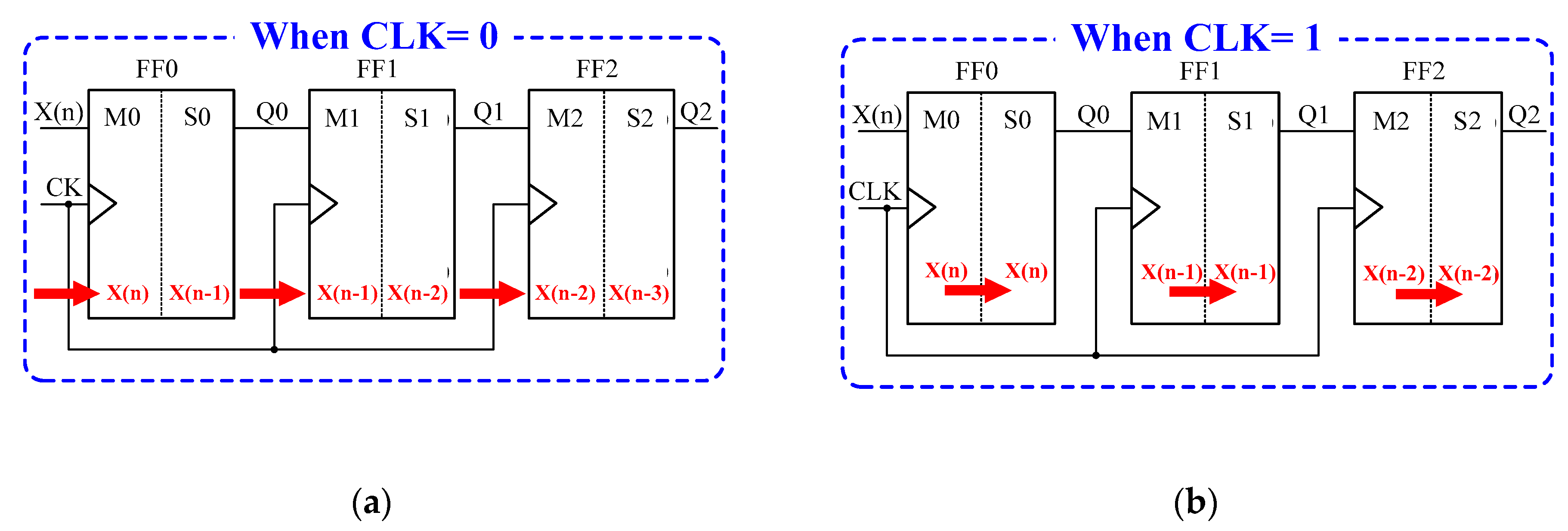

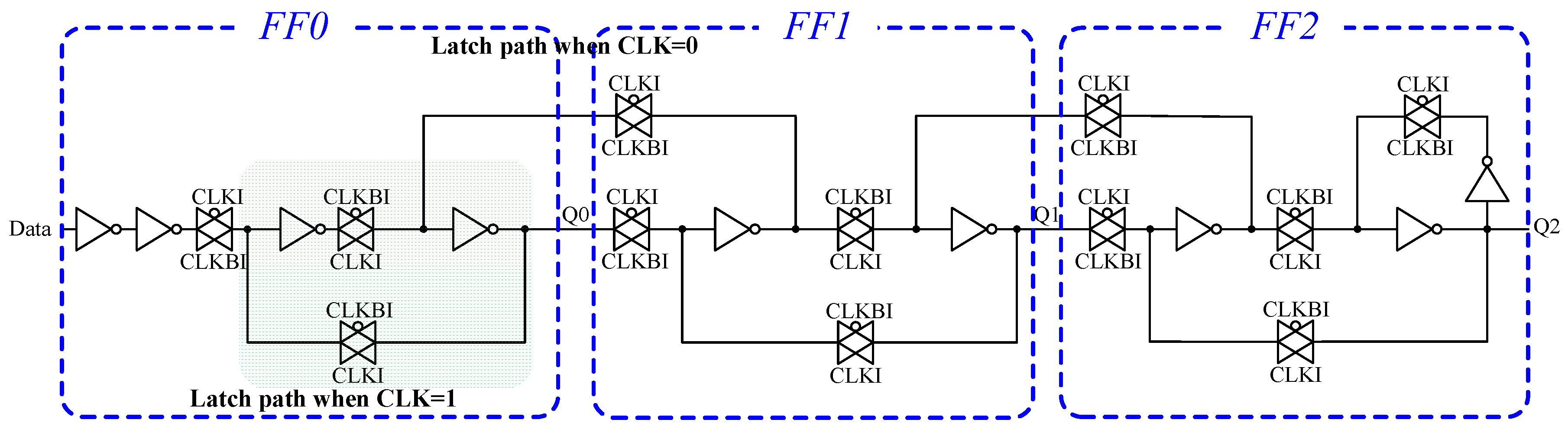

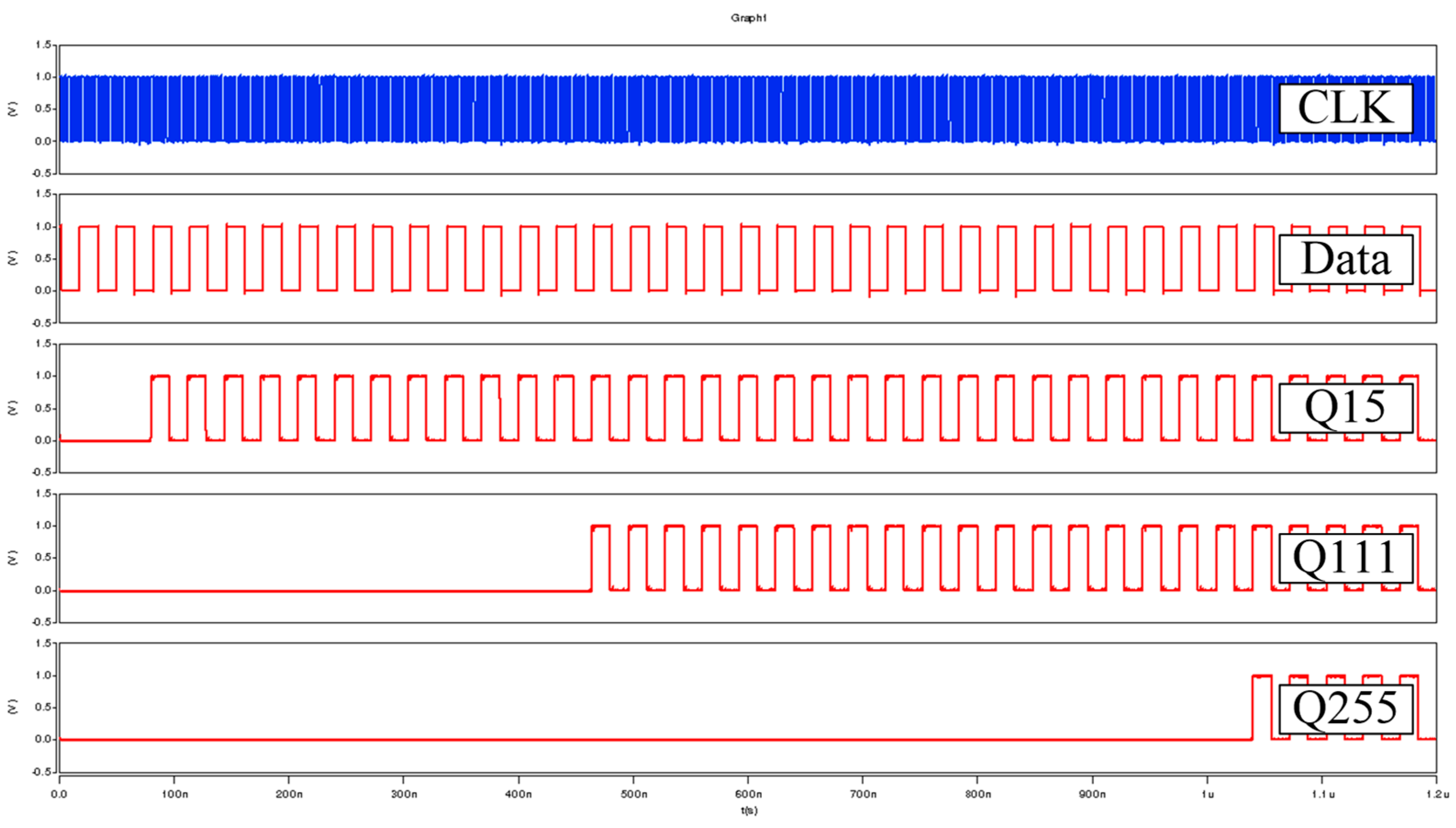

2. The Proposed Cross-Latch Shift Register (CLSR) Design

2.1. Principle of the Proposed Circuit Architecture

2.2. Delay Clock Circuit

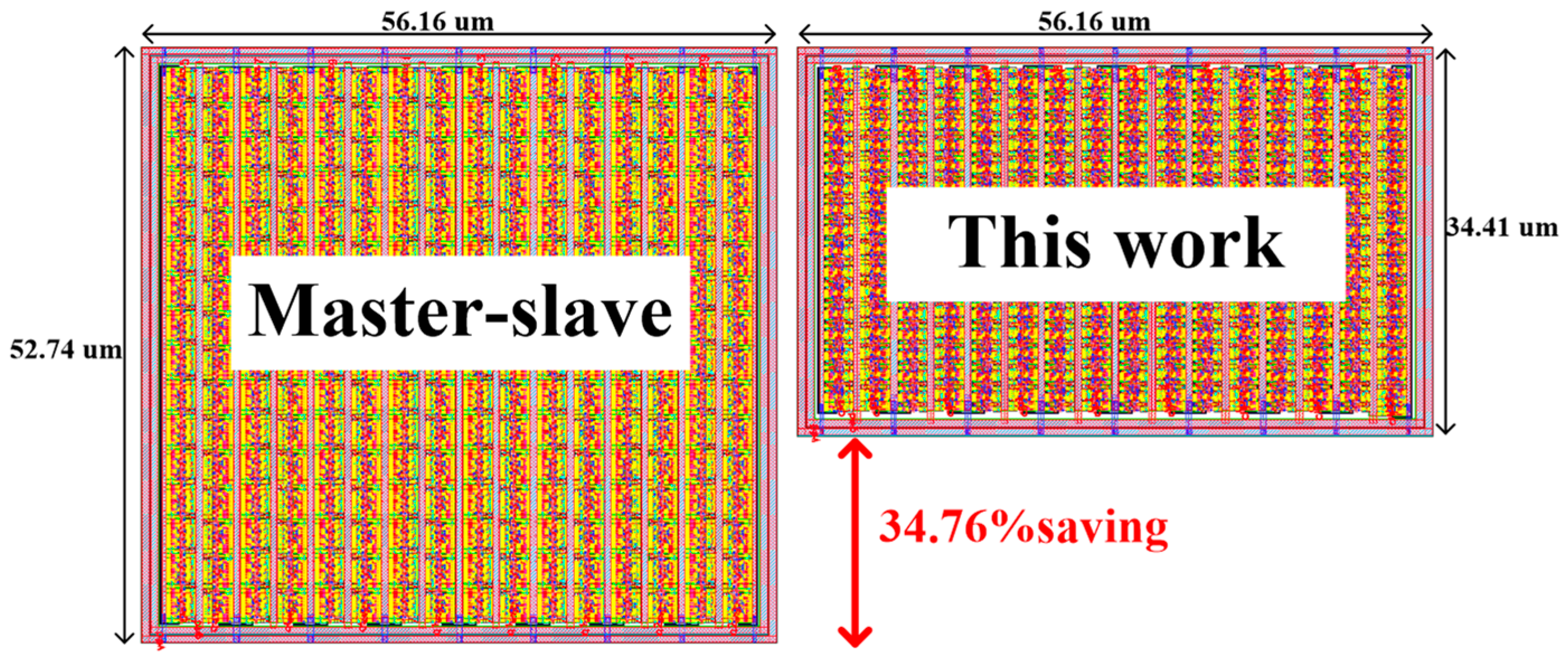

3. Analysis of Layout Area and Power Consumption of the Proposed CLSR Design

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Ng, T.N.; Schwartz, D.E.; Lavery, L.L.; Whiting, G.L.; Russo, B.; Krusor, B.; Veres, J.; Bröms, P.; Herlogsson, L.; Alam, N. Scalable printed electronics: An organic decoder addressing ferroelectric non-volatile memory. Sci. Rep. 2012, 2, 585. [Google Scholar] [CrossRef]

- Gelinck, G.H.; Huitema, H.E.A.; Van Veenendaal, E.; Cantatore, E.; Schrijnemakers, L.; Van Der Putten, J.B.; Geuns, T.C.; Beenhakkers, M.; Giesbers, J.B.; Huisman, B.-H. Flexible active-matrix displays and shift registers based on solution-processed organic transistors. Nat. Mater. 2004, 3, 106–110. [Google Scholar] [CrossRef] [PubMed]

- Hatamian, M.; Agazzi, O.E.; Creigh, J.; Samueli, H.; Castellano, A.J.; Kruse, D.; Madisetti, A.; Yousefi, N.; Bult, K.; Pai, P. Design considerations for gigabit Ethernet 1000Base-T twisted pair transceivers. In Proceedings of the IEEE 1998 Custom Integrated Circuits Conference (Cat. No. 98CH36143), Santa Clara, CA, USA, 14 May 1998; pp. 335–342. [Google Scholar]

- Yamasaki, H.; Shibata, T. A real-time image-feature-extraction and vector-generation VLSI employing arrayed-shift-register architecture. IEEE J. Solid-State Circuits 2007, 42, 2046–2053. [Google Scholar] [CrossRef]

- Kim, H.-S.; Yang, J.-H.; Park, S.-H.; Ryu, S.-T.; Cho, G.-H. A 10-bit column-driver IC with parasitic-insensitive iterative charge-sharing based capacitor-string interpolation for mobile active-matrix LCDs. IEEE J. Solid-State Circuits 2014, 49, 766–782. [Google Scholar] [CrossRef]

- Chiang, S.-H.W.; Kleinfelder, S. Scaling and design of a 16-mega-pixel CMOS image sensor for electron microscopy. In Proceedings of the 2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC), Orlando, FL, USA, 24 October–1 November 2009; pp. 1249–1256. [Google Scholar]

- Xie, Z.; Wu, Z.; Wu, J. Low Voltage Delay Element with Dynamic Biasing Technique for Fully Integrated Cold-Start in Battery-Assistance DC Energy Harvesting Systems. Appl. Sci. 2020, 10, 6993. [Google Scholar] [CrossRef]

- Nomura, S.; Tachibana, F.; Fujita, T.; Teh, C.K.; Usui, H.; Yamane, F.; Miyamoto, Y.; Kumtornkittikul, C.; Hara, H.; Yamashita, T.; et al. A 9.7 mW AAC-decoding, 620 mW H.264 720p 60fps decoding, 8-core media processor with embedded forward body-biasing and power-gating circuit in 65 nm CMOS technology. In Proceedings of the IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 262–612. [Google Scholar]

- Stojanovic, V.; Oklobdzija, V.G. Comparative analysis of master-slave latches and flip-flops for high-performance and low-power systems. IEEE J. Solid-State Circuits 1999, 34, 536–548. [Google Scholar] [CrossRef]

- Schwartz, D.E.; Ng, T.N. Comparison of static and dynamic printed organic shift registers. IEEE Electron Device Lett. 2013, 34, 271–273. [Google Scholar] [CrossRef]

- Lin, J.-F.; Sheu, M.-H.; Hwang, Y.-T.; Wong, C.-S.; Tsai, M.-Y. Low-power 19-transistor true single-phase clocking flip-flop design based on logic structure reduction schemes. IEEE Trans. Very Large Scale Integr. (TVLSI) Syst. 2017, 25, 3033–3044. [Google Scholar] [CrossRef]

- Otfinowski, P.; Grybos, P. Low area 4-bit 5MS/s flash-type digitizer for hybrid-pixel detectors—Design study in 180 nm and 40 nm CMOS. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrom. Detect. Assoc. Equip. 2015, 800, 104–110. [Google Scholar] [CrossRef]

- Kawai, N.; Takayama, S.; Masumi, J.; Kikuchi, N.; Itoh, Y.; Ogawa, K.; Ugawa, A.; Suzuki, H.; Tanaka, Y. A fully static topologically-compressed 21-transistor flip-flop with 75% power saving. IEEE J. Solid-State Circuits 2014, 49, 2526–2533. [Google Scholar] [CrossRef]

- Ruiz, G.A.; Granda, M. Efficient low-power register array with transposed access mode. Microelectron. J. 2014, 45, 463–467. [Google Scholar] [CrossRef]

- Jamshidi, V.; Fazeli, M. Design of ultra-low power current mode logic gates using magnetic cells. Int. J. Electron. Commun. 2018, 83, 270–279. [Google Scholar] [CrossRef]

- Taghizadeh, A.; Koozehkanani, Z.D.; Sobhi, J. A new high-speed low-power and low-offset dynamic comparator with a current-mode offset compensation technique. Int. J. Electron. Commun. 2017, 81, 163–170. [Google Scholar] [CrossRef]

- Kumar, D.; Kumar, M. Comparative analysis of adiabatic logic challenges for low power CMOS circuit designs. Microprocess. Microsyst. 2018, 60, 107–121. [Google Scholar] [CrossRef]

- Murugasami, R.; Ragupathy, U. Design and comparative analysis of D-Flip-flop using conditional pass transistor logic for high-performance with low-power systems. Microprocess. Microsyst. 2019, 68, 92–101. [Google Scholar] [CrossRef]

- Hassanli, K.; Sayedi, S.M.; Dehghani, R.; Jalili, A.; Wikner, J.J. A highly sensitive, low-power, and wide dynamic range CMOS digital pixel sensor. Sens. Actuators Phys. 2015, 236, 82–91. [Google Scholar] [CrossRef]

- Jeong, T.T. Implementation of low power adder design and analysis based on power reduction technique. Microelectron. J. 2008, 39, 1880–1886. [Google Scholar] [CrossRef]

- Piguet, C. Low-power and low-voltage CMOS digital design. Microelectron. Eng. 1997, 39, 179–208. [Google Scholar] [CrossRef]

- Sudheer, A.; Ravindran, A. Design and Implementation of Embedded Logic Flip-Flop for Low Power Applications. Procedia Comput. Sci. 2015, 46, 1393–1400. [Google Scholar] [CrossRef]

- Mahmoud, M.M.; El-Dib, D.A.; Fahmy, H.A. Low energy pipelined Dual Base (decimal/binary) Multiplier, DBM, design. Microelectron. J. 2017, 65, 11–20. [Google Scholar] [CrossRef]

- Tavana, M.K.; Khameneh, S.A.; Goudarzi, M. Dynamically adaptive register file architecture for energy reduction in embedded processors. Microprocess. Microsyst. 2015, 39, 49–63. [Google Scholar] [CrossRef]

- Brelsford, K.; López, S.A.P.; Fernandez-Gomez, S. Energy efficient computation: A silicon perspective. Integration 2014, 47, 1–11. [Google Scholar] [CrossRef]

- Katreepalli, R.; Haniotakis, T. Power efficient synchronous counter design. Comput. Electr. Eng. 2019, 75, 288–300. [Google Scholar] [CrossRef]

- Yang, B.-D. Low-power and area-efficient shift register using pulsed latches. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1564–1571. [Google Scholar] [CrossRef]

- Teh, C.K.; Fujita, T.; Hara, H.; Hamada, M. A 77% energy-saving 22-transistor single-phase-clocking D-flip-flop with adaptive-coupling configuration in 40 nm CMOS. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 338–340. [Google Scholar]

- Stas, F.; Bol, D. A 0.4-V 0.66-fJ/Cycle Retentive True-Single-Phase-Clock 18T Flip-Flop in 28-nm Fully-Depleted SOI CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 65, 935–945. [Google Scholar] [CrossRef]

- Li, J.; Chang, A.; Kim, T.T.-H. A 0.4-V, 0.138-fJ/Cycle Single-Phase-Clocking Redundant-Transition-Free 24T Flip-Flop with Change-Sensing Scheme in 40-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 2806–2817. [Google Scholar]

- Kim, Y.; Jung, W.; Lee, I.; Dong, Q.; Henry, M.; Sylvester, D.; Blaauw, D. A static contention-free single-phase-clocked 24t flip-flop in 45nm for low-power applications. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 466–467. [Google Scholar]

- Chang, C.H.; Gu, J.M.; Zhang, M. A review of 0.18-/spl mu/m full adder performances for tree structured arithmetic circuits. IEEE Trans. Very Large Scale Integr. (TVLSI) Syst. 2005, 13, 686–695. [Google Scholar] [CrossRef]

- TSMC. 40nm CMOS ASIC Process Digest; Taiwan Semiconductor Manufacturing Company: Taipei, Taiwan, 2009. [Google Scholar]

- Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 2003, 91, 305–327. [Google Scholar] [CrossRef]

| TGFF | ACFF [28] | TSPCFF [29] | CSFF [30] | CLSR | |

|---|---|---|---|---|---|

| Number of transistors | 48 | 44 | 36 | 48 | 36 |

| 1-bit P/N of transistors | 12/12 | 11/11 | 8/10 | 11/13 | 9/9 |

| Floating problem | N | Y | Y | Y | N |

| Power (nW) | 300.10 | 304.00 | 700.70 | 271.10 | 163.90 |

| Area (µm2) | 16.76 | 15.67 | 13.16 | 18.18 | 13.31 |

| Master–Slave Latch | CLSR | |||

|---|---|---|---|---|

| Process | 40 nm | 40 nm | ||

| Word length of shifter register | 256 | 256 | ||

| Number of transistors | 6144 | 3174 | ||

| Layout area (µm2) | 2961.88 | 1932.47 | ||

| Typical voltage (V) | 0.9 | 0.4 | 0.9 | 0.4 |

| Frequency (MHz) | 250 | 25 | 250 | 25 |

| Power (µW) | 794 | 26.09 | 504 | 14.24 |

| PDP (fJ) | 144.43 | 690.22 | 120.03 | 569.61 |

| Leakage power (µW) | 35.33 | 3.36 | 13.95 | 2.33 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kuo, P.-Y.; Sheu, M.-H.; Tsai, C.-M.; Tsai, M.-Y.; Lin, J.-F. A Novel Cross-Latch Shift Register Scheme for Low Power Applications. Appl. Sci. 2021, 11, 129. https://doi.org/10.3390/app11010129

Kuo P-Y, Sheu M-H, Tsai C-M, Tsai M-Y, Lin J-F. A Novel Cross-Latch Shift Register Scheme for Low Power Applications. Applied Sciences. 2021; 11(1):129. https://doi.org/10.3390/app11010129

Chicago/Turabian StyleKuo, Po-Yu, Ming-Hwa Sheu, Chang-Ming Tsai, Ming-Yan Tsai, and Jin-Fa Lin. 2021. "A Novel Cross-Latch Shift Register Scheme for Low Power Applications" Applied Sciences 11, no. 1: 129. https://doi.org/10.3390/app11010129

APA StyleKuo, P.-Y., Sheu, M.-H., Tsai, C.-M., Tsai, M.-Y., & Lin, J.-F. (2021). A Novel Cross-Latch Shift Register Scheme for Low Power Applications. Applied Sciences, 11(1), 129. https://doi.org/10.3390/app11010129