A 5.43 nV/√Hz Chopper Operational Amplifier Using Lateral PNP Input Stage with BJT Current Mirror Base Current Cancellation

Abstract

1. Introduction

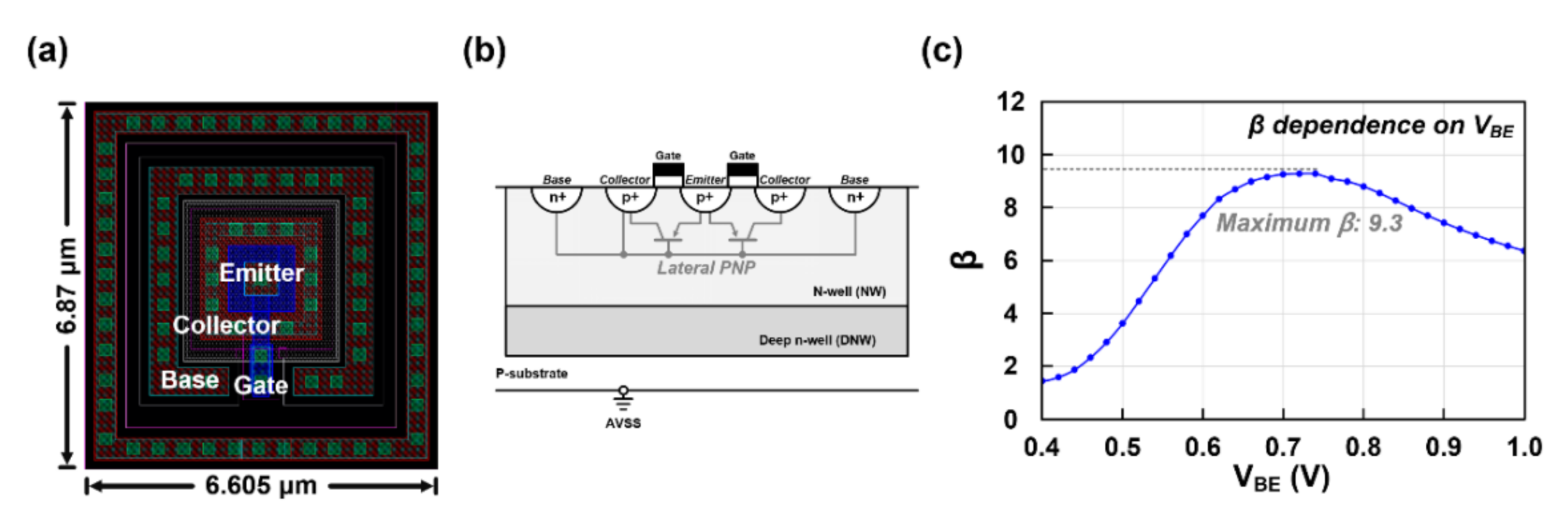

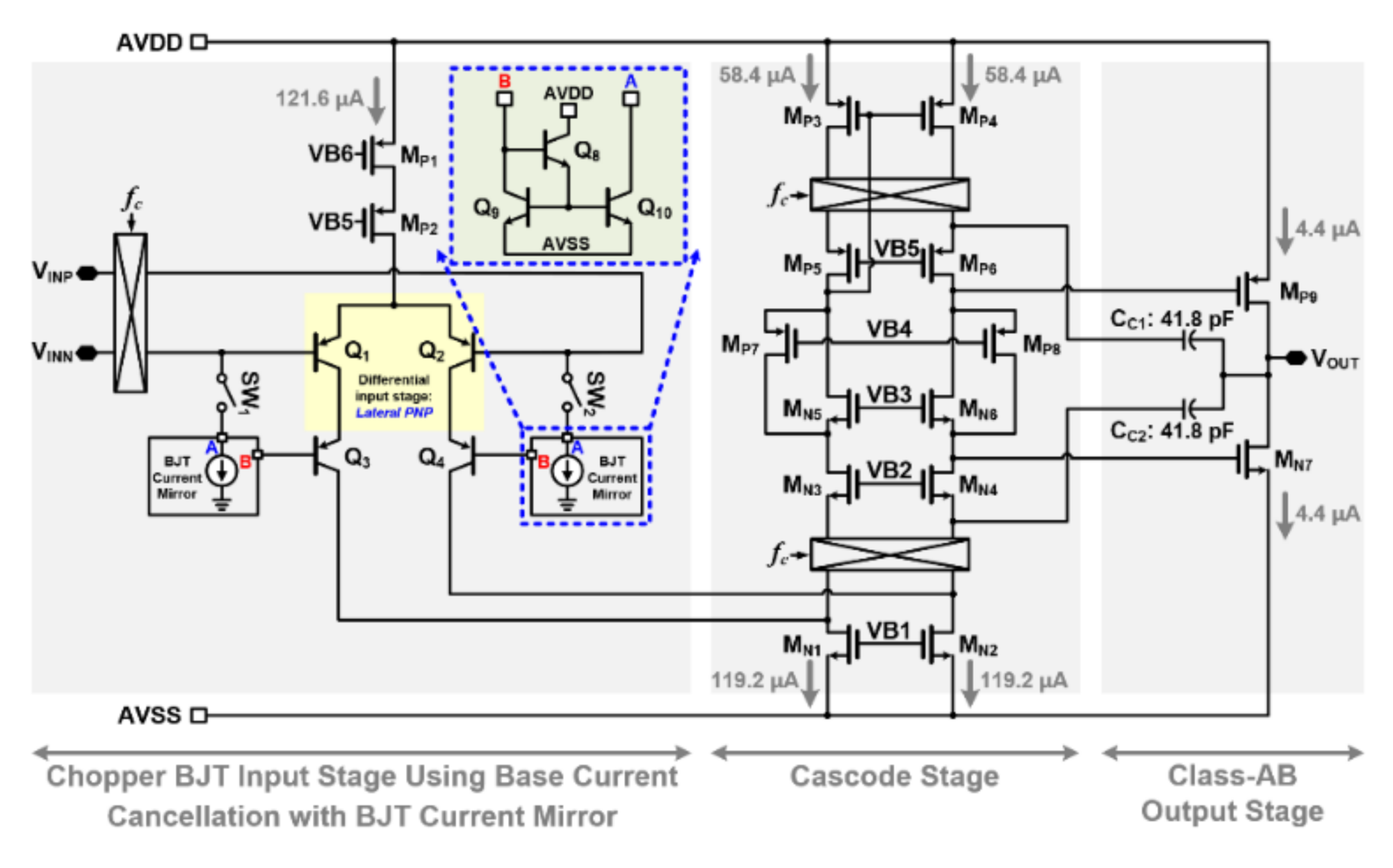

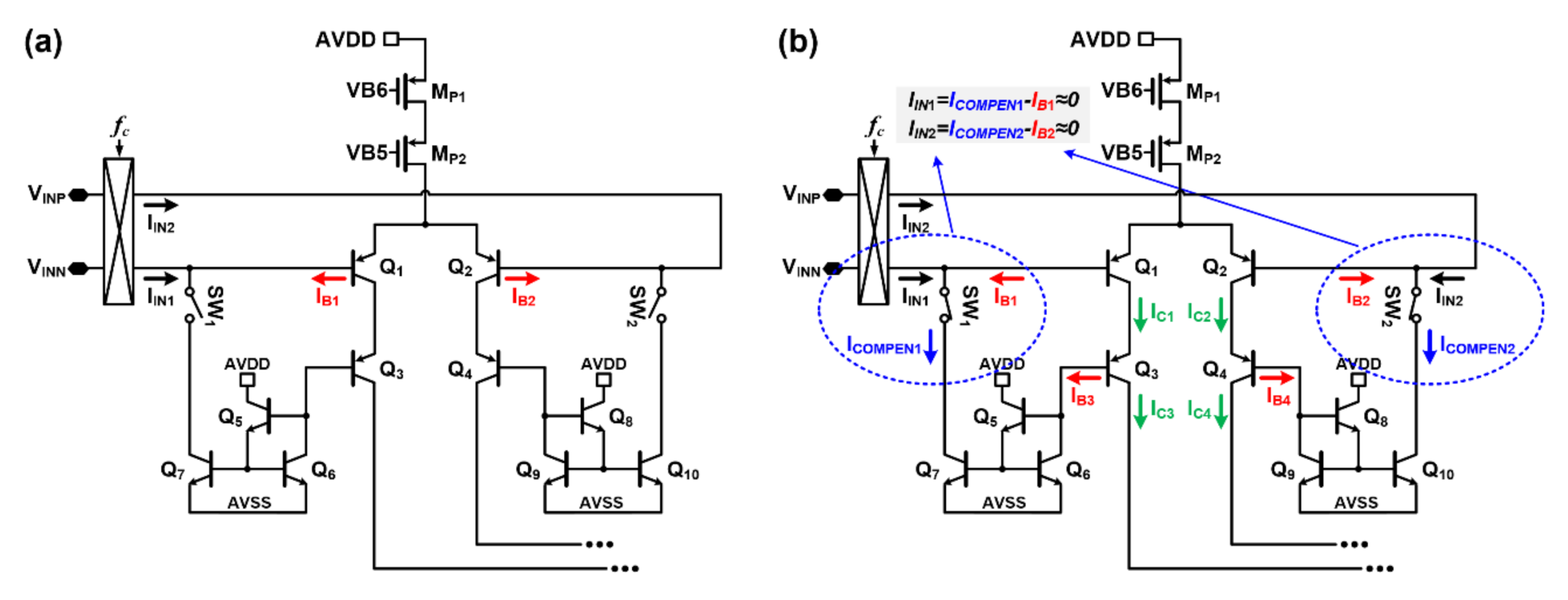

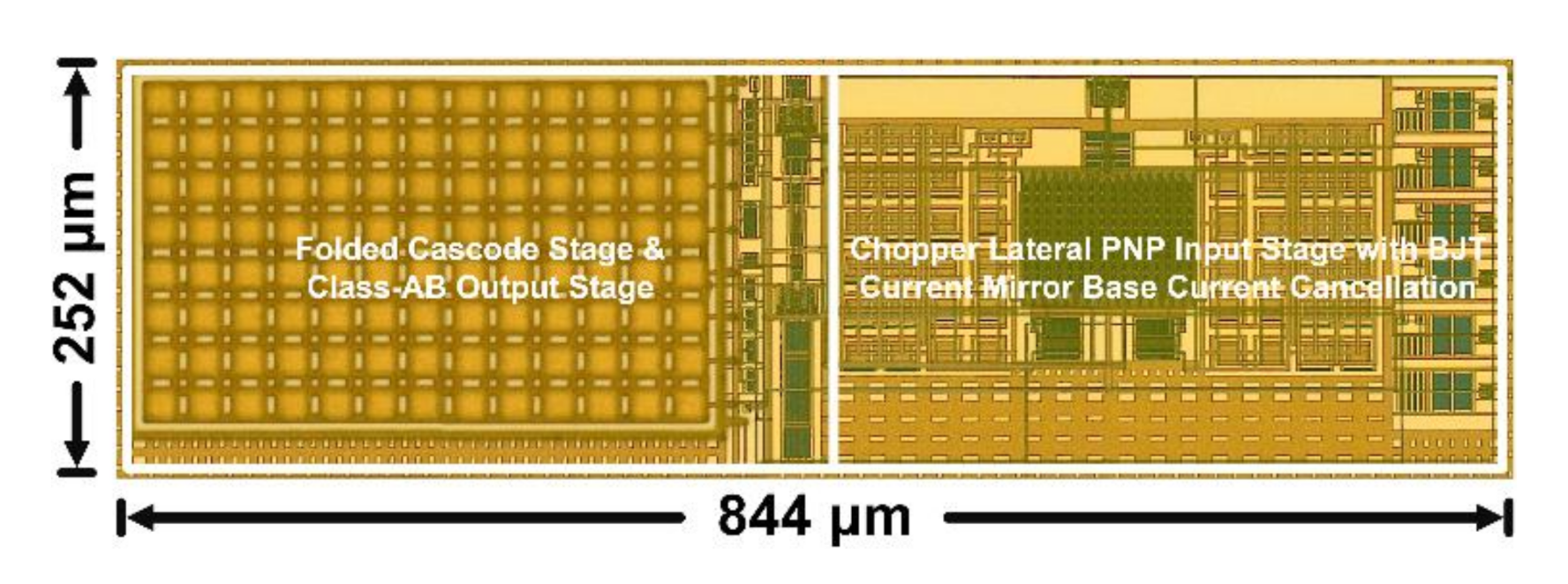

2. Circuit Implementation

3. Measurement Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Microchip MCP6V91. Available online: http://ww1.microchip.com/downloads/en/DeviceDoc/20005434B.pdf (accessed on 18 October 2020).

- Analog Devices ADA4522. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ADA4522-1_4522-2_4522-4.pdf (accessed on 18 October 2020).

- Texas Instruments OPA388. Available online: https://www.ti.com/lit/ds/symlink/opa388.pdf?ts=1602963493359&ref_url=https%253A%252F%252Fwww.google.com%252F (accessed on 18 October 2020).

- STMicroelectronics TSZ181. Available online: https://www.st.com/resource/en/datasheet/tsz181.pdf (accessed on 18 October 2020).

- On Semiconductor AND9857. Available online: https://www.onsemi.com/pub/Collateral/AND9857-D.PDF (accessed on 18 October 2020).

- Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Opris, I.E.; Kovacs, G.T.A. A rail-to-rail ping-pong op-amp. IEEE J. Solid-State Circuits 1996, 31, 1320–1324. [Google Scholar] [CrossRef]

- Oliaei, O. Noise analysis of correlated double sampling SC integrators with a hold capacitor. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2003, 50, 1198–1202. [Google Scholar] [CrossRef]

- Bakker, A.; Thiele, K.; Huijsing, J.H. A CMOS nested-chopper instrumentation amplifier with 100-nV offset. IEEE J. Solid-State Circuits 2000, 35, 1877–1883. [Google Scholar] [CrossRef]

- Lee, C.; Song, J. A chopper stabilized current-feedback instrumentation amplifier for EEG acquisition applications. IEEE Access 2019, 7, 11565–11569. [Google Scholar] [CrossRef]

- Burt, R.; Zhang, J. A micropower chopper-stabilized operational amplifier using a SC notch filter with synchronous integration inside the continuous-time signal path. IEEE J. Solid-State Circuits 2006, 41, 2729–2736. [Google Scholar] [CrossRef]

- Witte, J.F.; Makinwa, K.A.A.; Huijsing, J.H. A CMOS chopper offset-stabilized opamp. IEEE J. Solid-State Circuits 2007, 42, 1529–1535. [Google Scholar] [CrossRef]

- Fan, Q.; Huijsing, J.H.; Makinwa, K.A.A. A 21 nV/√Hz chopper-stabilized multi-path current-feedback instrumentation amplifier with 2 μV offset. IEEE J. Solid-State Circuits 2012, 47, 464–475. [Google Scholar] [CrossRef]

- Kim, J.; Kim, H.; Han, K.; You, D.; Heo, H.; Kwon, Y.; Cho, D.D.; Ko, H. Low-noise chopper-stabilized multi-path operational amplifier with nested miller compensation for high-precision sensors. Appl. Sci. 2020, 10, 281. [Google Scholar] [CrossRef]

- Steyaert, M.S.J.; Sansen, W.M.C.; Zhongyuan, C. A micropower low-noise monolithic instrumentation amplifier for medical purposes. IEEE J. Solid-State Circuits 1987, 22, 1163–1168. [Google Scholar] [CrossRef]

- Tsividis, Y.P.; Ulmer, R.W. A CMOS voltage references. IEEE J. Solid-State Circuits 1978, 13, 774–778. [Google Scholar] [CrossRef]

- Degrauwe, M.G.R.; Leuthold, O.N.; Vittoz, E.A.; Oguey, H.J.; Descombes, A. CMOS voltage references using lateral bipolar transistors. IEEE J. Solid-State Circuits 1985, 20, 1151–1157. [Google Scholar] [CrossRef]

- Vittoz, E.A. MOS transistors operated in the lateral bipolar mode and their application in CMOS technology. IEEE J. Solid-State Circuits 1983, 18, 273–279. [Google Scholar] [CrossRef]

- Pan, T.-W.; Abidi, A.A. A 50-dB variable gain amplifier using parasitic bipolar transistors in CMOS. IEEE J. Solid-State Circuits 1989, 24, 951–961. [Google Scholar] [CrossRef]

- Holman, W.T.; Connelly, J.A. A compact low noise operational amplifier for 1.2 µm digital CMOS technology. IEEE J. Solid-State Circuits 1995, 30, 710–714. [Google Scholar] [CrossRef]

- Zhao, D.; Zaman, M.F.; Ayazi, F. A chopper-stabilized lateral-BJT-input interface in 0.6µm CMOS for capacitive accelerometers. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 584–585. [Google Scholar] [CrossRef]

- Kusuda, Y. A 5.9 nV/√ Hz chopper operational amplifier with 0.78 μV maximum offset and 28.3 nV/°C offset drift. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 20–24 February 2011; pp. 242–244. [Google Scholar] [CrossRef]

| This Work | [14] | [22] | [13] | [20] | |

|---|---|---|---|---|---|

| Year | 2020 | 2020 | 2011 | 2010 | 1995 |

| Process (µm) | 0.18 | 0.18 | 0.35 | 0.7 | 1.2 |

| Input stage transistor | BJT | MOS transistor | MOS transistor | MOS transistor | BJT |

| Amplifier scheme | Chopper amplifier | Multipath amplifier | Multipath amplifier | Multipath amplifier | 2-stage amplifier |

| Supply voltage (V) | 3.3 | 1.8 | 2.5–5.5 | 5 | ±2.5 |

| Current consumption (µA) | 278.3 | 96.7 | 1470 | 143 | 2100 |

| DC gain (dB) | 115 | >137 | >150 | - | 20.8 (closed loop) |

| BW (MHz) | 2.30 | 3.16 | 4 | 1.8 | 122 |

| Input referred noise (nV/√Hz) | 5.43 | 11.8 | 5.9 | 10.5 | 3.2 |

| Input bias current (nA) | 67.971 | - | 0.072 | <0.250 | 1680 |

| CMRR (dB) | 90.9 | >125 | >150 | 137 | 99.6 |

| PSRR (dB) | 68.3 | >100 | >150 | 120 | 67.6 |

| Area (mm2) | 0.213 | 1.18 | 1.26 | 1.8 | 0.211 |

| NEF | 3.98 * | 4.46 | 8.4 | 4.8 | 5.64 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.; Kwon, Y.; You, D.; Choi, H.-W.; Kim, S.H.; Heo, H.; Kim, C.-Y.; Lee, H.-D.; Ko, H. A 5.43 nV/√Hz Chopper Operational Amplifier Using Lateral PNP Input Stage with BJT Current Mirror Base Current Cancellation. Appl. Sci. 2020, 10, 8376. https://doi.org/10.3390/app10238376

Kim H, Kwon Y, You D, Choi H-W, Kim SH, Heo H, Kim C-Y, Lee H-D, Ko H. A 5.43 nV/√Hz Chopper Operational Amplifier Using Lateral PNP Input Stage with BJT Current Mirror Base Current Cancellation. Applied Sciences. 2020; 10(23):8376. https://doi.org/10.3390/app10238376

Chicago/Turabian StyleKim, Hyungseup, Yongsu Kwon, Donggeun You, Hyun-Woong Choi, Seong Hyun Kim, Hyunwoo Heo, Choul-Young Kim, Hi-Deok Lee, and Hyoungho Ko. 2020. "A 5.43 nV/√Hz Chopper Operational Amplifier Using Lateral PNP Input Stage with BJT Current Mirror Base Current Cancellation" Applied Sciences 10, no. 23: 8376. https://doi.org/10.3390/app10238376

APA StyleKim, H., Kwon, Y., You, D., Choi, H.-W., Kim, S. H., Heo, H., Kim, C.-Y., Lee, H.-D., & Ko, H. (2020). A 5.43 nV/√Hz Chopper Operational Amplifier Using Lateral PNP Input Stage with BJT Current Mirror Base Current Cancellation. Applied Sciences, 10(23), 8376. https://doi.org/10.3390/app10238376