Real-Time Controller Design Test Bench for High-Voltage Direct Current Modular Multilevel Converters

Abstract

1. Introduction

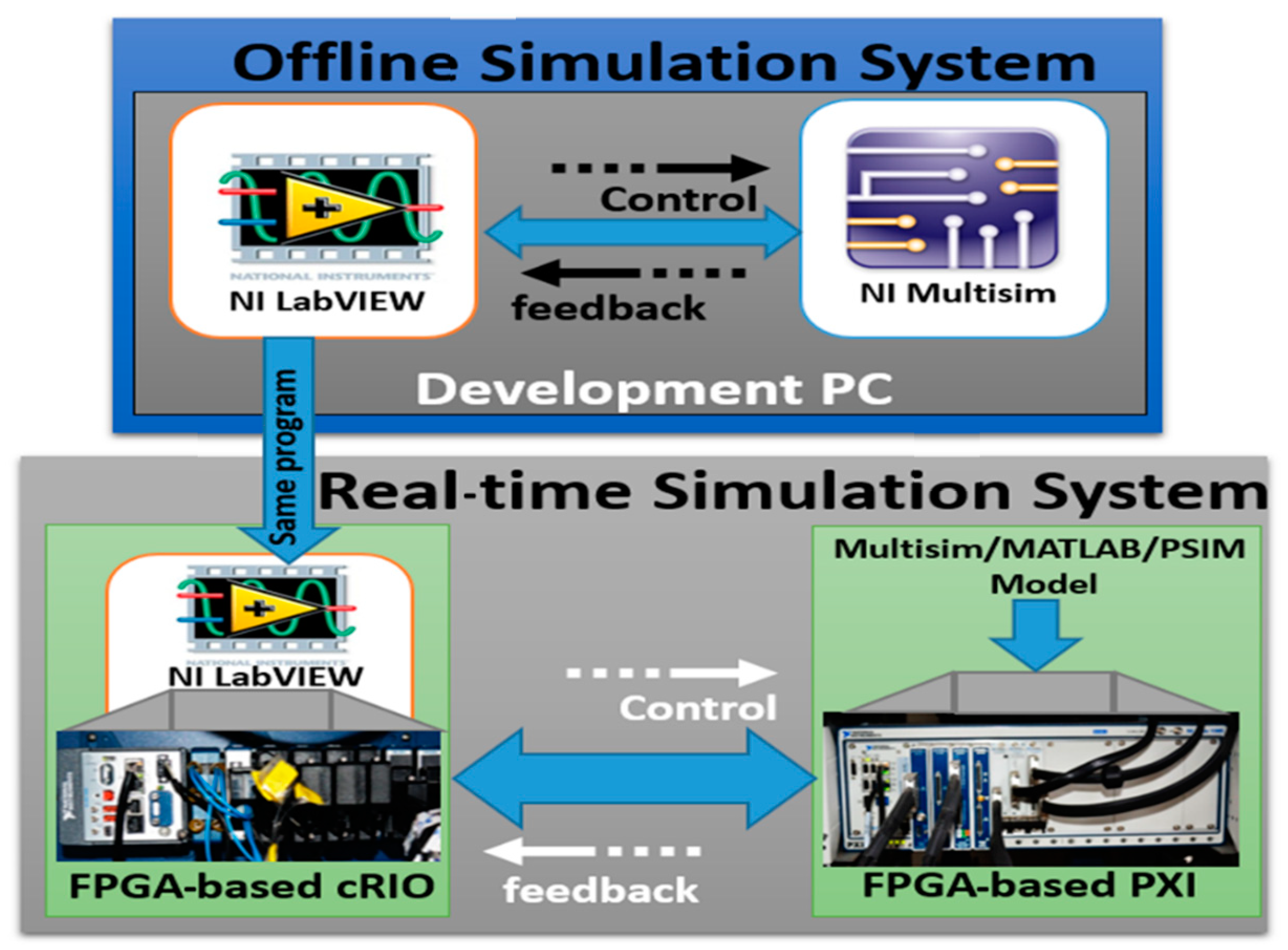

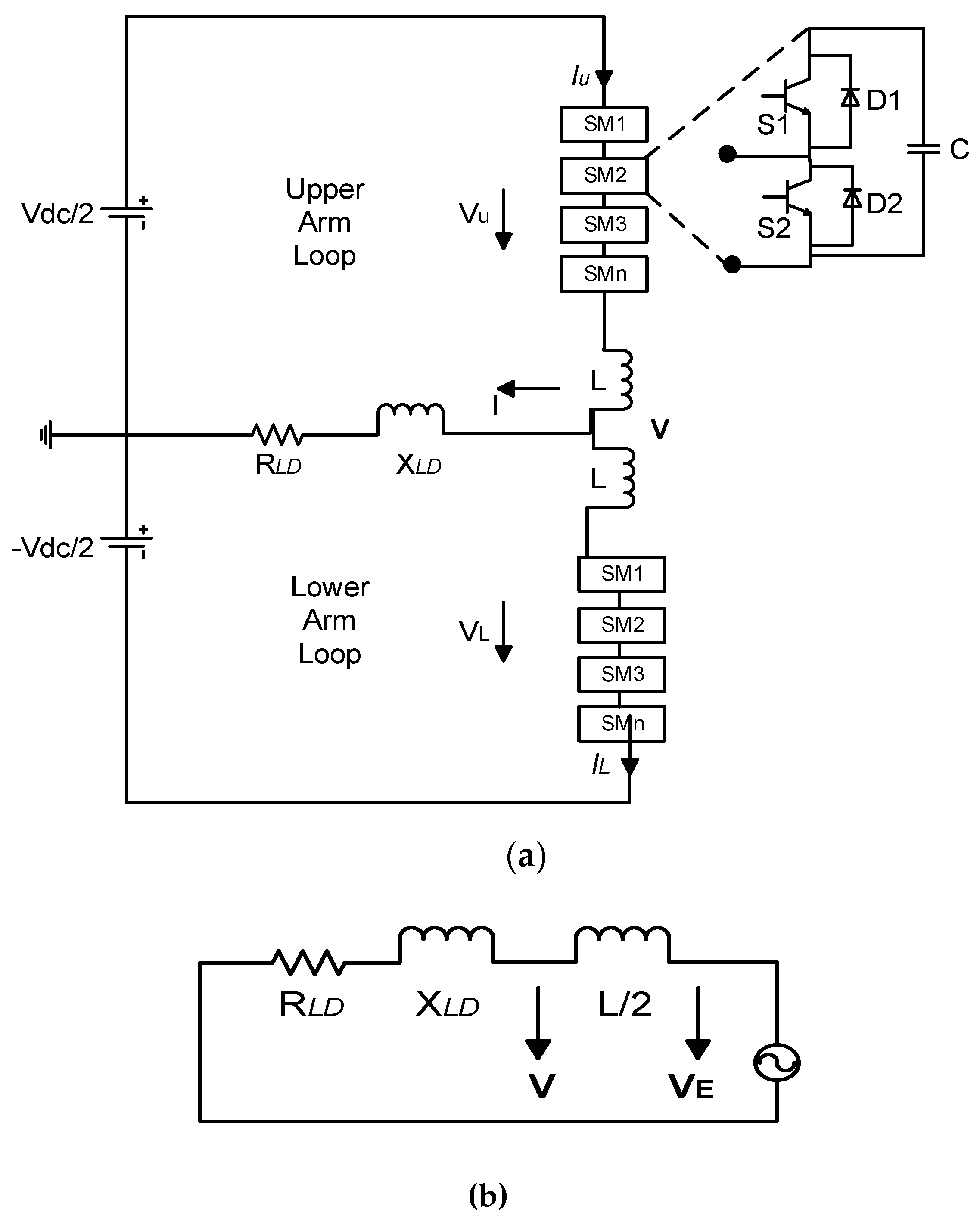

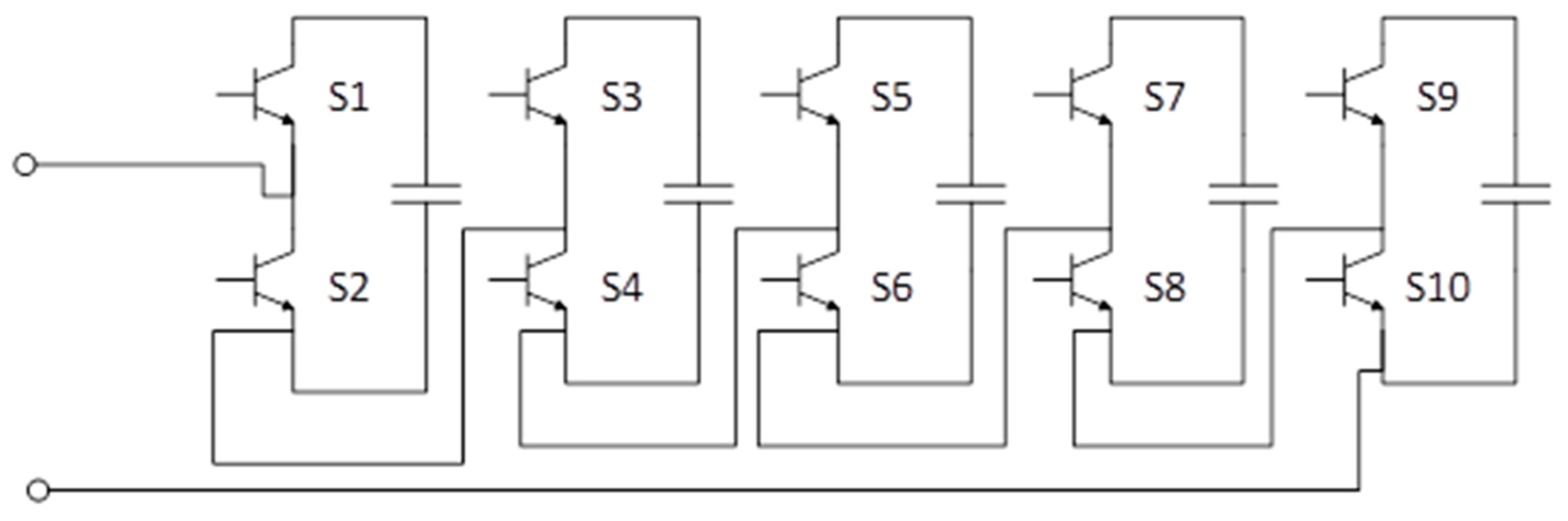

2. Comparison with Conventional Methods

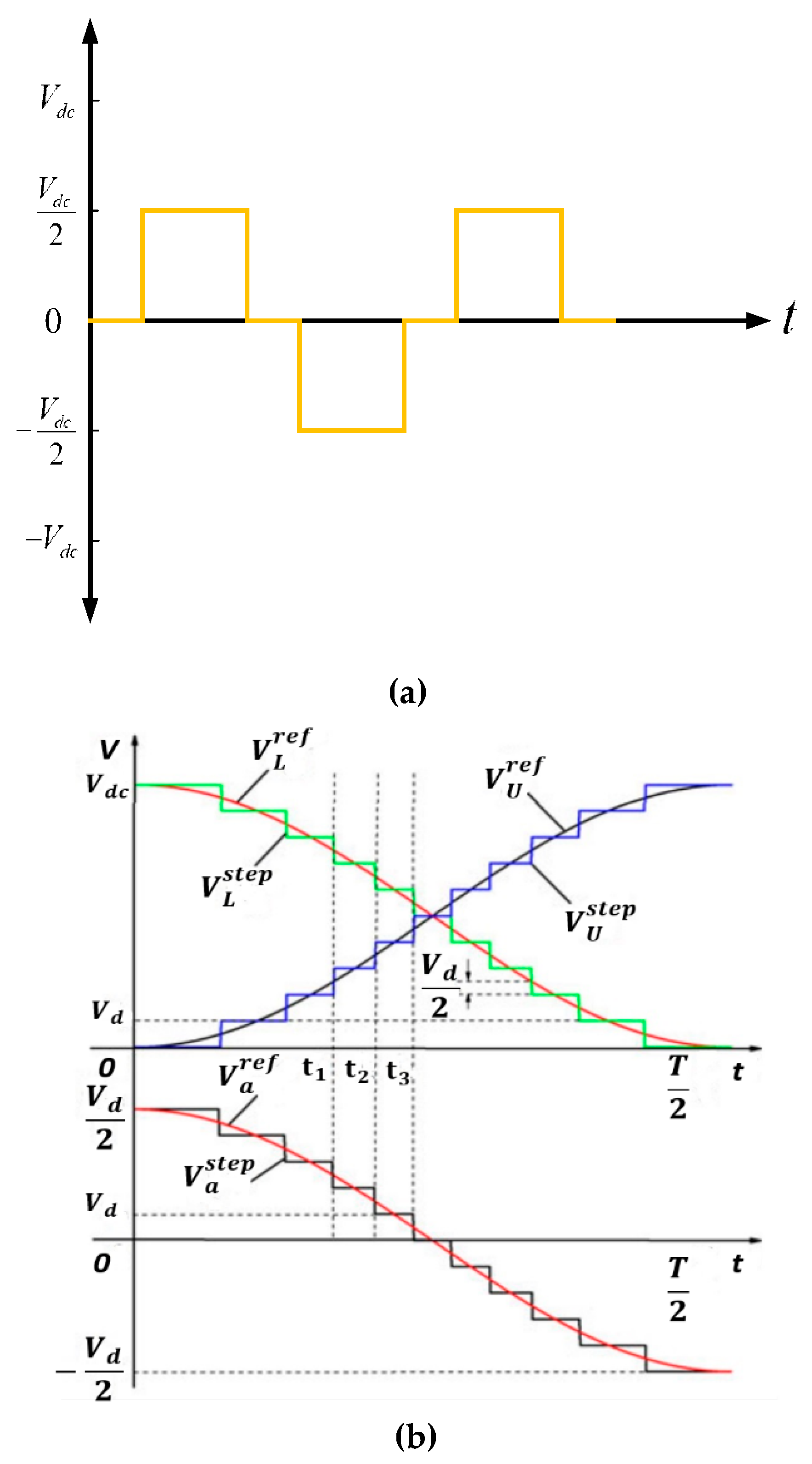

3. Operating Principles and Mathematical Modelling of the Proposed Controller Design Test Bench for the HVDC MMC

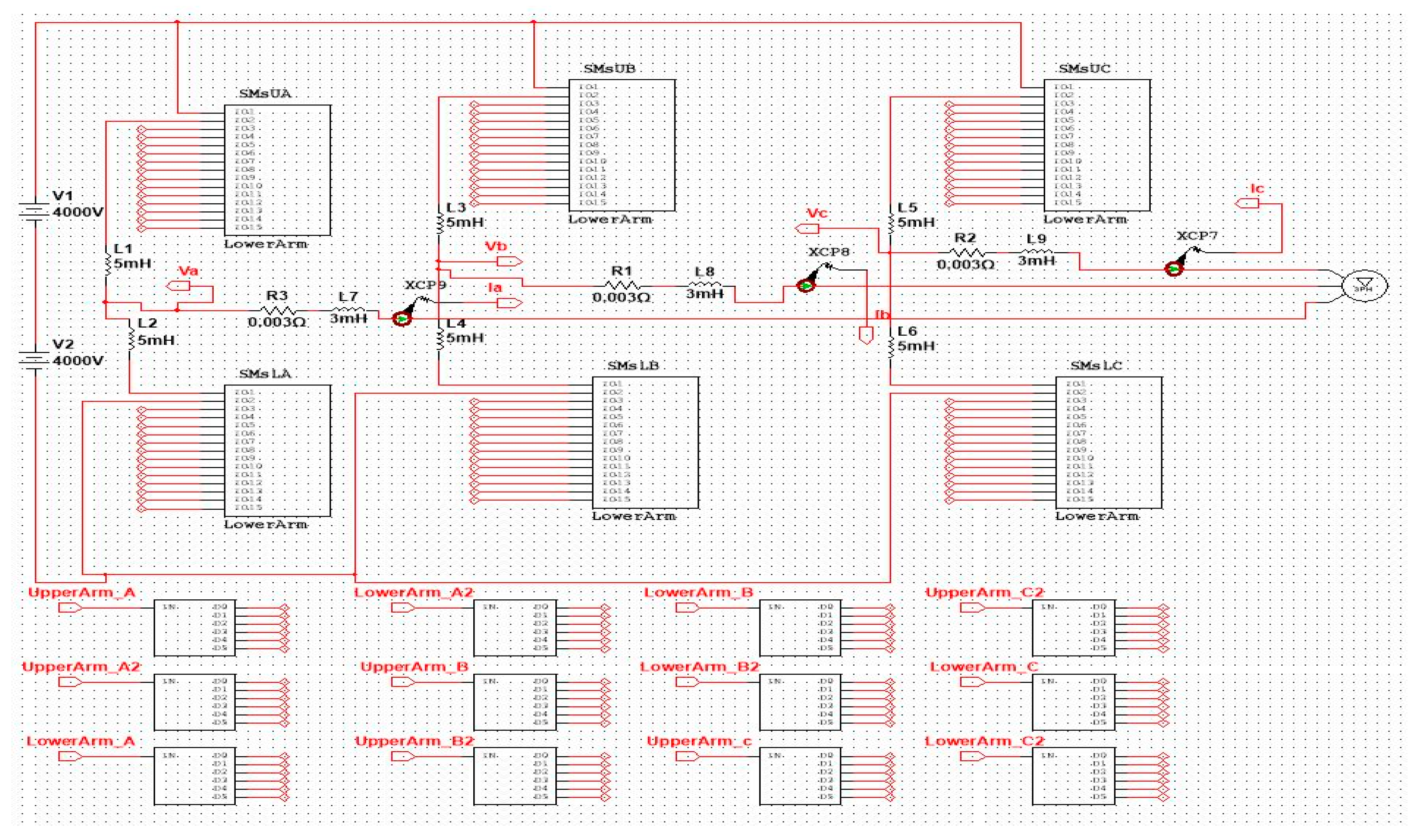

4. Proposed LabVIEW Multisim Co-Simulation Platform

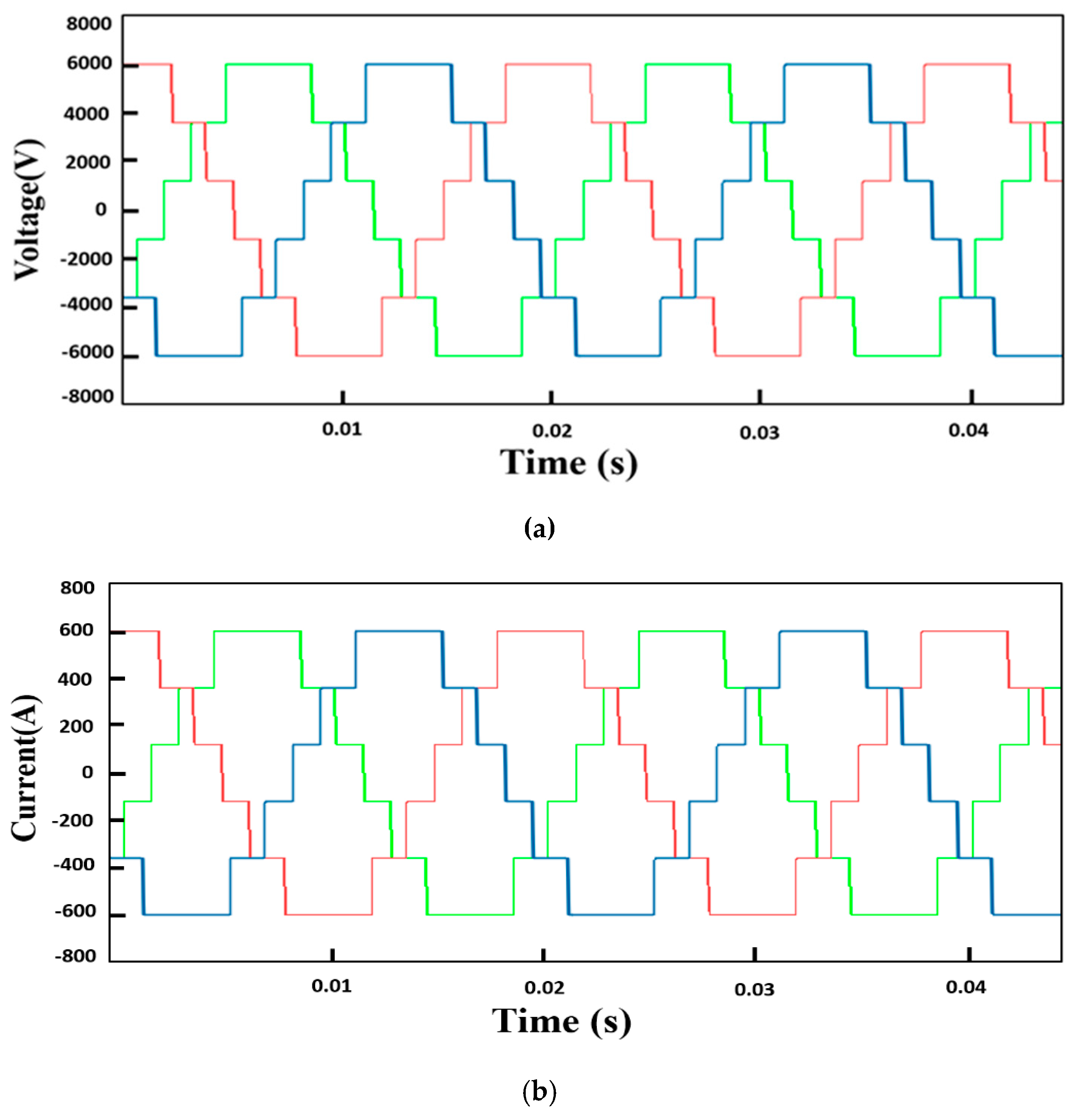

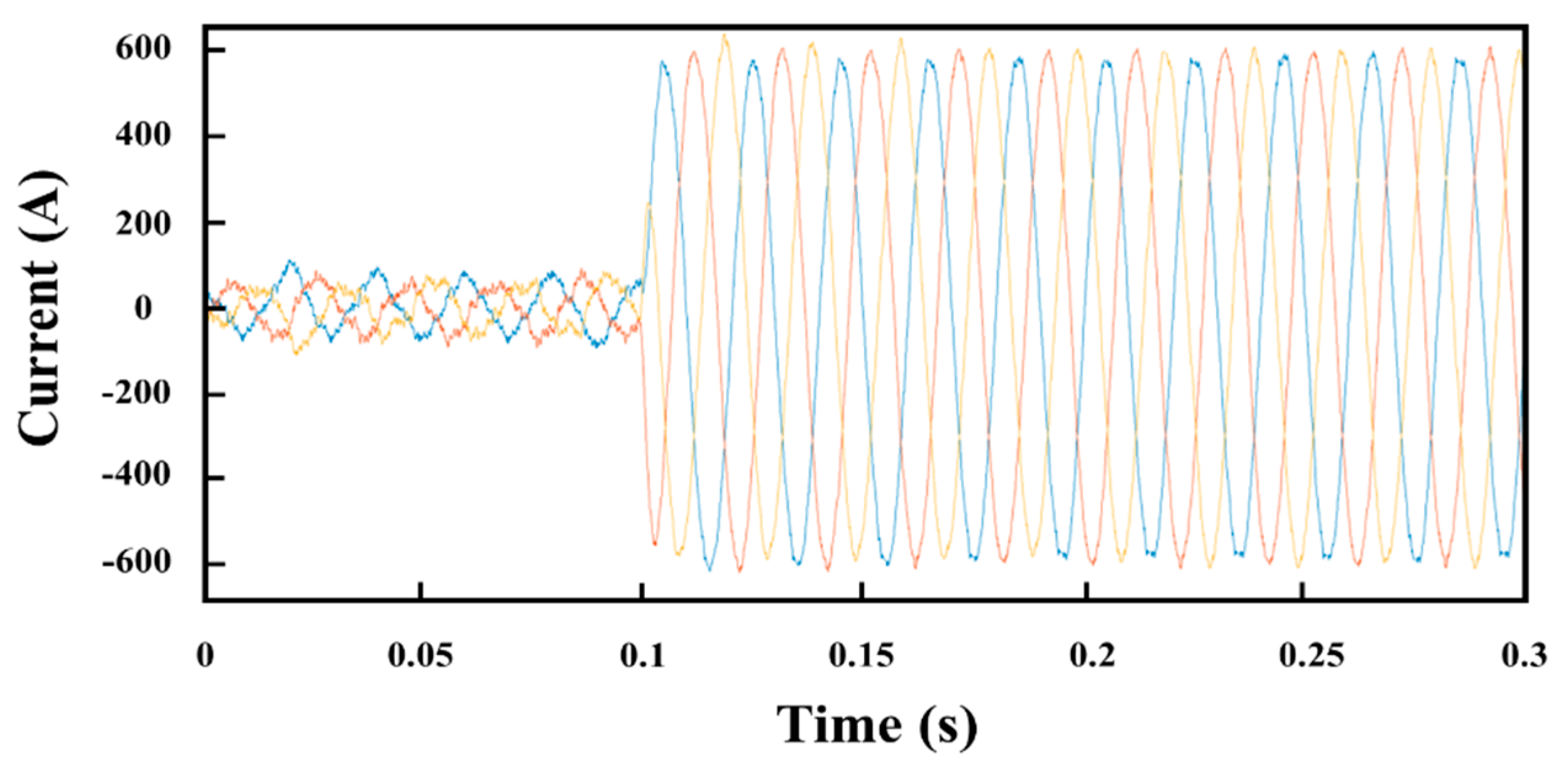

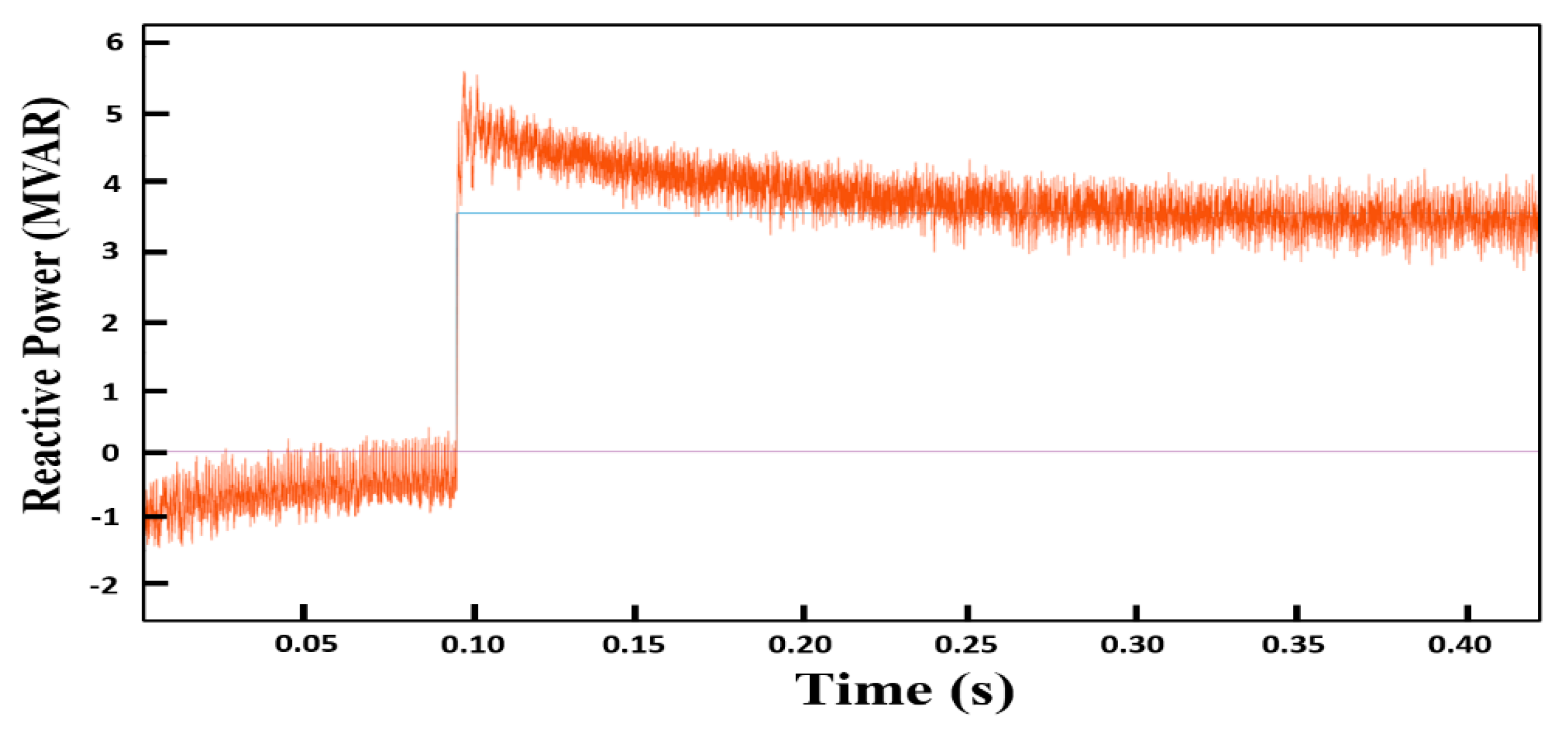

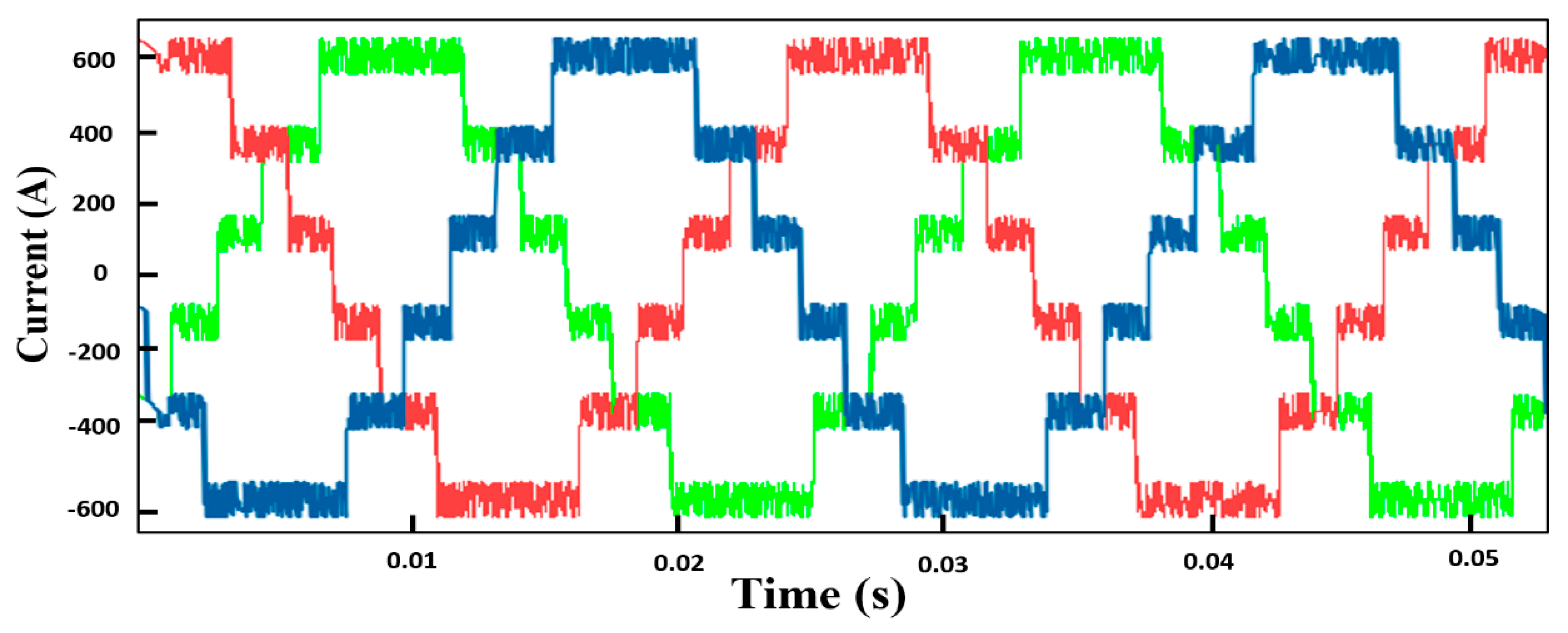

4.1. Open-Loop Results of MMC Co-Simulation

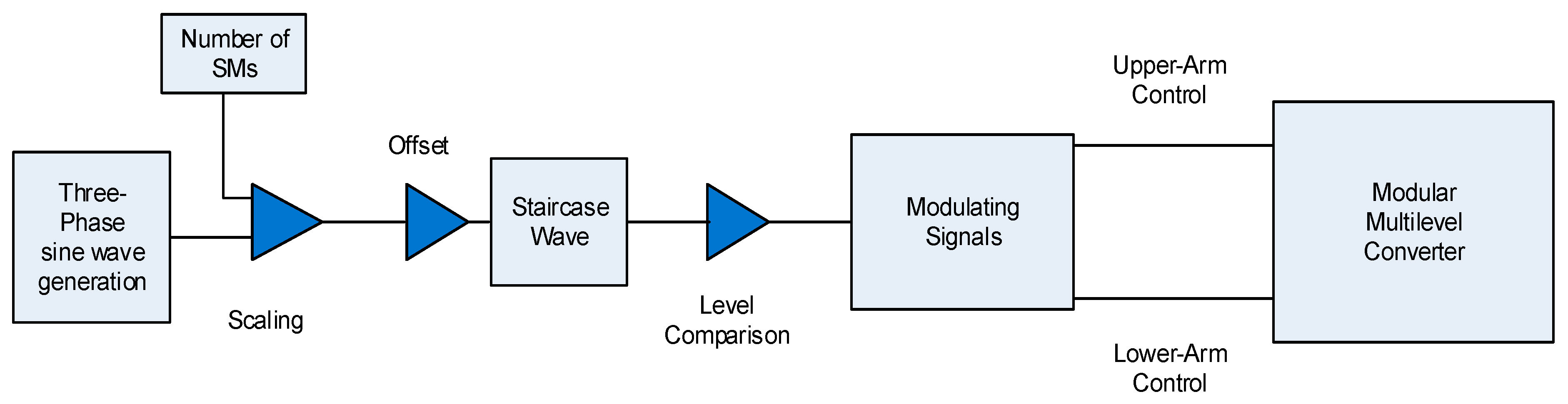

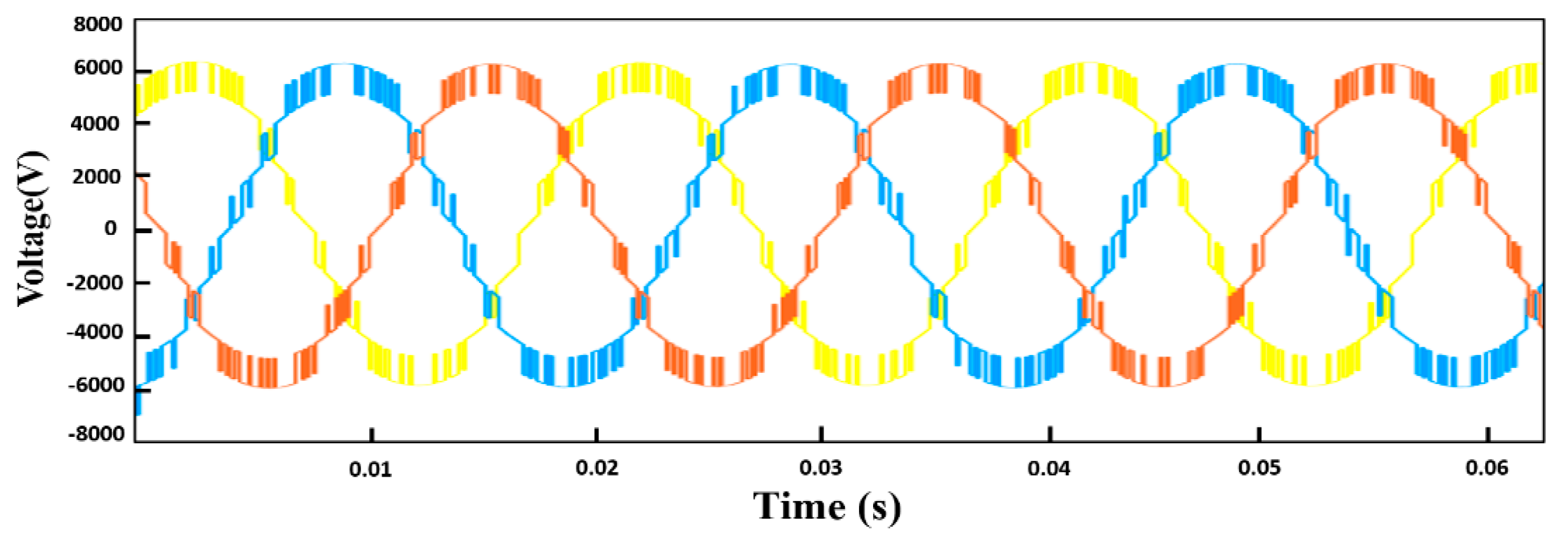

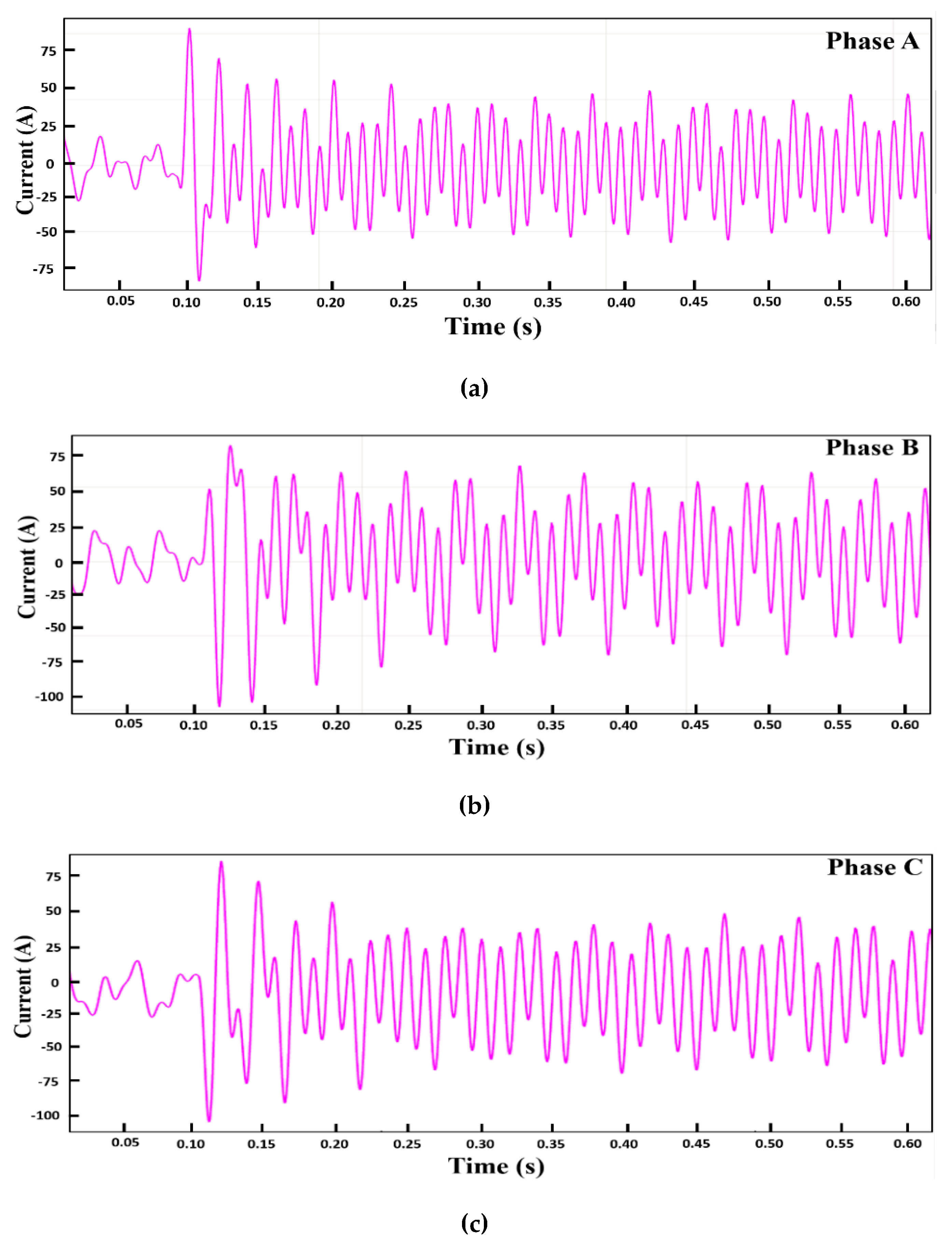

4.2. Closed-Loop NLC Algorithm Design in LabVIEW

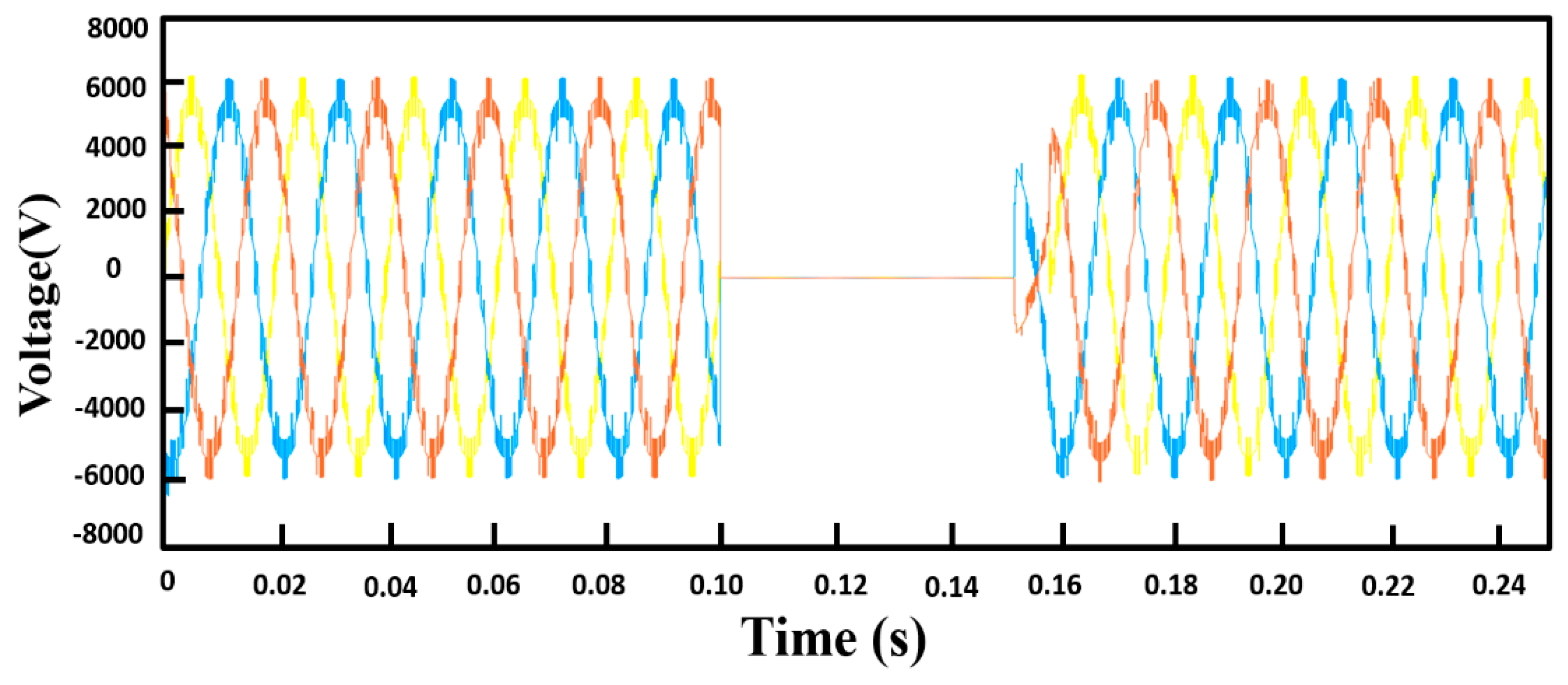

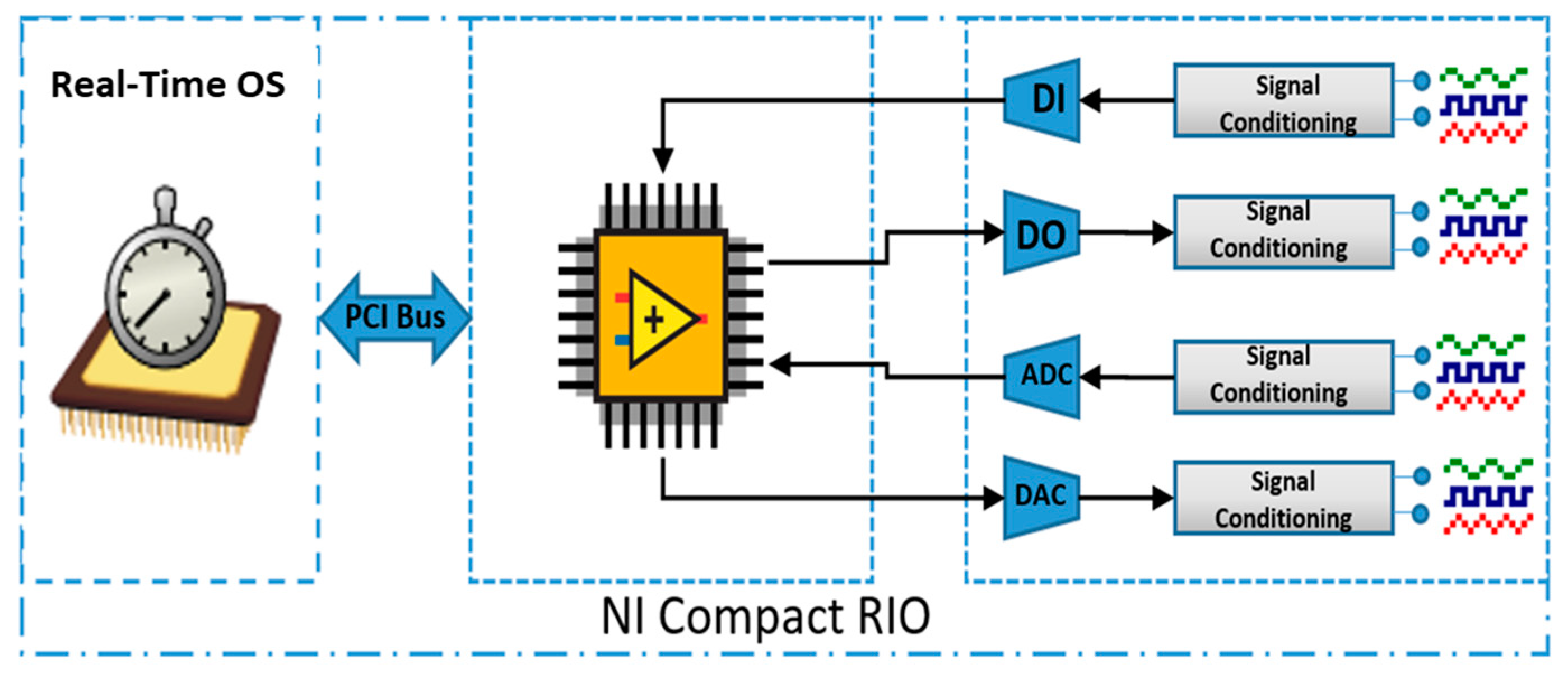

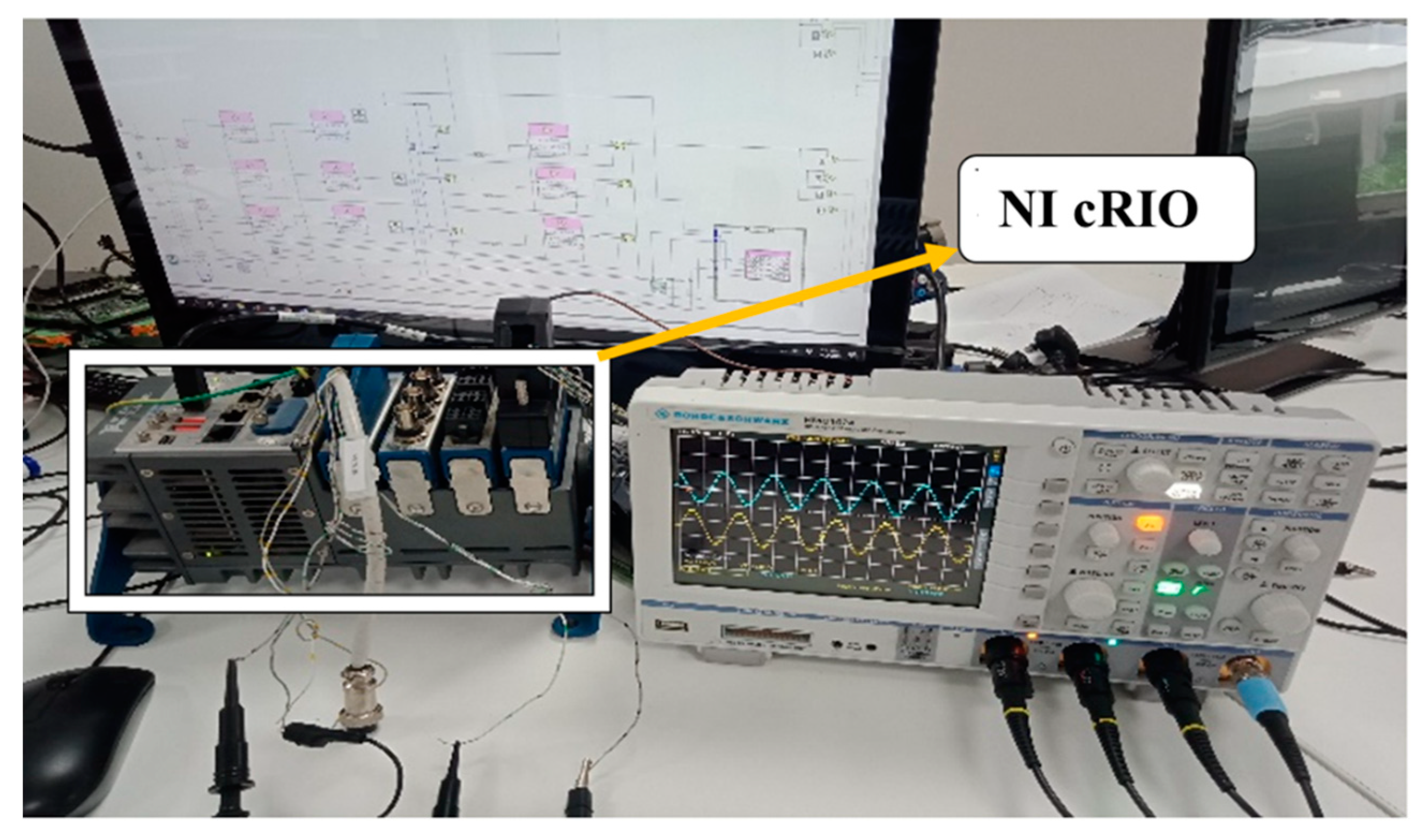

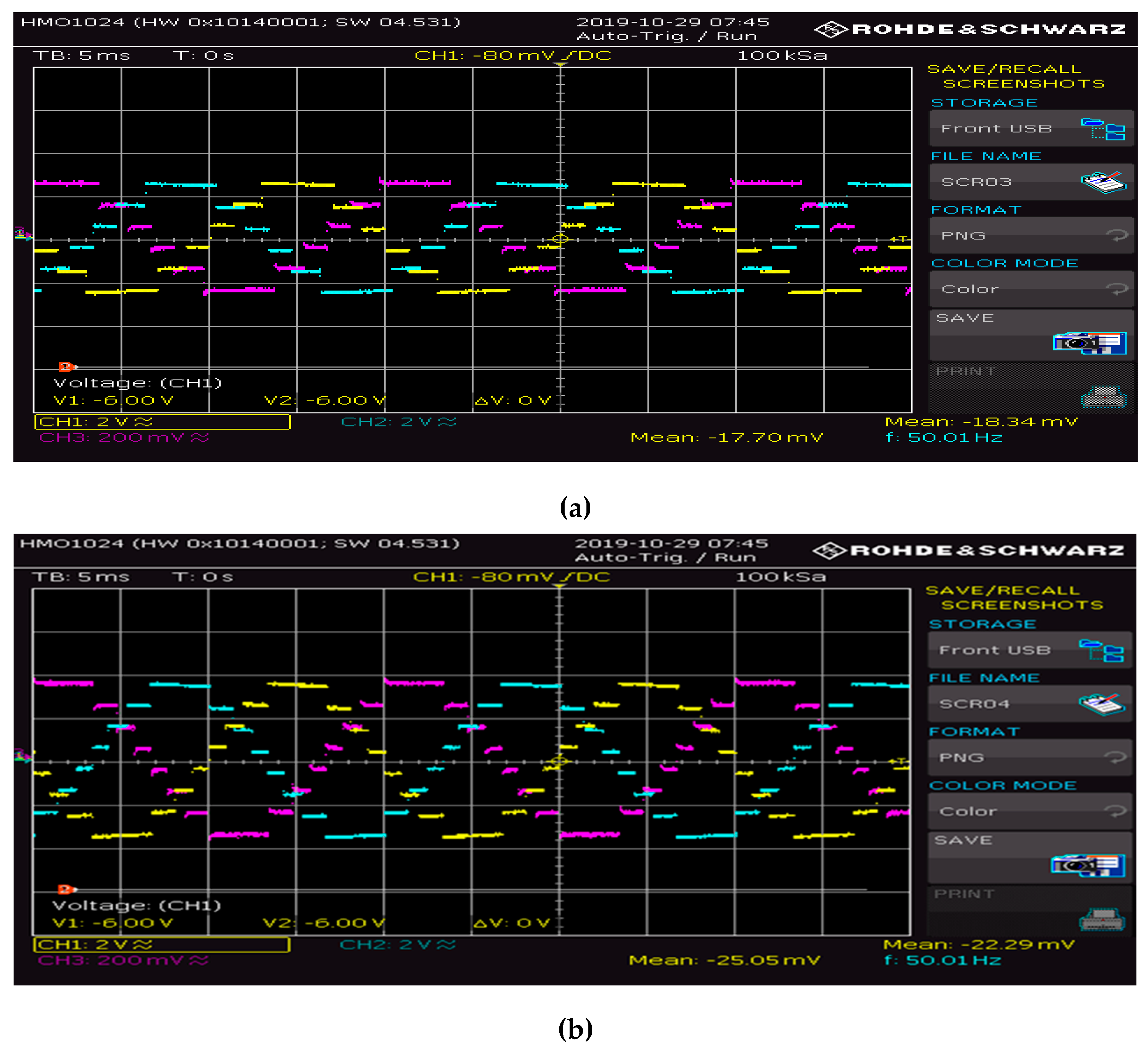

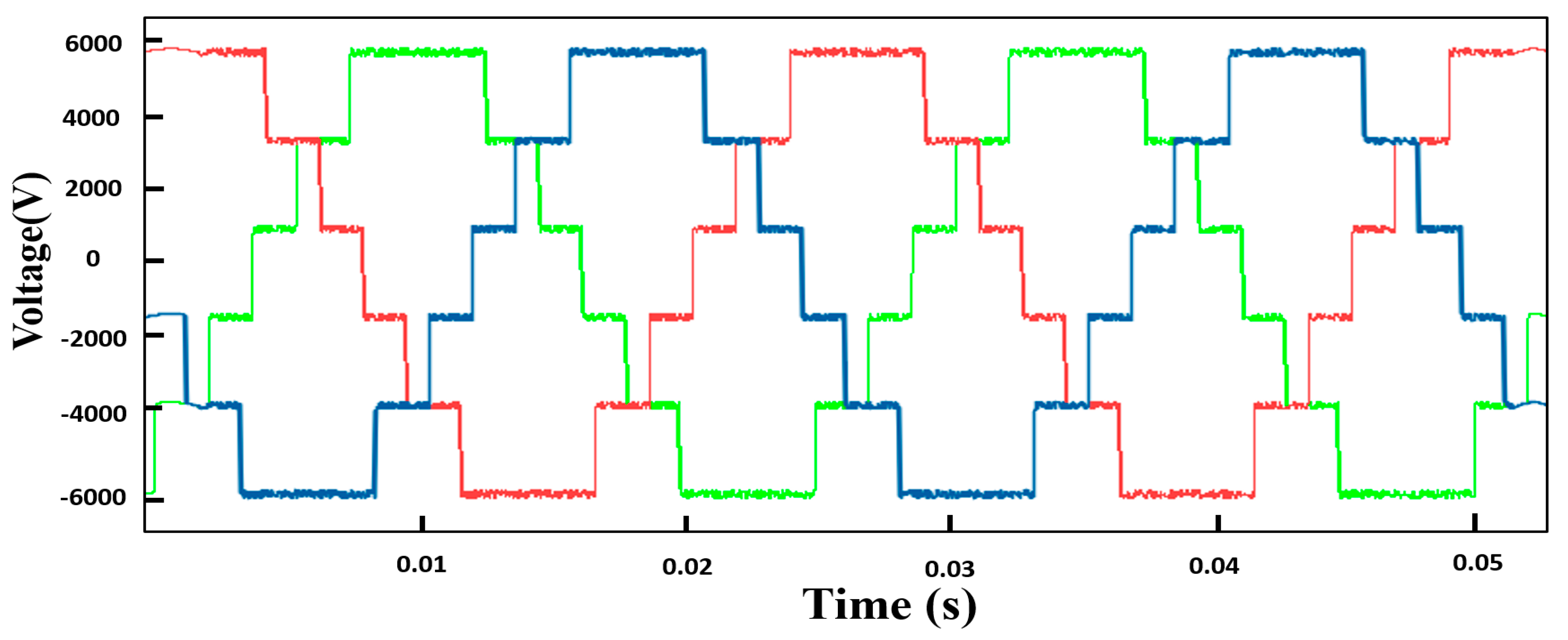

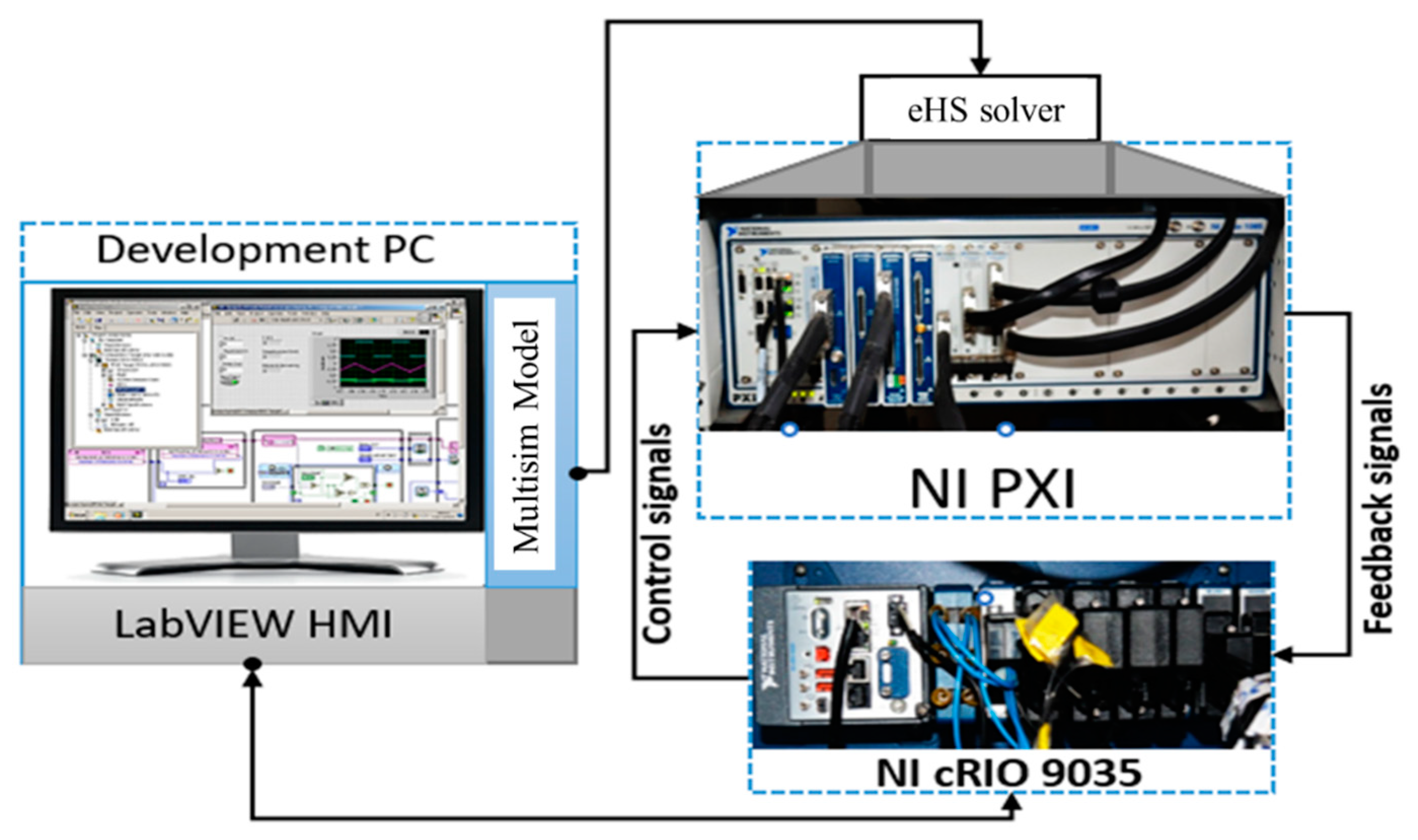

5. Real-Time Control Algorithm Implementation and Testing in NI Compact RIO and PXIe

6. State-of-the-Art Hardware-in-Loop Setup

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Bidadfar, A.; Saborío-Romano, O.; Naidu Sakamuri, J.; Akhmatov, V.; Antonio Cutululis, N.; Ejnar Sørensen, P. Coordinated Control of HVDC and HVAC Power Transmission Systems Integrating a Large Offshore Wind Farm. Energies 2019, 12, 3435. [Google Scholar] [CrossRef]

- Kalair, A.; Abas, N.; Khan, N. Comparative study of HVAC and HVDC transmission systems. Renew. Sustain. Energy Rev. 2016, 59, 1653–1675. [Google Scholar] [CrossRef]

- Chachar, F.A.; Bukhari, S.S.H.; Mangi, F.H.; MacPherson, D.E.; Harrison, G.P.; Bukhsh, W.; Ro, J.-S.; Akhter, F.; Buhksh, W. Hierarchical Control Implementation for Meshed AC/Multi-Terminal DC Grids with Offshore Windfarms Integration. IEEE Access 2019, 7, 142233–142245. [Google Scholar] [CrossRef]

- Jamshidifar, A.; Jovcic, D. Small-Signal Dynamic DQ Model of Modular Multilevel Converter for System Studies. IEEE Trans. Power Deliv. 2015, 31, 191–199. [Google Scholar] [CrossRef]

- Li, C.; Hu, X.; Guo, J.; Liang, J. The DC grid reliability and cost evaluation with Zhoushan five-terminal HVDC case study. In Proceedings of the 2015 50th International Universities Power Engineering Conference (UPEC), Stroke-on-Trent, UK, 1–4 September 2015; pp. 1–6. [Google Scholar]

- Dekka, A.; Wu, B.; Zargari, N.R. A Novel Modulation Scheme and Voltage Balancing Algorithm for Modular Multilevel Converter. IEEE Trans. Ind. Appl. 2015, 52, 432–443. [Google Scholar] [CrossRef]

- Ishfaq, M.; Uddin, W.; Zeb, K.; Khan, I.; Islam, S.U.; Adil Khan, M.; Kim, H.-J. A New Adaptive Approach to Control Circulating and Output Current of Modular Multilevel Converter. Energies 2019, 12, 1118. [Google Scholar] [CrossRef]

- Hu, P.; Jiang, D.; Zhou, Y.; Liang, Y.; Guo, J.; Lin, Z. Energy-Balancing Control Strategy for Modular Multilevel Converters under Submodule Fault Conditions. IEEE Trans. Power Electron. 2013, 29, 5021–5030. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Taheri, S.; Vechiu, I.; Catalão, J.P. Novel Control Strategy for Modular Multilevel Converters Based on Differential Flatness Theory. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 6, 888–897. [Google Scholar] [CrossRef]

- Cui, S.; Kim, S.; Jung, J.-J.; Sul, S.-K. A comprehensive cell capacitor energy control strategy of a modular multilevel converter (MMC) without a stiff DC bus voltage source. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 602–609. [Google Scholar]

- Li, K.; Yuan, L.; Zhao, Z.; Lu, S.; Zhang, Y. Fault-Tolerant Control of MMC With Hot Reserved Submodules Based on Carrier Phase Shift Modulation. IEEE Trans. Power Electron. 2016, 32, 6778–6791. [Google Scholar] [CrossRef]

- Lee, Y.; Cui, S.; Kim, S.; Sul, S.-K. Control of hybrid HVDC transmission system with LCC and FB-MMC. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 13–18 September 2014; pp. 475–482. [Google Scholar]

- Zhou, Y.; Jiang, D.; Hu, P.; Guo, J.; Liang, Y.; Lin, Z. A Prototype of Modular Multilevel Converters. IEEE Trans. Power Electron. 2013, 29, 3267–3278. [Google Scholar] [CrossRef]

- Moranchel, M.; Sánchez, F.M.; Bueno, E.J.; Rodriguez, F.J.; Sanz, I. Six-Level modular multilevel converter prototype with centralized hardware platform controller. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 3863–3868. [Google Scholar]

- Schnarrenberger, M.; Kammerer, F.; Brackle, D.; Braun, M. Cell design of a square-wave powered 1AC-3AC modular multilevel converter low voltage prototype. In Proceedings of the 2016 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–11. [Google Scholar]

- Wang, Z.; Hua, L.; Ma, Y. A Control Strategy of Modular Multilevel Converter with Integrated Battery Energy Storage System Based on Battery Side Capacitor Voltage Control. Energies 2019, 12, 2151. [Google Scholar] [CrossRef]

- Hakimi, S.M.; Hajizadeh, A. Integration of Photovoltaic Power Units to Power Distribution System through Modular Multilevel Converter. Energies 2018, 11, 2753. [Google Scholar] [CrossRef]

- Yin, J.; Wu, W.; Tongzhen, W.; Xuezhi, W.; Qunhai, H. A Novel Fault-Tolerant Control of Modular Multilevel Converter under Sub-Module Faults based on Phase Disposition PWM. Energies 2018, 12, 20. [Google Scholar] [CrossRef]

- Kim, K.-M.; Kim, J.-H.; Kim, D.-H.; Han, B.-M.; Lee, J.Y. Improved Pre-Charging Method for MMC-Based HVDC Systems Operated in Nearest Level Control. J. Power Electron. 2017, 17, 127–135. [Google Scholar] [CrossRef]

- Talon Louokdom, E.; Gavin, S.; Siemaszko, D.; Biya-Motto, F.; Essimbi Zobo, B.; Marchesoni, M.; Carpita, M. Small-Scale Modular Multilevel Converter for Multi-Terminal DC Networks Applications: System Control Validation. Energies 2018, 11, 1690. [Google Scholar] [CrossRef]

- Andrus, M.; Ravindra, H.; Hauer, J.; Steurer, M.; Bosworth, M.; Soman, R. PHIL implementation of a MVDC fault management test bed for ship power systems based on megawatt-scale modular multilevel converters. In Proceedings of the 2015 IEEE Electric Ship Technologies Symposium (ESTS), Old Town Alexandria, VA, USA, 21–24 June 2015; pp. 337–342. [Google Scholar]

- Liang, T.; Dinavahi, V. Real-Time Device-Level Simulation of MMC-Based MVDC Traction Power System on MPSoC. IEEE Trans. Transp. Electrific. 2018, 4, 626–641. [Google Scholar] [CrossRef]

- Blaszczyk, P.; Steurer, M.; Soto, D.; Bogdan, F.; Hauer, J.; Sloderbeck, M.; Schoder, K. Modular multilevel converter based test bed for mvdc applications—A case study with a 12 kV, 5 MW setup. In Proceedings of the 2016 IEEE International Power Electronics and Motion Control Conference (PEMC), Varna, Bulgaria, 25–30 September 2016; pp. 139–145. [Google Scholar]

- Zhang, S.; Wang, S.; Praisuwanna, N.; Kong, L.; Li, Y.; Martin, R.B.; Wang, F.; Tolbert, L.M. Development of a Flexible Modular Multilevel Converter Test-Bed. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 24–27 September 2018; pp. 5250–5257. [Google Scholar]

- Guillaud, X.; Faruque, M.O.; Teninge, A.; Hariri, A.H.; Vanfretti, L.; Paolone, M.; Dinavahi, V.; Mitra, P.; Lauss, G.; Dufour, C.; et al. Applications of Real-Time Simulation Technologies in Power and Energy Systems. IEEE Power Energy Technol. Syst. J. 2015, 2, 103–115. [Google Scholar] [CrossRef]

- Li, Y.; Shi, X.; Liu, B.; Lei, W.; Wang, F.; Tolbert, L.M. Development, Demonstration, and Control of a Testbed for Multiterminal HVDC System. IEEE Trans. Power Electron. 2017, 32, 6069–6078. [Google Scholar] [CrossRef]

- Steurer, M.M.; Schoder, K.; Faruque, O.; Soto, D.; Bosworth, M.; Sloderbeck, M.; Bogdan, F.; Hauer, J.; Winkelnkemper, M.; Schwager, L.; et al. Multifunctional Megawatt-Scale Medium Voltage DC Test Bed Based on Modular Multilevel Converter Technology. IEEE Trans. Transp. Electrific. 2016, 2, 597–606. [Google Scholar] [CrossRef]

- Wang, L.; Bosworth, M.; Hauer, J.; Soto, D.; Schoder, K.; Steurer, M. Common-Mode Characterization of a Modular Multilevel Converter in a Megawatt-scale Medium-Voltage DC Test Bed. In Proceedings of the 2019 IEEE Electric Ship Technologies Symposium (ESTS), Washington, DC, USA, 14–16 August 2019; pp. 388–395. [Google Scholar]

| 1-Phase | SM Number | Output Voltage Levels | ||||||

|---|---|---|---|---|---|---|---|---|

| 0 | ½ Vdc | 0 | −½ Vdc | 0 | ½ Vdc | 0 | ||

| Upper Arm | SM1 | ✓ | ✕ | ✓ | ✓ | ✓ | ✕ | ✓ |

| SM2 | ✕ | ✕ | ✕ | ✓ | ✕ | ✕ | ✕ | |

| Lower Arm | SM1 | ✓ | ✓ | ✓ | ✕ | ✓ | ✓ | ✓ |

| SM2 | ✕ | ✓ | ✕ | ✕ | ✕ | ✓ | ✕ | |

| Item No. | System Parameters | Values |

|---|---|---|

| 1 | Rated power | 10 MVA |

| 2 | Vac grid voltage | 4.16 kV |

| 3 | Vdc | 8 kV |

| 4 | Switching frequency | 300 Hz |

| 5 | Rated frequency | 50 Hz |

| 6 | SM_cap (submodule capacitance) | 5000 μF |

| 7 | L_arm (arm inductance) | 5 mH |

| 8 | L_val (line inductance) | 3 mH |

| 9 | R_line (line resistance) | 0.003 Ω |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ali, S.; Badar, J.; Akhter, F.; Bukhari, S.S.H.; Ro, J.-S. Real-Time Controller Design Test Bench for High-Voltage Direct Current Modular Multilevel Converters. Appl. Sci. 2020, 10, 6004. https://doi.org/10.3390/app10176004

Ali S, Badar J, Akhter F, Bukhari SSH, Ro J-S. Real-Time Controller Design Test Bench for High-Voltage Direct Current Modular Multilevel Converters. Applied Sciences. 2020; 10(17):6004. https://doi.org/10.3390/app10176004

Chicago/Turabian StyleAli, Saddaqat, Jahangir Badar, Faheem Akhter, Syed Sabir Hussain Bukhari, and Jong-Suk Ro. 2020. "Real-Time Controller Design Test Bench for High-Voltage Direct Current Modular Multilevel Converters" Applied Sciences 10, no. 17: 6004. https://doi.org/10.3390/app10176004

APA StyleAli, S., Badar, J., Akhter, F., Bukhari, S. S. H., & Ro, J.-S. (2020). Real-Time Controller Design Test Bench for High-Voltage Direct Current Modular Multilevel Converters. Applied Sciences, 10(17), 6004. https://doi.org/10.3390/app10176004