A Review on the Fabrication and Reliability of Three-Dimensional Integration Technologies for Microelectronic Packaging: Through-Si-via and Solder Bumping Process

Abstract

1. Introduction

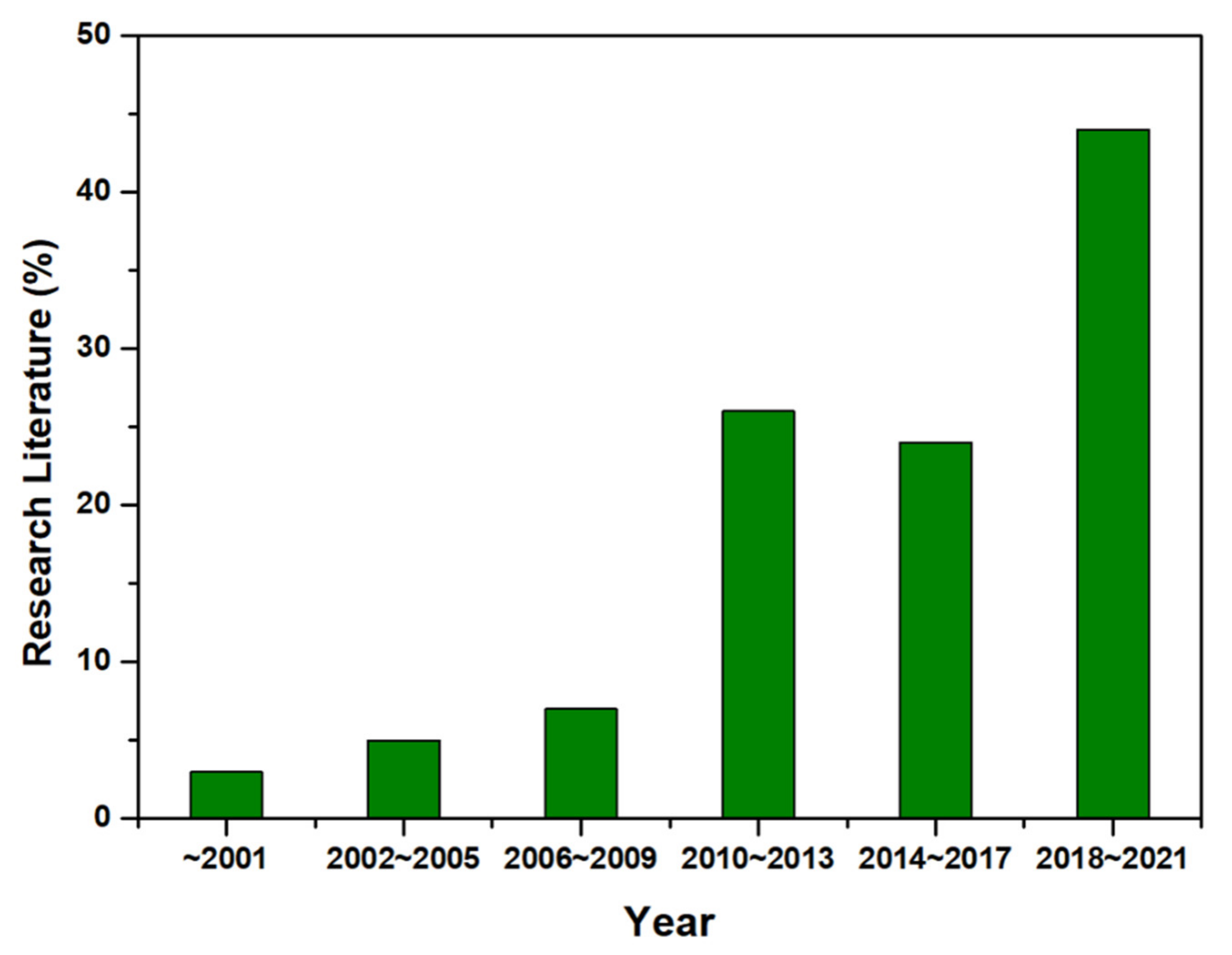

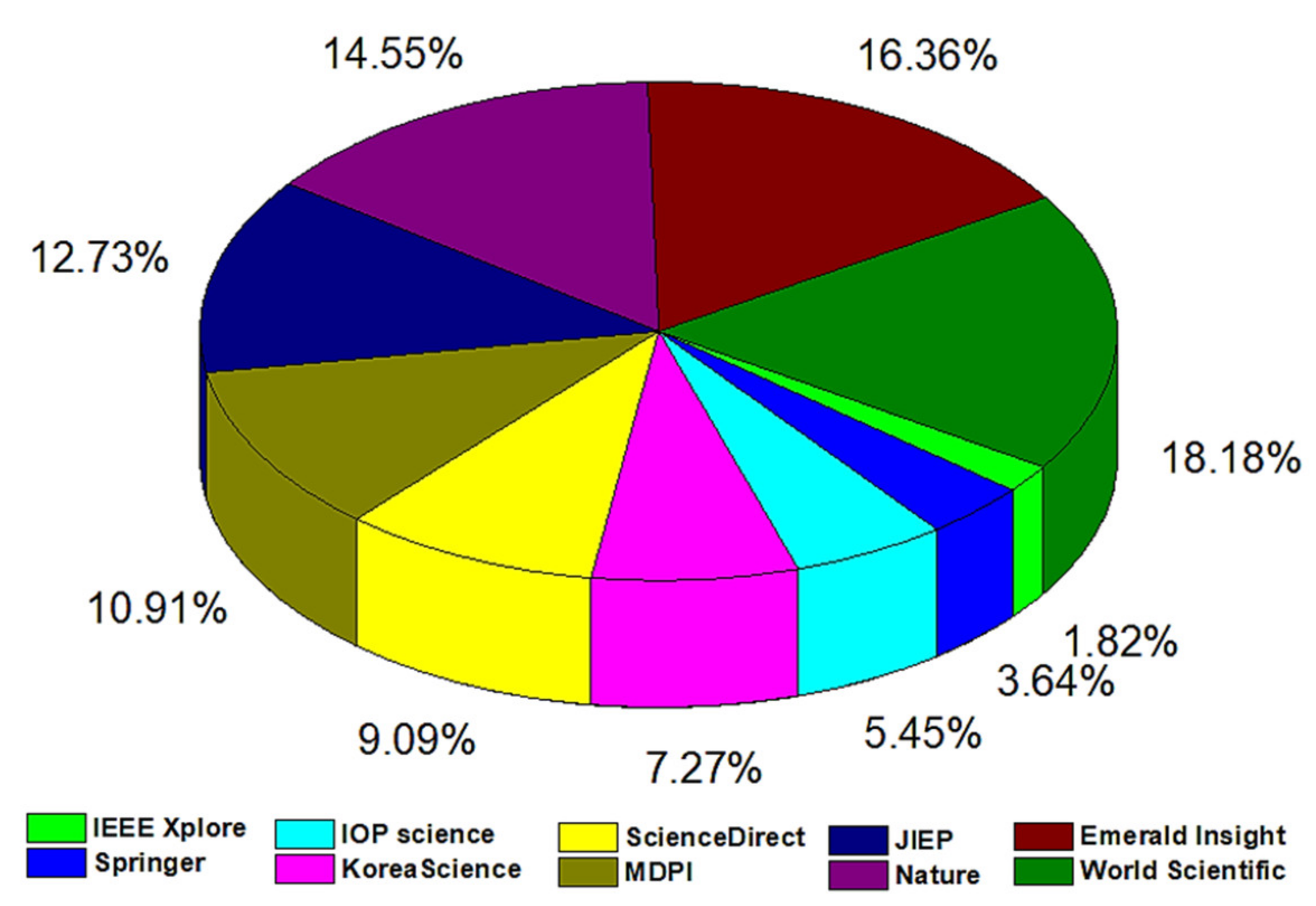

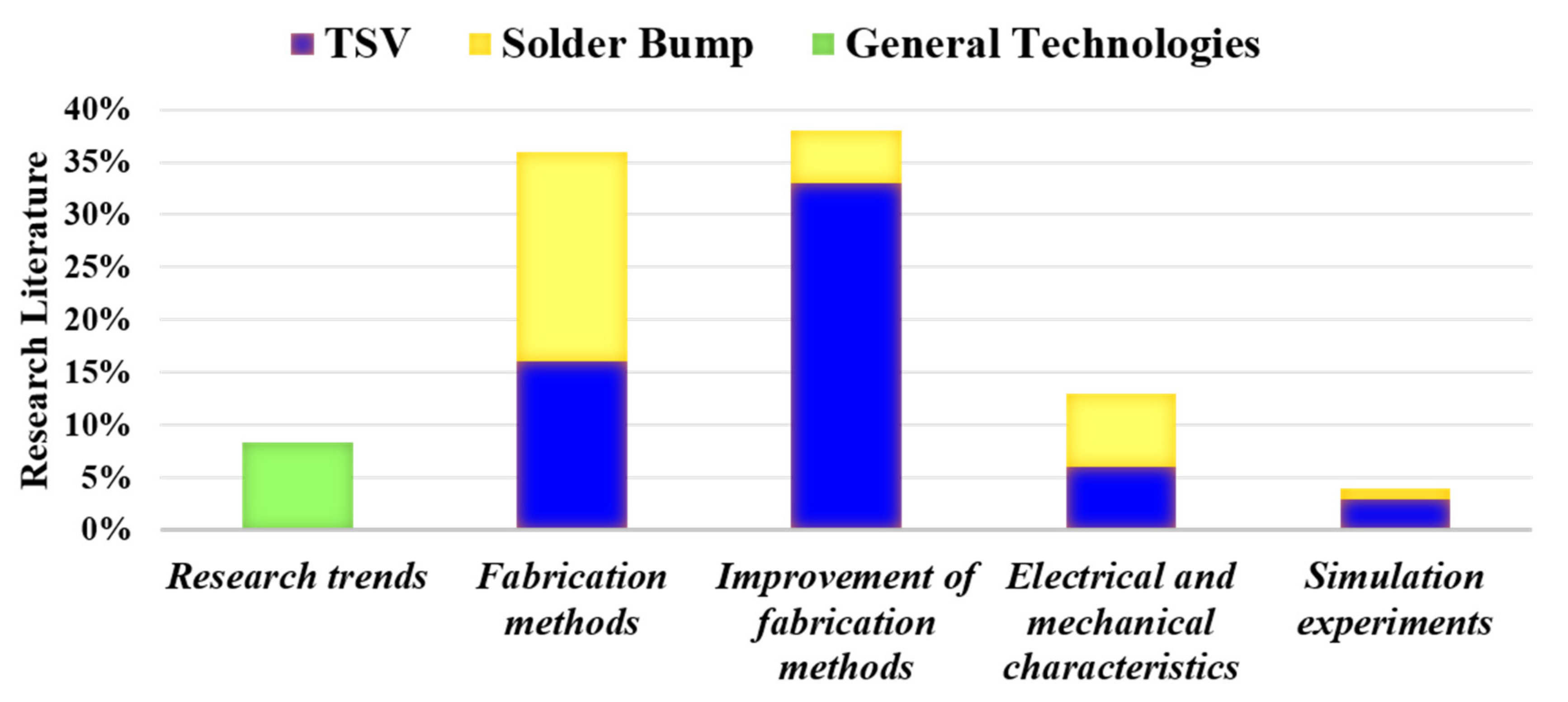

Research Methodology

- Collective overview of 3D packaging technologies and their importance in recent microelectronic packaging is introduced.

- Research trends and challenges associated with the TSV fabrication techniques is discussed systematically, and the important features are highlighted.

- The electrical and mechanical properties of TSV are analyzed in relation to their fabrication technique, and the future direction to overcome the reliability issues is discussed.

- Research trends and recent developments associated with solder bumping techniques are reviewed and illustrated pictorially.

- The advantages and disadvantages of various solder bumping techniques are tabulated with respect to current technological limitations.

- The future directions to improve the reliability of the solder bumping is discussed in terms of controlling the intermetallic compound at the TSV/solder bumping interface.

2. Through-Si-via

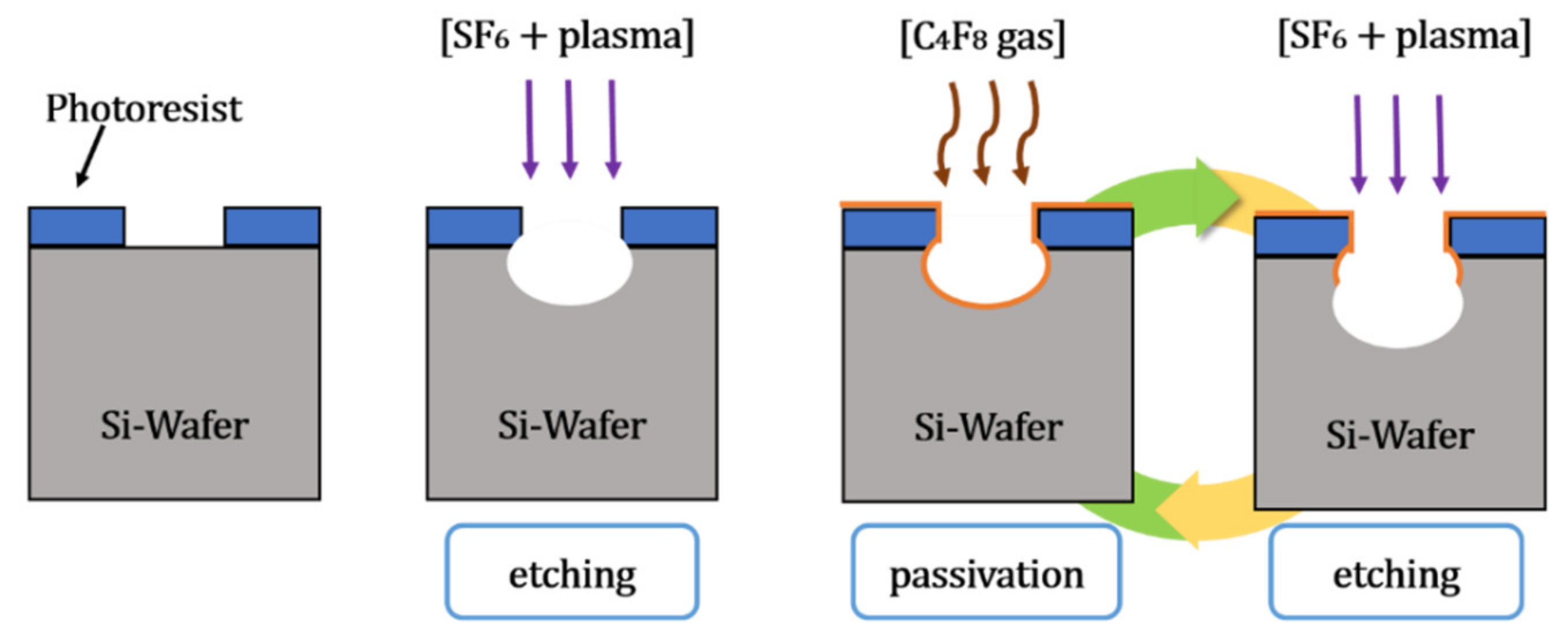

2.1. TSV Formation and DRIE Technology

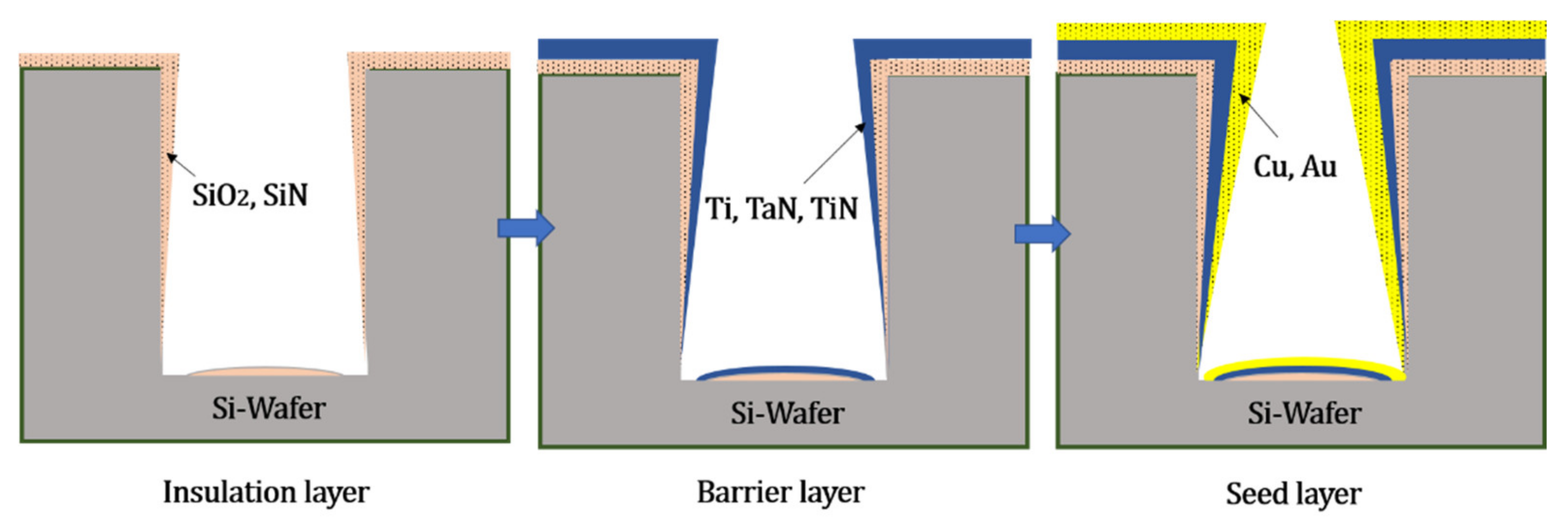

2.2. TSV Inner Wall Coating

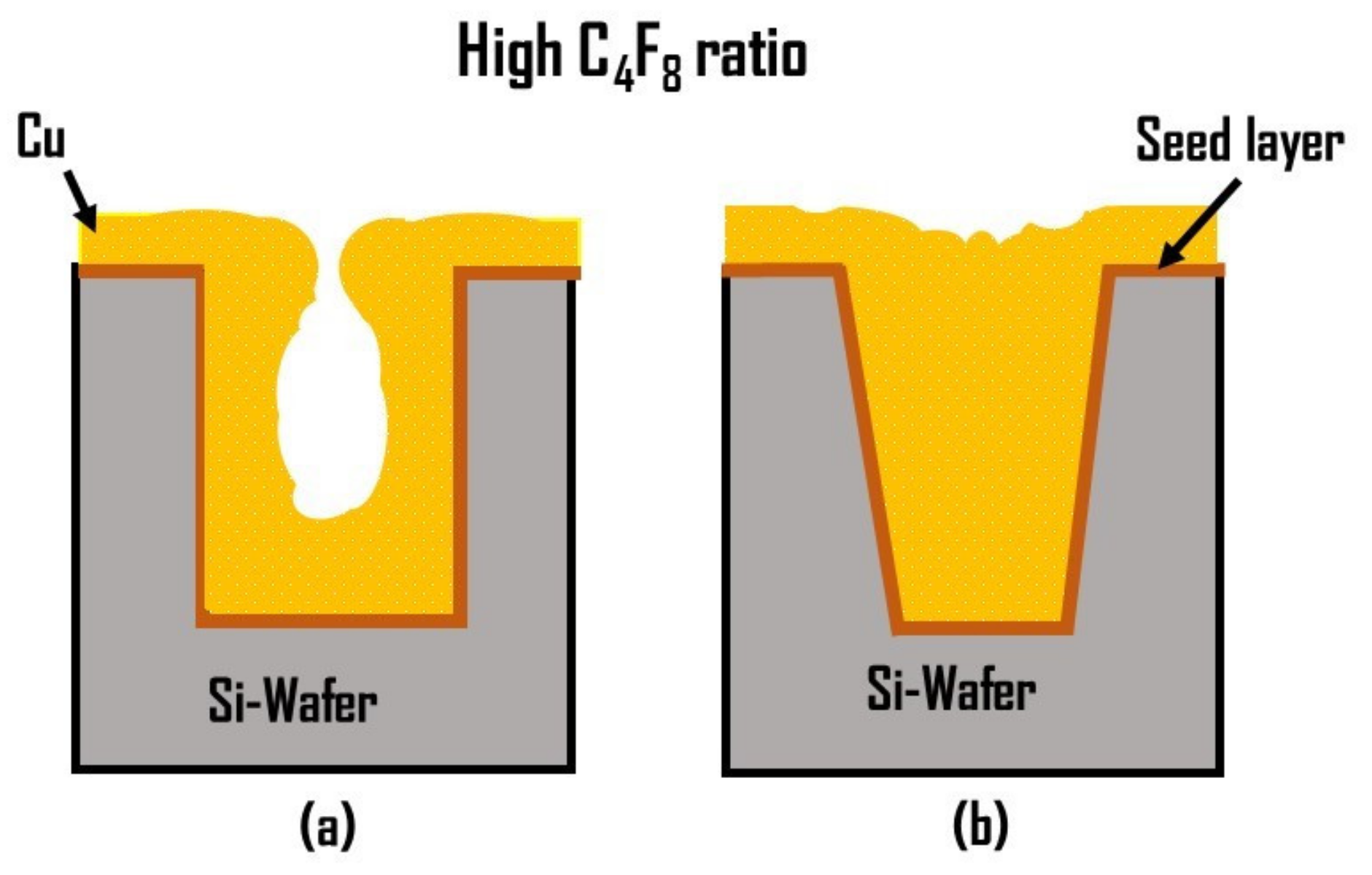

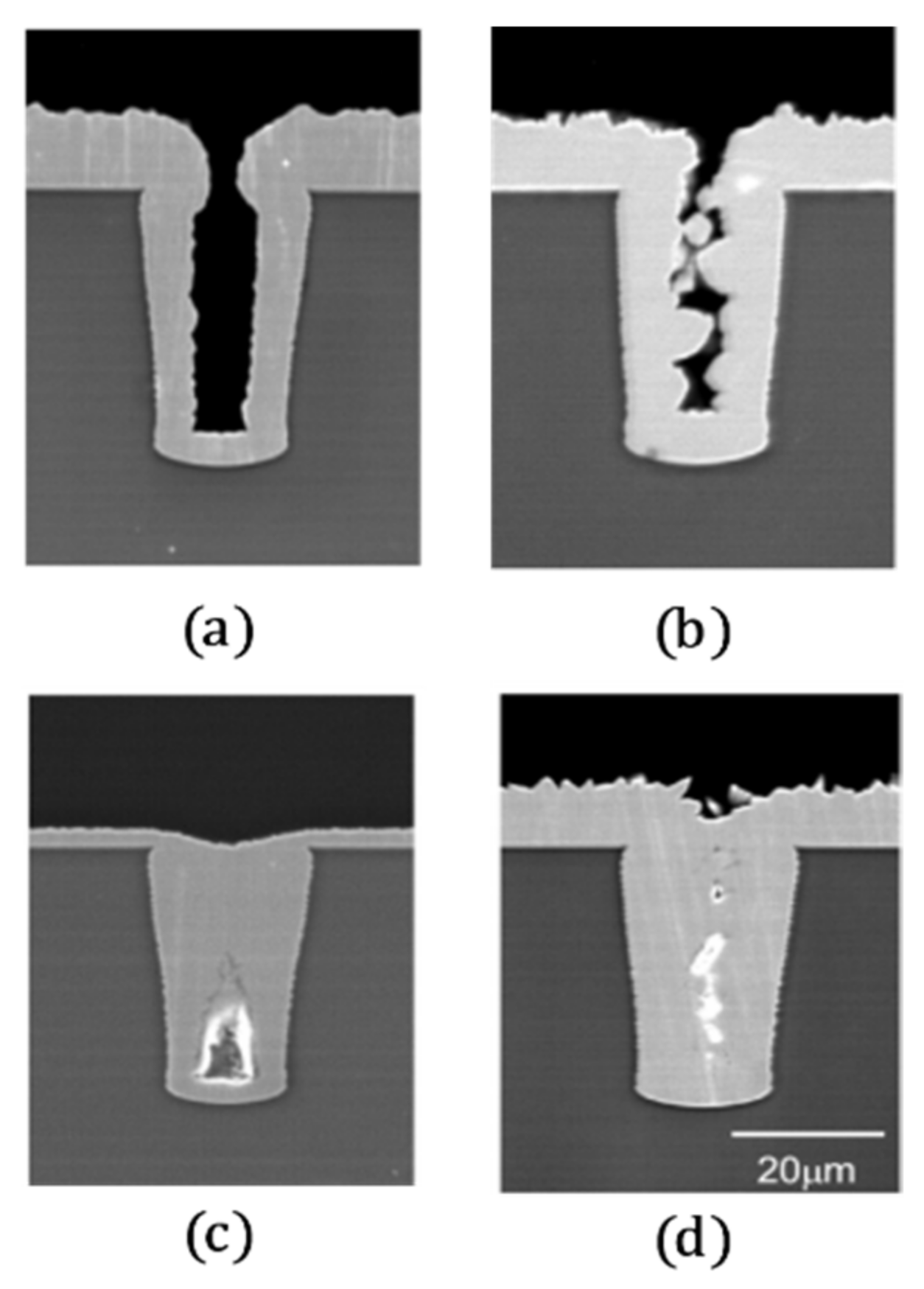

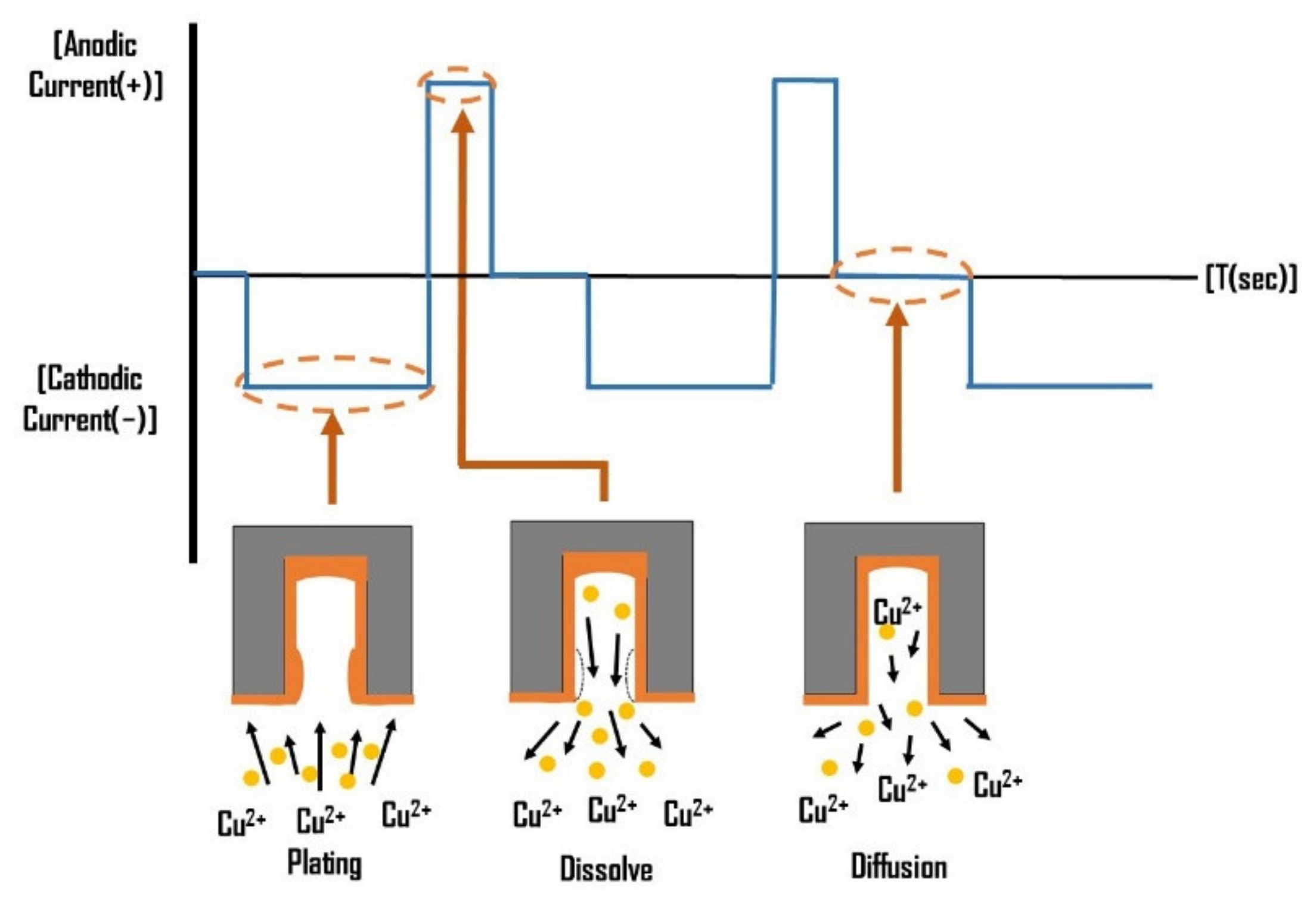

2.3. TSV Filling

2.4. Electrical Properties of TSV

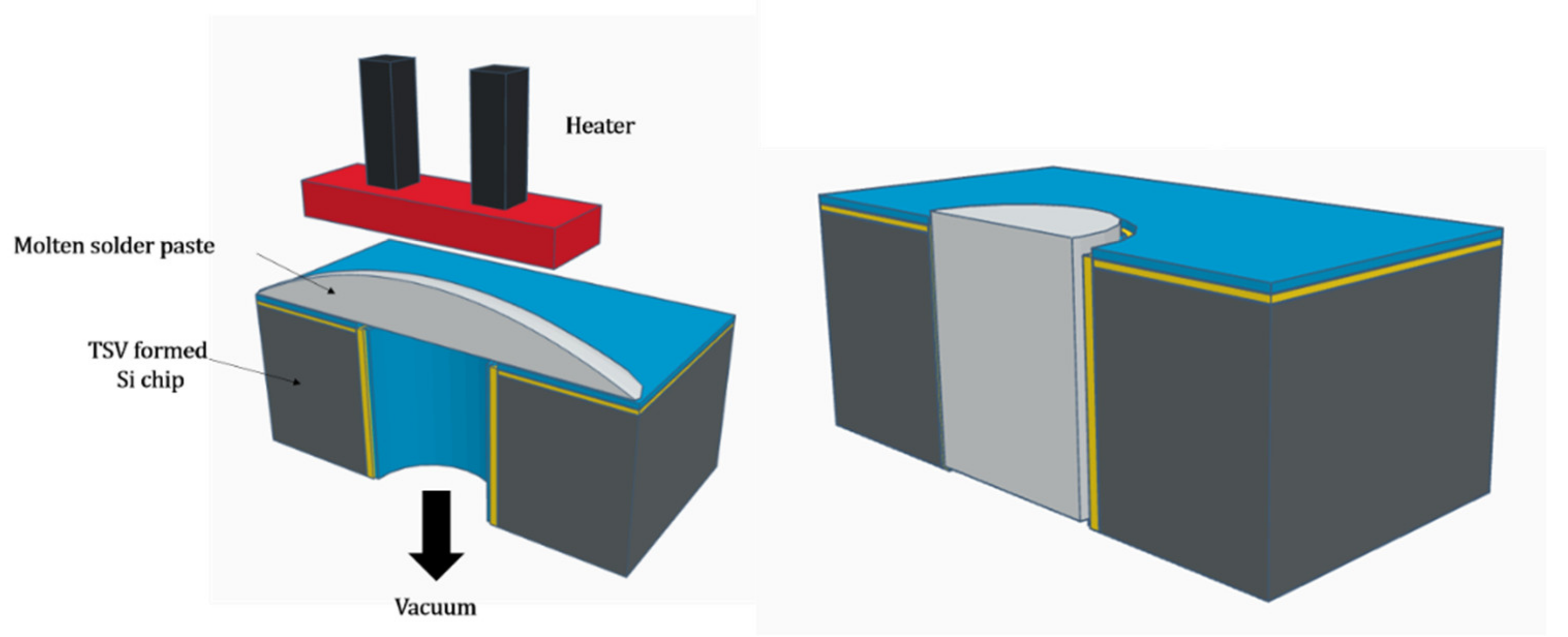

2.5. TSV Filling with Molten Solder

2.6. Reliability of TSV and Future Directions

3. Solder Bumping

3.1. Solder Bump by Electroplating

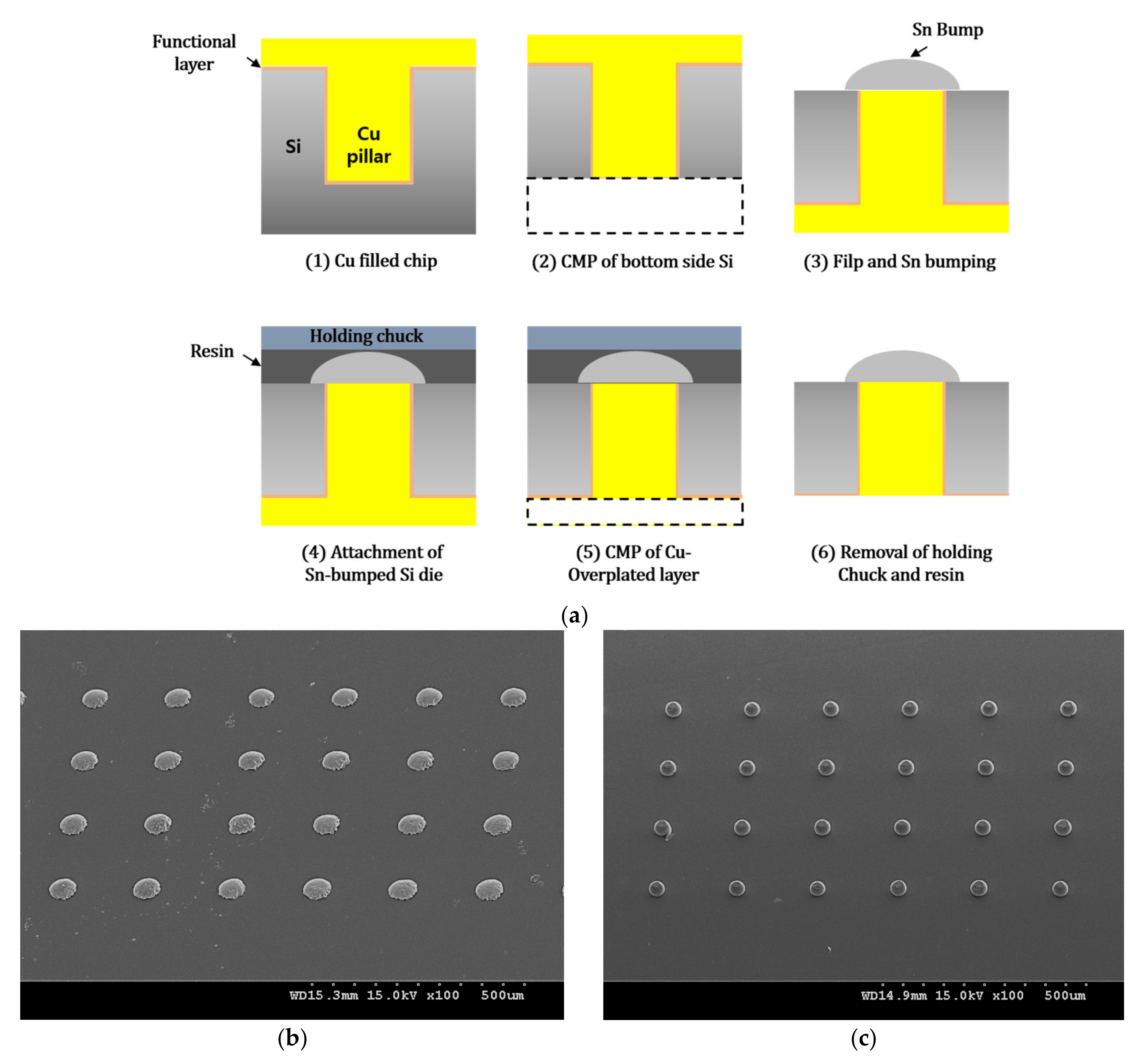

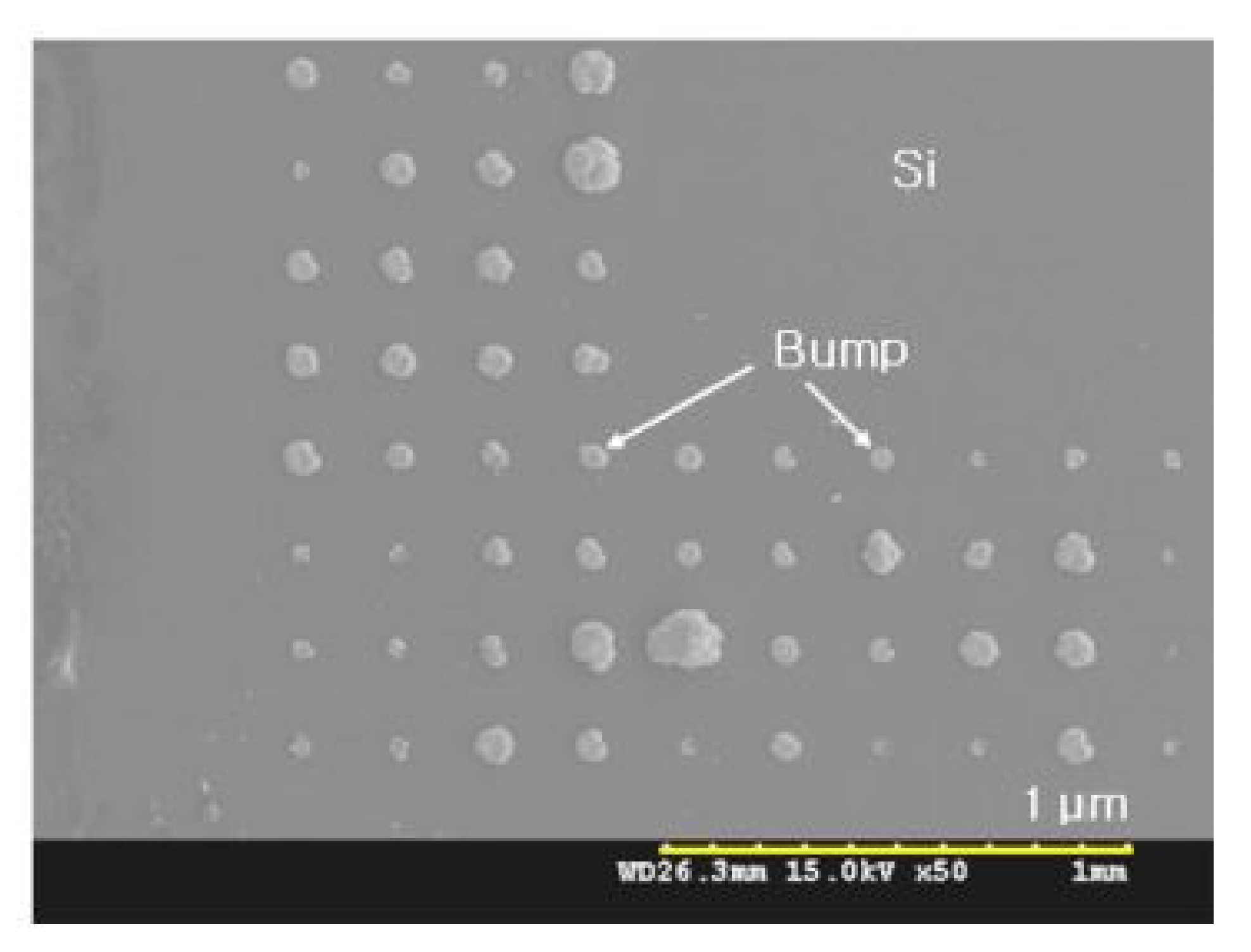

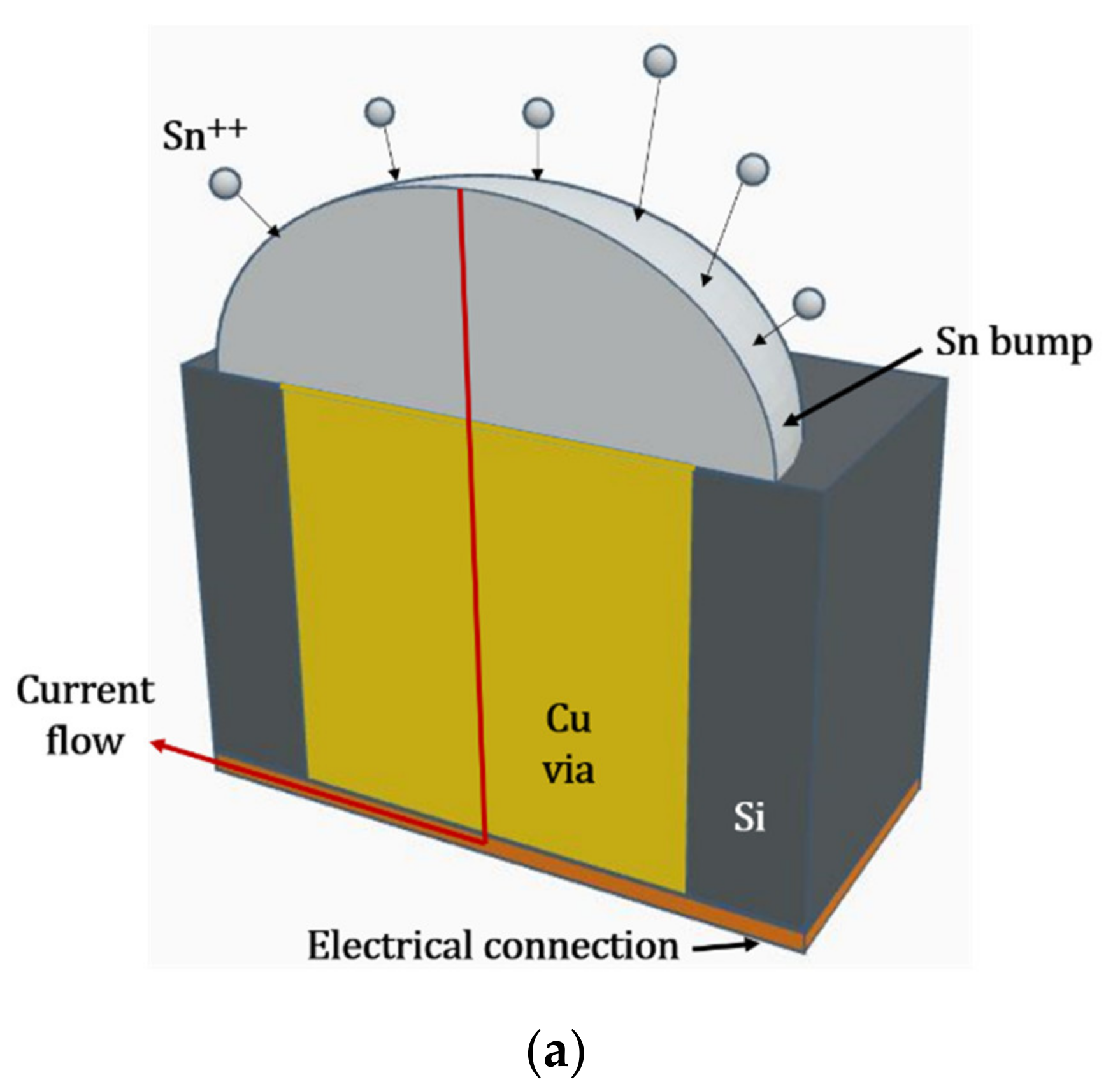

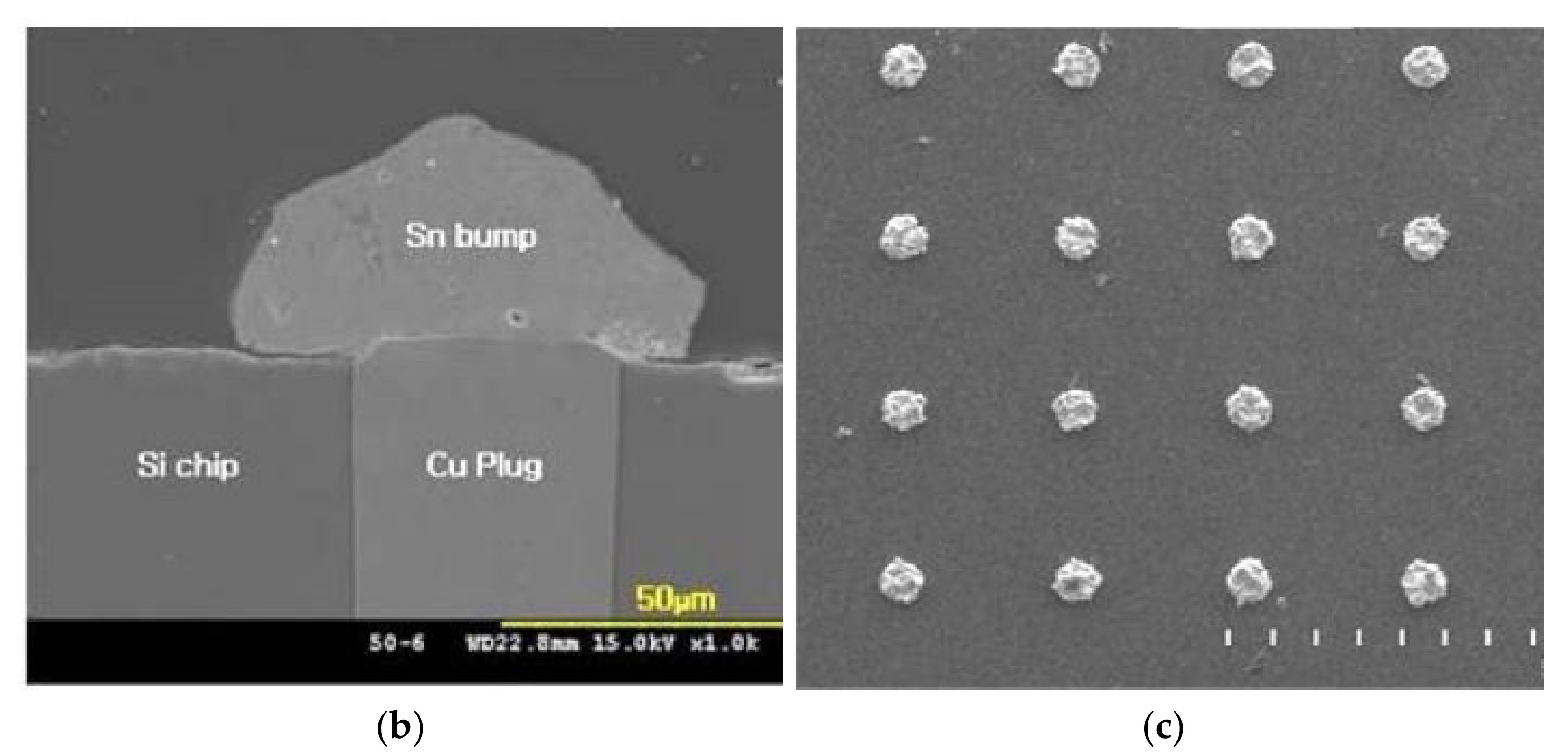

3.1.1. Solder Bump Plating on TSV

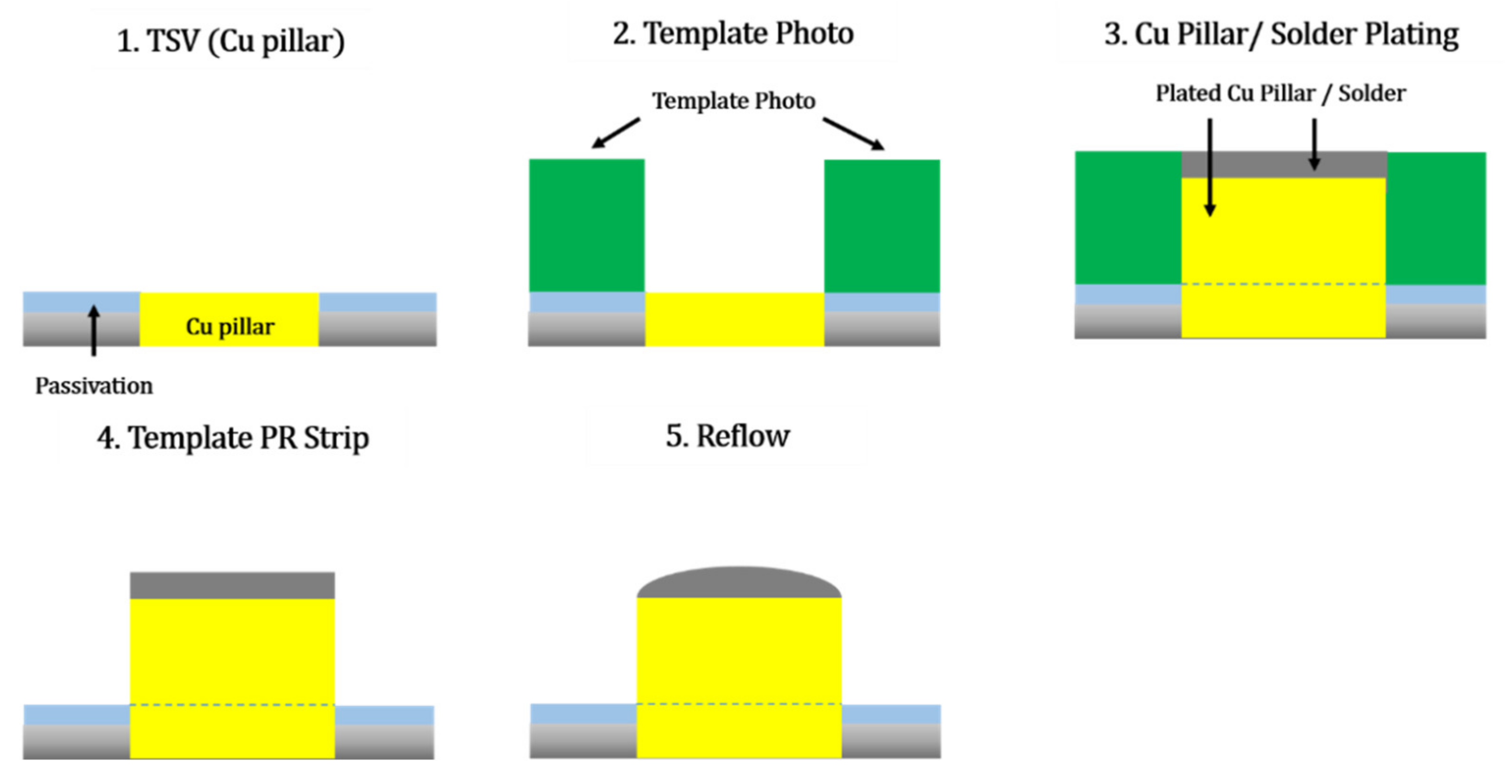

3.1.2. Cu Pillar Bump with Solder Cap

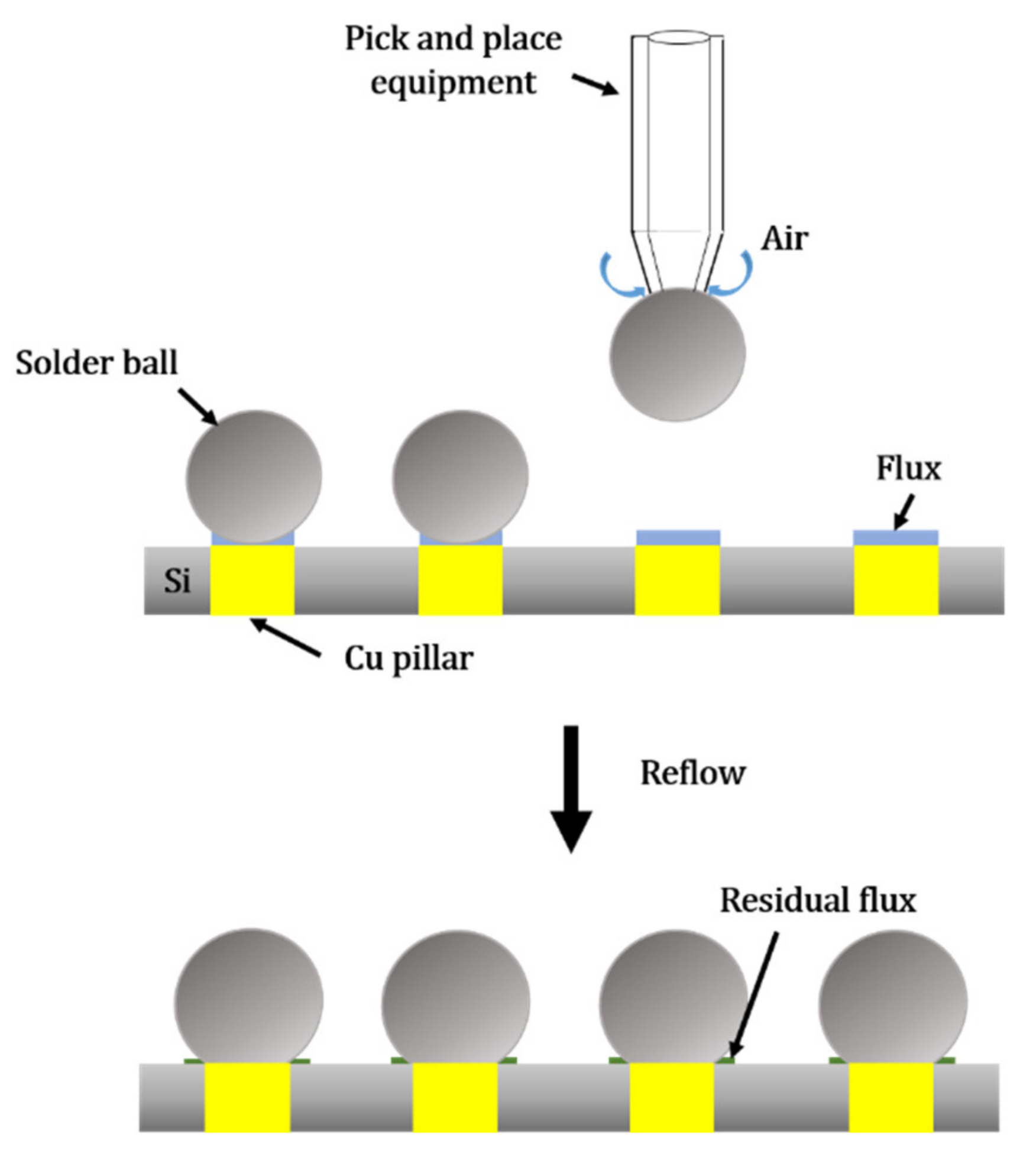

3.2. Solder Ball Bumping

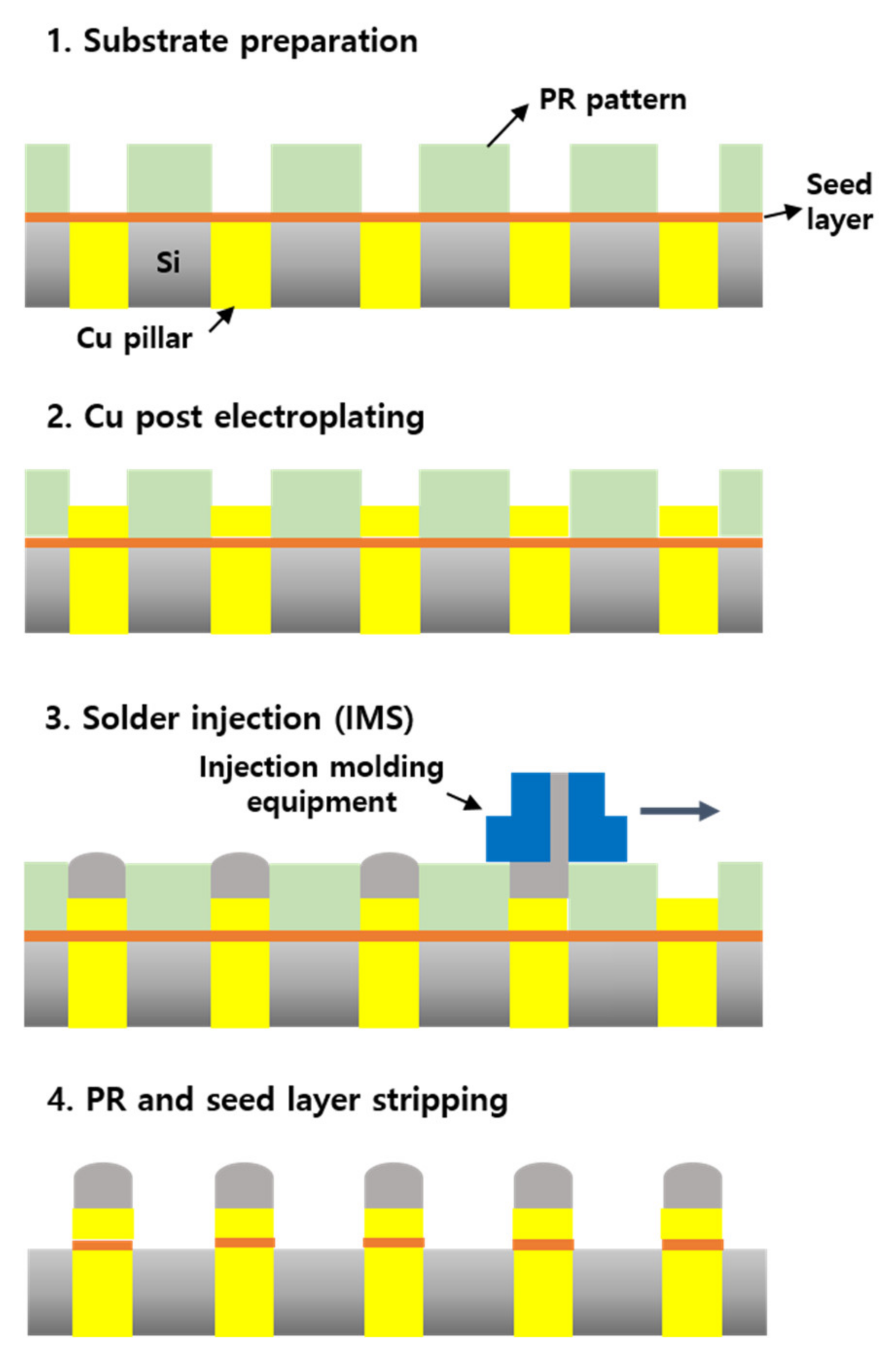

3.3. Solder Injection on Cu-Pillar

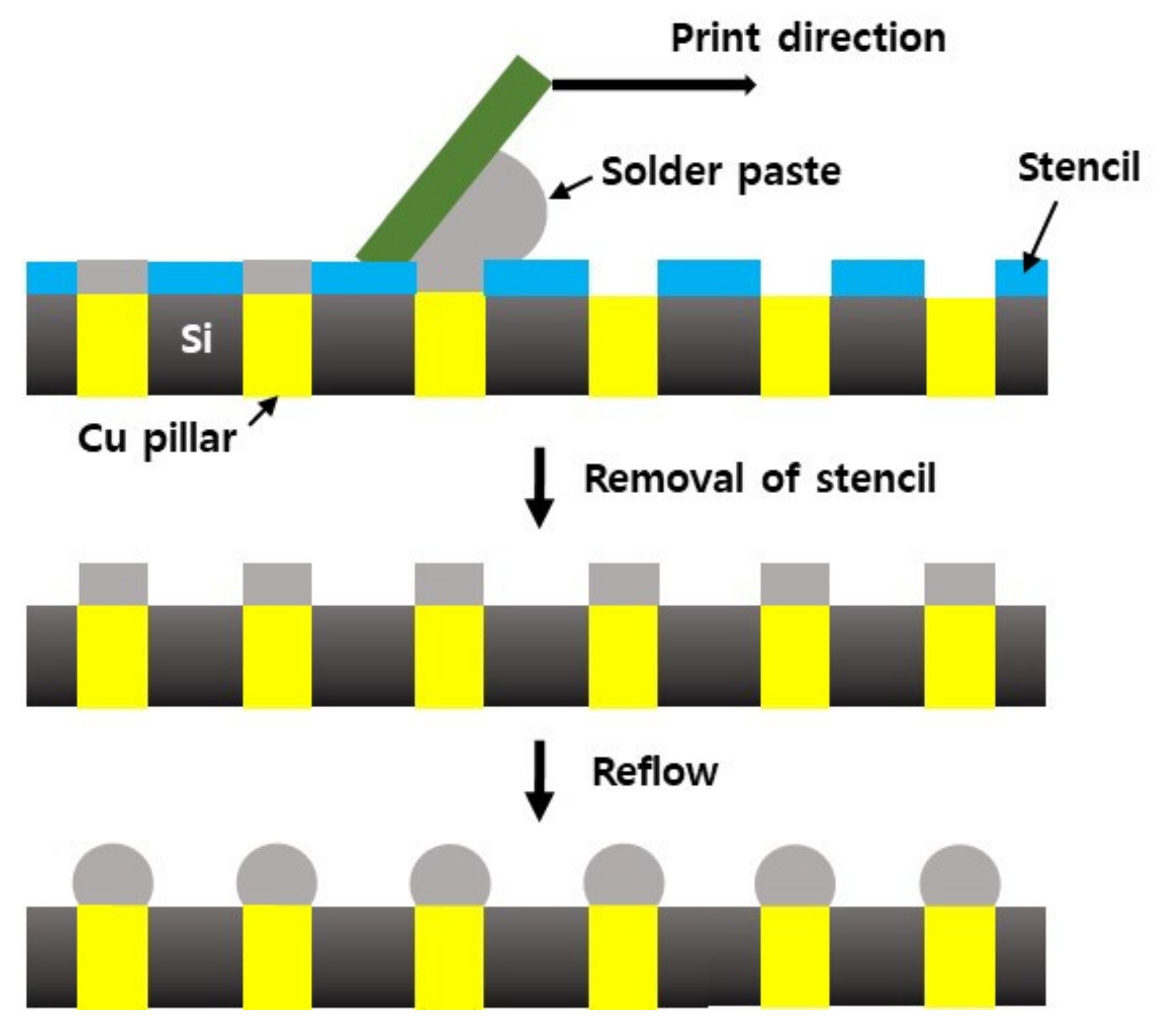

3.4. Solder Paste Printing

3.5. Reliability of Solder Bump and Future Directions

4. Bumpless Joining of Stacked TSV

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Kikuchi, K. 3D—IC Technology for Contribution to the IoT Society. J. Japan Inst. Electron. Packag. 2019, 22, 501–506. [Google Scholar] [CrossRef]

- Jiang, T.; Im, J.; Huang, R.; Ho, P.S. Through-silicon via stress characteristics and reliability impact on 3D integrated circuits. MRS Bull. 2015, 40, 248–256. [Google Scholar] [CrossRef]

- Shi, H.; Poonjolai, E. Fundamentals and Failures in Die Preparation for 3D Packaging. In 3D Microelectronic Packaging, 1st ed.; Li, Y., Deepak, G., Eds.; Springer International Publishing: New York, NY, USA, 2017; Volume 57, pp. 101–128. [Google Scholar] [CrossRef]

- Shen, Y.; Meng, X.; Chen, Q.; Rumley, S.; Abrams, N.; Gazman, A.; Manzhosov, E.; Glick, M.S.; Bergman, K. Silicon Photonics for Extreme Scale Systems. J. Light. Technol. 2019, 37, 245–259. [Google Scholar] [CrossRef]

- Khorramdel, B.; Liljeholm, J.; Laurila, M.M.; Lammi, T. Inkjet printing technology for increasing the I/O density of 3D TSV interposers. Microsyst. Nanoeng. 2017, 3, 17002. [Google Scholar] [CrossRef]

- Annuar, S.; Mahmoodian, R.; Hamid, M.; Tu, K.N. Intermetallic compounds in 3D integrated circuits technology: A brief review. Sci. Technol. Adv. Mater. 2017, 18, 693–703. [Google Scholar] [CrossRef] [PubMed]

- Li, L.; Ton, P.; Nagar, M.; Chia, P. Reliability challenges in 2.5D and 3D IC integration. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 1504–1509. [Google Scholar] [CrossRef]

- Watanabe, Y.; Kato, M.; Yahagi, T.; Murayama, H.; Yoshida, K.; Sashida, K.; Ikeda, K.; Ikeda, K.; Takemori, T. MEMS Rogowski Coil Current Sensor with TSV Structural Wiring. J. Jpn. Inst. Electron. Packag. 2021, 24, 101–106. [Google Scholar] [CrossRef]

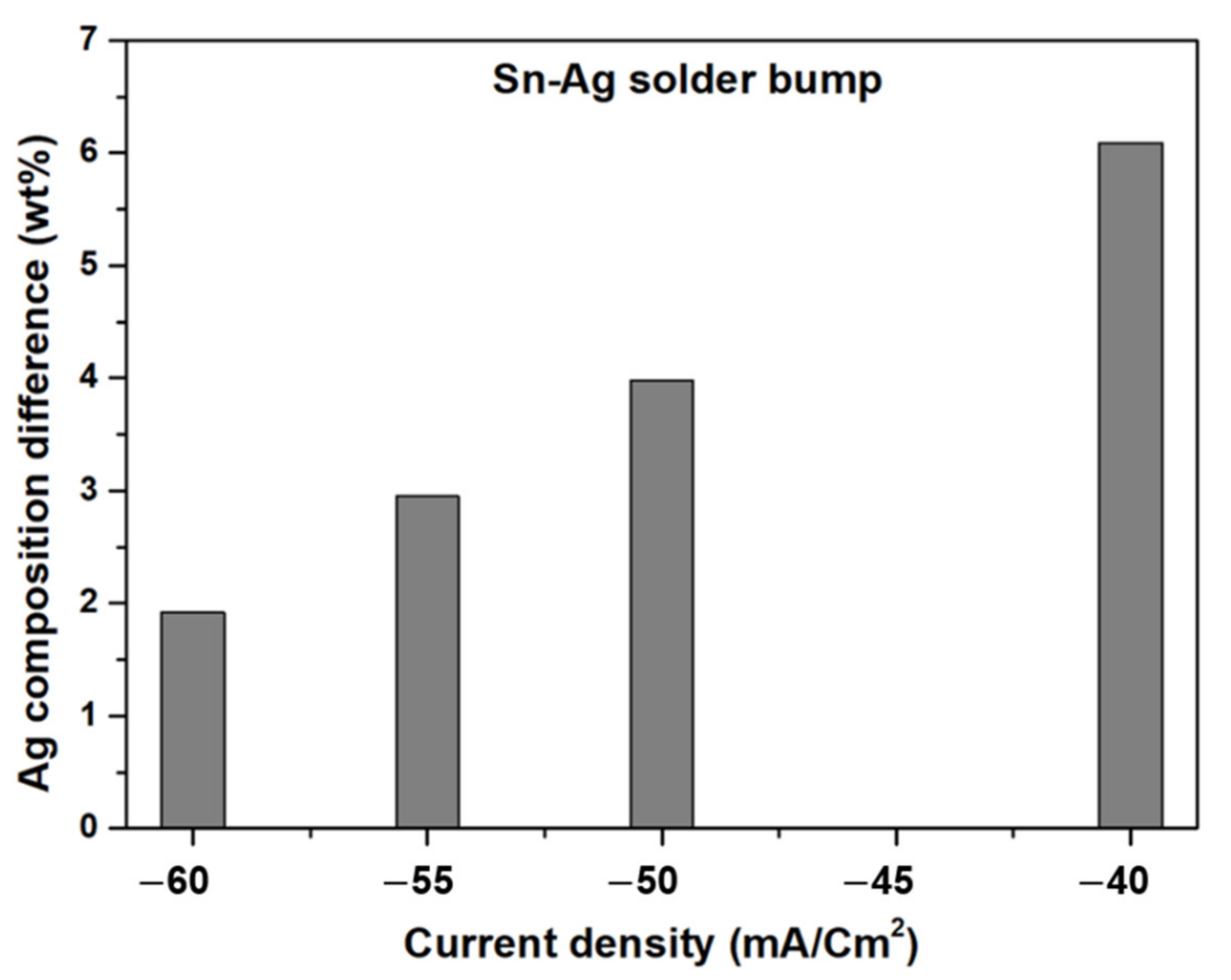

- Hong, S.C.; Jung, D.H.; Lee, W.G.; Kim, W.J.; Jung, J.P. Non-PR Sn-3.5Ag Bumping on a Fast Filled Cu-Plug by PPR Current. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 574–580. [Google Scholar] [CrossRef]

- Zare, Y.; Sasajima, Y.; Onuki, J. Evaluation of Cu-TSV Barrier Materials as a Solution to Copper Protrusion. J. Electron. Mater. 2019, 49, 2076–2085. [Google Scholar] [CrossRef]

- Zhang, Z.; Ding, Y.; Xiao, L.; Cai, Z.; Yang, B.; Wu, Z.; Su, Y.; Chen, Z. Development of cu seed layers in ultra-high aspect ratio through-silicon-vias (TSVs) with small diameters. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 1904–1909. [Google Scholar] [CrossRef]

- Murugesan, M.; Koyanagi, M.; Fukushima, T. Impact of electroless-Ni seed layer on cu-bottom-up electroplating in high aspect ratio (>10) TSVs for 3D-IC packaging applications. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 1736–1741. [Google Scholar] [CrossRef]

- Sung, M.; Lee, A.; Kim, T.; Yoon, Y.; Lim, T.; Kim, J.J. Sulfur-Containing Additives for Mitigating Cu Protrusion in Through Silicon Via (TSV). J. Electrochem. Soc. 2019, 166, D514–D520. [Google Scholar] [CrossRef]

- Sharma, A.; Jung, D.H.; Roh, M.H.; Jung, J.P. Fabrication and Shear Strength Analysis of Sn-3.5Ag/Cu-Filled TSV for 3D Microelectronic Packaging. Electron. Mater. Lett. 2016, 12, 856–863. [Google Scholar] [CrossRef]

- Jung, D.H.; Agarwal, S.; Kumar, S.; Jung, J.P. High Shear Speed Characteristics of Sub-100 mm Low Alpha SAC105 Solder Bump Directly Fabricated on Cu Filled Through Si Via for 3D Integration. J. Microelectron. Electron. Packag. 2015, 12, 161–169. [Google Scholar] [CrossRef]

- Sakui, K.; Ohba, T. Three-dimensional integration (3DI) with bumpless interconnects for tera-scale generation: High speed, low power, and ultra-small operating platform. In Proceedings of the 2019 IEEE Custom Integration Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2010. [Google Scholar] [CrossRef]

- Laermer, F.; Schilip, A. Method of Anisotropically Etching Silicon. U.S. Patent 5,501,893, 1996. [Google Scholar]

- Laermer, F.; Schilip, A. Method of Anisotropic Etching of Silicon. U.S. Patent 6,531,068 B2, 2003. [Google Scholar]

- MacDonald, R.J.; Goswami, S.; Ruffalo, R.; Edmond, M.; Szymanski, C. Influence of resist profile on DRIE sidewall morphology. In Proceedings of the 2021 32nd Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Milpitas, CA, USA, 10–12 May 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Rudy, A.S.; Morozov, O.V.; Kurbatov, S.V. A Modernized Bosch Etching Process for the Formation of Tapered Structures on a Silicon Surface. J. Synch. Investig. 2021, 15, 461–466. [Google Scholar] [CrossRef]

- Yoon, T.; Kim, T.S. Thermo-Mechanical Reliability of TSV based 3D-IC. J. Microelectron. Packag. Soc. 2017, 24, 35–43. [Google Scholar] [CrossRef]

- Beak, K.H.; Kim, D.P.; Park, K.S.; Kang, J.Y.; Lee, K.; Do, L.M. DRIE Technology for TSV Fabrication. J. Korean Soc. Precis. Eng. 2009, 26, 32–40. [Google Scholar]

- Park, J.S.; Kang, D.H.; Kwak, S.M. Low-temperature smoothing method of scalloped DRIE trench by post-dry etching process based on SF6 plasma. Micro Nano Syst. Lett. 2020, 14, 1–8. [Google Scholar] [CrossRef]

- Frasca, S.; Leghziel, R.C.; Arabadzhiev, I.N.; Pasquier, B.; Tomassi, G.F.; Carrara, S.; Charbon, E. The Michelangelo step: Removing scalloping and tapering effects in high aspect ratio through silicon vias. Sci. Rep. 2021, 11, 1–6. [Google Scholar] [CrossRef] [PubMed]

- Shi, Z.; Jefimovs, K.; Romano, L.; Stampanoni, M. Towards the Fabrication of High-Aspect-Ratio Silicon Gratings by Deep Reactive Ion Etching. Micromachines 2020, 11, 864. [Google Scholar] [CrossRef]

- Baklykov, D.A.; Andronic, M.; Sorokina, O.S.; Avdeev, S.S.; Buzaverov, K.A.; Ryzhikov, I.A.; Rodionov, I.A. Self-Controlled Cleaving Method for Silicon DRIE Process Cross-Section Characterization. Micromachines 2021, 12, 534. [Google Scholar] [CrossRef] [PubMed]

- Wang, X.; Wang, Q.; Zhou, J. Inverse RIE micro-loading in deep etching of silicon via array. In Proceedings of the 2019 IEEE 13th International Conference on ASIC (ASICON), Chongquig, China, 29 October–1 November 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Gerlt, M.S.; Läubli, N.F.; Manser, M.; Nelson, B.J.; Dual, J. Reduced etch lag and high aspect ratios by deep reactive ion etching (DRIE). Micromachines 2021, 12, 542. [Google Scholar] [CrossRef]

- Chen, Y.; Zhang, P.; Xia, K.; Huang, H. Boundary Layers Defect Diagnosis and Analysis of Through Silicon Via (TSV). Int. J. Perform. Eng. 2019, 15, 97. [Google Scholar] [CrossRef]

- Ren, Y.; Geng, F.; Sung, P.; Sun, Y.; Sima, G. Etching process development for 3D wafer level via last TSV package. In Proceedings of the 2017 18th International Conference on Electronic Packaging Technology (ICEPT), Harbin, China, 16–19 August 2017; pp. 296–300. [Google Scholar] [CrossRef]

- Jung, M.W.; Kim, K.T.; Koo, Y.S.; Lee, J.H. The Effects of Levelers on Electrodeposition of Copper in TSV filling. J. Microelectron. Packag. Soc. 2012, 19, 55–59. [Google Scholar] [CrossRef]

- Roh, M.H.; Sharma, A.; Lee, J.H.; Jung, J.P. Extrusion Suppression of TSV Filling Metal by Cu-W Electroplating for Three-Dimensional Microelectronic Packaging. Metall. Mater. Trans. A 2015, 46A, 2051–2062. [Google Scholar] [CrossRef]

- Lin, N.; Miao, J.; Dixit, P. Void formation over limiting current density and impurity analysis of TSV fabricated by constant-current pulse-reverse modulation. Microelectron. Reliab. 2013, 53, 1943–1953. [Google Scholar] [CrossRef]

- Ahmed, W.; Ahmed, E.; Dost, A. Chemical Vapor Deposition (CVD) of Borophosphosilicate Glass Films. J. Mater. Sci. Mater. Electron. 1996, 7, 127–131. [Google Scholar] [CrossRef]

- Murugesan, M.; Mori, K.; Kojima, T.; Hashimoto, H.; Bea, J.C.; Fukushima, T.; Koyanagi, M. Nano Ni/Cu-TSVs with an improved reliability for 3D-IC integration application. In Proceedings of the 2020 31st Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 24–26 August 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Hong, S.J.; Hong, S.C.; Kim, W.J.; Jung, J.P. Copper Filling to TSV(Through-Si-Via) and Simplification of Bumping Process. J. Microelectron. Packag. Soc. 2010, 17, 79–84. [Google Scholar] [CrossRef]

- Kim, B.H.; Kim, H.C.; Chun, J.K.; Ki, J.H.; Tak, Y.S. Cantilevert-type microelectromechanical systems probe card with through-wafer interconnects for fine pitch and high-speed testing. Japan. J. Appl. Phys. 2004, 43, 3877. [Google Scholar] [CrossRef]

- Kee, S.H.; Kim, W.J.; Jung, J.P. Copper-silicon carbide composite plating for inhibiting the extrusion of through silicon via (TSV). Microelectron. Eng. 2019, 214, 5–14. [Google Scholar] [CrossRef]

- Knaut, M.; Junige, M.; Neumann, V.; Wojcik, H.; Henke, T.; Hossbach, C.; Hiess, A.; Albert, M.; Bartha, J.W. Atomic layer deposition for high aspect ratio through silicon vias. Microelectron. Eng. 2013, 107, 80–83. [Google Scholar] [CrossRef]

- Matsudaira, T.; Shindo, S.; Shimizu, T.; Ito, T.; Shinguhara, S.; Shimizu, S. Cu diffusion barrier properties of various CoWB electroless plated films on SiO 2/Si substrate for via-last TSV application. In Proceedings of the 2019 International 3D Systems Integration Conference (3DIC), Sendai, Japan, 8–10 October 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Murugesan, M.; Fukushima, T.; Mori, K.; Nakamura, A.; Lee, Y.; Motoyoshi, M.; Koyanagi, M. Fully-Filled, highly-reliable fine-pitch interposers with TSV aspect ratio >10 for future 3D-LSI/IC packaging. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vagas, NV, USA, 28–31 May 2019; pp. 1047–1051. [Google Scholar] [CrossRef]

- Murugesan, M.; Fukushima, T.; Koyanagi, M. 500 nm-sized Ni-TSV with Aspect Ratio 20 for Future 3D-LSIs_A Low-Cost Electroless-Ni Plating Approach. In Proceedings of the 2019 30th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 6–9 May 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Hong, S.C.; Jung, D.H.; Jung, J.P.; Kim, W.J. Effective Cu filling method to TSV for 3-dimensiional Si chip stacking. Korean J. Met. Mater. 2012, 50, 152–158. [Google Scholar] [CrossRef]

- Hong, S.C.; Kim, W.J.; Jung, J.P. High-speed Cu filling into TSV and non-PR bumping for 3D chip packaging. J. Microelectron. Packag. Soc. 2011, 18, 49–53. [Google Scholar] [CrossRef]

- Lee, K.Y.; Oh, T.S. Cu Via-Filling Characteristics with Rotating-Speed Variation of the Rotating Disc Electrode for Chip-stack-package Applications. J. Microelectron. Packag. Soc. 2007, 14, 65–71. [Google Scholar]

- Lee, S.J.; Jang, Y.J.; Lee, J.H.; Jung, J.P. Cu-Filling Behavior in TSV with Positions in Wafer Level. J. Microelectron. Packag. Soc. 2014, 21, 91–96. [Google Scholar] [CrossRef]

- Hofmann, L.; Ecke, R.; Schulz, S.E.; Gessner, T. Investigations regarding through silicon via filling for 3D integration by periodic pulse reverse plating with and without additives. Microelectron. Eng. 2011, 88, 705–708. [Google Scholar] [CrossRef]

- Kim, I.R.; Hong, S.C.; Jung, J.P. High speed Cu filling into tapered TSV for 3-dimensional Si chip stacking. Korean J. Met. Mater. 2011, 49, 388–394. [Google Scholar] [CrossRef]

- Gabrielli, C.; Mocoteguy, P.; Perrot, H.; Nieto, S.D.; Zdunek, A. A Model for Copper Deposition in the Damascene Process. Electrochim. Acta 2006, 51, 1462–1472. [Google Scholar] [CrossRef]

- Jin, S.; Wang, G.; Yoo, B. Through-Silicon-Via (TSV) Filling by Electrodeposition of Cu with Pulse Current at Ultra-Short Duty Cycle. J. Electrochem. Soc. 2013, 160, D3300–D3305. [Google Scholar] [CrossRef]

- Hong, S.C.; Kumar, S.; Jung, D.H.; Kim, W.J.; Jung, J.P. High speed Cu-Ni filling in to TSV for 3-Dimensional Si chip stacking. Met. Mater. Int. 2013, 19, 123–128. [Google Scholar] [CrossRef]

- Kim, H.C.; Kim, M.J.; Kim, J.J. Communication—Acceleration of TSV Filling by Adding Thiourea to PEG-PPG-SPS-I−. J. Electrochem. Soc. 2018, 165, D91–D93. [Google Scholar] [CrossRef]

- Sung, M.; Yoon, Y.; Hong, J.; Kim, M.J.; Kim, J.J. Bromide Ion as a Leveler for High-Speed TSV Filling. J. Electrochem. Soc. 2019, 166, D546–D550. [Google Scholar] [CrossRef]

- Dinh, V.Q.; Kondo, K.; Hoang, V.H.; Hirato, T. Communication—Bottom-Up TSV Filling Using Sulfonated Diallyl Dimethyl Ammonium Bromide Copolymer as a Leveler. J. Electrochem. Soc. 2019, 166, D505–D507. [Google Scholar] [CrossRef]

- Ha, H.V.; Kondo, K. Extreme fast filling of conical shape through-silicon vias in 3 minutes and additive optimization. Electrochim. Acta 2016, 212, 270–276. [Google Scholar] [CrossRef]

- Shin, S.H.; Kim, T.Y.; Park, J.H.; Suh, S.J. Optimization of Additive and Current Conditions for Void-Free Filled Through-Silicon Via. Appl. Sci. 2018, 8, 2135. [Google Scholar] [CrossRef]

- Wu, H.; Wang, Y.; Li, Z.; Zhu, W. Investigations of the electrochemical performance and filling effects of additives on electroplating process of TSV. Sci. Rep. 2020, 10, 9204. [Google Scholar] [CrossRef]

- Tomie, M.; Akita, T.; Irita, M.; Hayase, M. Transitional Additive Adsorption with Co-Addition of Suppressor and Leveler for Copper TSV Filling. J. Electrochem. Soc. 2020, 167, 082513. [Google Scholar] [CrossRef]

- Wang, F.; Le, Y. Experiment and simulation of single inhibitor SH110 for void-free TSV copper filling. Sci. Rep. 2020, 11, 12108. [Google Scholar] [CrossRef] [PubMed]

- Le, Y.; Wang, F. Void free TSV copper filling using single additive 3-(1-pyridinio)-1-propanesulfonate (PPS). In Proceedings of the 2020 3rd International Conference on Advanced Electronic Materials, Computers and Software Engineering (AEMCSE), Shenzhen, China, 24–26 April 2020; pp. 636–640. [Google Scholar] [CrossRef]

- Xiao, H.; Wang, F.; Wang, Y.; He, H.; Zhu, W. Effect of Ultrasound on Copper Filling of High Aspect Ratio Through-Silicon Via (TSV). J. Electrochem. Soc. 2017, 164, 126–129. [Google Scholar] [CrossRef]

- Wang, F.; Zeng, P.; Wang, Y.; Ren, X.; Xiao, H.; Zhu, W. High-speed and high-quality TSV filling with the direct ultrasonic agitation for copper electrodeposition. Microelectron. Eng. 2017, 180, 30–34. [Google Scholar] [CrossRef]

- Zeng, P.; Ren, X. The influence of pulse and ultrasonic agitation on TSV filing. In Proceedings of the 2017 18th International Conference on Electronic Packaging Technology (ICEPT), Harbin, China, 16–19 August 2017; pp. 432–435. [Google Scholar] [CrossRef]

- Jeong, I.H.; Kee, S.H.; Jung, J.P. A study on Electrical Characteristic and Thermal Shock Property of TSV for 3-Dimensional Packaging. J. Microelectron. Electron. Packag. 2014, 21, 23–29. [Google Scholar] [CrossRef]

- Majd, A.E.; Jeong, I.H.; Jung, J.P.; Ekere, N.N. Cu Protrusion of Different through-Silicon via Shapes under Annealing Process. J. Mater. Eng. Perform. 2021, 30, 4712–4720. [Google Scholar] [CrossRef]

- Jeong, I.H.; Majd, A.E.; Jung, J.P.; Ekere, N.M. Electrical and Mechanical Analysis of Different TSV Geometries. Metals 2020, 10, 467. [Google Scholar] [CrossRef]

- Pak, J.S.; Ryu, C.; Kim, J. Electrical characterization of trough silicon via (TSV) depending on structural and material parameters based on 3D full wave simulation. In Proceedings of the 2007 International Conference on Electronic Materials and Packaging, Daejeon, Korea, 19–22 November 2007; pp. 1–6. [Google Scholar] [CrossRef]

- Belaid, K.A.; Belahrach, H.; Ayad, H. Numerical laplace inversion method for through-silicon via (TSV) noise coupling in 3D-IC design. Electronics 2019, 8, 1010. [Google Scholar] [CrossRef]

- Ko, Y.K.; Fujii, H.T.; Sato, Y.S.; Lee, C.W.; Yoo, S. High-speed TSV filling with molten solder. Microelectron. Eng. 2012, 89, 62–64. [Google Scholar] [CrossRef]

- Jung, H.S.; Jang, Y.J.; Choa, S.H.; Jung, J.P. Lower Protrusion of a Copper-Nickel Alloy in a Through-Silicon via and Its Numerical Simulation. Mater. Trans. 2015, 56, 2034–2041. [Google Scholar] [CrossRef]

- Sable, K.; Sahoo, M. Electrical and thermal analysis of cu-CNT composite TSV and GNR interconnects. In Proceedings of the 2020 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 4–6 March 2020; pp. 1–6. [Google Scholar] [CrossRef]

- Chen, G.; Sundaram, R.; Sekiguchi, A.; Hata, K.; Futaba, D.N. Through-Silicon-Via Interposers with Cu-Level Electrical Conductivity and Si-Level Thermal Expansion Based on Carbon Nanotube-Cu Composites for Microelectronic Packaging Applications. ACS Appl. Nano Mater. 2021, 4, 869–876. [Google Scholar] [CrossRef]

- Lwo, B.J.; Lin, M.S.; Huang, K.H. TSV reliability model under various stress tests. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 620–624. [Google Scholar] [CrossRef]

- Merrit, S.A.; Heim, P.J.S.; Cho, S.H.; Dagenais, M. Controlled solder interdiffusion for high power semiconductor laser diode die bonding. IEEE Trans. Compon. Packag. Manufac. Technol. Part. B 1997, 20, 141–145. [Google Scholar] [CrossRef]

- Busby, J.; Hawken, D.; Perfecto, E.; Dang, B.; Shah, J.; Ruhmer, K.; Cruber, P.; Weisman, R.; Buchwalter, S. C4NP lead free solder bumping and 3D micro bumping. In Proceedings of the 2008 IEEE/SEMI Advanced Semiconductor Manufacturing Conference, Cambridge, MA, USA, 5–7 May 2008; pp. 333–339. [Google Scholar] [CrossRef]

- Dixit, P.; Tan, C.W.; Xu, L.; Lin, N.; Miao, J.; Pang, J.; Backus, P.; Preisser, R. Fabrication and characterization of fine pitch on-chip copper interconnects for advanced wafer level packaging by a high aspect ratio through AZ9260 resist electro-plating. J. Micromech. Microeng. 2007, 17, 1078. [Google Scholar] [CrossRef]

- Tanida, K.; Umemoto, M.; Tanaka, N.; Tomita, Y.; Takahashi, K. Micro Cu Bump Interconnection on 3D Chip Stacking Technology. Jpn. J. Appl. Phys. 2004, 43, 2264–2270. [Google Scholar] [CrossRef]

- Hong, S.J.; Jun, J.H.; Jung, J.P.; Mayer, M.; Zhou, Y. Sn Bumping Without Photoresist Mould and Si Dice Stacking for 3-D Packaging. IEEE Trans. Adv. Packag. 2010, 33, 912–917. [Google Scholar] [CrossRef]

- Jun, J.; Kim, I.; Mayer, M.; Zhou, Y.N.; Jung, S.; Jung, J.P. A New Non-PRM Bumping Process by Electroplating on Si Die for Three Dimensional Packaging. Mater. Trans. 2010, 51, 1887–1892. [Google Scholar] [CrossRef]

- Pham, N.P.; Tezcan, D.S.; Majeed, B.; Moor, P.D.; Baert, K.; Swinnen, B.; Ruythooren, W. Lithography for patterning inside through-Si vias. In Proceedings of the 2007 9th Electronics Packaging Technology Conference, Singapore, 10–12 December 2007; pp. 120–124. [Google Scholar] [CrossRef]

- Fukuda, M.; Imayoshi, K.; Matsumoto, Y. Effects of thiourea and polyoxyethylene lauryl ether on electrodeposition of Sn-Ag-Cu alloy as a Pb-free solder. J. Electrochem. Soc. 2002, 149, C244–C249. [Google Scholar] [CrossRef]

- Jun, J.H.; Park, J.K.; Jung, J.P. Fabrication of Electroplate Sn-Ag Bumps Without a Lithography Process for 3D Packaging. Met. Mater. Int. 2012, 18, 487–491. [Google Scholar] [CrossRef]

- Hong, S.C. High-Speed Filling into TSV by Electroplating and 3-Dimensional Chip Stacking Using Sn-3.5Ag Bumps Formed Without Photoresist. Ph.D. Thesis, University of Seoul, Seoul, Korea, 2012. [Google Scholar]

- Park, J.K.; Lee, K.J.; Jung, J.P. Electroplating characteristics of eutectic Sn-Cu ions for micro-solder bump on a Si chip. J. Nanosci. Nanotechnol. 2012, 12, 3582–3588. [Google Scholar] [CrossRef] [PubMed]

- Ding, M.Z.; Chen, Z.; Lim, S.P.S.; Rao, V.S.; Lin, J. Mitigation of warpage for large 2.5D through silicon interposer (TSI) package assembly. In Proceedings of the 2015 IEEE 17th Electronics Packaging and Technology Conference (EPTC), Singapore, 2–4 December 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Jun, J.H.; Lee, W.G.; Jung, J.P.; Zhou, Y.N. Characteristics of electroplated Sn bumps fabricated without a PR mould on a Si chip for 3D packaging. Microelectron. Eng. 2021, 93, 85–90. [Google Scholar] [CrossRef]

- Lee, C.W.; Ko, Y.K.; Ko, Y.H.; Bang, J.H. Advanced TSV Filling Technology for 3-Dimensional Electronic Packaging. Mater. Sci. Forum. 2014, 783–786, 2758–2764. [Google Scholar] [CrossRef]

- Koh, W.; Lin, B.; Tai, J. Copper pillar bump technology progress overview. In Proceedings of the 2011 12th International Conference on Electronic Packaging Technology and High Density Packaging, Shanghai, China, 8–11 August 2011; pp. 1–5. [Google Scholar] [CrossRef]

- Gerber, M.; Craig, B.C.; Shawn, O.S.; Yoo, M.; Lee, M.J.; Kang, D.B.; Park, S.S.; Zwenger, C.; Darveaux, R.; Lanzone, R.; et al. Next generation fine pitch cu pillar technology—Enabling next generation silicon nodes. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 612–618. [Google Scholar] [CrossRef]

- Ma, M.; Ren, S.; Wang, J.; Hu, A.; Li, M. Influence of bump diameter on the growth of intermetallic compounds in Cu/Ni/Sn copper pillar bump during aging process. In Proceedings of the 2020 21st International Conference on Electronic Packaging Technology (ICEPT), Guangzhou, China, 12–15 August 2020; pp. 1–4. [Google Scholar] [CrossRef]

- Jung, D.H.; Sharma, A.; Kim, K.H.; Choo, Y.C.; Jung, J.P. Effect of Current Density and Plating Time on Cu Electroplating in TSV and Low Alpha Solder Bumping. J. Mater. Eng. Perf. 2015, 24, 1107. [Google Scholar] [CrossRef]

- Nah, J.; Gelorme, J.; Sorce, P.; Lauro, P.; Perfecto, E.; Mcleod, M.; Yoriyama, K.; Orii, Y.; Brofman, P.; Nauchi, T.; et al. Wafer IMS (injection molded solder)—A new fine pitch solder bumping technology on wafers with solder alloy composition flexibility. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 1308–1313. [Google Scholar] [CrossRef]

- AoKi, T.; Toriyama, K.; Mori, H.; Orii, Y.; Nah, J.; Takahashi, S.; Mukawa, J.; Hasegawa, K.; Kusumoto, S.; Inomata, K. IMS (injection molded solder) technology with liquid photoresist for ultra fine pitch bumping. In Proceedings of the International Symposium on Microelectronics, San Diego, CA, USA, 13–18 October 2014; pp. 713–717. [Google Scholar] [CrossRef]

- Hyang, C.Y.; Lin, Y.H.; Ying, K.C.; Ku, C.L. The solder paste printing process: Critical parameters, defect scenarios, specifications, and cost reduction. Solder. Surf. Mt. Technol. 2011, 23, 211–223. [Google Scholar] [CrossRef]

- Kim, M.S.; Hong, W.S.; Kim, M.G. Flip Chip—Chip Scale Package Bonding Technology with Type 7 Solder Paste Printing. J. Weld. Join. 2021, 39, 1–9. [Google Scholar] [CrossRef]

- Kumar, S.; Mallik, S.; Ekere, N.; Jung, J.P. Stencil Printing Behavior of Lead-Free Sn-3Ag-0.5Cu Solder Paste for Wafer Level Bumping for Sub-100 µm Size Solder Bumps. Met. Mater. Int. 2013, 19, 1083–1090. [Google Scholar] [CrossRef]

- Depiver, A.; Mallik, S.; Amalu, E.H. Thermal fatigue life of ball grid array (BGA) solder joints made from different alloy compositions. Eng. Fail. Anal. 2021, 125, 105447. [Google Scholar] [CrossRef]

- Tikale, S.; Prabhu, N.K. Bond shear strength of Al2O3 nanoparticles reinforced 2220-capacitor/SAC305 solder interconnects reflowed on bare and Ni-coated copper substrate. J. Mater. Sci. Mater. Electron. 2021, 32, 2865–2886. [Google Scholar] [CrossRef]

- Su, M.; Black, B.; Hsiao, Y.; Changchien, C.; Lee, C.; Chang, H. 2.5D IC micro-bump materials characterization and IMCs evolution under reliability stress conditions. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 322–328. [Google Scholar] [CrossRef]

- Rajendran, S.H.; Hwang, S.J.; Jung, J.P. Shear Strength and Aging Characteristics of Sn-3.0Ag-0.5Cu/Cu Solder Joint Reinforced with ZrO2 Nanoparticles. Metals 2020, 10, 1295. [Google Scholar] [CrossRef]

- Shin, Y.S.; Ko, Y.K.; Kim, J.K.; Yoo, S.H.; Lee, C.W. SiC-nanoparticle dispersed composite solder bumps fabricated by electroplating. Surf. Rev. Lett. 2010, 17, 201–205. [Google Scholar] [CrossRef]

- Tsao, L.C.; Chang, S.Y.; Lee, C.I.; Sun, W.H.; Huang, C.H. Effects of Nano-Al2O3 additions on microstructure development and hardness of Sn3.5Ag0.5Cu solder. Mater. Des. 2010, 31, 4831–4835. [Google Scholar] [CrossRef]

- Rajendran, S.H.; Kang, H.; Jung, J.P. Ultrasonic-Assisted Dispersion of ZnO Nanoparticles to Sn-Bi Solder: A Study on Microstructure, Spreading, and Mechanical Properties. J. Mater. Eng. Perform. 2021, 30, 3167–3172. [Google Scholar] [CrossRef]

- Bukat, K.; Sitek, J.; Koscielski, M.; Miedzwiedz, W.; Mlozniak, A.; Jakubowska, M. SAC solder paste with carbon nanotubes. Part II: Carbon nanotubes ‘effect on solder joints’ mechanical properties and microstructure. Solder. Surf. Mt. Technol. 2013, 25, 195–208. [Google Scholar] [CrossRef]

- Chang, N.; Chung, C.K.; Wang, Y.-P.; Lin, C.F.; Su, P.J.; Shih, T.; Kao, N.; Joe, H. 3D micro bump interface enabling top die interconnect to true circuit through silicon via wafer. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 26–29 May 2020; pp. 1888–1893. [Google Scholar] [CrossRef]

- Chuang, H.Y.; Yang, T.L.; Kuo, M.S.; Chen, Y.J.; Yu, J.J.; Li, C.C.; Kao, C.R. Critical Concerns in Soldering Reactions Arising from Space Confinement in 3-D IC Packages. IEEE Trans. Device Mater. Reliab. 2012, 12, 233–240. [Google Scholar] [CrossRef]

- Bashir, M.N.; Haseeb, A.S.M.A. Improving mechanical and electrical properties of Cu/SAC305/Cu solder joints under electromigration by using Ni nanoparticles doped flux. J. Mater. Sci. Mater. Electron. 2018, 29, 3182–3188. [Google Scholar] [CrossRef]

- Ismail, N.; Jalar, A.; Atiqah, A.; Abu, B.M. Electrical resistivity of Sn-3.0Ag-0.5Cu solder joint with the incorporation of carbon nanotubes. Nomaterials 2021, 11, 184798042199653. [Google Scholar] [CrossRef]

| Process | Solder Bump by Electroplating | Cu Pillar with Solder Cap | Solder Ball Bumping | Solder Injection on Cu Pillar | Paste Printing |

|---|---|---|---|---|---|

| Advantage | Mass production | Mass production Applicable to fine-pitch TSV | Eco-friendly Mass production Solder alloy flexibility | Fluxless process Eco-friendly Applicable to fine-pitch TSV Solder alloy flexibility | Cost-effective Mass production Solder alloy flexibility |

| Disadvantage | Limited to dual alloy systems Disposal hazardous to environment | Limited to dual alloy system Disposal hazardous to environment | Expensive tool for fine pitch TSV Flux residue | Requires high-temperature photoresist material | Flux residue Bridging Uniformity in bump height Micro voids |

| Technical limitation | Maintenance of electrolyte composition | Maintenance of electrolyte composition | Ball size | Fine-pitch stencil |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, D.H.; Seo, S.M.; Kim, J.B.; Rajendran, S.H.; Jung, J.P. A Review on the Fabrication and Reliability of Three-Dimensional Integration Technologies for Microelectronic Packaging: Through-Si-via and Solder Bumping Process. Metals 2021, 11, 1664. https://doi.org/10.3390/met11101664

Cho DH, Seo SM, Kim JB, Rajendran SH, Jung JP. A Review on the Fabrication and Reliability of Three-Dimensional Integration Technologies for Microelectronic Packaging: Through-Si-via and Solder Bumping Process. Metals. 2021; 11(10):1664. https://doi.org/10.3390/met11101664

Chicago/Turabian StyleCho, Do Hoon, Seong Min Seo, Jang Baeg Kim, Sri Harini Rajendran, and Jae Pil Jung. 2021. "A Review on the Fabrication and Reliability of Three-Dimensional Integration Technologies for Microelectronic Packaging: Through-Si-via and Solder Bumping Process" Metals 11, no. 10: 1664. https://doi.org/10.3390/met11101664

APA StyleCho, D. H., Seo, S. M., Kim, J. B., Rajendran, S. H., & Jung, J. P. (2021). A Review on the Fabrication and Reliability of Three-Dimensional Integration Technologies for Microelectronic Packaging: Through-Si-via and Solder Bumping Process. Metals, 11(10), 1664. https://doi.org/10.3390/met11101664