Exploring SiC Planar IGBTs towards Enhanced Conductivity Modulation Comparable to SiC Trench IGBTs

Abstract

1. Introduction

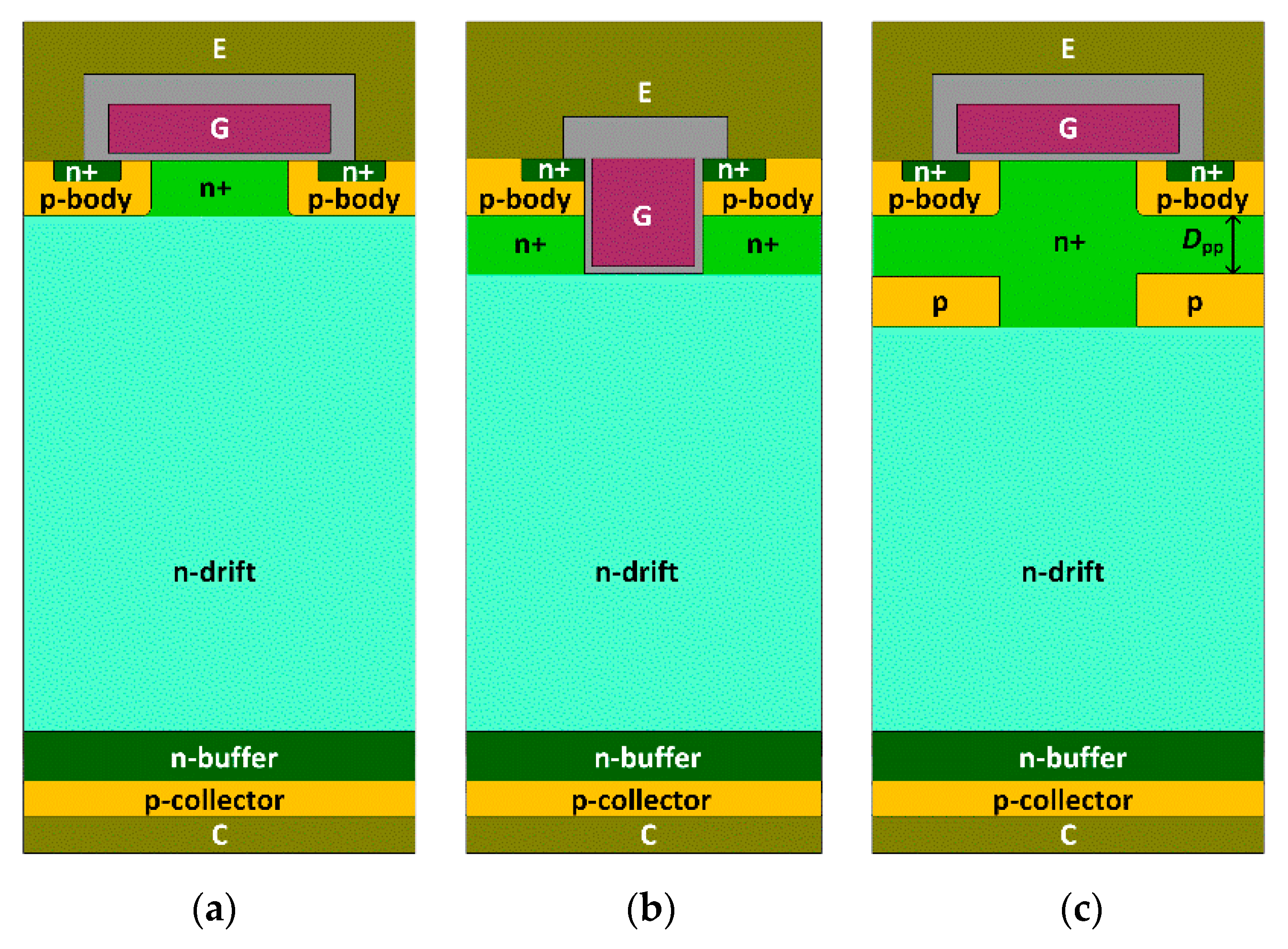

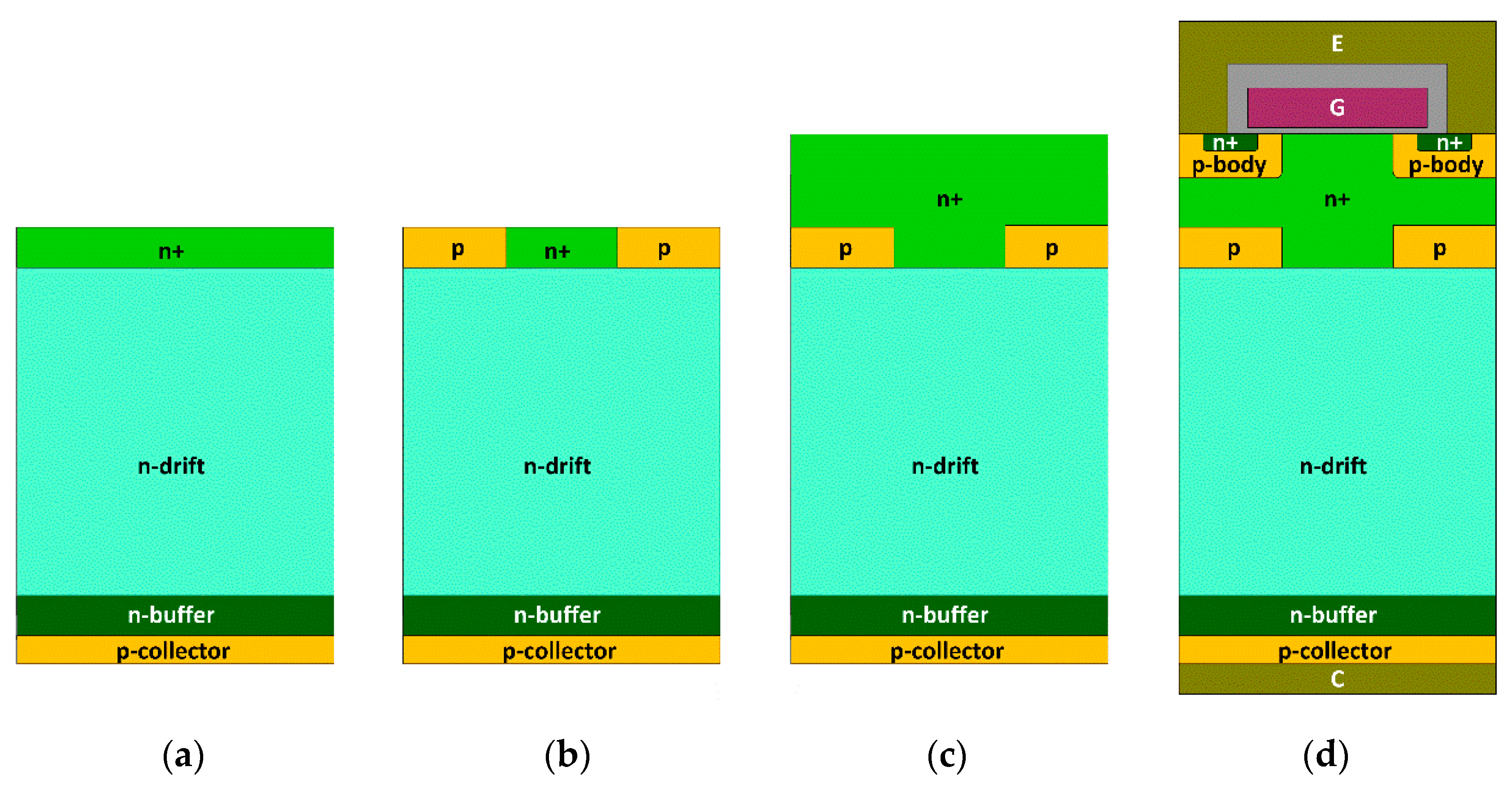

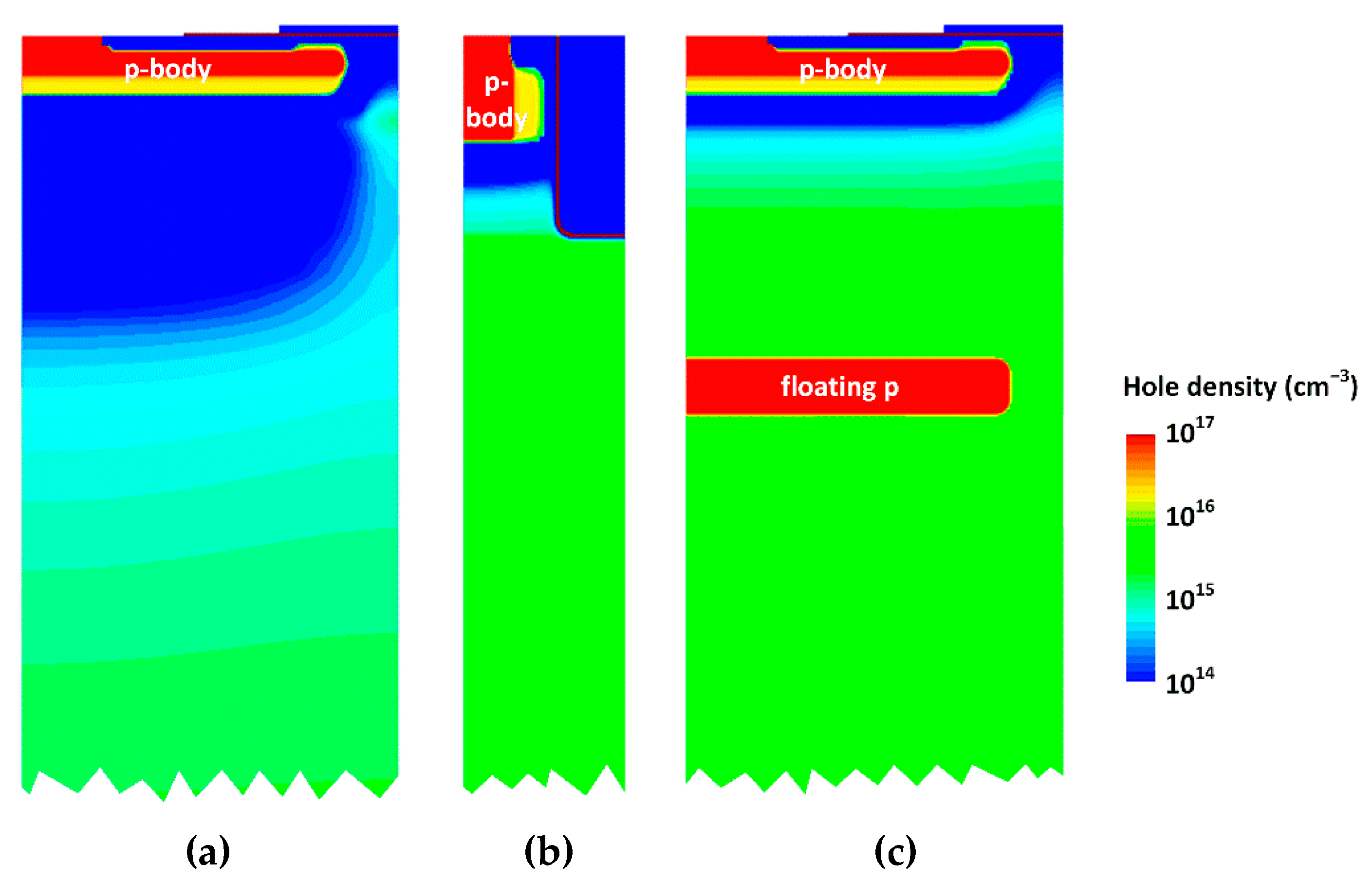

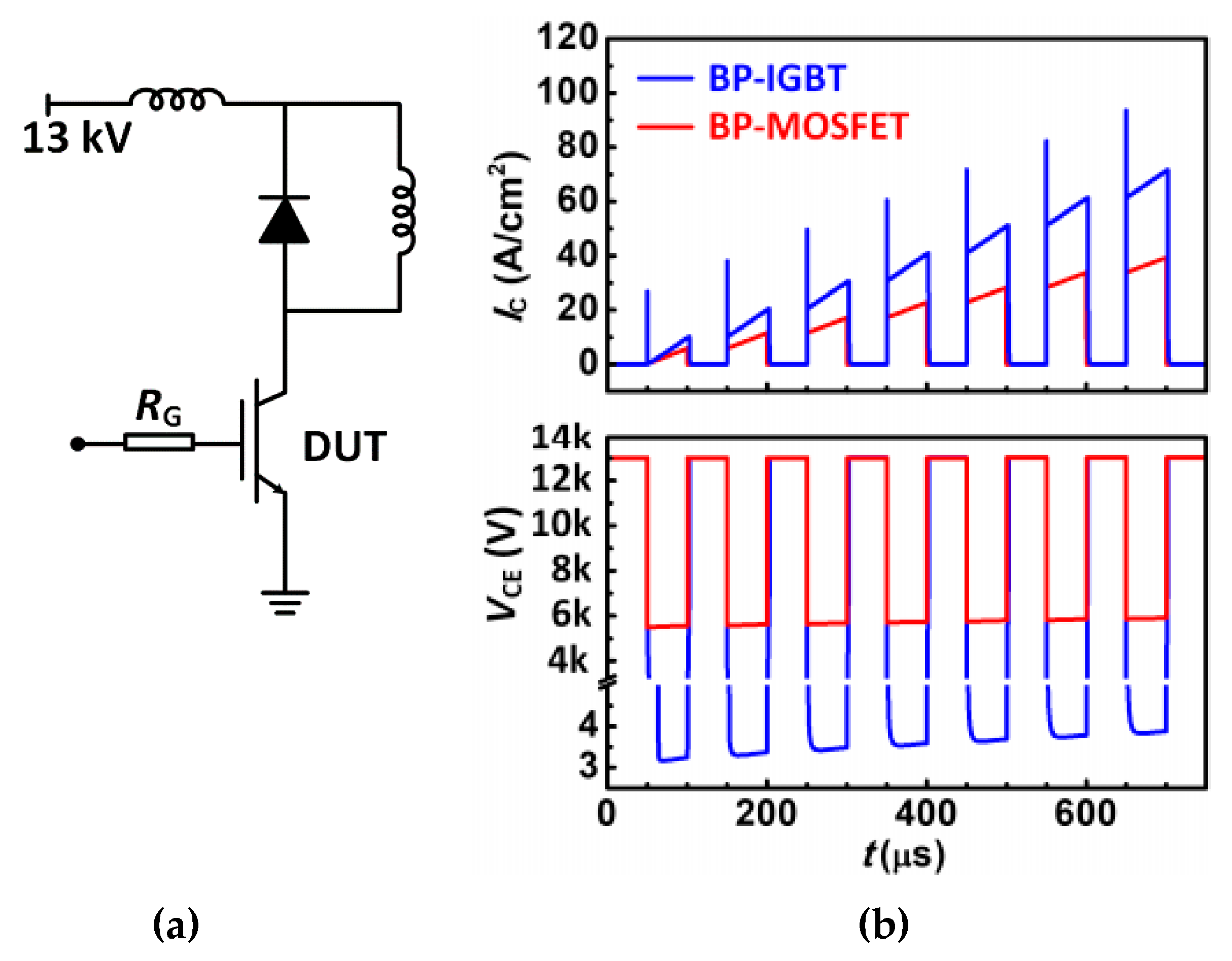

2. Device Structure and Proposed Process Flow

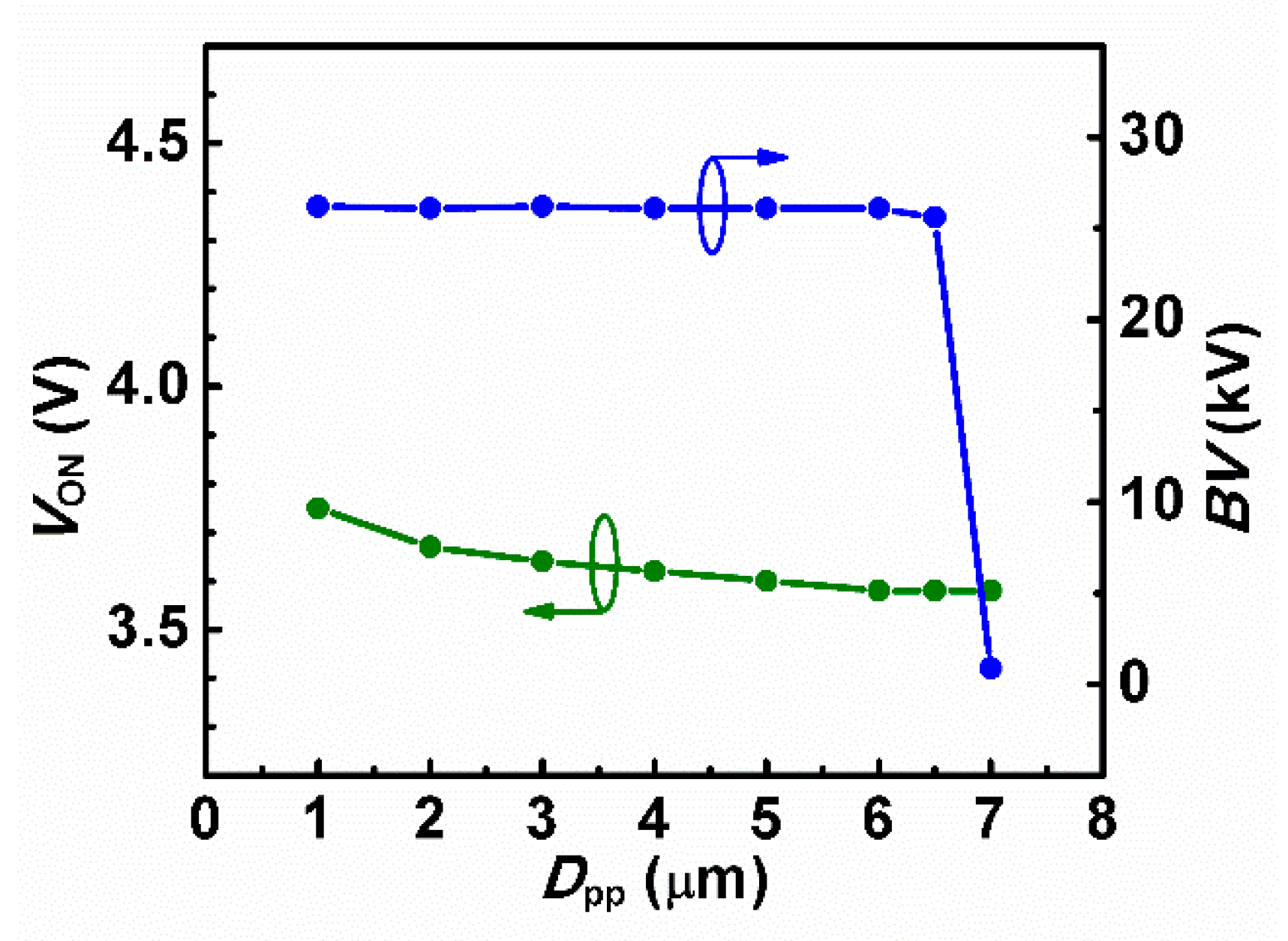

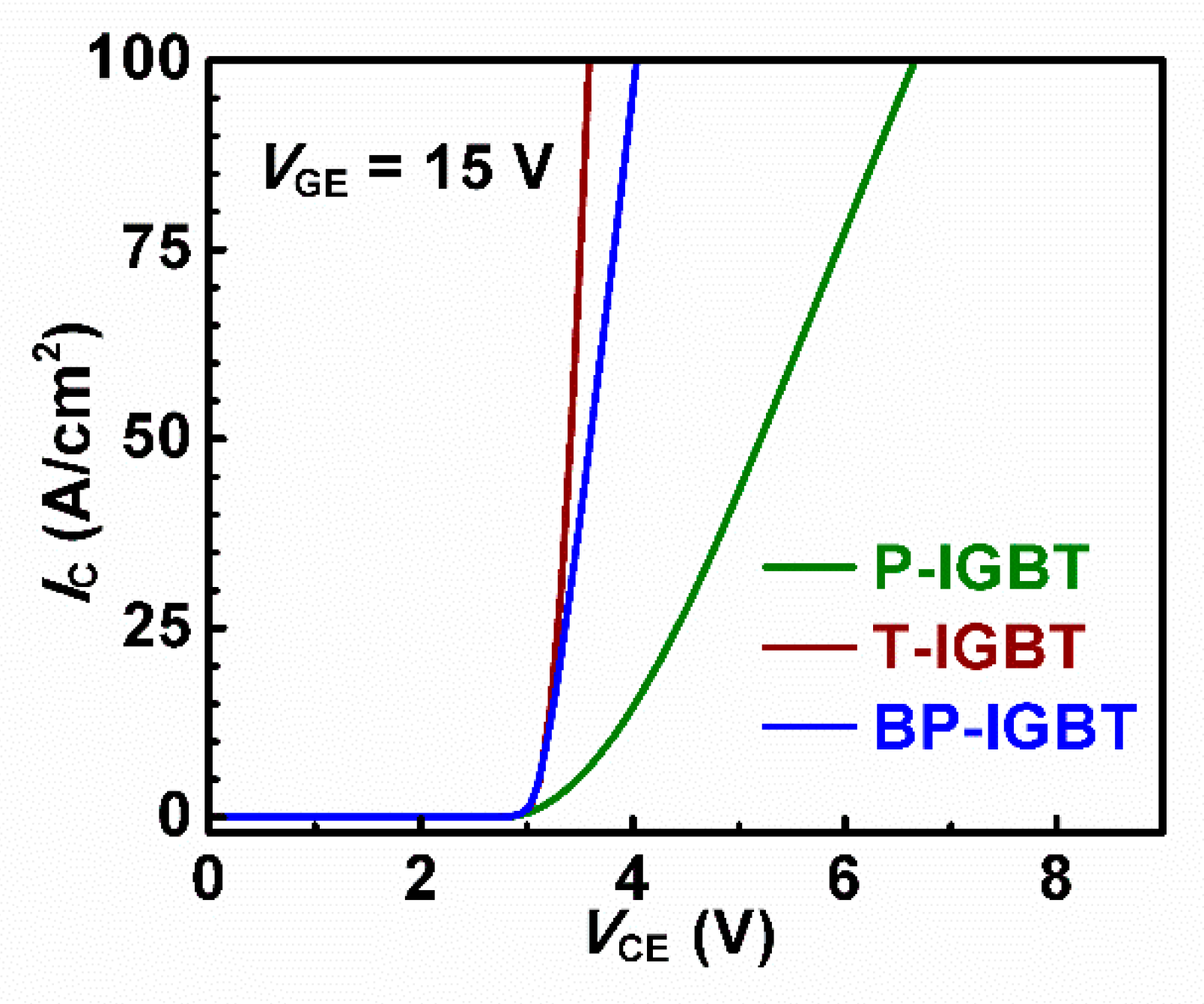

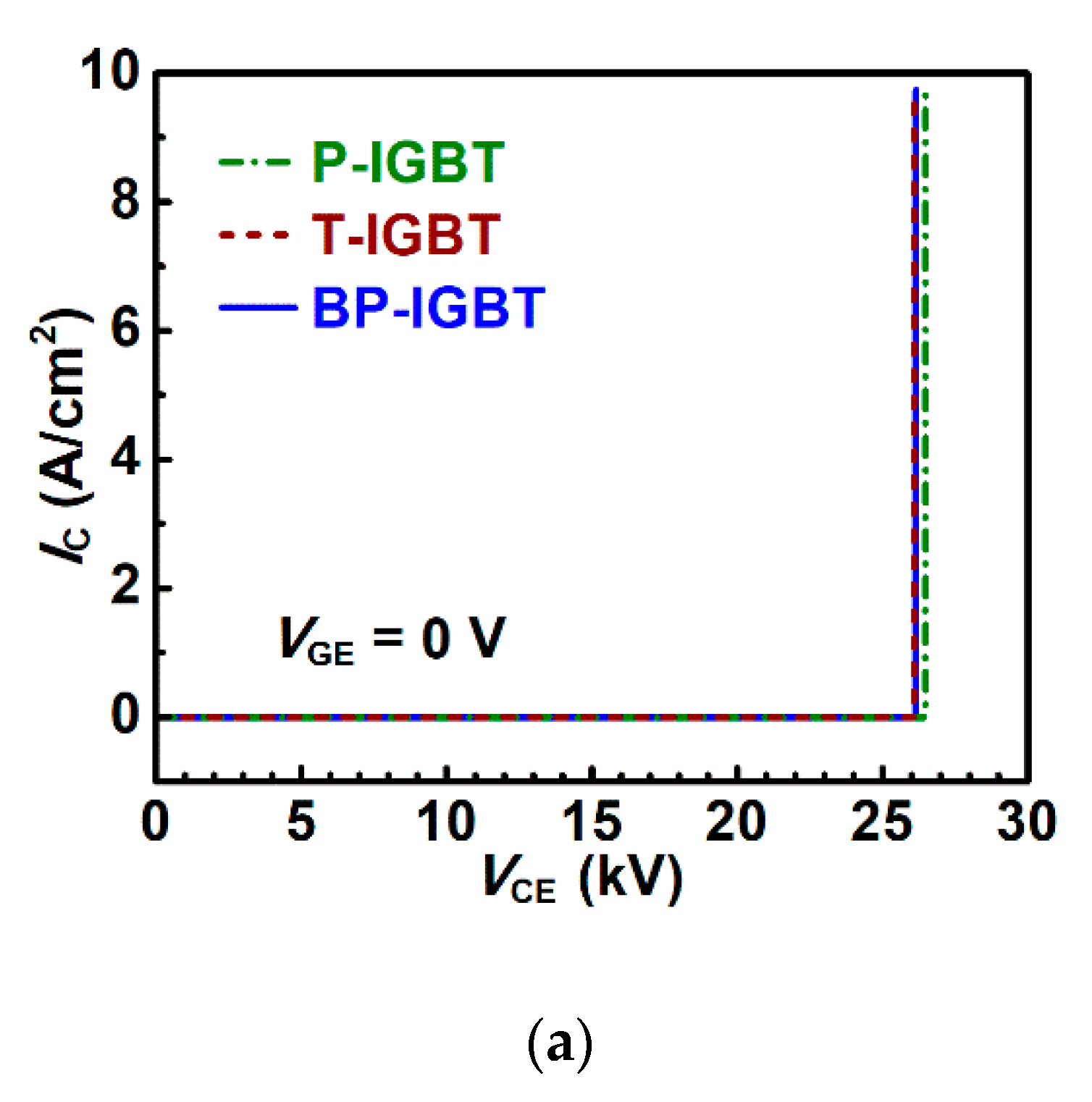

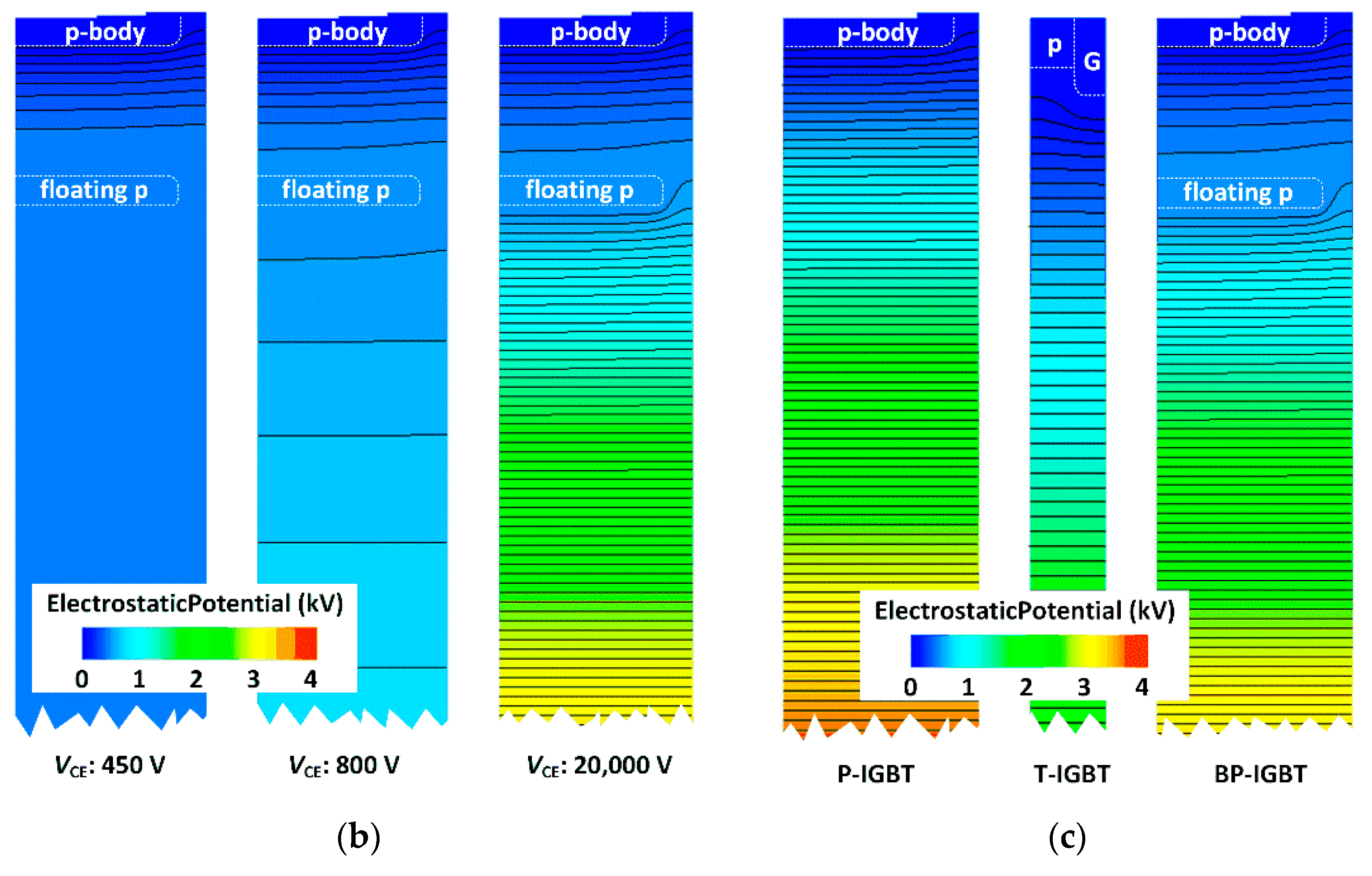

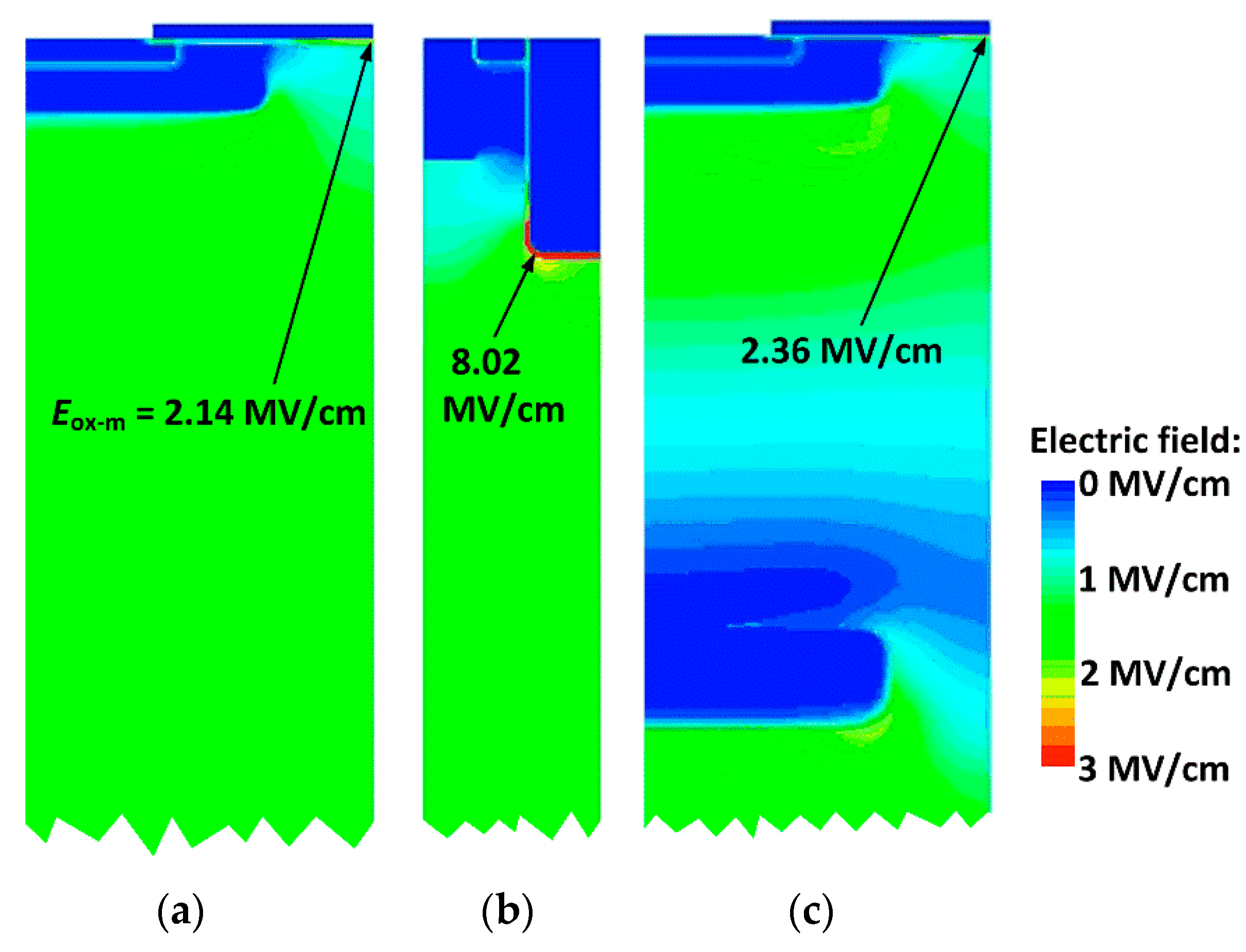

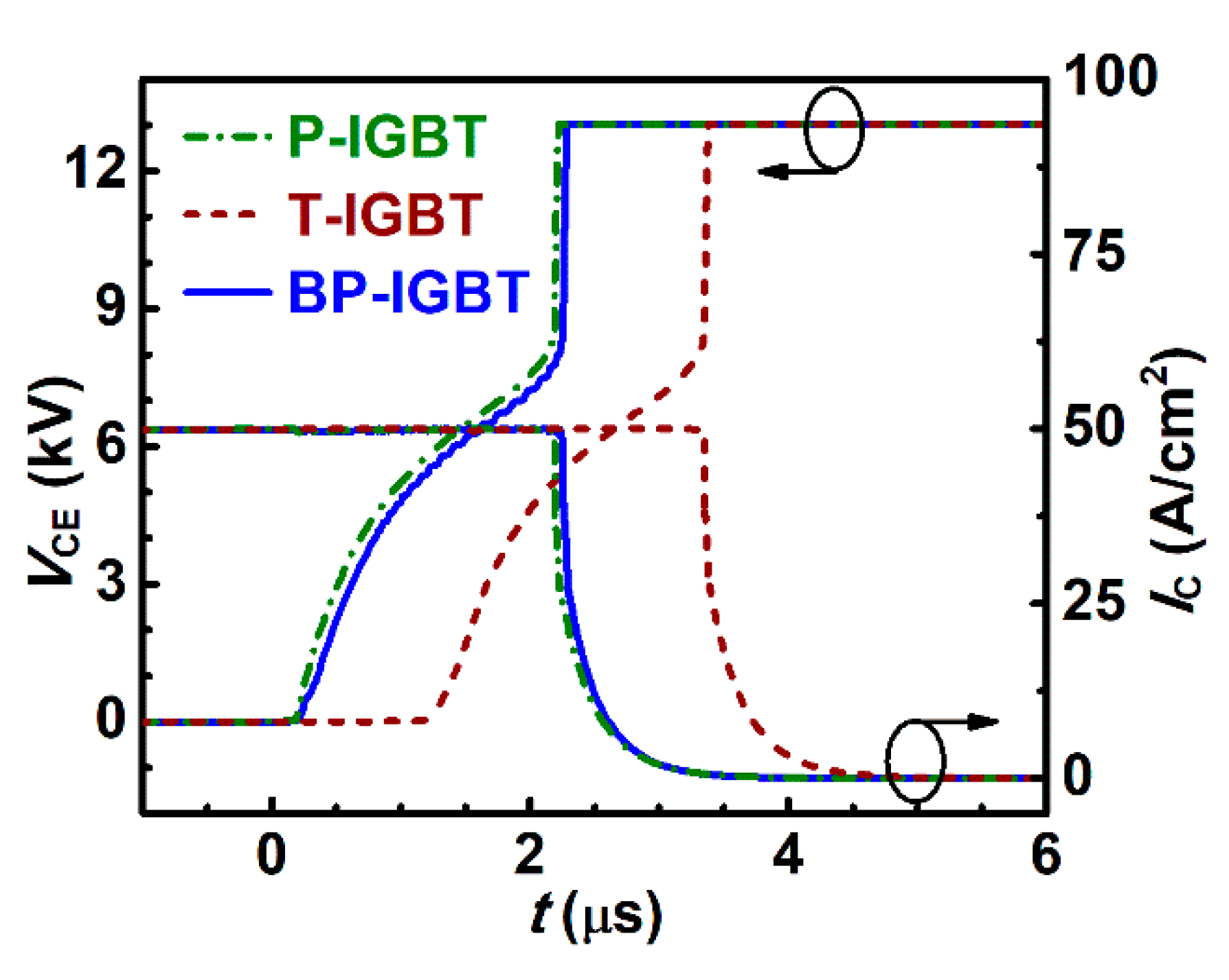

3. Device Characteristics

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; Wiley: Singapore, 2014. [Google Scholar]

- Capan, I.; Yamazaki, Y.; Oki, Y.; Brodar, T.; Makino, T.; Ohshima, T. Minority carrier trap in n-type 4H–SiC Schottky barrier diodes. Crystals 2019, 9, 328. [Google Scholar] [CrossRef]

- Lebedev, A.A.; Ber, B.Y.; Seredova, N.V.; Kazantsev, D.Y.; Kozlovski, V.V. Radiation-stimulated photoluminescence in electron irradiated 4H-SiC. J. Phys. D Appl. Phys. 2015, 48, 485106. [Google Scholar] [CrossRef]

- Daviau, K.; Lee, K.K.M. High-performance, high-temperature behavior of silicon carbide: A review. Crystals 2018, 8, 217. [Google Scholar] [CrossRef]

- Tiwari, A.K.; Antoniou, M.; Lophitis, N.; Perkins, S.; Udrea, F. Retrograde p-well for 10-kV class SiC IGBTs. IEEE Trans. Electron Devices 2019, 66, 3066–3072. [Google Scholar] [CrossRef]

- Brunt, E.V.; Cheng, L.; O’Loughlin, M.; Capell, C.; Jonas, C.; Lam, K.; Richmond, J.; Pala, V.; Ryu, S.; Allen, S.T.; et al. 22 kV 1 cm2 4H-SiC n-IGBTs with improved conductivity modulation. In Proceedings of the ISPSD, Waikoloa, HI, USA, 15–19 June 2014; pp. 358–361. [Google Scholar]

- Ryu, S.; Capell, C.; Jonas, C.; Cheng, L.; O’Loughlin, M.; Burk, A.; Agarwal, A.; Palmour, J.; Hefner, A. Ultra high voltage (>12 kV), high performance 4H-SiC IGBTs. In Proceedings of the ISPSD, Bruges, Belgium, 3–7 June 2012; pp. 257–260. [Google Scholar]

- Vechalapu, K.; Bhattacharya, S.; Van Brunt, E.; Ryu, S.; Grider, D.; Palmour, J.W. Comparative evaluation of 15-kV SiC MOSFET and 15-kV SiC IGBT for medium-voltage converter under the same dv/dt conditions. IEEE J. Emerg. Sel. Top. Power Electron 2017, 5, 469–489. [Google Scholar] [CrossRef]

- Kitagawa, M.; Omura, I.; Hasegawa, S.; Inoue, T.; Nakagawa, A. A 4500 V injection enhanced insulated gate bipolar transistor (IEGT) operating in a mode similar to a thyristor. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 679–682. [Google Scholar]

- Zhang, Q.; Chang, H.; Gomez, M.; Bui, C.; Hanna, E. 10 kV trench gate IGBTs on 4H-SiC. In Proceedings of the ISPSD, Santa Barbara, CA, USA, 23–26 May 2005; pp. 303–306. [Google Scholar]

- Zhang, M.; Wei, J.; Jiang, H.; Chen, K.J.; Cheng, C. SiC trench MOSFET with self-biased p-shield for low RON-SP and low OFF-state oxide field. IET Power Electron 2017, 10, 1208–1213. [Google Scholar] [CrossRef]

- Matsunaga, S.; Mizushima, T. Low Von 17kV SiC IGBT assisted n-MOS thyristor. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 474–477. [Google Scholar]

- Synopsys. TCAD Sentaurus Device Manual; Synopsys Inc.: Mountain View, CA, USA, 2013. [Google Scholar]

- An, J.; Namai, M.; Tanabe, M.; Okamoto, D.; Yano, H.; Iwamuro, N. Experimental demonstration of −730V vertical SiC p-MOSFET with high short circuit withstand capability for complementary inverter applications. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 272–275. [Google Scholar]

- Usman, M.; Nawaz, M. Device design assessment of 4H–SiC n-IGBT—A simulation study. Solid-State Electron. 2014, 92, 5–11. [Google Scholar] [CrossRef]

- Uchida, K.; Saitoh, Y.; Hiyoshi, T.; Masuda, T.; Wada, K.; Tamaso, H.; Hatayama, T.; Hiratsuka, K.; Tsuno, T.; Furumai, M.; et al. The optimised design and characterization of 1200 V/2.0 mΩ cm2 4H-SiC V-groove trench MOSFETs. In Proceedings of the ISPSD, Hong Kong, China, 10–14 May 2015; pp. 85–88. [Google Scholar]

- Nishio, J.; Ota, C.; Hatakeyama, T.; Shinohe, T.; Kojima, K.; Nishizawa, S.; Ohashi, H. Ultralow-loss SiC floating junction Schottky barrier diodes (super-SBDs). IEEE Trans. Electron Devices 2008, 55, 1954–1960. [Google Scholar] [CrossRef]

- Sumitomo, M.; Sakane, H.; Arakawa, K.; Higuchi, Y.; Matsui, M. Injection control technique for high speed switching with a double gate PNM-IGBT. In Proceedings of the ISPSD, Kanazawa, Japan, 26–30 May 2013; pp. 33–36. [Google Scholar]

- Zerarka, M.; Austin, P.; Bafleur, M. Comparative study of sensitive volume and triggering criteria of SEB in 600 V planar and trench IGBTs. Microelectron. Reliab. 2011, 51, 1990–1994. [Google Scholar] [CrossRef]

- Matocha, K.; Dunne, G.; Soloviev, S.; Beaupre, R. Time-dependent dielectric breakdown of 4H-SiC MOS capacitors and DMOSFETs. IEEE Trans. Electron Devices 2008, 55, 1830–1834. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Wang, H.; Chen, K.J. Dynamic degradation in SiC trench MOSFET with a floating p-shield revealed with numerical simulations. IEEE Trans. Electron Devices 2017, 64, 2592–2598. [Google Scholar] [CrossRef]

- Takaya, H.; Miyagi, K.; Hamada, K. Floating islands and thick bottom oxide trench gate MOSFET (FITMOS) with passive hole gate. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar]

| Parameter | P-IGBT | T-IGBT | BP-IGBT | Unit |

|---|---|---|---|---|

| n-drift thickness | 180 | 180 | 180 | μm |

| n-drift doping | 2.5 × 1014 | 2.5 × 1014 | 2.5 × 1014 | cm−3 |

| gate oxide thickness | 50 | 50 | 50 | nm |

| n+-emitter thickness | 0.2 | 0.2 | 0.2 | μm |

| n+-emitter doping | 5 × 1019 | 5 × 1019 | 5 × 1019 | cm−3 |

| p-body thickness | 1.0 | 1.2 | 1.0 | μm |

| p-body doping | 1 × 1017 | 1 × 1017 | 1 × 1017 | cm−3 |

| cell pitch | 14 | 3.5 | 14 | μm |

| carrier lifetime | 2.0 | 2.0 | 2.0 | μs |

| n+-region doping | 2 × 1016 | 2 × 1016 | 2 × 1016 | cm−3 |

| thickness of buried p-layer | n/a | n/a | 1 | μm |

| buried p-layer doping | n/a | n/a | 1 × 1018 | cm−3 |

| n-buffer thickness | 10 | 10 | 10 | μm |

| n-buffer doping | 4 × 1017 | 4 × 1017 | 4 × 1017 | cm−3 |

| p-collector thickness | 5 | 5 | 5 | μm |

| p-collector doping | 1 × 1019 | 1 × 1019 | 1 × 1019 | cm−3 |

| P-IGBT | T-IGBT | BP-IGBT | Unit | |

|---|---|---|---|---|

| VON | 5.2 | 3.4 | 3.6 | V |

| BV | 26.5 | 26.09 | 26.15 | kV |

| Eox-m | 2.14 | 8.02 | 2.36 | MV/cm |

| EOFF | 0.65 | 0.65 | 0.62 | J/cm2 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, M.; Li, B.; Wei, J. Exploring SiC Planar IGBTs towards Enhanced Conductivity Modulation Comparable to SiC Trench IGBTs. Crystals 2020, 10, 417. https://doi.org/10.3390/cryst10050417

Zhang M, Li B, Wei J. Exploring SiC Planar IGBTs towards Enhanced Conductivity Modulation Comparable to SiC Trench IGBTs. Crystals. 2020; 10(5):417. https://doi.org/10.3390/cryst10050417

Chicago/Turabian StyleZhang, Meng, Baikui Li, and Jin Wei. 2020. "Exploring SiC Planar IGBTs towards Enhanced Conductivity Modulation Comparable to SiC Trench IGBTs" Crystals 10, no. 5: 417. https://doi.org/10.3390/cryst10050417

APA StyleZhang, M., Li, B., & Wei, J. (2020). Exploring SiC Planar IGBTs towards Enhanced Conductivity Modulation Comparable to SiC Trench IGBTs. Crystals, 10(5), 417. https://doi.org/10.3390/cryst10050417