Novel Tunable Pseudoresistor-Based Chopper-Stabilized Capacitively Coupled Amplifier and Its Machine Learning-Based Application

Abstract

1. Introduction

2. Materials and Methods

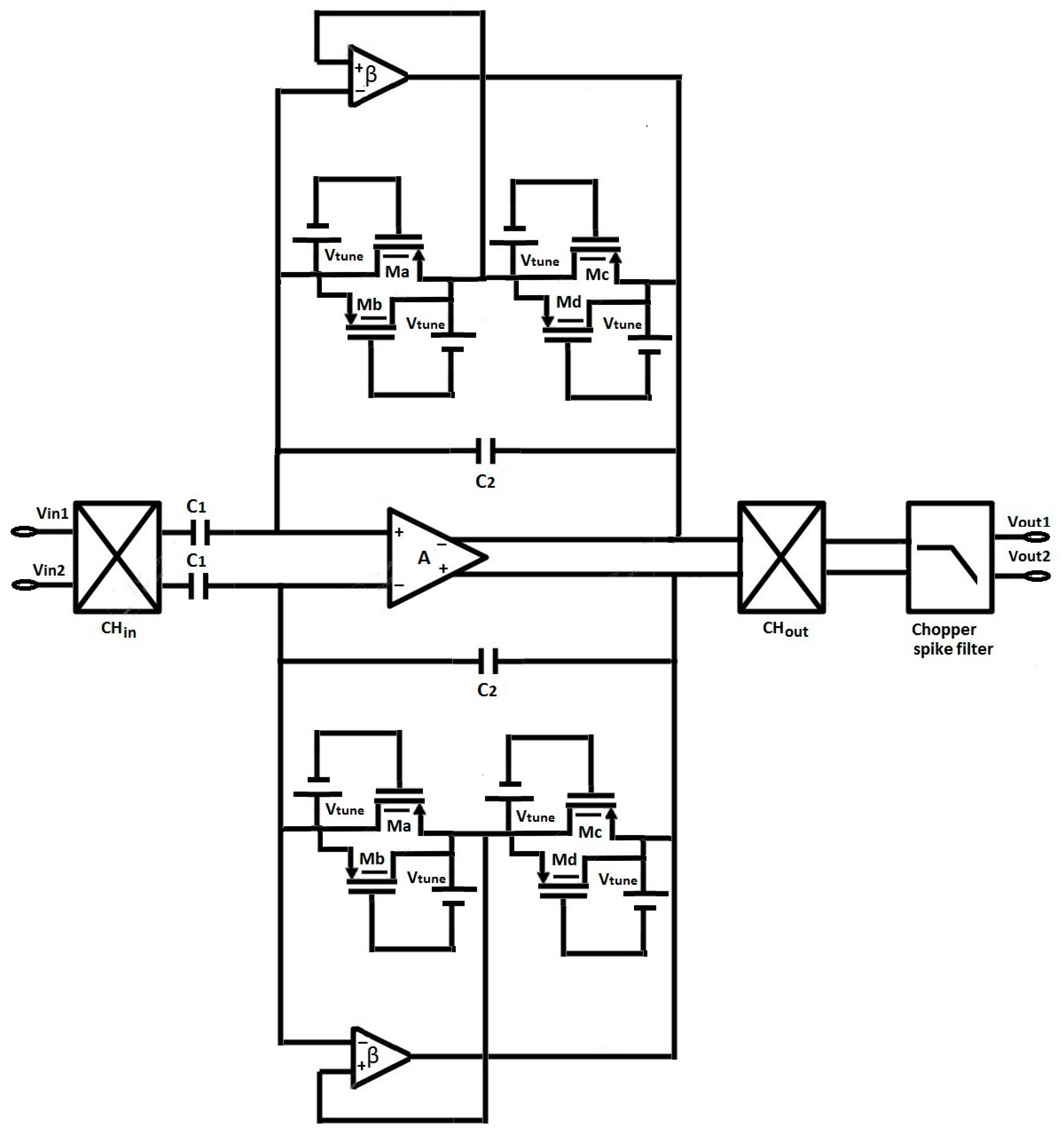

2.1. Capacitively Coupled Chopper-Based Amplifier

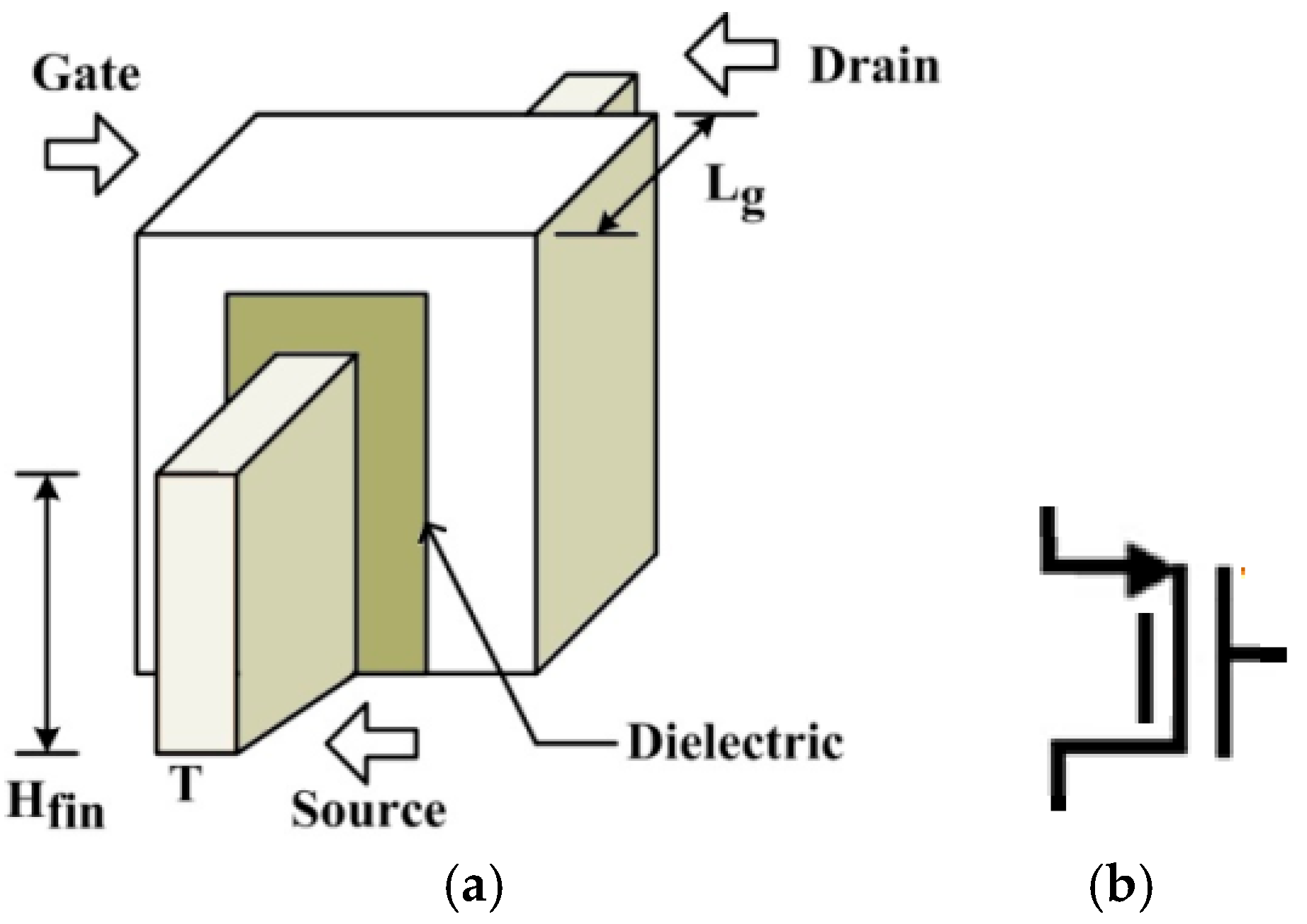

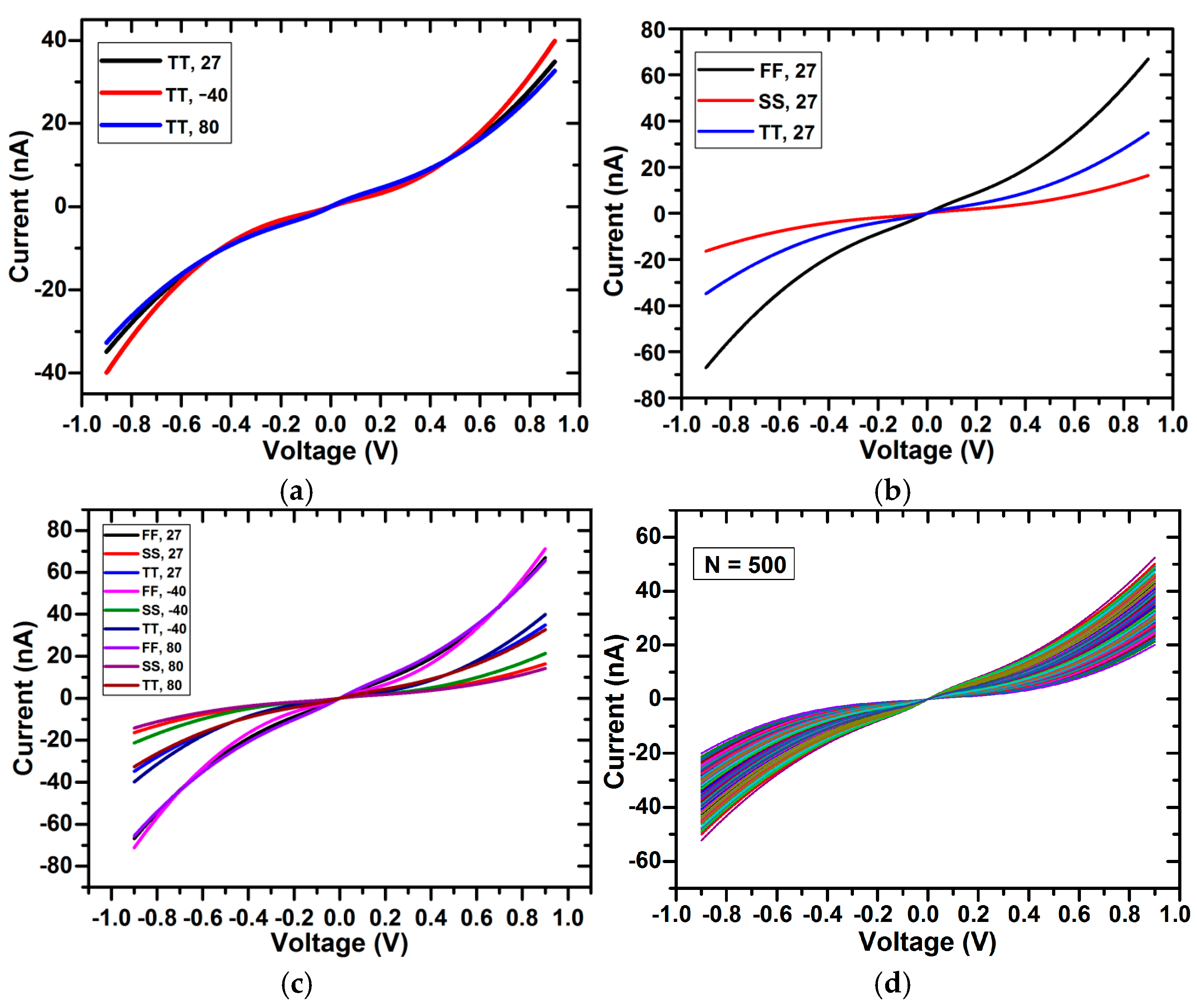

2.2. Pseudoresistor

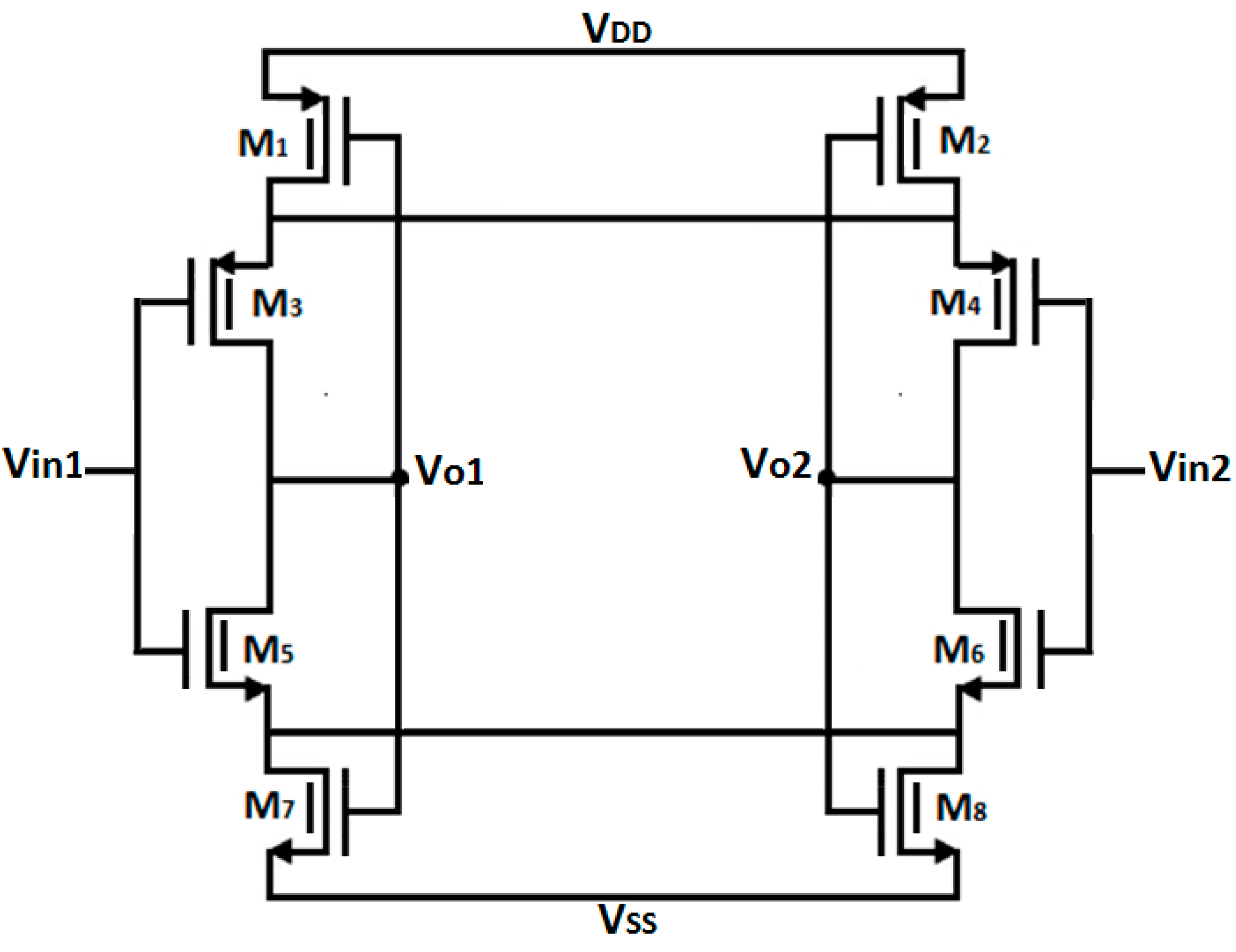

2.3. Core Amplifier

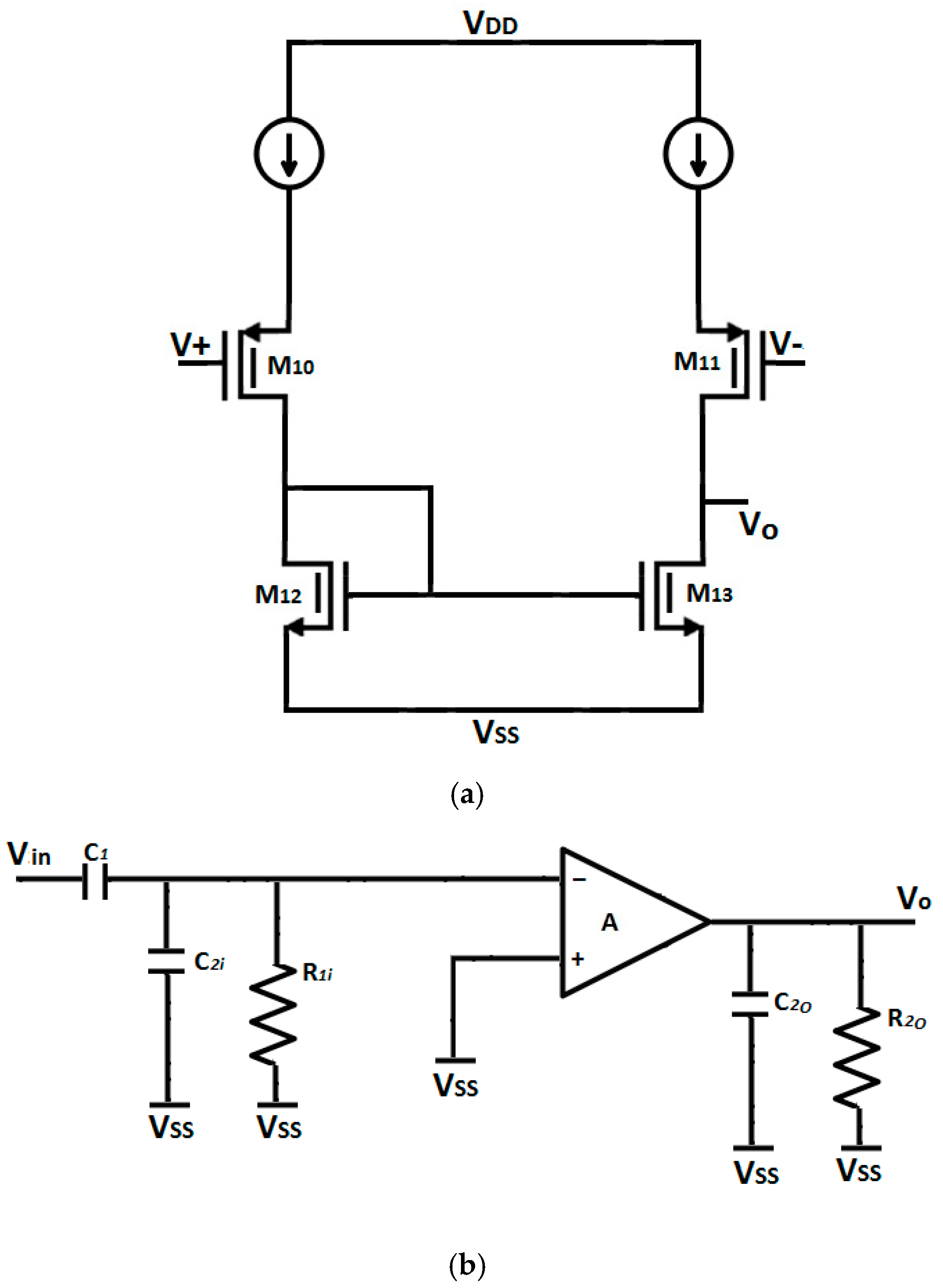

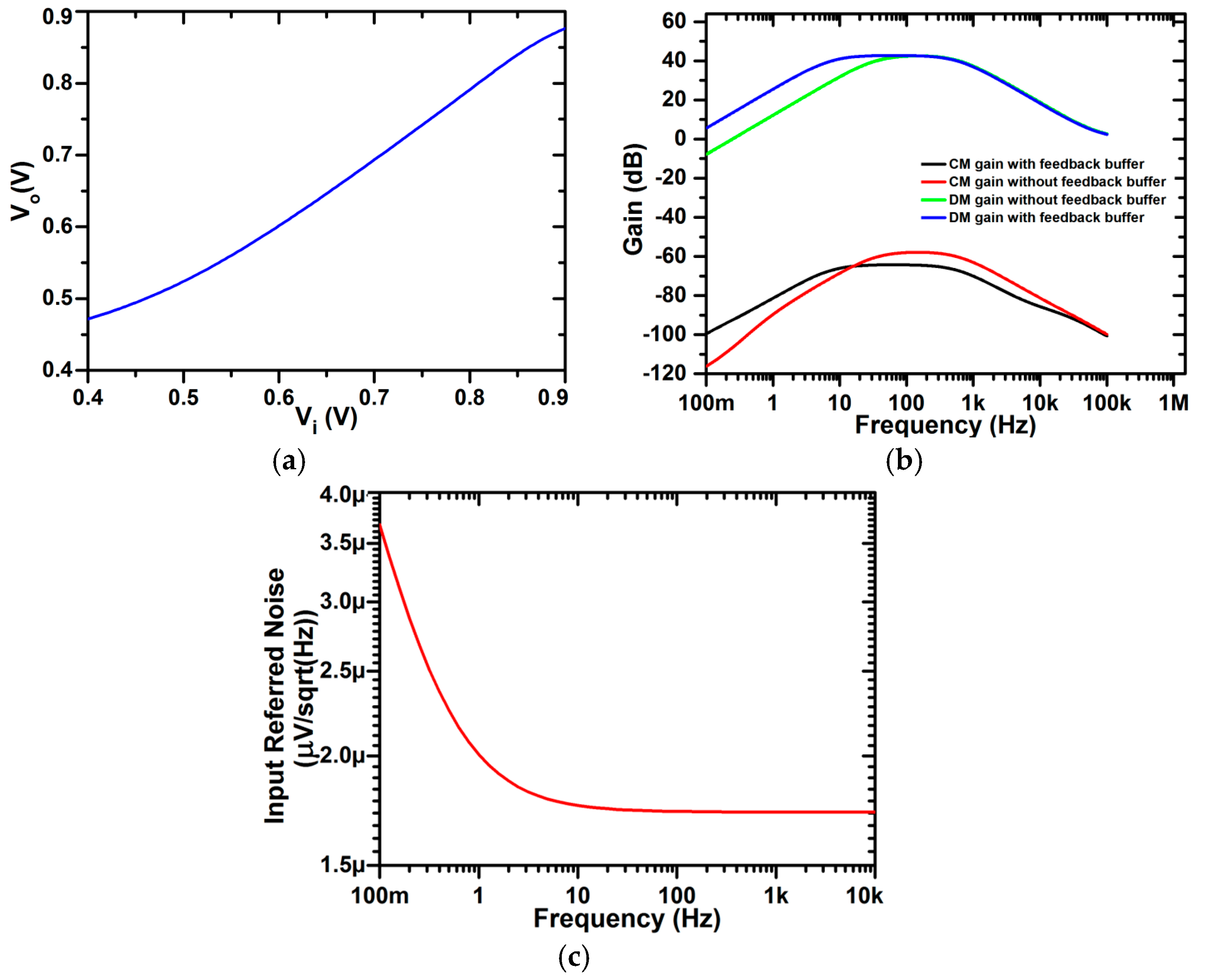

2.4. Feedback Buffer

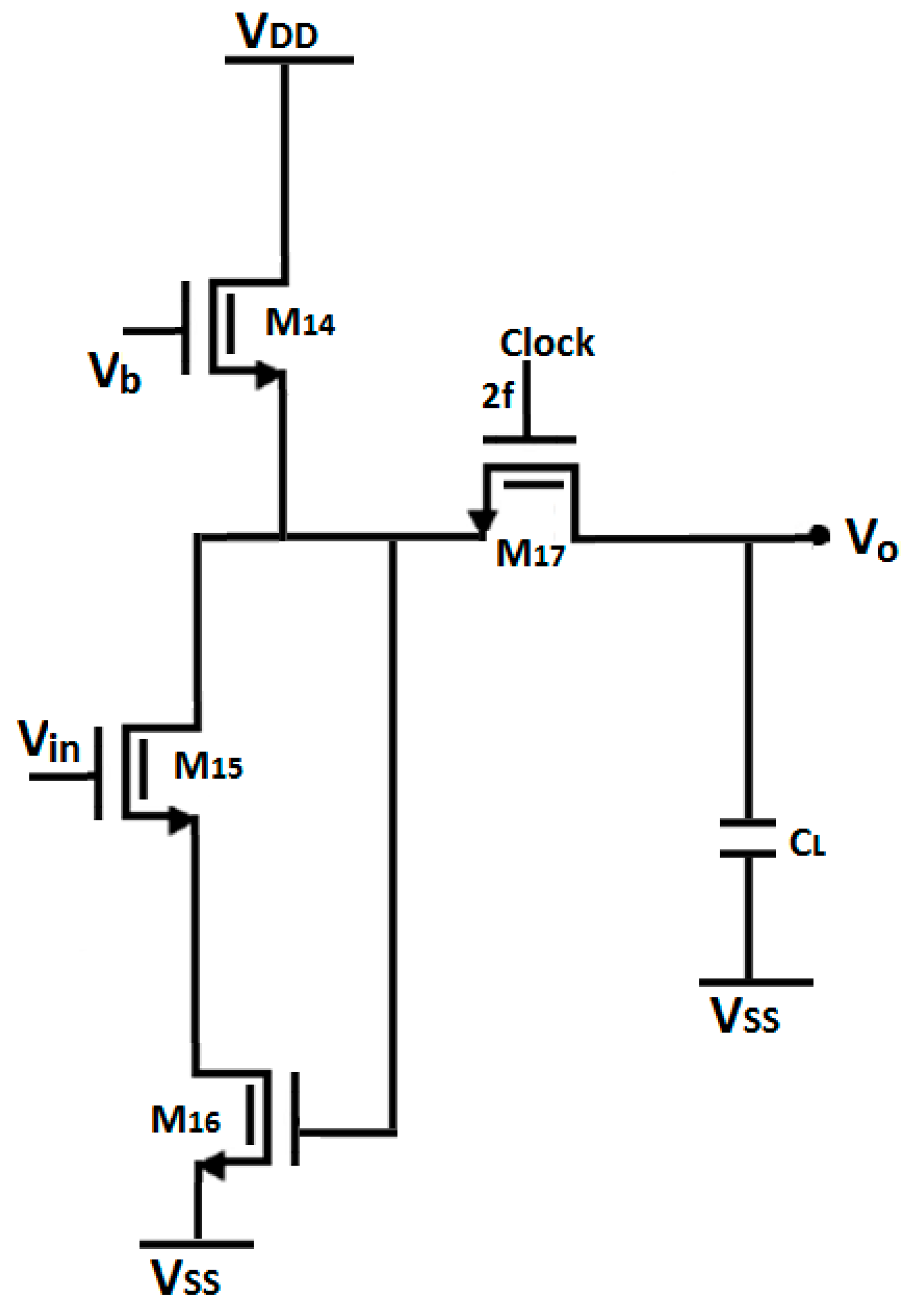

2.5. Chopper Spike Filter

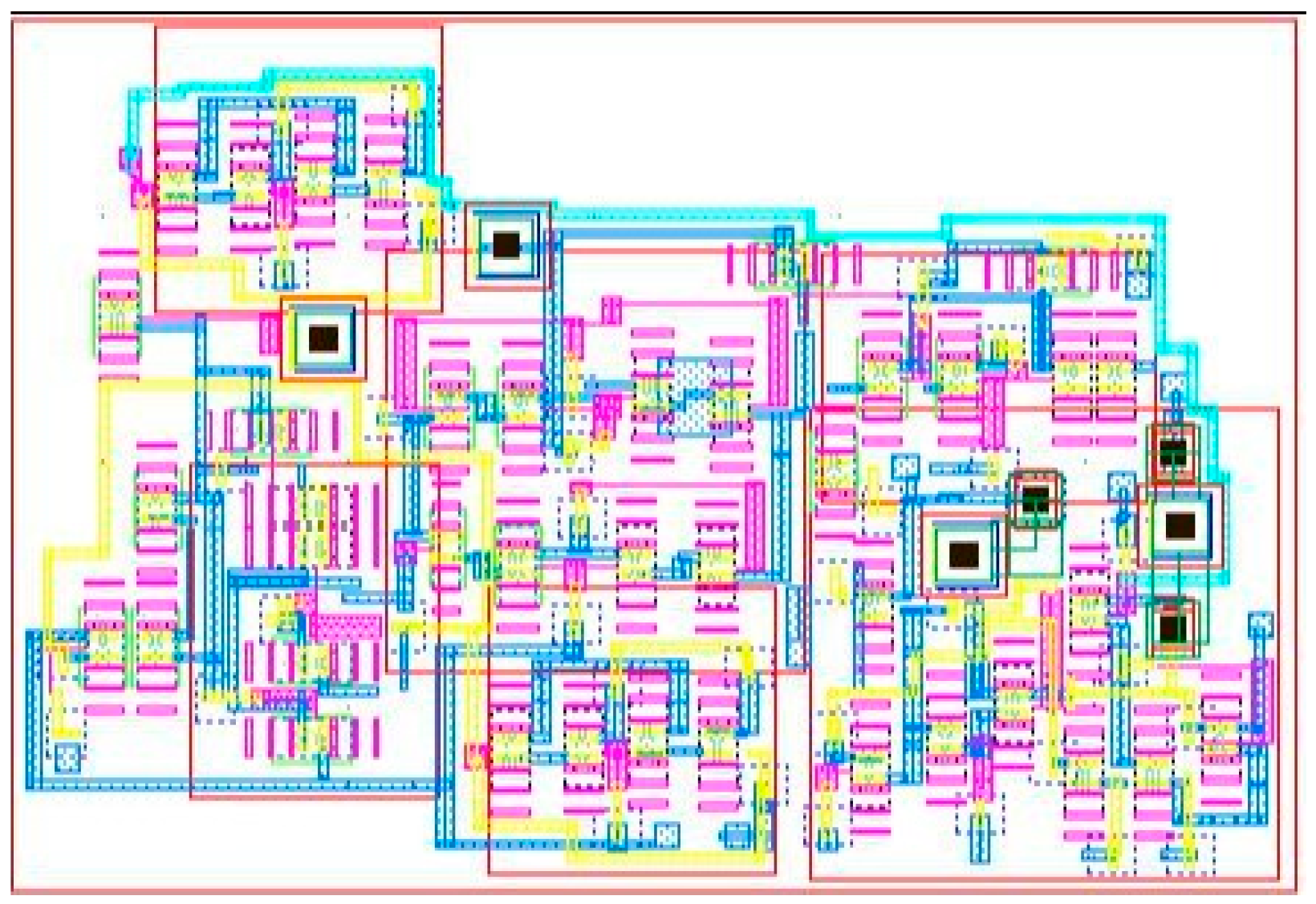

2.6. Circuit Design Methodology

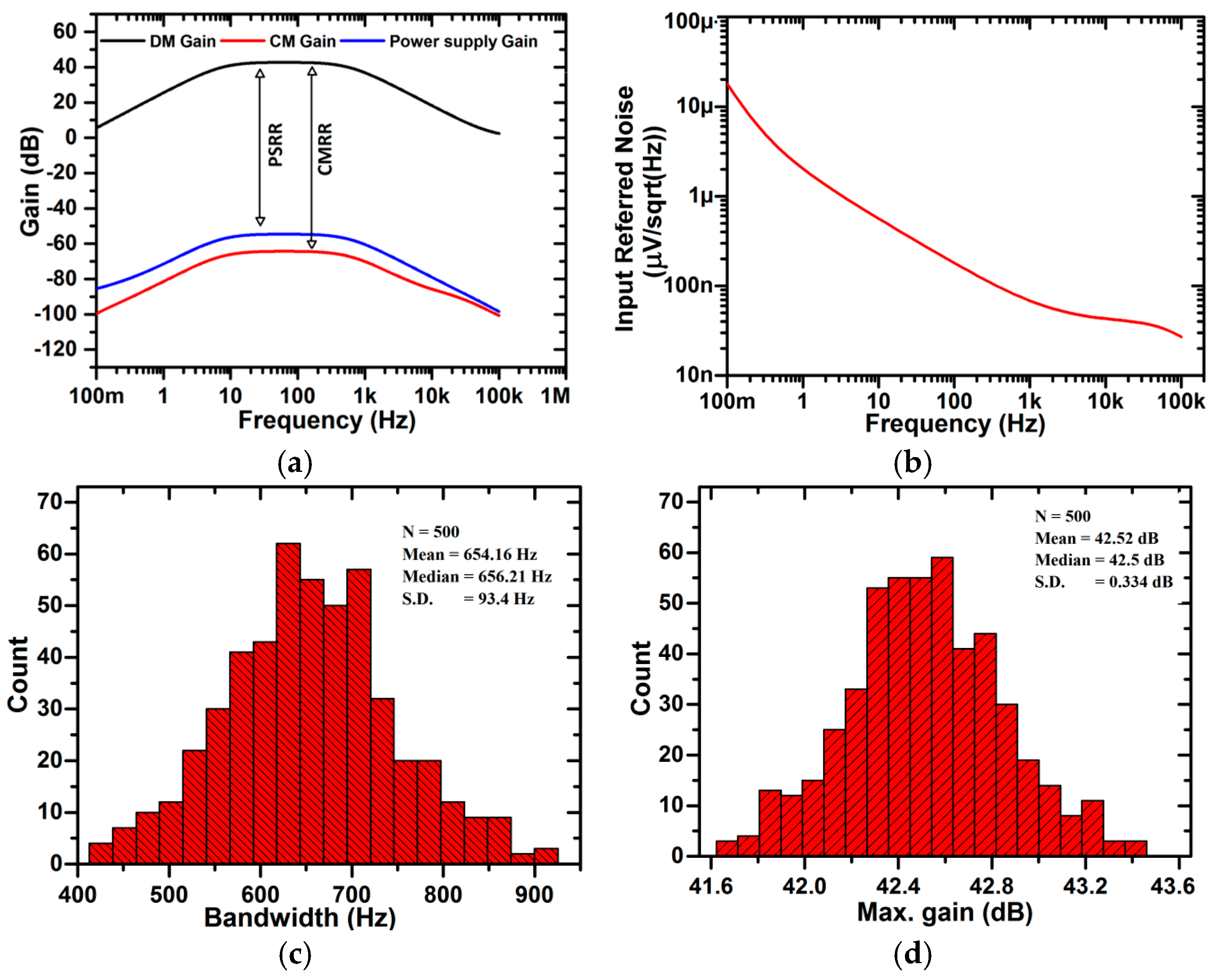

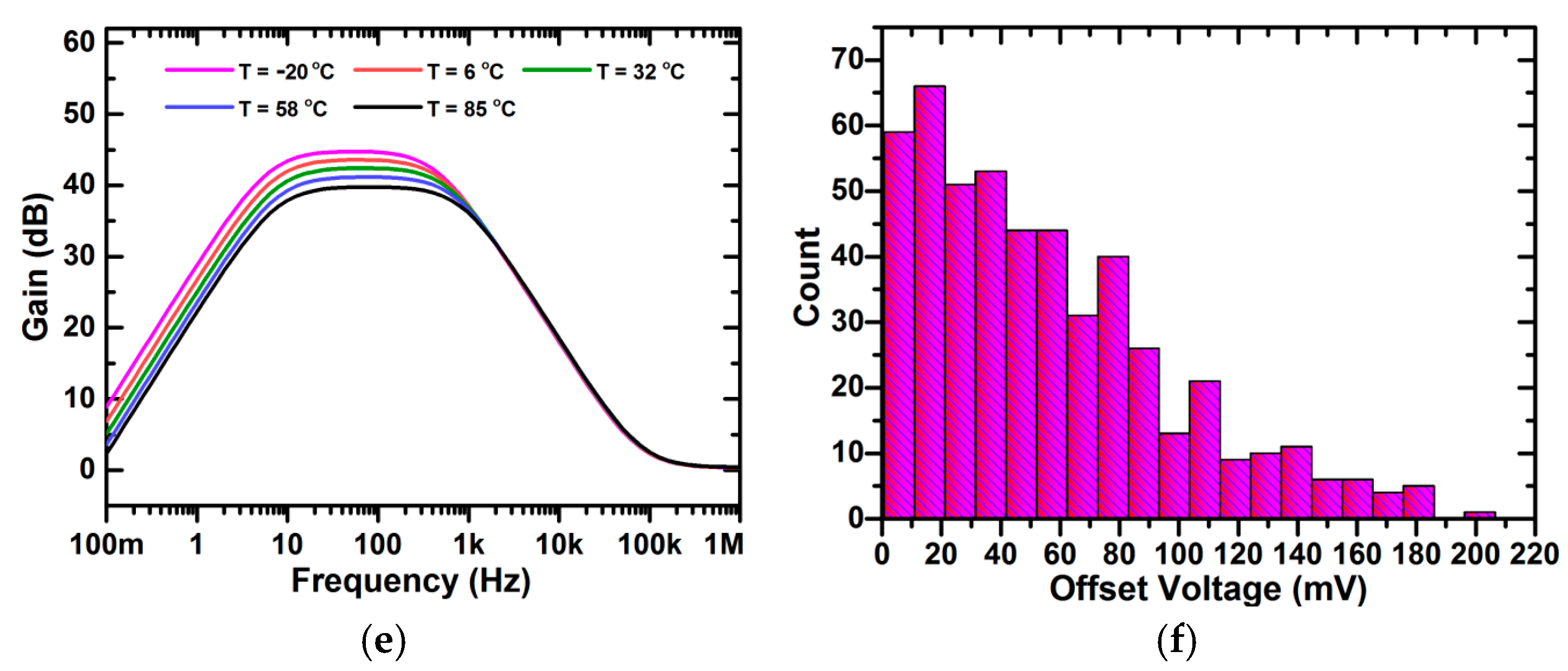

3. Results

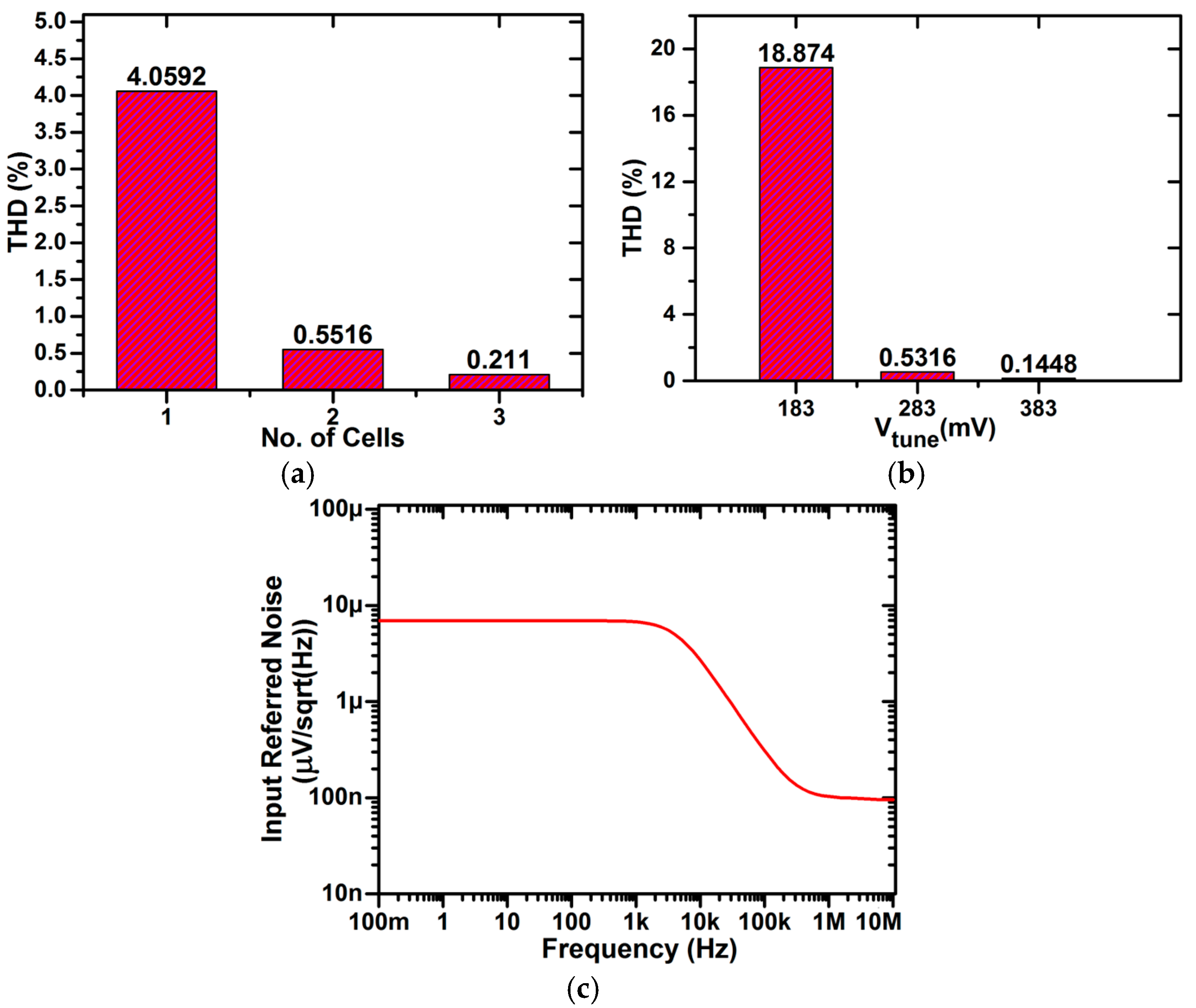

3.1. Effect of the Parallel Cell Configuration of the Tunable Pseudoresistor

3.2. Effect of Feedback Buffer

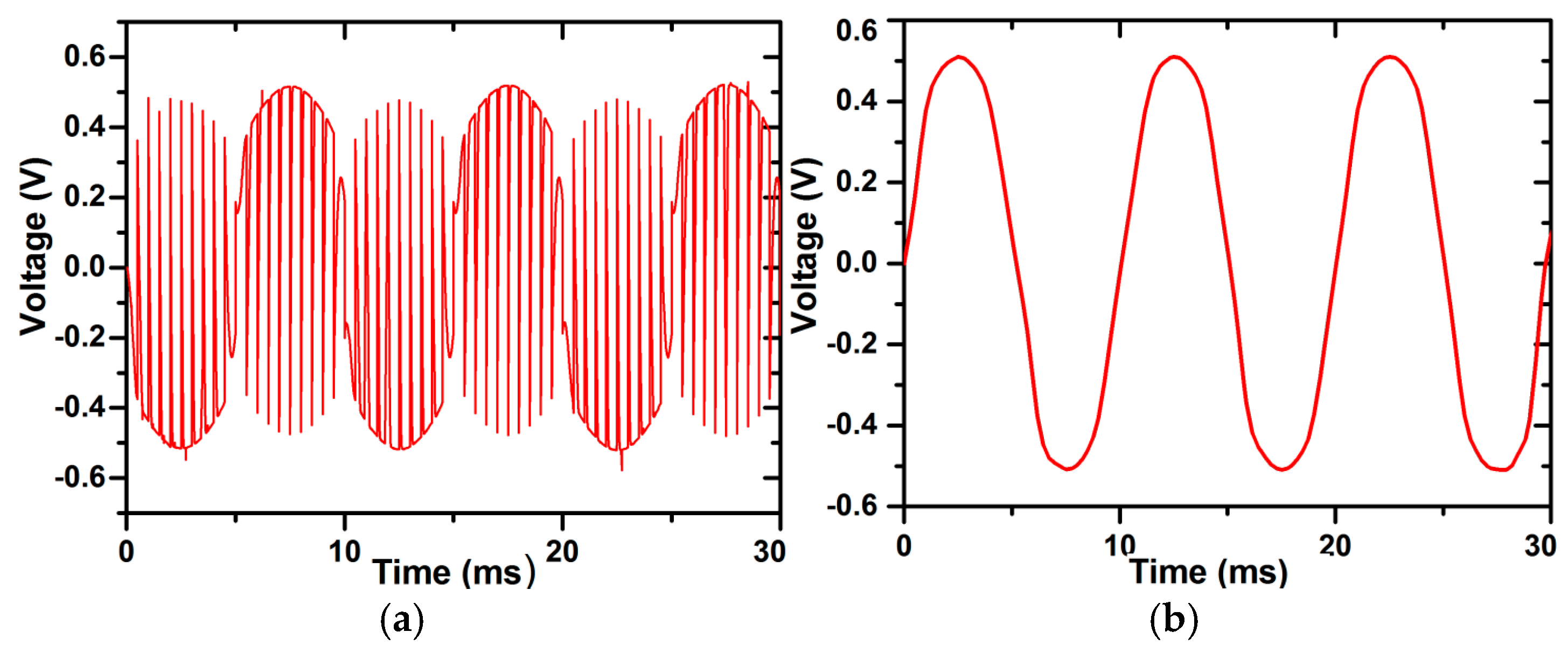

3.3. Effect of the Chopper Spike Filter

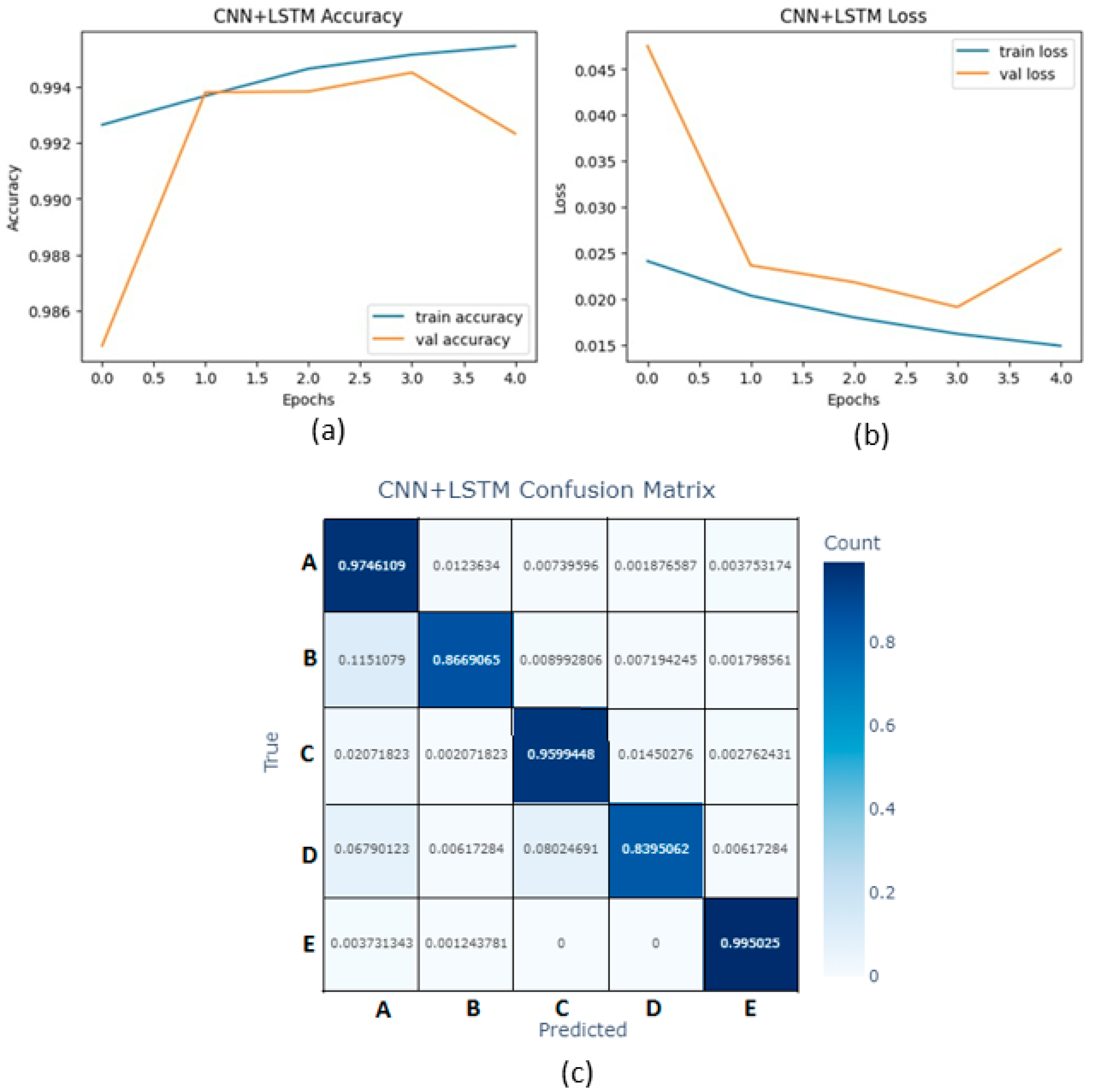

4. Machine Learning-Based Application of Biomedical Signals for Arrhythmia Diagnosis

5. Discussion

- Higher CMRR: This work presents a better CMRR compared to other works [25,26,27,28,29,30,31], primarily due to the use of a feedback buffer. Unlike [32], where the CM-REP technique was utilized, the proposed approach improves the CMRR by reducing the common-mode gain through parasitic capacitance compensation using the buffer.

- Lower cut-off frequency: In this work, a reduced low cut-off frequency is achieved by applying Miller’s effect simultaneously on both the feedback buffer and capacitance, while in [31], Miller’s effect is applied only on the feedback capacitor.

- Biasing technique: The gm/Id biasing technique is used in this work, with the circuit biased in the moderate inversion region, resulting in an optimal trade-off between power, gain, and noise.

- Interdisciplinary application: In addition, this study presents a machine learning-based proof of concept for arrhythmia classification, which demonstrates the amplifier’s practical usefulness in real-time biomedical IoT applications.

- Robustness to mismatch: The Monte-Carlo offset analysis (Figure 7f) exhibits a mean value of 53.24 mV and a standard deviation of 8.3 mV, producing a variability ratio (σ/μ) of 0.155. This is lower than the typically reported values in CMOS-based bio-amplifiers [25,26,28], confirming that the proposed FinFET-based design provides better robustness against process variation and mismatch.

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Kim, J.; Ko, H. A dynamic instrumentation amplifier for low-power and low-noise biopotential acquisition. Sensors 2016, 16, 354. [Google Scholar] [CrossRef]

- Zhao, Y.; Shang, Z.; Lian, Y. A 2.55 NEF 76 dB CMRR DC-coupled fully differential difference amplifier based analog front end for wearable biomedical sensors. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 918–926. [Google Scholar] [CrossRef]

- Ng, K.A.; Xu, Y.P. A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE J. Solid-State Circuits 2016, 51, 724–737. [Google Scholar]

- Chebli, R.; Ali, M.; Sawan, M. High-CMRR low-noise fully integrated front-end for eeg acquisition systems. Electronics 2019, 8, 1157. [Google Scholar] [CrossRef]

- Pham, X.T.; Kieu, X.T.; Hoang, M.K. Ultra-low power programmable bandwidth Capacitively-coupled chopper instrumentation amplifier using 0.2 V supply for biomedical applications. J. Low Power Electron. Appl. 2023, 13, 37. [Google Scholar] [CrossRef]

- Hashemi Noshahr, F.; Nabavi, M.; Gosselin, B.; Sawan, M. Low-cutoff frequency reduction in neural amplifiers: Analysis and implementation in CMOS 65 nm. Front. Neurosci. 2021, 15, 667846. [Google Scholar] [CrossRef]

- Ahmad, R.; Choudhary, N.; Gupta, S.K.; Joshi, A.M.; Boolchandani, D. Novel tunable current feedback instrumentation amplifier based on BBFC OP-AMP for biomedical applications with low power and high CMRR. Integration 2023, 90, 214–223. [Google Scholar] [CrossRef]

- Webster, J.G. (Ed.) Medical Instrumentation: Application and Design; John Wiley & Sons: Hoboken, NJ, USA, 2009. [Google Scholar]

- Zaidi, M.; Grout, I.; A’ain, A.K. Operational Amplifier Design in CMOS at Low-Voltage for Sensor Input Front-End Circuits in VLSI Devices. In Very-Large-Scale Integration; IntechOpen: London, UK, 2017. [Google Scholar]

- Agnes, A.; Cabrini, A.; Maloberti, F.; Martini, G. Cancellation of Amplifier Offset and 1/f Noise: An Improved Chopper Stabilized Technique. IEEE Trans. Circuits Syst. II Express Briefs 2007, 54, 469–473. [Google Scholar] [CrossRef]

- Rajput, S.S.; Jamuar, S.S. Low voltage analog circuit design techniques. IEEE Circuits Syst. Mag. 2002, 2, 24–42. [Google Scholar] [CrossRef]

- Atamuratov, A.E.; Abdikarimov, A.; Khalilloev, M.; Atamuratova, Z.A.; Rahmanov, R.; Garcia-Loureiro, A.; Yusupov, A. Simulation of DIBL effect in 25 nm SOI-FinFET with the different body shapes. Nanosyst. Phys. Chem. Math. 2017, 8, 71–74. [Google Scholar] [CrossRef][Green Version]

- Guo, Z.; Balasubramanian, S.; Zlatanovici, R.; King, T.J.; Nikolić, B. FinFET-based SRAM design. In Proceedings of the 2005 International Symposium on Low Power Electronics and Design, San Diego, CA, USA, 8–10 August 2005; pp. 2–7. [Google Scholar]

- Sharma, P.; Khandelwal, S.; Akashe, S. Design & optimization of FinFET based Schmitt trigger using leakage reduction techniques. In Proceedings of the 2015 Fifth International Conference on Advanced Computing & Communication Technologies, Haryana, India, 21–22 February 2015; pp. 70–74. [Google Scholar]

- Benko, P.L.; Galeti, M.; Pereira, C.F.; Lucchi, J.C.; Giacomini, R.C. Bio-Amplifier based on MOS bipolar Pseudo-Resistors: A New Approach using its non-linear characteristic. J. Integr. Circuits Syst. 2016, 11, 132–139. [Google Scholar] [CrossRef]

- Guglielmi, E.; Toso, F.; Zanetto, F.; Sciortino, G.; Mesri, A.; Sampietro, M.; Ferrari, G. High-value tunable pseudo-resistors design. IEEE J. Solid-State Circuits 2020, 55, 2094–2105. [Google Scholar] [CrossRef]

- Tajalli, A.; Leblebici, Y.; Brauer, E.J. Implementing ultra-high-value floating tunable CMOS resistors. Electron. Lett. 2008, 44, 349–351. [Google Scholar] [CrossRef]

- Djugova, A.; Radic, J.; Videnovic-Misic, M.; Nagy, L. Inverter-based low-noise amplifier topologies for ultra-wideband applications. In Proceedings of the 2013 2nd Mediterranean Conference on Embedded Computing (MECO), Budva, Montenegro, 15–20 June 2013; pp. 192–195. [Google Scholar]

- Bhatia, V.; Pandey, N.; Bhattacharyya, A. High speed power efficient CMOS inverter based current comparator in UMC 90 nm technology. Int. J. Electr. Comput. Eng. 2016, 6, 90. [Google Scholar]

- Sharroush, S.M. Design of the CMOS inverter-based amplifier: A quantitative approach. Int. J. Circuit Theory Appl. 2019, 47, 1006–1036. [Google Scholar] [CrossRef]

- Suadet, A.; Kasemsuwan, V. A CMOS inverter-based class-AB pseudo-differential amplifier with current-mode common-mode feedback (CMFB). Analog Integr. Circuits Signal Process. 2013, 74, 387–398. [Google Scholar] [CrossRef]

- Sharma, A.; Pal, T.; Jaiswal, V. Heart disease prediction using convolutional neural network. In Cardiovascular and Coronary Artery Imaging; Academic Press: Cambridge, MA, USA, 2022; pp. 245–272. [Google Scholar]

- Revathi, T.K.; Balasubramaniam, S.; Sureshkumar, V.; Dhanasekaran, S. An improved long short-term memory algorithm for cardiovascular disease prediction. Diagnostics 2024, 14, 239. [Google Scholar] [CrossRef]

- Kachuee, M.; Fazeli, S.; Sarrafzadeh, M. ECG heartbeat classification: A deep transferable representation. In Proceedings of the 2018 IEEE International Conference on Healthcare Informatics (ICHI), New York, NY, USA, 4–7 June 2018; pp. 443–444. [Google Scholar]

- Lee, C.J.; Song, J.I. A chopper-stabilized amplifier with a tunable bandwidth for EEG acquisition applications. IEEE Access 2019, 7, 73165–73171. [Google Scholar] [CrossRef]

- Verma, N.; Shoeb, A.; Bohorquez, J.; Dawson, J.; Guttag, J.; Chandrakasan, A.P. A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system. IEEE J. Solid-State Circuits 2010, 45, 804–816. [Google Scholar] [CrossRef]

- Sonkusare, R.; Joshi, O.; Rathod, S.S. SOI FinFET based instrumentation amplifier for biomedical applications. Microelectron. J. 2019, 91, 1–10. [Google Scholar] [CrossRef]

- Horestani, F.K.; Eshghi, M.; Yazdchi, M. An ultra-low power amplifier for wearable and implantable electronic devices. Microelectron. Eng. 2019, 216, 111054. [Google Scholar] [CrossRef]

- Fava, A.; Centurelli, F.; Monsurrò, P.; Scotti, G. A Compact Low-Power Chopper Low Noise Amplifier for High Density Neural Front-Ends. Sensors 2025, 25, 1157. [Google Scholar] [CrossRef]

- Fan, X.; Gao, F.; Chan, P.K. Design of a 0.5 V chopper-stabilized differential difference amplifier for analog signal processing applications. Sensors 2023, 23, 9808. [Google Scholar] [CrossRef]

- Chae, M.; Kim, J.; Liu, W. Fully-differential self-biased bio-potential amplifier. Electron. Lett. 2008, 44, 1390–1391. [Google Scholar] [CrossRef]

- Zhang, S.; Zhou, X.; Gao, C.; Li, Q. A 130-dB CMRR instrumentation amplifier with common-mode replication. IEEE J. Solid-State Circuits 2021, 57, 278–289. [Google Scholar] [CrossRef]

| Reference | Technology | Channel Length (nm) | Amplifier Gain (dB) | Bandwidth (kHz) | Supply Voltage (V) | Power (µW) | CMRR (dB) | NEF |

|---|---|---|---|---|---|---|---|---|

| [25] | CMOS | 180 | 47.6 | 0.5 | 1.5 | 0.85 | 105.6 | 2.91 |

| [26] | CMOS | 180 | 60 | -- | 1 | 0.33 | 60 | 11 |

| [27] | FinFET | 30 | 81.37 | -- | 1 | 388 | 127.6 | 9.63 |

| [28] | CMOS | 180 | 35 | 0.2 | ±0.6 | 0.64 | >100 | 9.11 |

| [29] | CMOS | 130 | 27–39 | 7.5 | 0.8 | 1.6 | 67 | 1.62 |

| [30] | CMOS | 40 | 89 | -- | 0.5 | 0.72 | 101 | 1.03 |

| [31] | CMOS | 350 | 40 | 20 | 3.3 | 6.7 | 90 | 1.8 |

| [32] | CMOS | 180 | 46–64 | -- | 1.8 | -- | >130 | 2.34 |

| [This Work] | FinFET | 14 | 42.6 | 0.61 | 0.9 | 0.92 | 106.9 | 6.1 |

| Component | Dimensions |

|---|---|

| M1, M2, M3, M4 | 1/450 nm (nfin/L) |

| M5, M6, M7, M8 | 1/1800 nm (nfin/L) |

| M10, M11 | 1/10 um (nfin/L) |

| M12, M13 | 1/68.8 um (nfin/L) |

| C1 | 3800 pF |

| C2 | 30 pF |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Farshori, M.A.; Nizamuddin, M.; Bheemana, R.C.; Prakash, K.; Bansal, S.; Zulqarnain, M.; Sharma, V.; Babu, S.S.; Kaur, K. Novel Tunable Pseudoresistor-Based Chopper-Stabilized Capacitively Coupled Amplifier and Its Machine Learning-Based Application. Micromachines 2025, 16, 1000. https://doi.org/10.3390/mi16091000

Farshori MA, Nizamuddin M, Bheemana RC, Prakash K, Bansal S, Zulqarnain M, Sharma V, Babu SS, Kaur K. Novel Tunable Pseudoresistor-Based Chopper-Stabilized Capacitively Coupled Amplifier and Its Machine Learning-Based Application. Micromachines. 2025; 16(9):1000. https://doi.org/10.3390/mi16091000

Chicago/Turabian StyleFarshori, Mohammad Aleem, M. Nizamuddin, Renuka Chowdary Bheemana, Krishna Prakash, Shonak Bansal, Mohammad Zulqarnain, Vipin Sharma, S. Sudhakar Babu, and Kanwarpreet Kaur. 2025. "Novel Tunable Pseudoresistor-Based Chopper-Stabilized Capacitively Coupled Amplifier and Its Machine Learning-Based Application" Micromachines 16, no. 9: 1000. https://doi.org/10.3390/mi16091000

APA StyleFarshori, M. A., Nizamuddin, M., Bheemana, R. C., Prakash, K., Bansal, S., Zulqarnain, M., Sharma, V., Babu, S. S., & Kaur, K. (2025). Novel Tunable Pseudoresistor-Based Chopper-Stabilized Capacitively Coupled Amplifier and Its Machine Learning-Based Application. Micromachines, 16(9), 1000. https://doi.org/10.3390/mi16091000