Design Strategies for Optimized Bulk-Linearized MOS Pseudo-Resistor

Abstract

1. Introduction

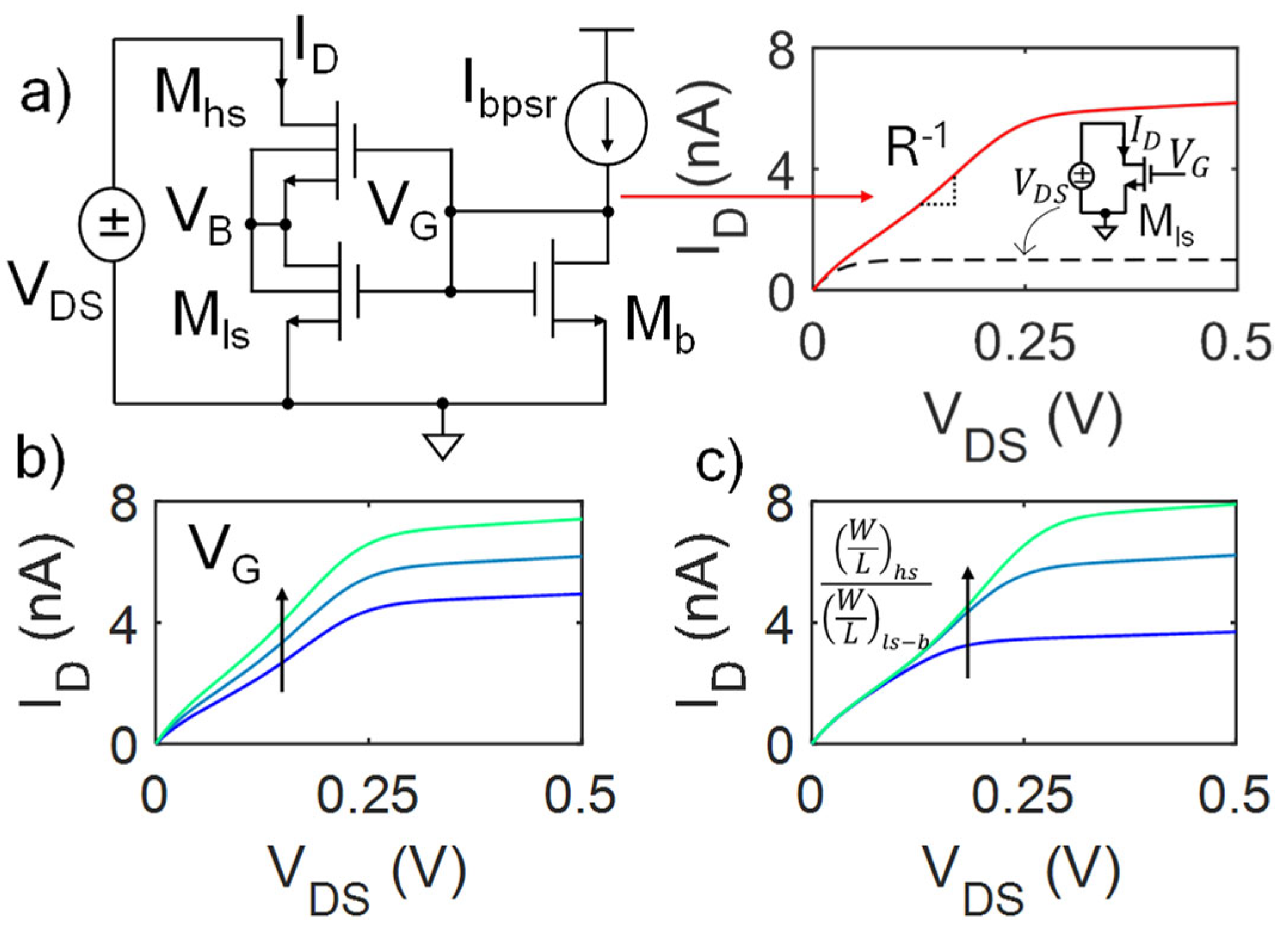

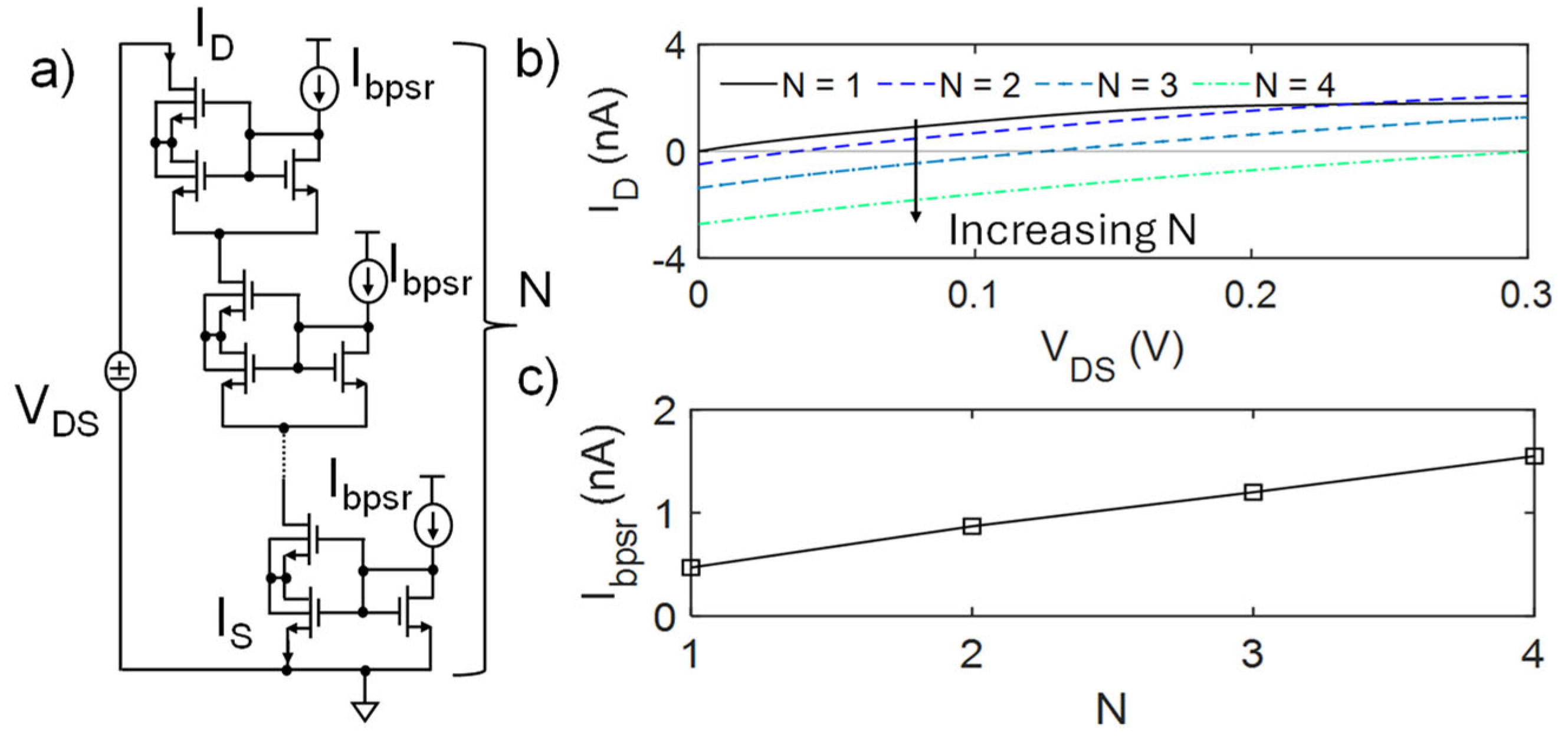

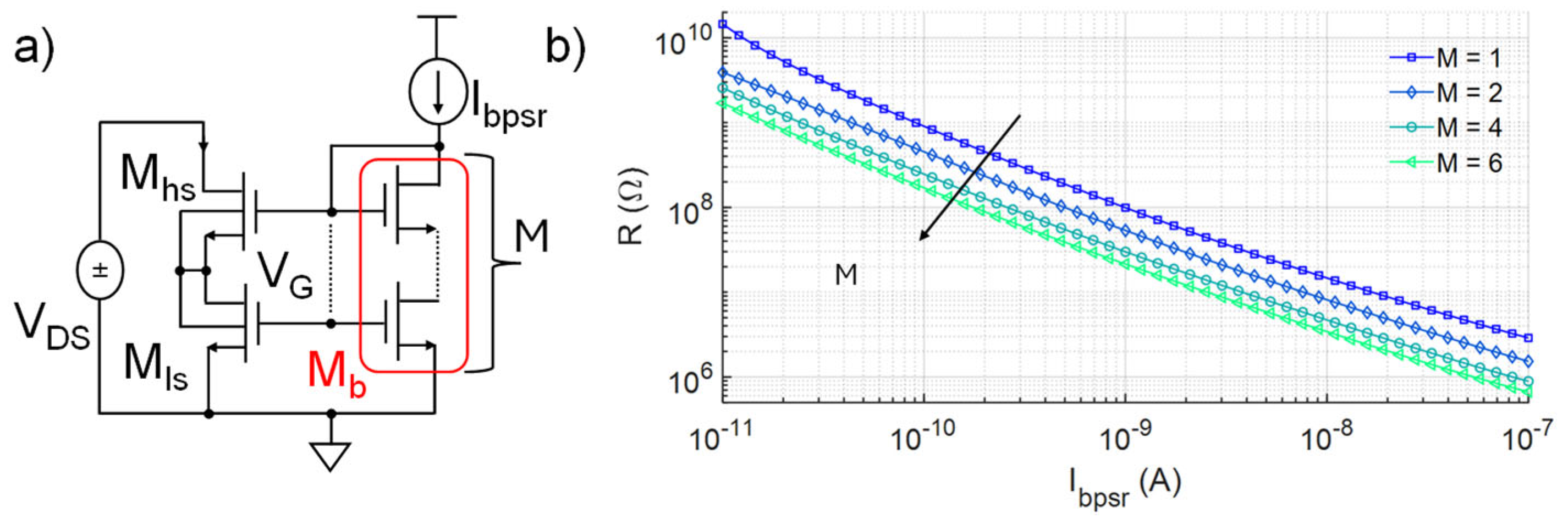

2. Methods

3. Results

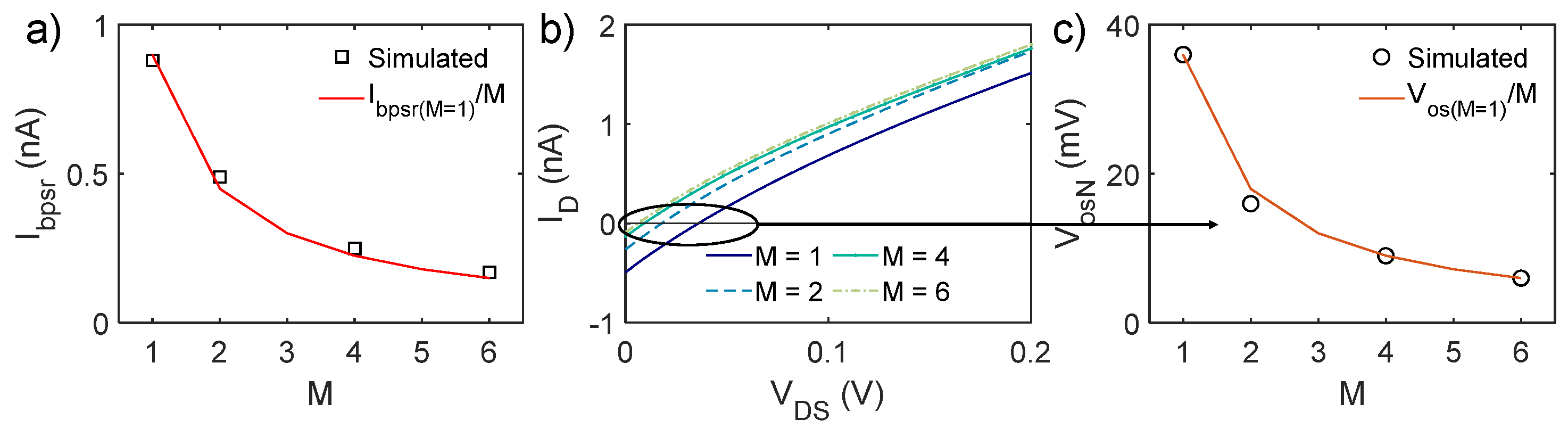

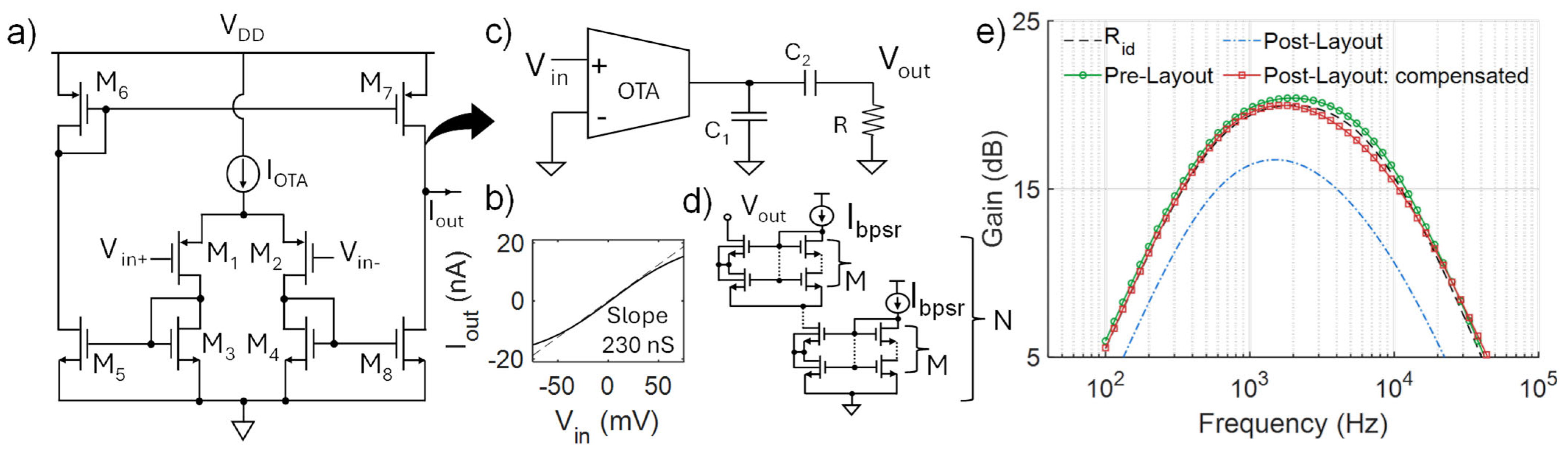

3.1. Power Consumption

3.2. Offset Reduction

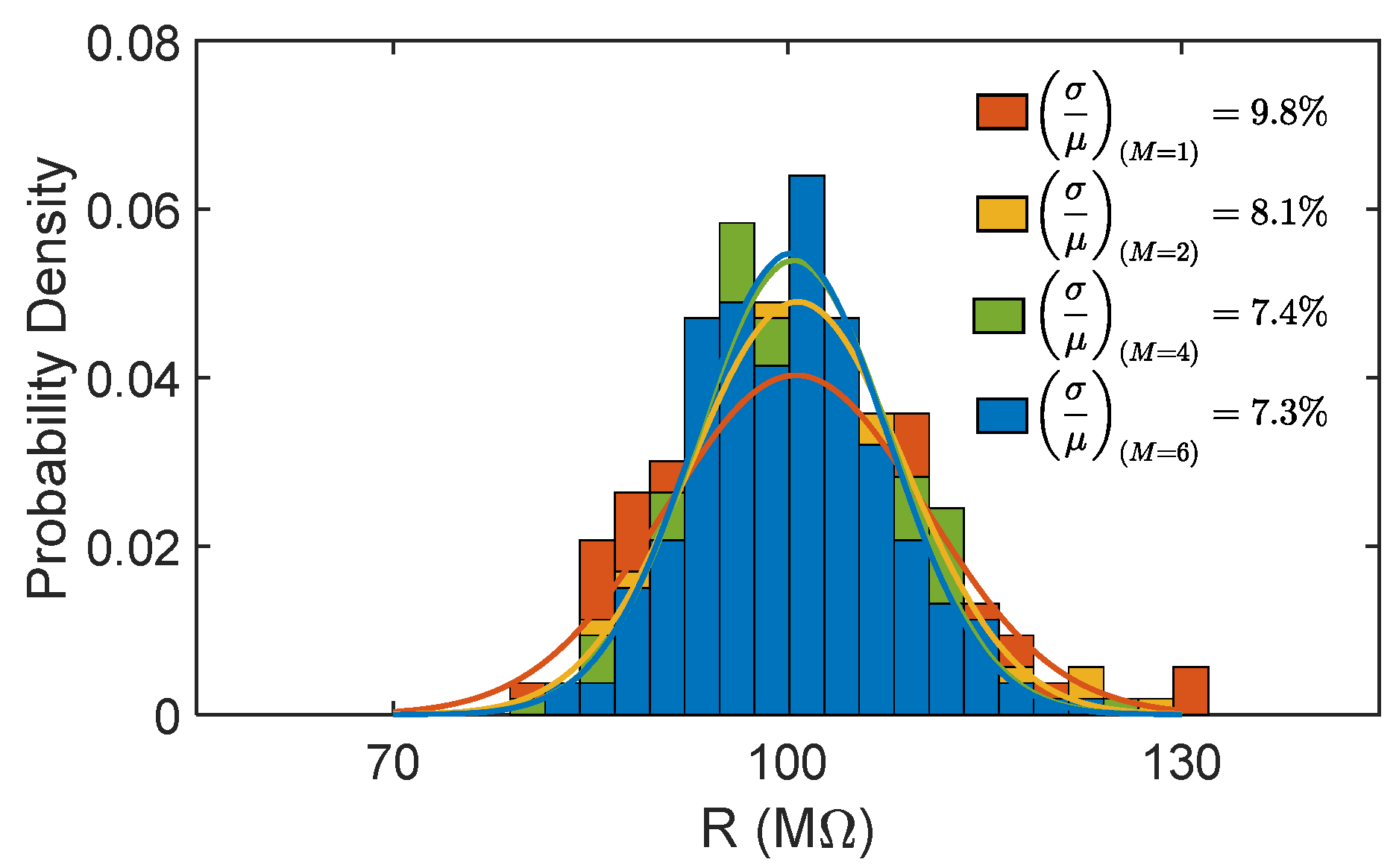

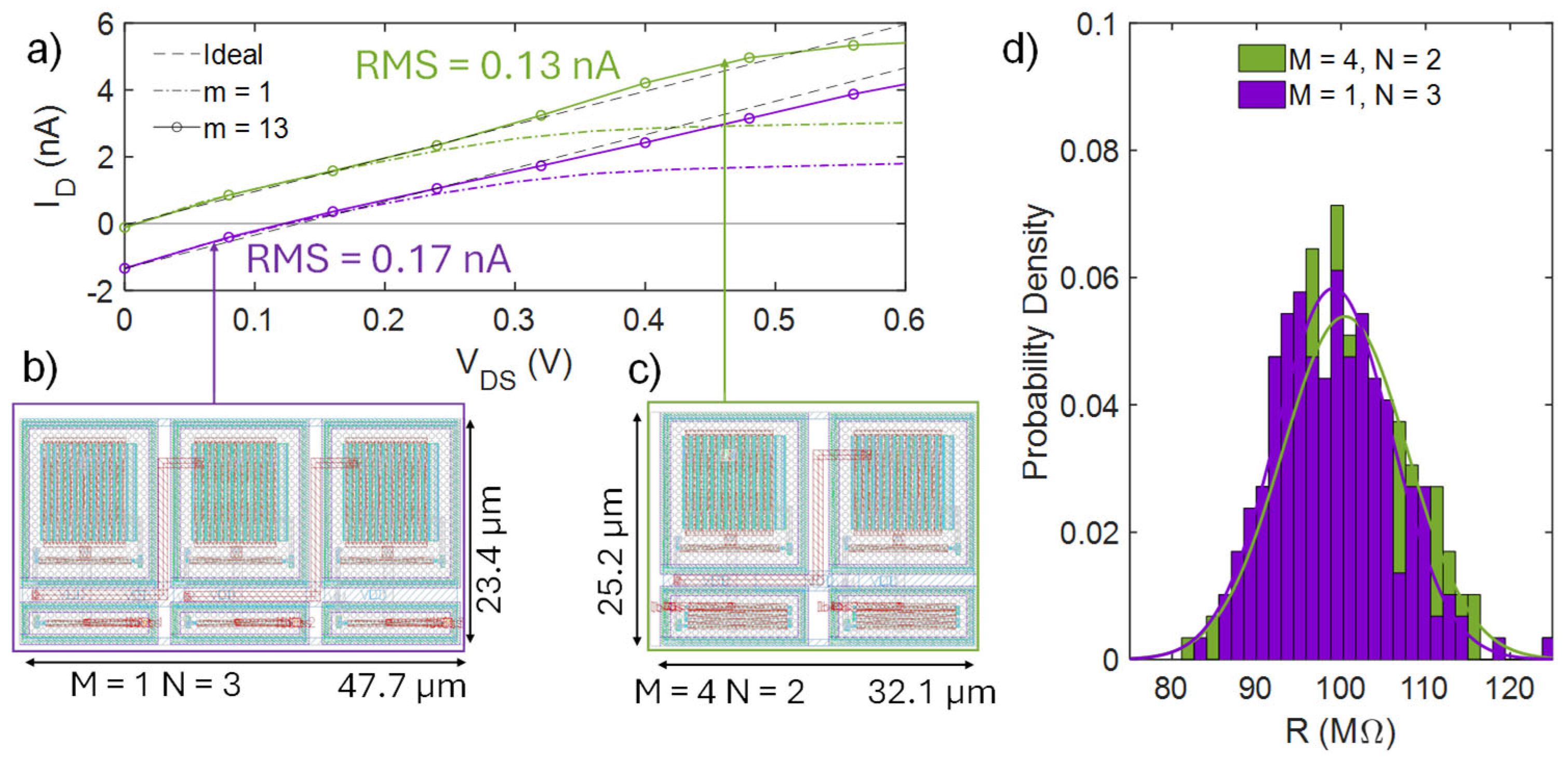

3.3. Process Variations/Mismatch

3.4. Area Occupation

- The sum of the bias current drops from 3.6 nA to 400 pA (−89%), since now each PSR element should exhibit a higher R (lower Ibpsr) to keep the overall R unchanged;

- The offset voltage drops from 120 mV to 9 mV (−92.5%) because of the lower Ibpsr;

- The total area occupation drops from 1116 µm2 to 809 µm2 (−27.5%) since fewer PSR elements are employed;

- The −3 dB bandwidth (BW) increases from 6 kHz to 10.5 kHz (+75%).

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| BL | Bulk-linearized/Bulk Linearization |

| PSR | Pseudo-resistor |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| PVM | Process/Variation Mismatch |

| OTA | Operational Transconductance Amplifier |

| FOM | Figure of Merit |

| THD | Total Harmonic Distortion |

References

- Zhou, Z.; Liao, H.; Zhu, L.; Liu, Y.; Zhu, L.; Wang, K.; Wang, Z. A Bootstrapped Pseudo Resistor by Reusing OTA-C Filter for Neural Signal Processing. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 714–718. [Google Scholar] [CrossRef]

- Gonzalez-Diaz, V.R. On-Chip Active Filter for Electrocardiographic Signals Through CMOS Pseudo Resistors. IEEE Trans. Circuits Syst. II Express Briefs 2025, 72, 883–887. [Google Scholar] [CrossRef]

- Chen, X.; Yajima, T.; Inoue, I.H.; Iizuka, T. An ultra-compact leaky integrate-and-fire neuron with long and tunable time constant utilizing pseudo resistors for spiking neural networks. Jpn. J. Appl. Phys. 2022, 61, SC1051. [Google Scholar] [CrossRef]

- Djekic, D.; Haberle, M.; Mohamed, A.; Baumgartner, L.; Anders, J. A 440-kOhm to 150-GOhm Tunable Transimpedance Amplifier based on Multi-Element Pseudo-Resistors. In Proceedings of the ESSCIRC 2021—IEEE 47th European Solid State Circuits Conference, Grenoble, France, 13–22 September 2021. [Google Scholar] [CrossRef]

- Djekic, D.; Fantner, G.; Lips, K.; Ortmanns, M.; Anders, J. A 0.1% THD, 1-M Ω to 1-G Ω Tunable, Temperature-Compensated Transimpedance Amplifier Using a Multi-Element Pseudo-Resistor. IEEE J. Solid-State Circuits 2018, 53, 1913–1923. [Google Scholar] [CrossRef]

- Puddu, R.; Carboni, C.; Bisoni, L.; Barabino, G.; Pani, D.; Raffo, L.; Barbaro, M. A Precision Pseudo Resistor Bias Scheme for the Design of Very Large Time Constant Filters. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 762–766. [Google Scholar] [CrossRef]

- Guglielmi, E.; Toso, F.; Zanetto, F.; Sciortino, G.; Mesri, A.; Sampietro, M.; Ferrari, G. High-value tunable pseudo-resistors design. IEEE J. Solid-State Circuits 2020, 55, 2094–2105. [Google Scholar] [CrossRef]

- Rueda-Diaz, J.M.; Bolzan, E.; Fernandes, T.D.; Schneider, M.C. Tunable CMOS Pseudo-Resistors for Resistances of Hundreds of GΩ. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 657–667. [Google Scholar] [CrossRef]

- Arnaud, A.; Miguez, M. Bulk linearisation of the MOS resistor. Electron. Lett. 2018, 54, 1106–1108. [Google Scholar] [CrossRef]

- Arnaud, A.; Puyol, R.; Chacon-Rodriguez, A.; Miguez, M.; Gak, J. An asymmetrical bulk-modified composite MOS transistor with enhanced linearity. In Proceedings of the 2019 IEEE 10th Latin American Symposium on Circuits and Systems, LASCAS 2019, Armenia, Colombia, 24–27 February 2019. [Google Scholar] [CrossRef]

- Costa, D.; Arnaud, A.; Gak, J.; Miguez, M. Enhancing an OTA Linearity Through Bulk Degeneration: A Comparative Analysis. In Proceedings of the 2024 IEEE 15th Latin America Symposium on Circuits and Systems (LASCAS), Punta del Este, Uruguay, 27 February–1 March 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Zanotti, T.; Ranjan, A.; O’Shea, S.J.; Raghavan, N.; Thamankar, R.; Pey, K.L.; Puglisi, F.M. Guidelines for the Design of Random Telegraph Noise-Based True Random Number Generators. IEEE Trans. Device Mater. Reliab. 2024, 24, 184–193. [Google Scholar] [CrossRef]

- Djekic, D.; Fantner, G.; Behrends, J.; Lips, K.; Ortmanns, M.; Anders, J. A transimpedance amplifier using a widely tunable PVT-independent pseudo-resistor for high-performance current sensing applications. In Proceedings of the ESSCIRC 2017—43rd IEEE European Solid State Circuits Conference, Leuven, Belgium, 11–14 September 2017. [Google Scholar] [CrossRef]

- Brezeanu, M.; Rusu, A.; Dobrescu, L. MOS channel length modulation in weak inversion. In Proceedings of the International Semiconductor Conference, Sinaia, Romania, 8–12 October 2002. [Google Scholar] [CrossRef]

- Enz, C.C.; Krummenacher, F.; Vittoz, E.A. An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Analog. Integr. Circuits Signal Process 1995, 8, 83–114. [Google Scholar] [CrossRef]

- Drennan, P.G.; McAndrew, C.C. Understanding MOSFET mismatch for analog design. IEEE J. Solid-State Circuits 2003, 38, 450–456. [Google Scholar] [CrossRef]

- Wang, T.Y.; Lai, M.R.; Twigg, C.M.; Peng, S.Y. A fully reconfigurable low-noise biopotential sensing amplifier with 1.96 noise efficiency factor. IEEE Trans. Biomed. Circuits Syst. 2014, 8, 411–422. [Google Scholar] [CrossRef] [PubMed]

- Han, D.; Zheng, Y.; Rajkumar, R.; Dawe, G.S.; Je, M. A 0.45 v 100-channel neural-recording IC with sub-μW/Channel Consumption in 0.18 μ CMOS. IEEE Trans. Biomed. Circuits Syst. 2013, 7, 735–746. [Google Scholar] [CrossRef] [PubMed]

- Kim, S.J.; Liu, L.; Yao, L.; Goh, W.L.; Gao, Y.; Je, M. A 0.5-V sub-μW/channel neural recording IC with delta-modulation-based spike detection. In Proceedings of the 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), KaoHsiung, Taiwan, 10–12 November 2014. [Google Scholar] [CrossRef]

| This Work a | [9] a | [5] b | [8] b | [7] b | [6] b | ||

|---|---|---|---|---|---|---|---|

| BL | yes | Yes | no | No | No | No | |

| Tech. (nm) | 130 | 130 | 180-SOI | 180 | 350 | 350 | |

| Rmin | 1 MΩ | 1 MΩ | 1 MΩ | 180 GΩ | 20 MΩ | 500 MΩ | |

| Rmax | 1 GΩ | 1 GΩ | 1 GΩ | 700 GΩ | 20 GΩ | 70 GΩ | |

| BW @Rmin | 1.3 MHz | 380 kHz | 2 MHz | 100 Hz | 10 MHz | 8 kHz | |

| BW @Rmax | 1.3 kHz | 650 Hz | 8 kHz | 3 Hz | 100 kHz | 0 | |

| Supply | 1 V | 1 V | 1.8 V | 1.8 V | 3.3 V | 3.3 V | |

| Power (nW) | N = 2 | N = 2 | N = 3 | 200k | 5.4 | 100 | 2000 |

| 0.4 * | 2 ** | 3.6 ** | |||||

| Offset (mV) | 9 * | 36 ** | 120 ** | - | - | - | - |

| σ/µ (%) | 7.4 * | 9.8 ** | 7.4 ** | 3.6 | 2.53 | 25.5 | 13 |

| Area (µm2) | 809 * | 730 ** | 1116 ** | 16k | 16.5k | 17.7k | 54k |

| FOM | 2.1 * | 2.6 ** | 2.5 ** | 4.6 | 3.2 | 34 | 30 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Benatti, L.; Zanotti, T.; Puglisi, F.M. Design Strategies for Optimized Bulk-Linearized MOS Pseudo-Resistor. Micromachines 2025, 16, 941. https://doi.org/10.3390/mi16080941

Benatti L, Zanotti T, Puglisi FM. Design Strategies for Optimized Bulk-Linearized MOS Pseudo-Resistor. Micromachines. 2025; 16(8):941. https://doi.org/10.3390/mi16080941

Chicago/Turabian StyleBenatti, Lorenzo, Tommaso Zanotti, and Francesco Maria Puglisi. 2025. "Design Strategies for Optimized Bulk-Linearized MOS Pseudo-Resistor" Micromachines 16, no. 8: 941. https://doi.org/10.3390/mi16080941

APA StyleBenatti, L., Zanotti, T., & Puglisi, F. M. (2025). Design Strategies for Optimized Bulk-Linearized MOS Pseudo-Resistor. Micromachines, 16(8), 941. https://doi.org/10.3390/mi16080941