The Impact of Single-Event Radiation on Latch-Up Effect in High-Temperature CMOS Devices and Its Mechanism

Abstract

1. Introduction

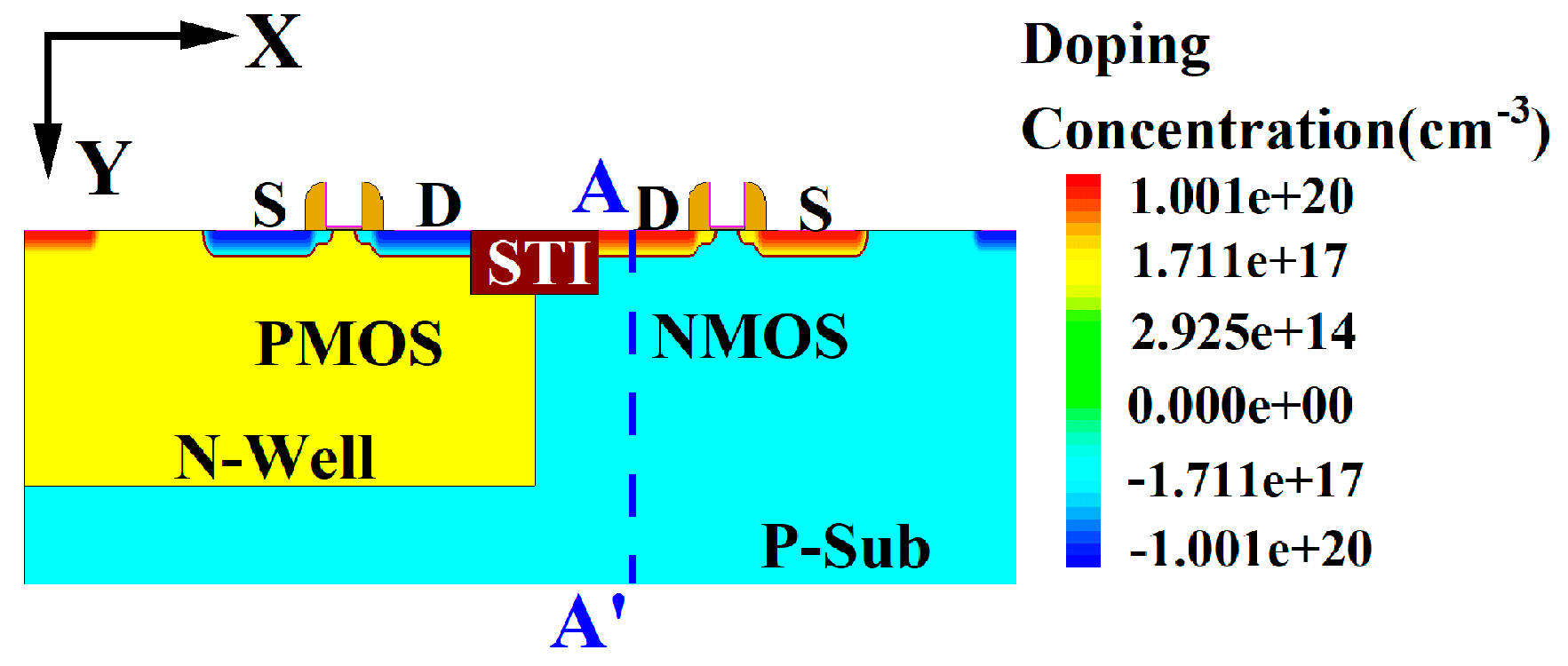

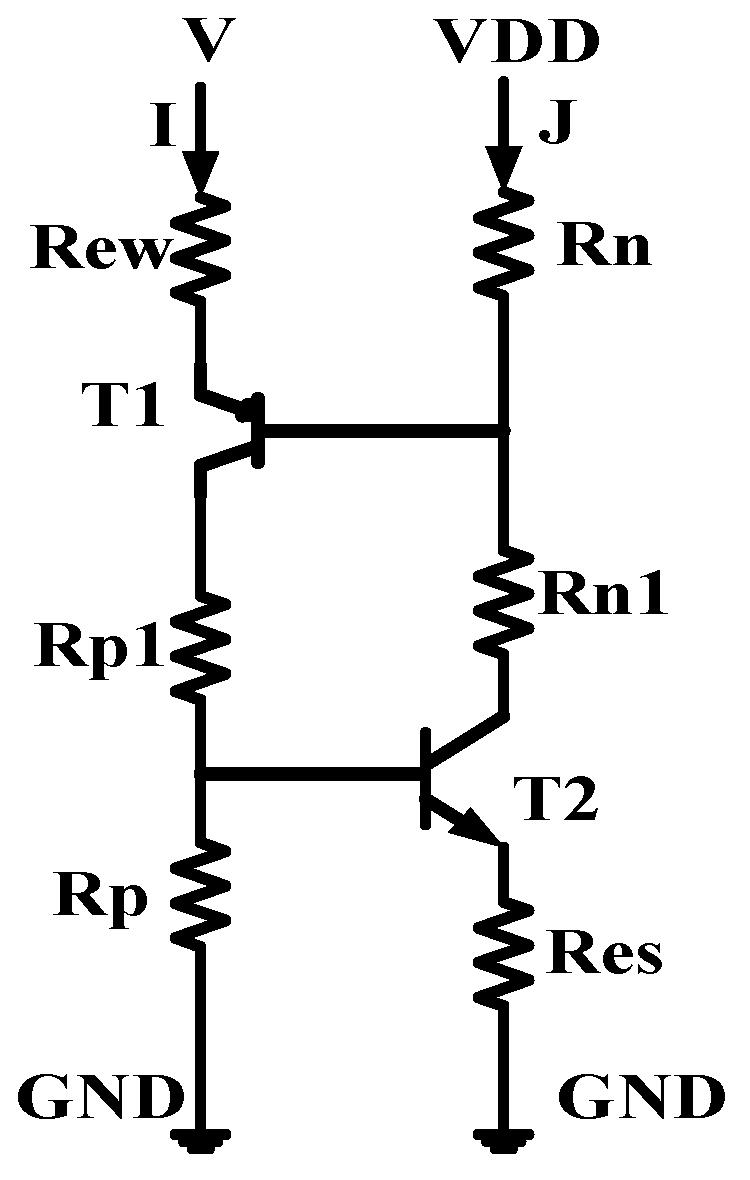

2. Device Parameters and Model Establishment

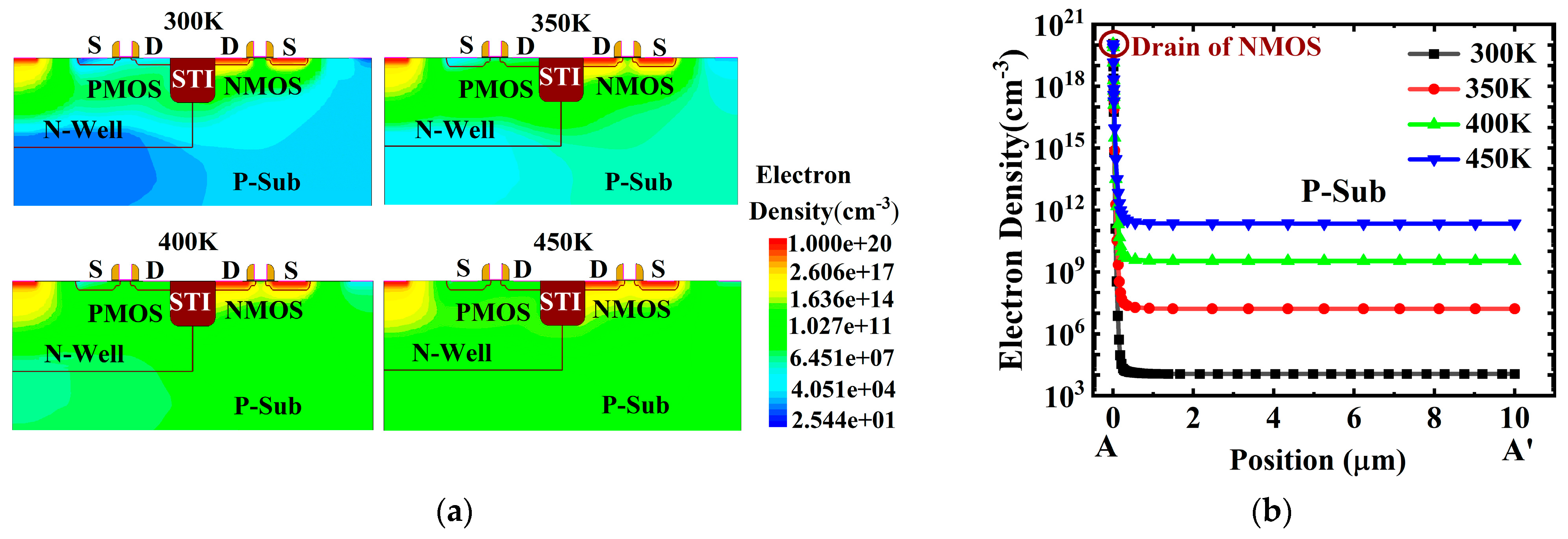

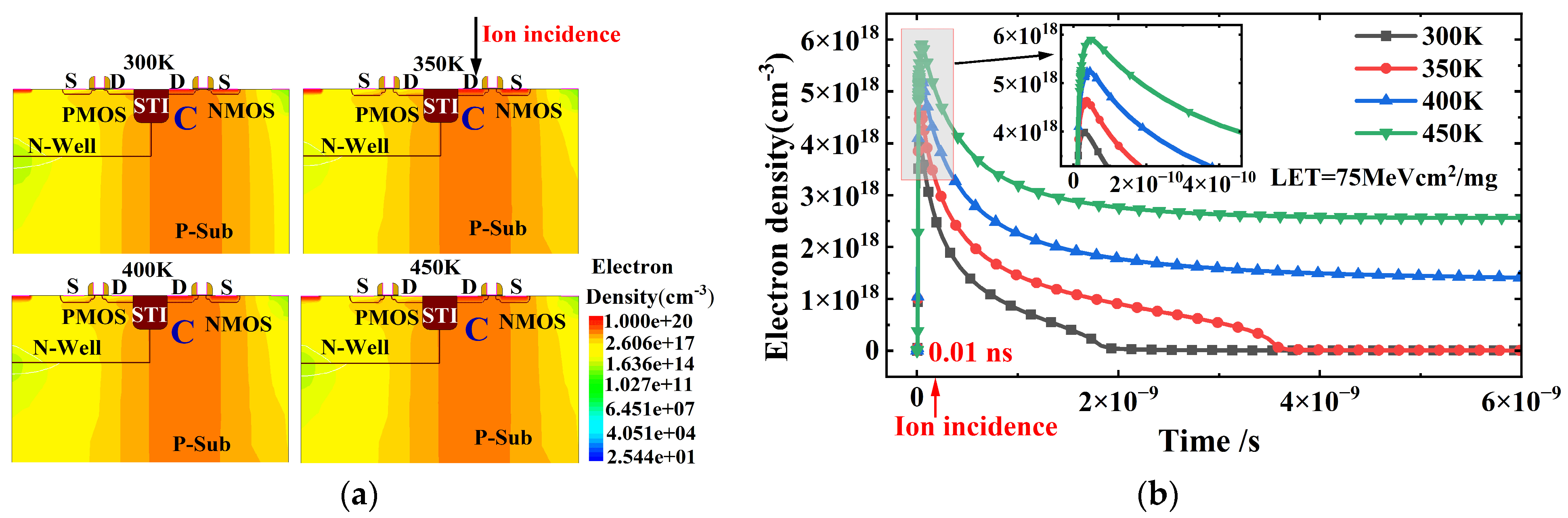

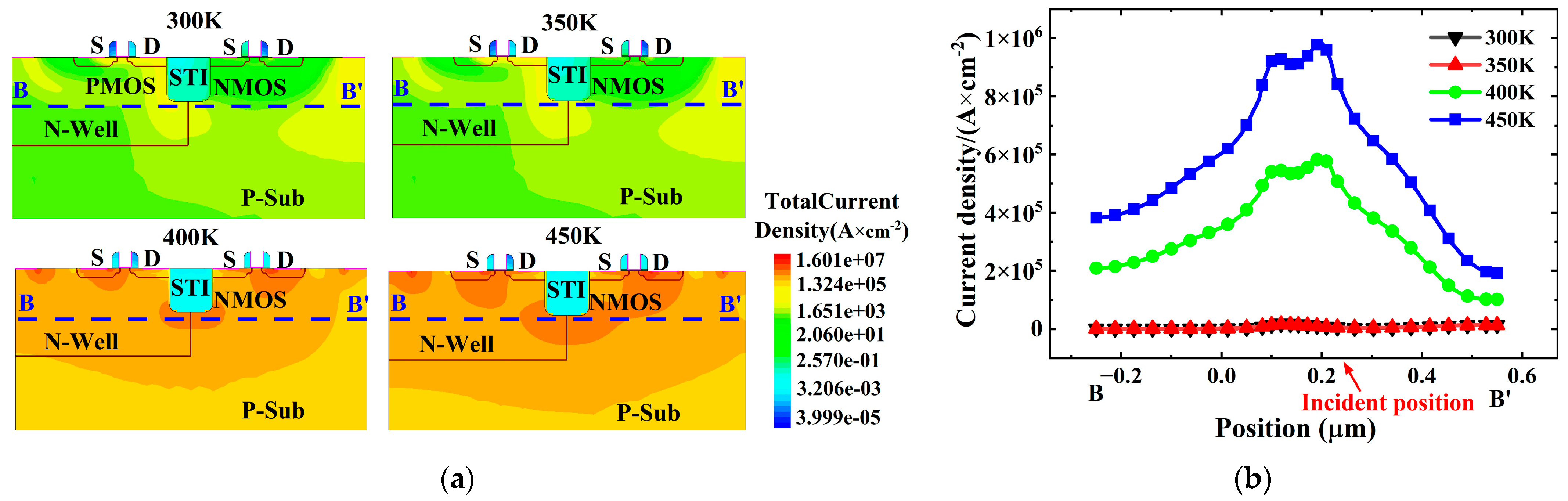

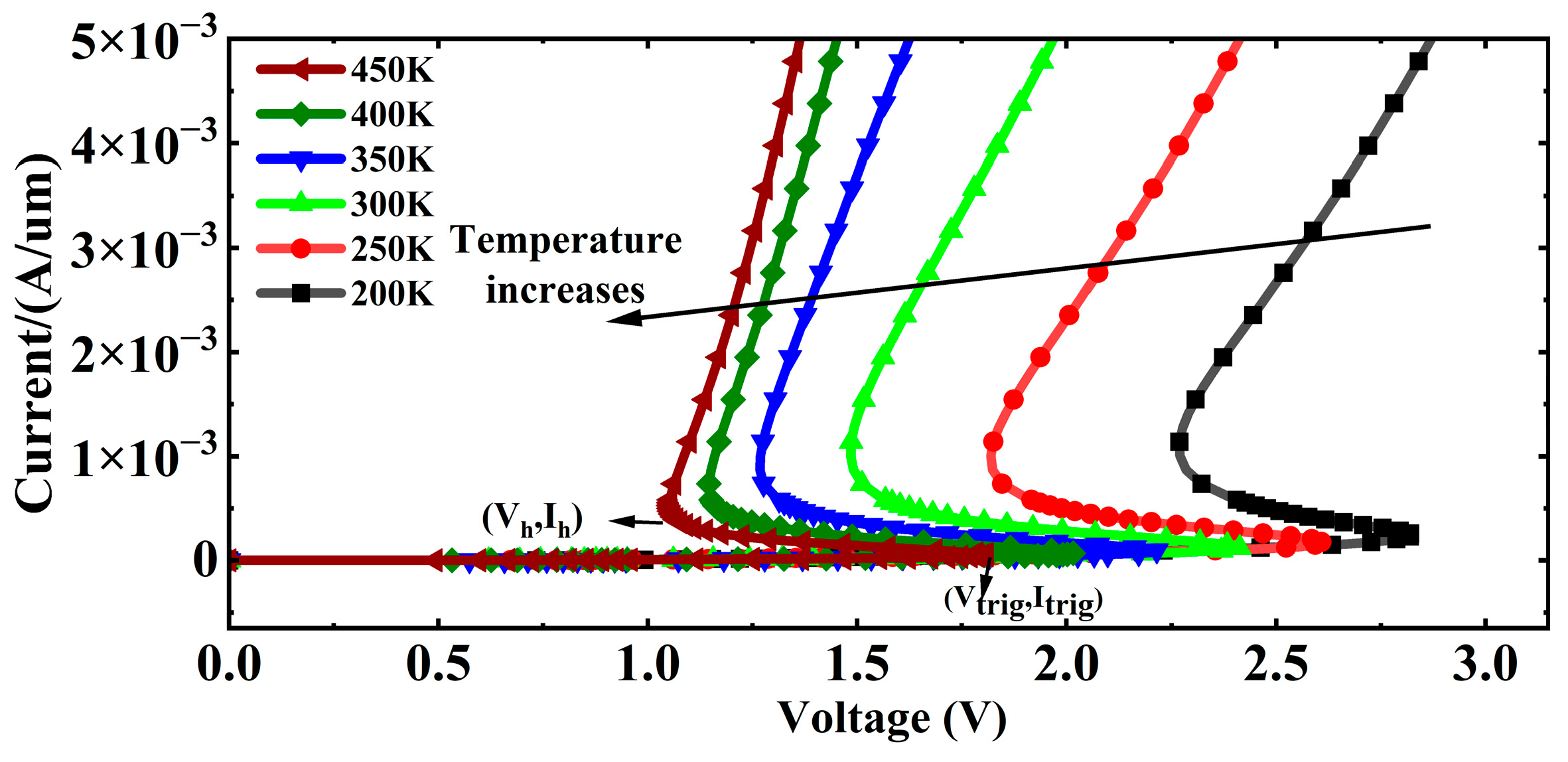

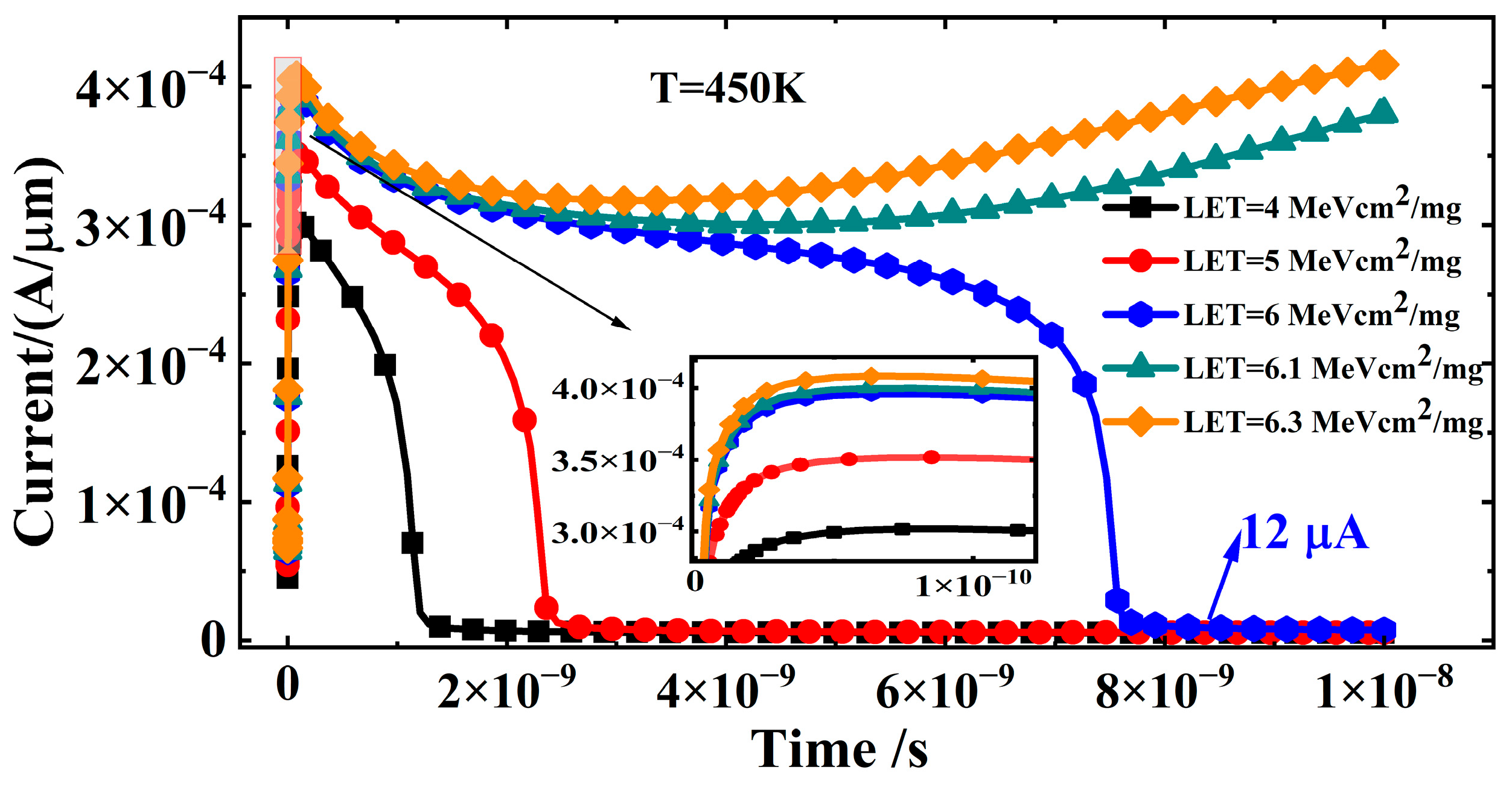

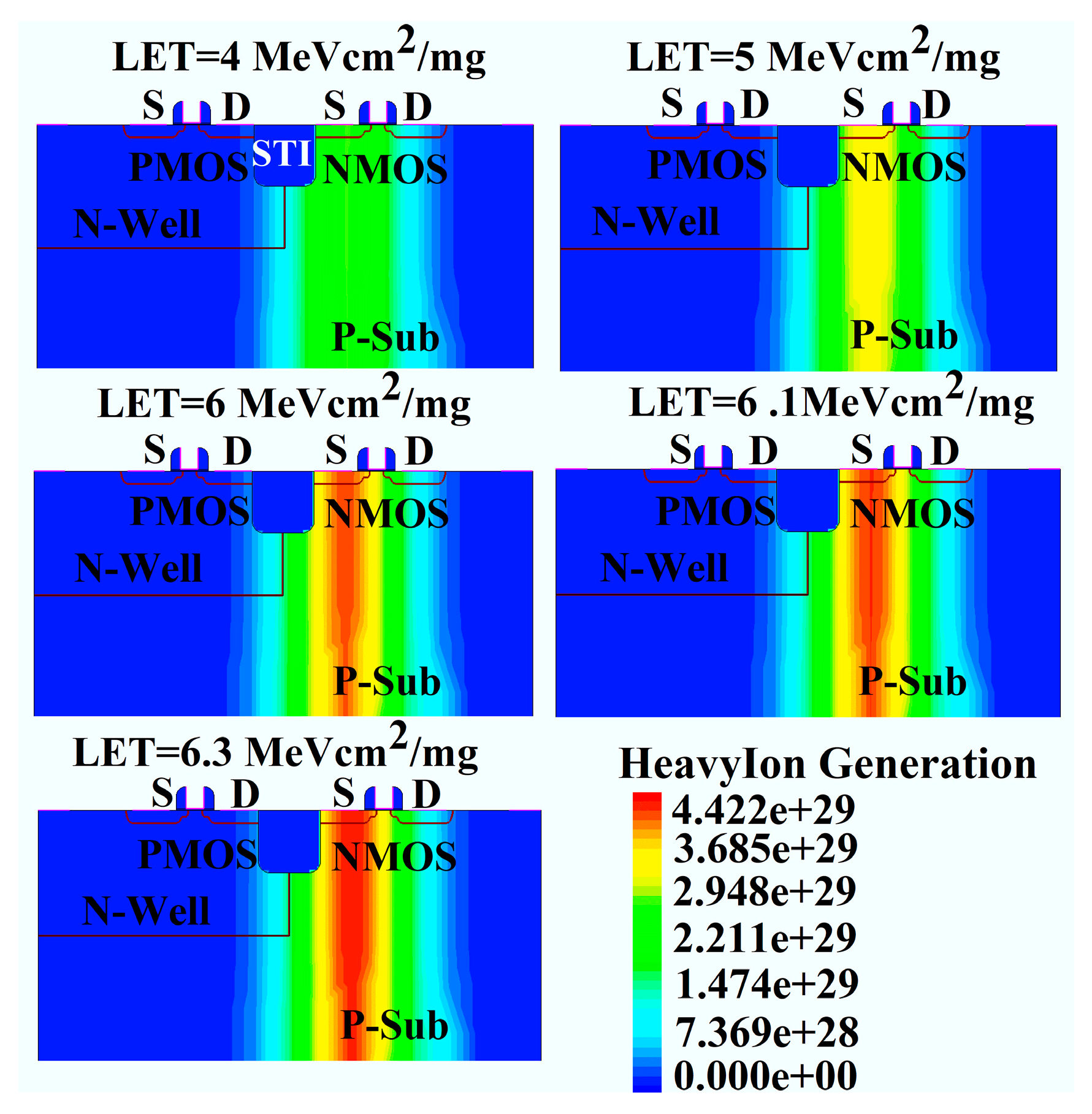

3. Simulation Results and Analysis

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Ning, X.W.; Li, J.D.; Wang, Y.Y.; Jiang, F. Review on construction of new spacecraft thermal control system in China. Acta Aeronaut. Tronautica Sin. 2019, 40, 022874. [Google Scholar] [CrossRef]

- Marshall, C.J.; Marshall, P.W.; Ladbury, R.L.; Waczynski, A.; Arora, R.; Foltz, R.D.; Cressler, J.D.; Kahle, D.M.; Chen, D.; Delo, G.S.; et al. Mechanisms and Temperature Dependence of Single Event Latchup Observed in a CMOS Readout Integrated Circuit from 16–300 K. IEEE Trans. Nucl. Sci. 2010, 57, 3078–3086. [Google Scholar] [CrossRef]

- Al Youssef, A.; Artola, L.; Ducret, S.; Hubert, G.; Perrier, F. Investigation of Electrical Latchup and SEL Mechanisms at Low Temperature for Applications Down to 50 K. IEEE Trans. Nucl. Sci. 2017, 64, 2089–2097. [Google Scholar] [CrossRef]

- Youssef, A.A.; Artola, L.; Ducret, S.; Hubert, G.; Perrier, F. Analysis of low temperature on single event Latchup mechanisms by TCAD simulations for applications down to 50K. In Proceedings of the 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Bremen, Germany, 19–23 September 2016; pp. 1–5. [Google Scholar] [CrossRef]

- Deferm, L.; Simoen, E.; Dierickx, B.; Claeys, C. Anomalous latch-up behavior of CMOS at liquid helium temperatures. Cryogenics 1990, 30, 1051–1055. [Google Scholar] [CrossRef]

- Serbulova, K.; Qiu, S.Z.-N.; Chen, A.; Grill, K.; Kao, K.-H.; Boeck, J.D.; Groeseneken, G. Insight into Latchup Risk in 28nm Planar Bulk Technology for Quantum Computing Applications. In Proceedings of the 2024 IEEE International Reliability Physics Symposium (IRPS), Grapevine, TX, USA, 14–18 April 2024; pp. 1–7. [Google Scholar] [CrossRef]

- Yao, C.; Thou, J.; Cheung, R.; Chan, H. Temperature Dependence of CMOS Device Reliability. In Proceedings of the 24th International Reliability Physics Symposium, Anaheim, CA, USA, 1–3 April 1986; pp. 175–182. [Google Scholar] [CrossRef]

- Dooley, J.G.; Jaeger, R.C. Temperature dependence of latchup in CMOS circuits. IEEE Electron Device Lett. 1984, 5, 41–43. [Google Scholar] [CrossRef]

- Sangiorgi, E.; Johnston, R.L.; Pinto, M.R.; Bechtold, P.F.; Fichtner, W. Temperature dependence of latch-up phenomena in scaled CMOS structures. IEEE Electron Device Lett. 1986, 7, 28–31. [Google Scholar] [CrossRef]

- Yao, C.C.; Tzou, J.J.; Cheung, R.; Chan, H. Temperature dependence of latch-up characteristics in LDD CMOS devices. IEEE Electron Device Lett. 1986, 7, 92–94. [Google Scholar] [CrossRef]

- Liang, W.; Dong, A.; Li, H.; Miao, M.; Liou, J.J.; Kuo, C.-C.; Klebanov, M. Characteristics of ESD protection devices operated under elevated temperatures. In Proceedings of the 2016 IEEE International Nanoelectronics Conference (INEC), Chengdu, China, 9–11 May 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Johnston, A.H.; Hughlock, B.W.; Baze, M.P.; Plaag, R.E. The effect of temperature on single-particle latchup. IEEE Trans. Nucl. Sci. 1991, 38, 1435–1441. [Google Scholar] [CrossRef]

- Iwata, H.; Ohzone, T. Numerical simulation of single event latchup in the temperature range of 77–450 K. IEEE Trans. Nucl. Sci. 1995, 42, 148–154. [Google Scholar] [CrossRef]

- Guagliardo, S.; Wrobel, F.; Aguiar, Y.Q.; Autran, J.L.; Leroux, P.; Saigné, F.; Pouget, V.; Touboul, A.D. Effect of Temperature on Single Event Latchup Sensitivity. In Proceedings of the 2020 15th Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Marrakech, Morocco, 1–3 April 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Mrozovskaya, E.V.; Chubunov, P.A.; Iakovlev, S.; Zebrev, G.I. Investigation and Simulation of SEL Cross Sections at Different Temperatures. IEEE Trans. Nucl. Sci. 2022, 69, 1587–1592. [Google Scholar] [CrossRef]

- Chiang, T.-H.; Huang, C.-Y.; Lin, W.-J.; Lee, J.-W.; Chen, K.-J.; Song, M.-H. Single Event Latch-up (SEL) Rate Prediction Methodology in Bulk FinFET Technology. In Proceedings of the 2024 46th Annual EOS/ESD Symposium (EOS/ESD), Reno, NV, USA, 1–3 April 2024; pp. 1–6. [Google Scholar] [CrossRef]

- Fang, R.C.-Y.; Moll, J.L. Latchup model for the parasiticp-n-p-n path in bulk CMOS. IEEE Trans. Electr. Dev. 1984, 31, 113–120. [Google Scholar] [CrossRef]

- Bruguier, G.; Palau, J.-M. Single particle-induced latchup. IEEE Trans. Nucl. Sci. 1996, 43, 522–532. [Google Scholar] [CrossRef]

- Jiang, M.; Fu, G.; Wan, B.; Jia, M.; Qiu, Y. Research on single event latch-up effect of CMOS based on TCAD. In Proceedings of the 2017 Second International Conference on Reliability Systems Engineering (ICRSE), Beijing, China, 10–12 July 2017; pp. 1–5. [Google Scholar] [CrossRef]

- Sangiorgi, E.C.; Pinto, M.R. Two-Dimensional Numerical Analysis of Latchup in a VLSI CMOS Technology. IEEE Trans Comput.-Aided Des. 1985, 4, 561–574. [Google Scholar] [CrossRef]

- TCAD Sentaurus User Guide; Synop. Inc.: Mountain View, CA, USA, 2022.

- Tiwari, S.; Saha, R.; Gopal, G.; Varma, T. Sensitivity Analysis of Ge Source Double Gate TFET Under Heavy Ion Irradiation. IEEE Sens. J. 2024, 24, 36730–36736. [Google Scholar] [CrossRef]

- Maurya, A.; Koley, K.; Kumar, J.; Kumar, P. Investigation of single-event-transient effects induced by heavy-ion in all-silicon DG-TFET. IEEE Access 2022, 10, 109357–109365. [Google Scholar] [CrossRef]

- Wang, Y.; He, X.-W.; Shan, C. A simulation study of SOI like bulk silicon MOSFET with improved performance. IEEE Trans. Electron Dev. 2014, 61, 3339–3344. [Google Scholar] [CrossRef]

| Parameters | Values |

|---|---|

| Length of gate | 28 nm |

| Source doping concentration | 1 × 1020 cm−3 |

| Drain doping concentration | 1 × 1020 cm−3 |

| LDD concentration | 1 × 1019 cm−3 |

| N-Well concentration | 1 × 1018 cm−3 |

| P-Sub concentration | 1 × 1016 cm−3 |

| Thickness of gate SiO2 | 1 nm |

| Thickness of gate HfO2 | 3 nm |

| Junction depth | 20 nm |

| Thickness of silicon | 10 um |

| Thickness of N-Well | 200 nm |

| Temperature (K) | Itrig (A/μm) | Vtrig (V) | Vh (V) | Ih (A/μm) |

|---|---|---|---|---|

| 450 | 4.65 × 10−5 | 1.81 | data | 4.02 × 10−4 |

| 400 | 6.85 × 10−5 | 2.02 | 1.18 | 5.75 × 10−4 |

| 350 | 9.14 × 10−5 | 2.21 | 1.27 | 7.28 × 10−4 |

| 300 | 1.18 × 10−4 | 2.41 | 1.48 | 9.15 × 10−4 |

| 250 | 1.72 × 10−4 | 2.60 | 1.82 | 1.03 × 10−3 |

| 200 | 2.47 × 10−4 | 2.82 | 2.26 | 1.21 × 10−3 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, B.; Cui, J.; Lv, L.; Wu, L. The Impact of Single-Event Radiation on Latch-Up Effect in High-Temperature CMOS Devices and Its Mechanism. Micromachines 2025, 16, 783. https://doi.org/10.3390/mi16070783

Wang B, Cui J, Lv L, Wu L. The Impact of Single-Event Radiation on Latch-Up Effect in High-Temperature CMOS Devices and Its Mechanism. Micromachines. 2025; 16(7):783. https://doi.org/10.3390/mi16070783

Chicago/Turabian StyleWang, Bin, Jianguo Cui, Ling Lv, and Longsheng Wu. 2025. "The Impact of Single-Event Radiation on Latch-Up Effect in High-Temperature CMOS Devices and Its Mechanism" Micromachines 16, no. 7: 783. https://doi.org/10.3390/mi16070783

APA StyleWang, B., Cui, J., Lv, L., & Wu, L. (2025). The Impact of Single-Event Radiation on Latch-Up Effect in High-Temperature CMOS Devices and Its Mechanism. Micromachines, 16(7), 783. https://doi.org/10.3390/mi16070783