Design and Implementation of 24-GHz and 48-GHz VCOs Using Noise Filtering Technique in 90-nm CMOS

Abstract

1. Introduction

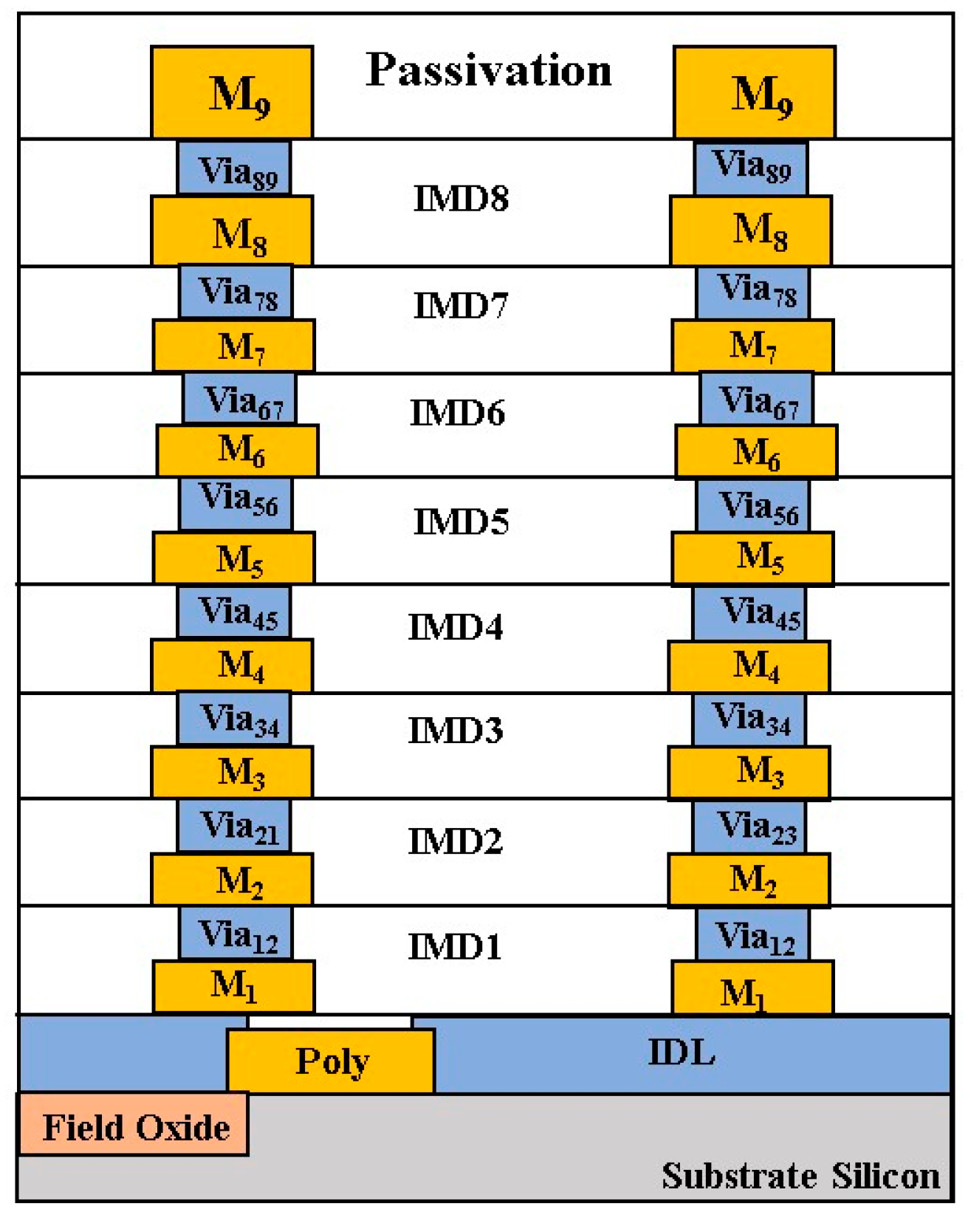

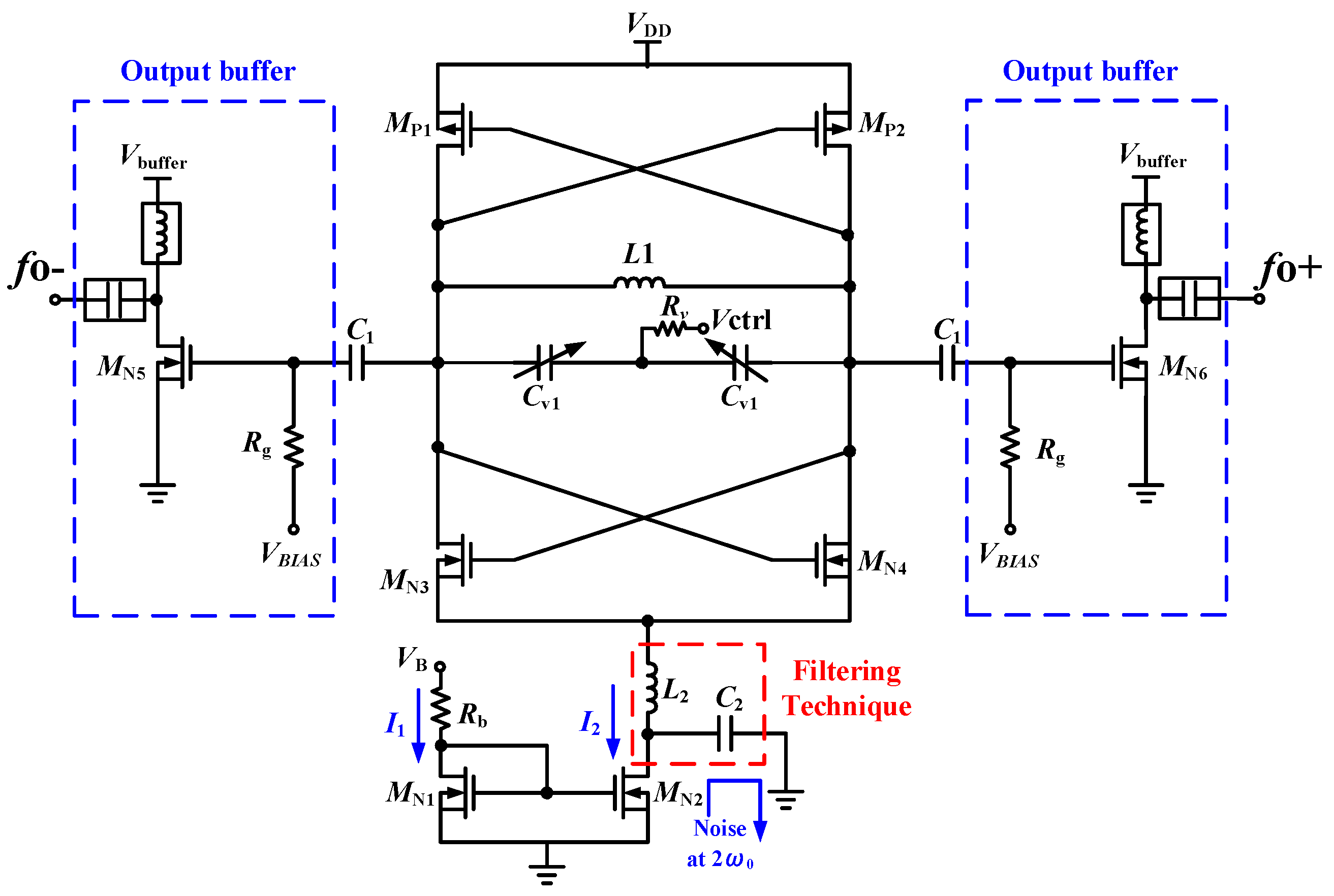

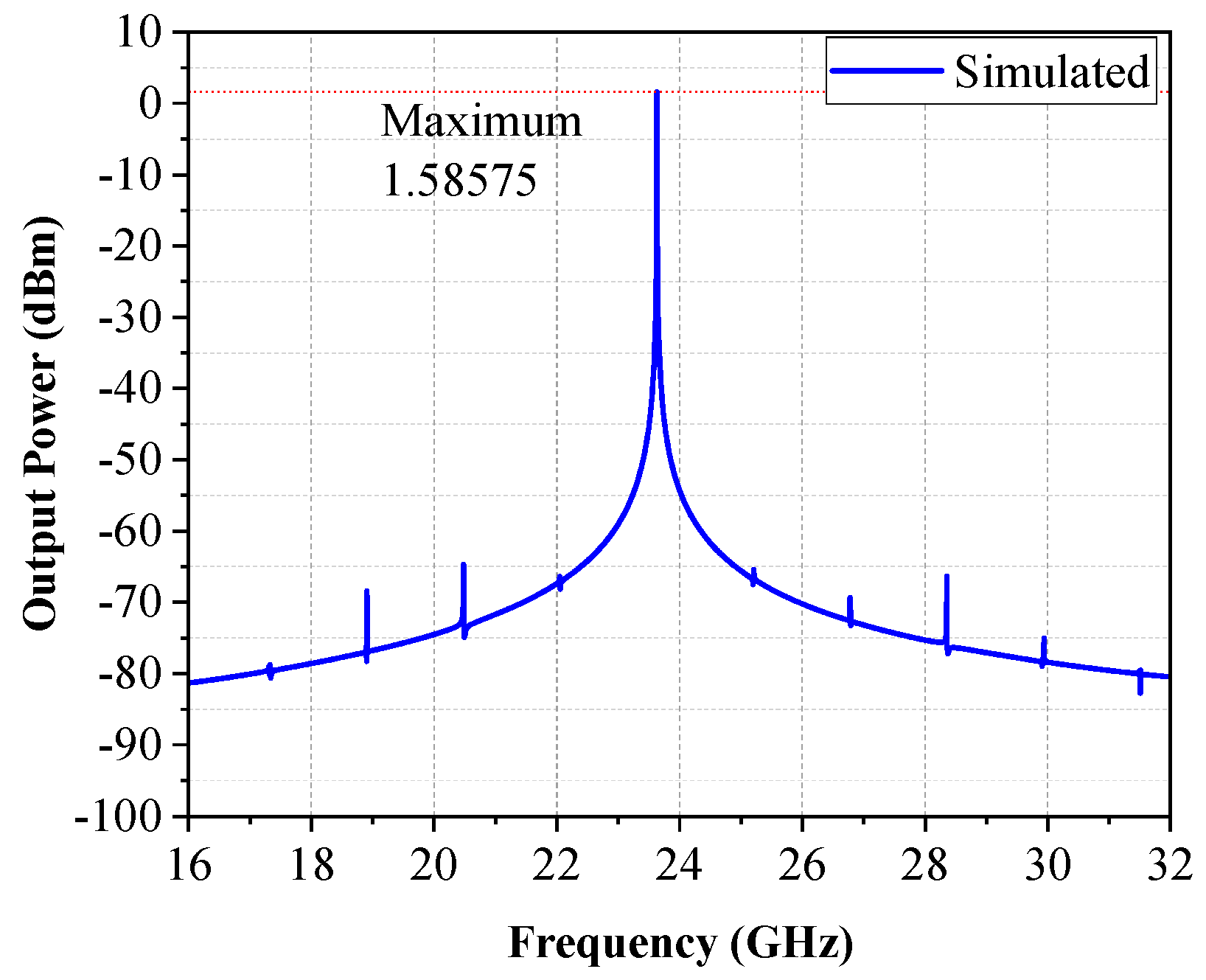

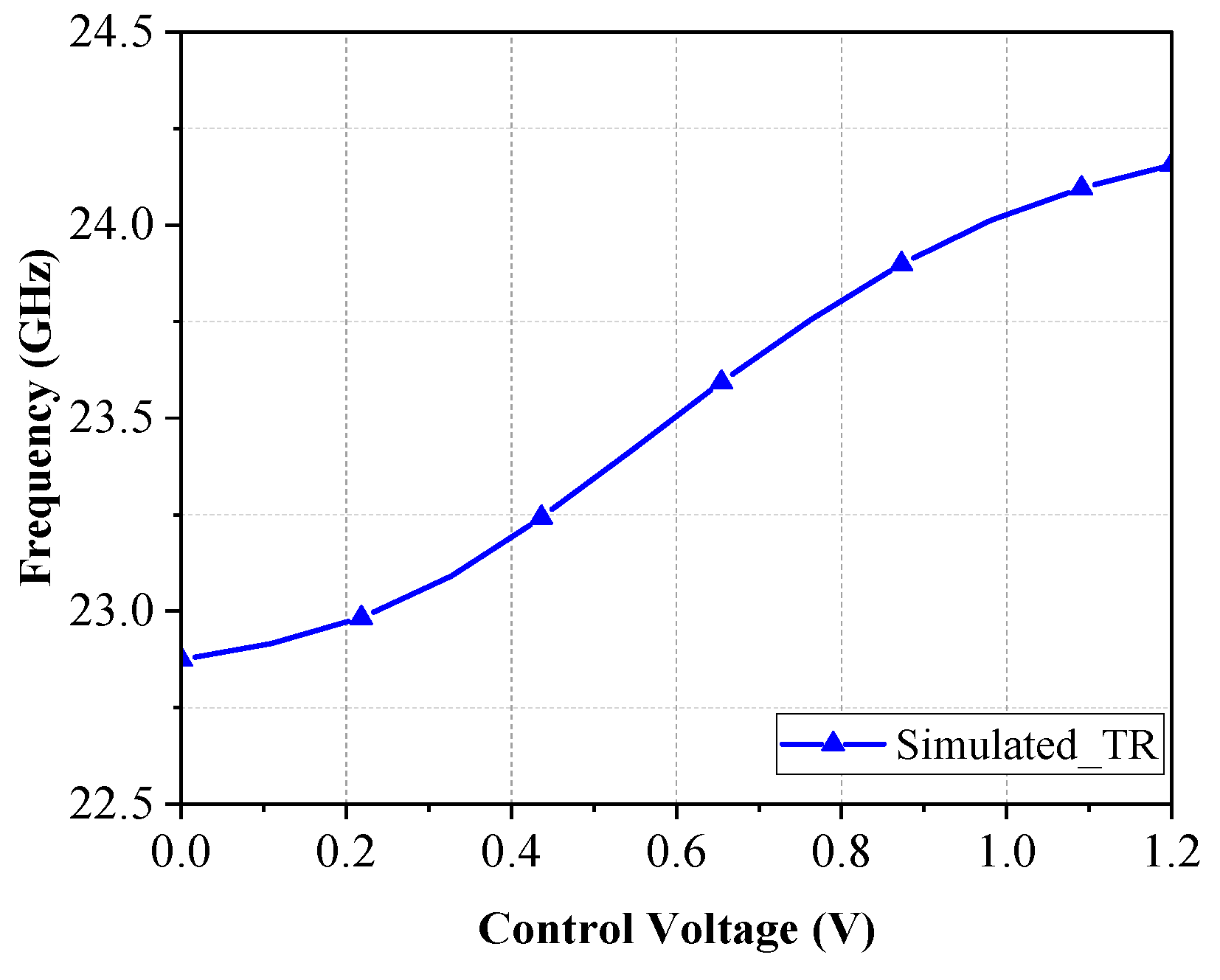

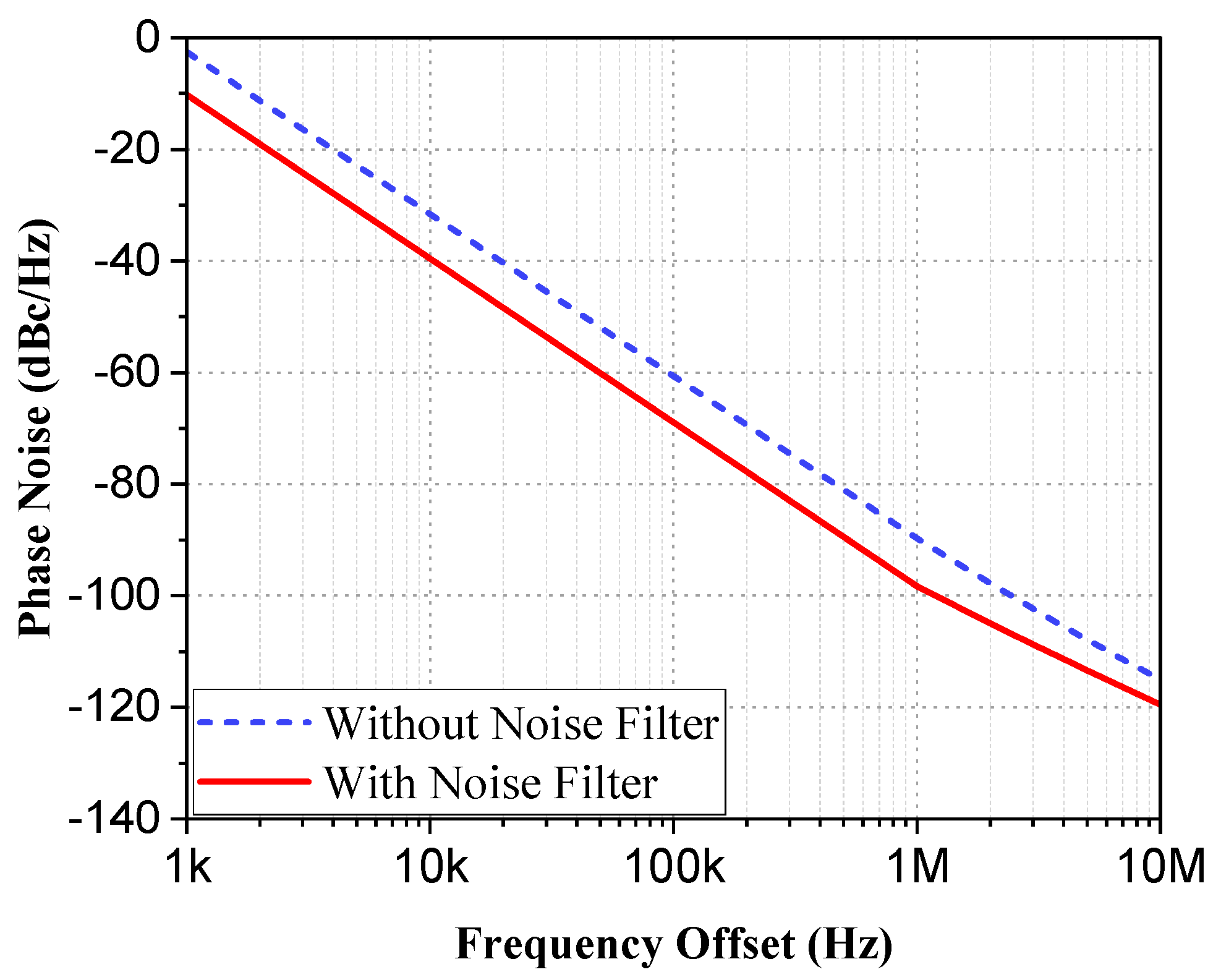

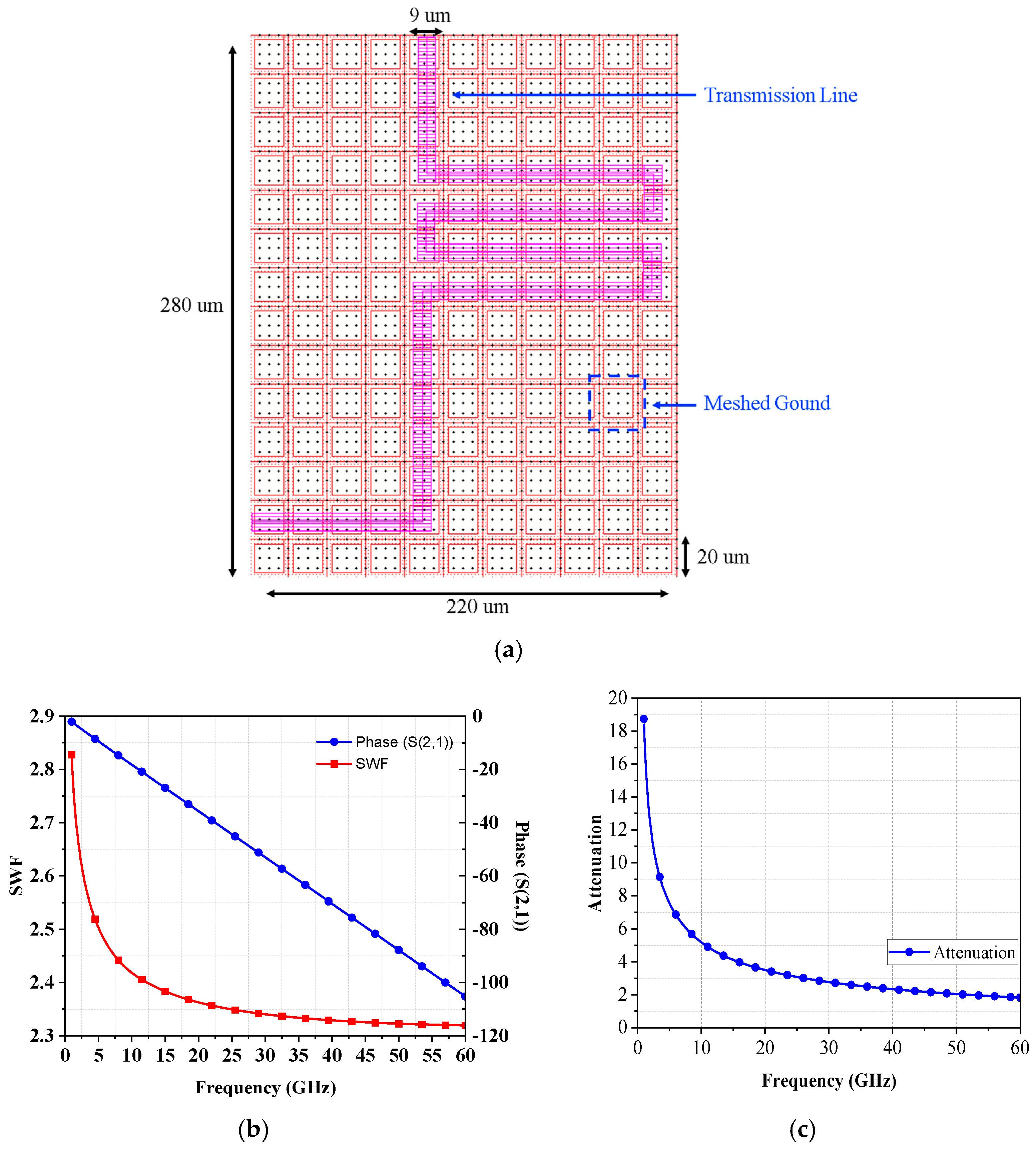

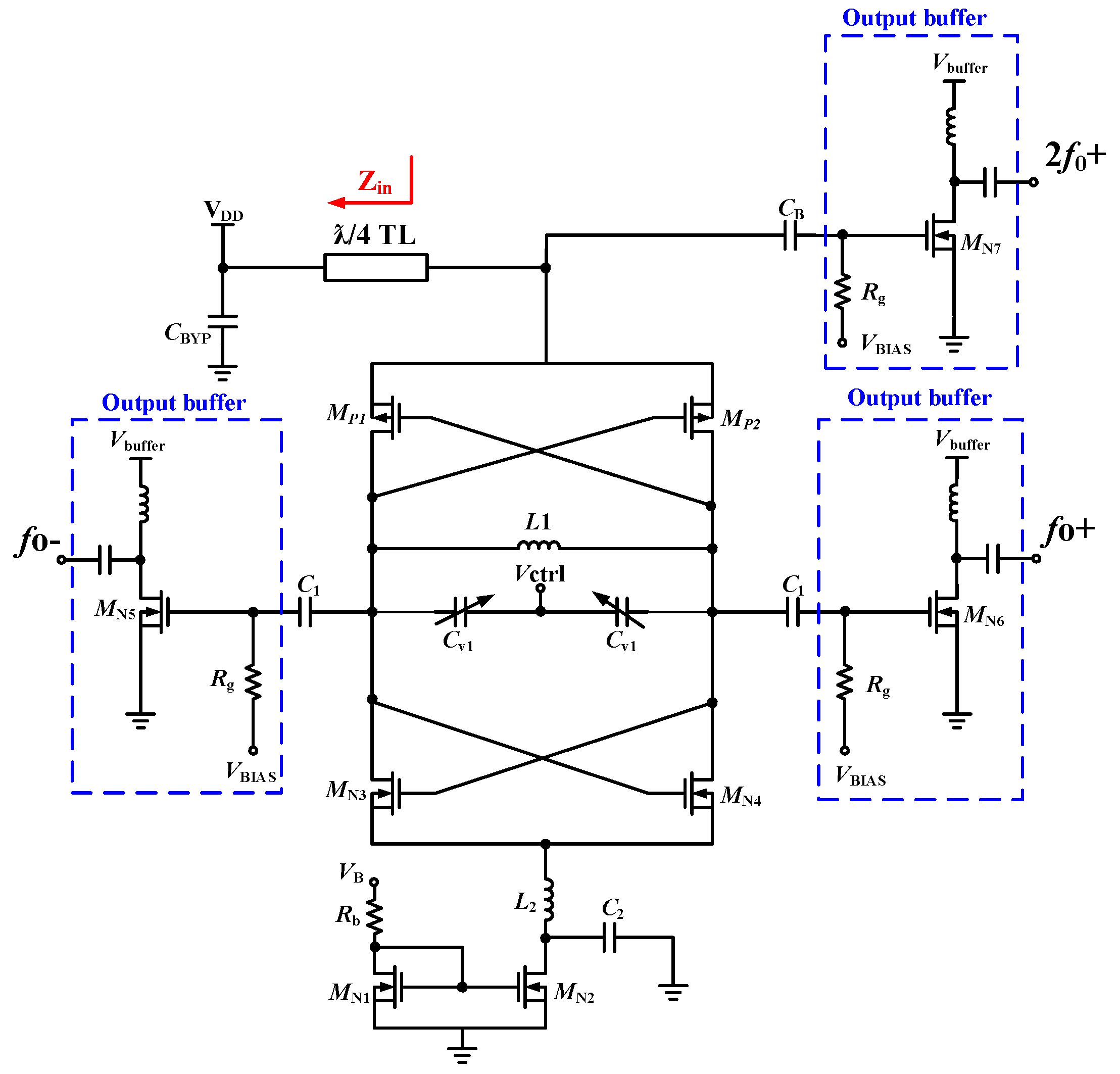

2. Design and Analysis

2.1. The Proposed 24-GHz VCO

2.2. The Proposed Push–Push 48-GHz VCO

2.2.1. The

2.2.2. The Push–Push VCO

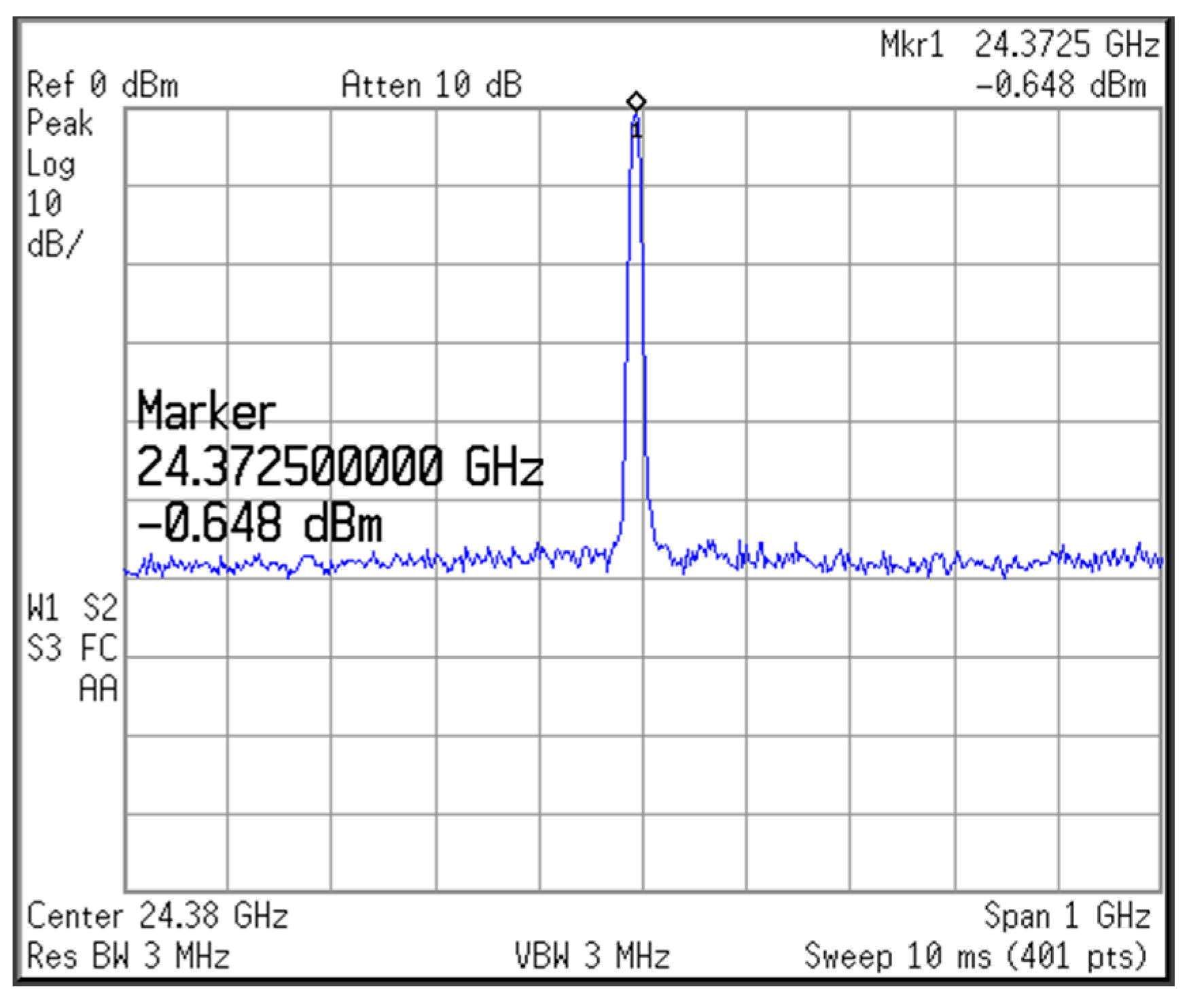

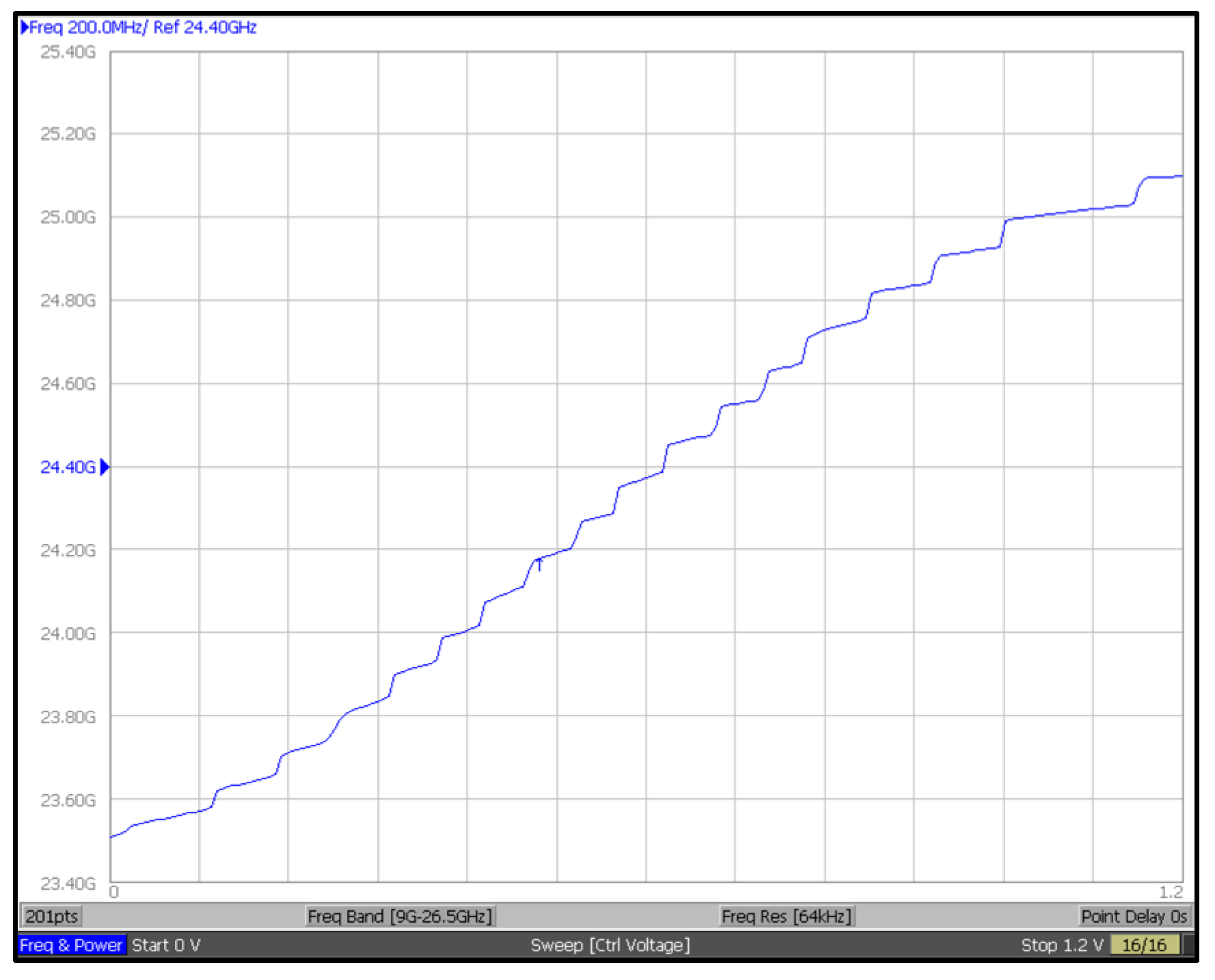

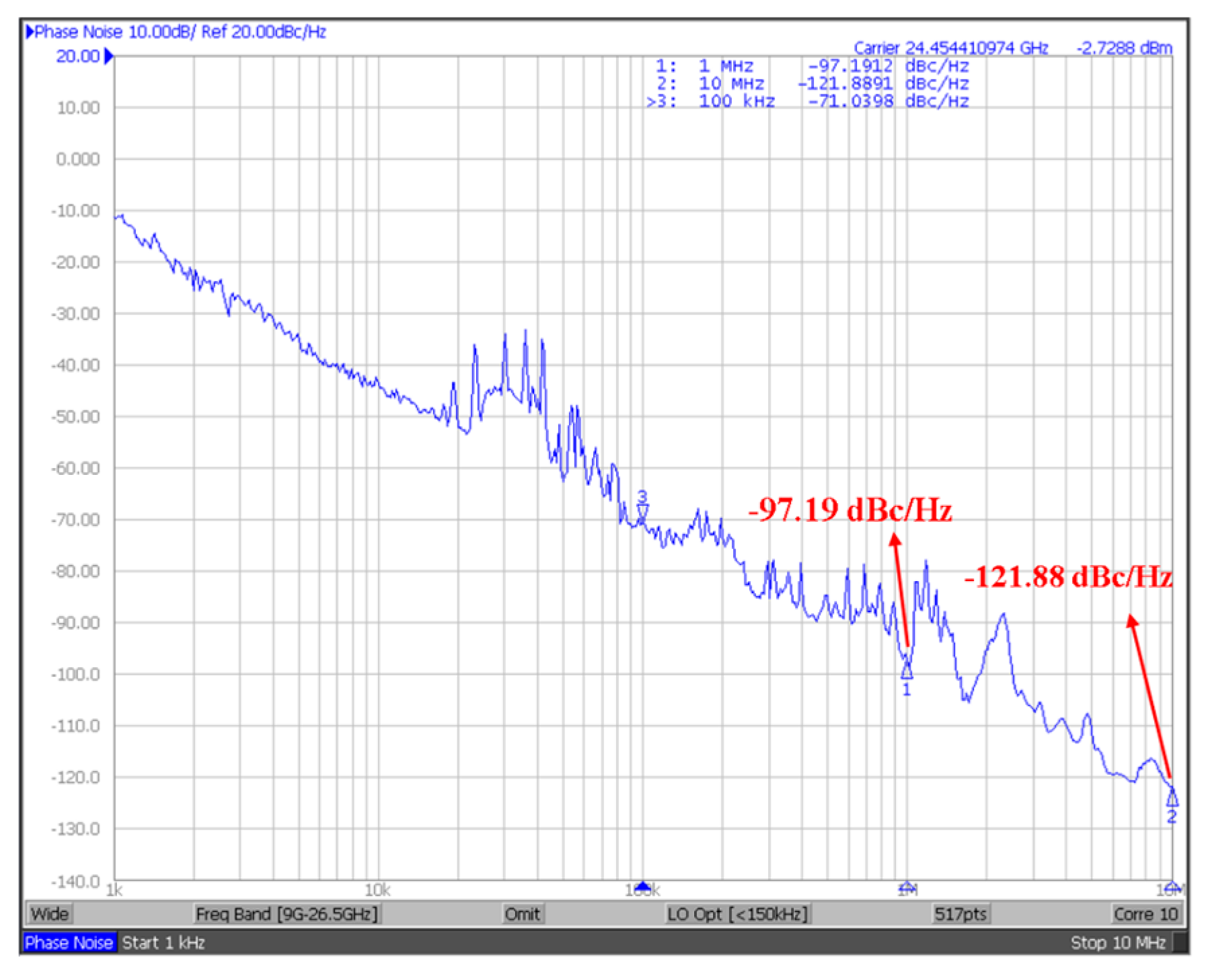

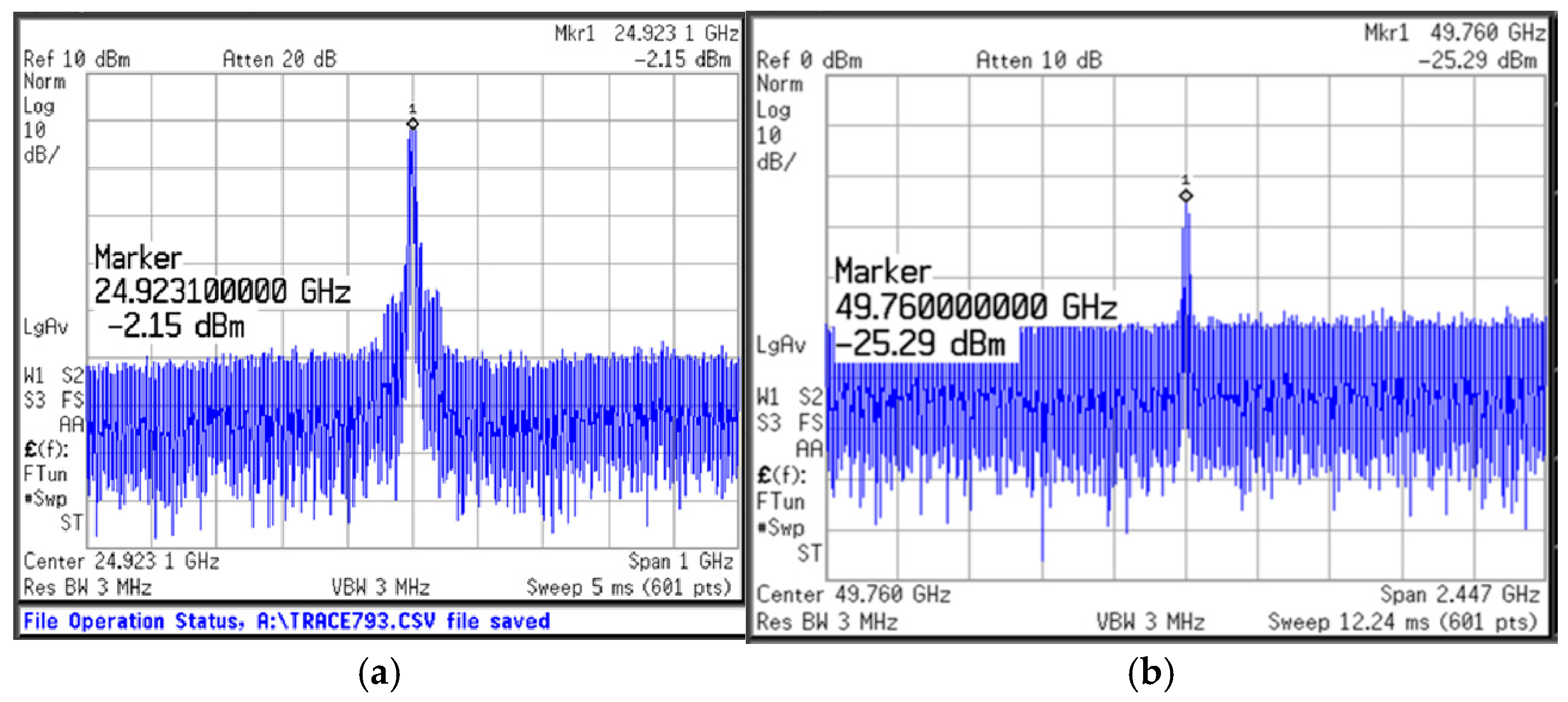

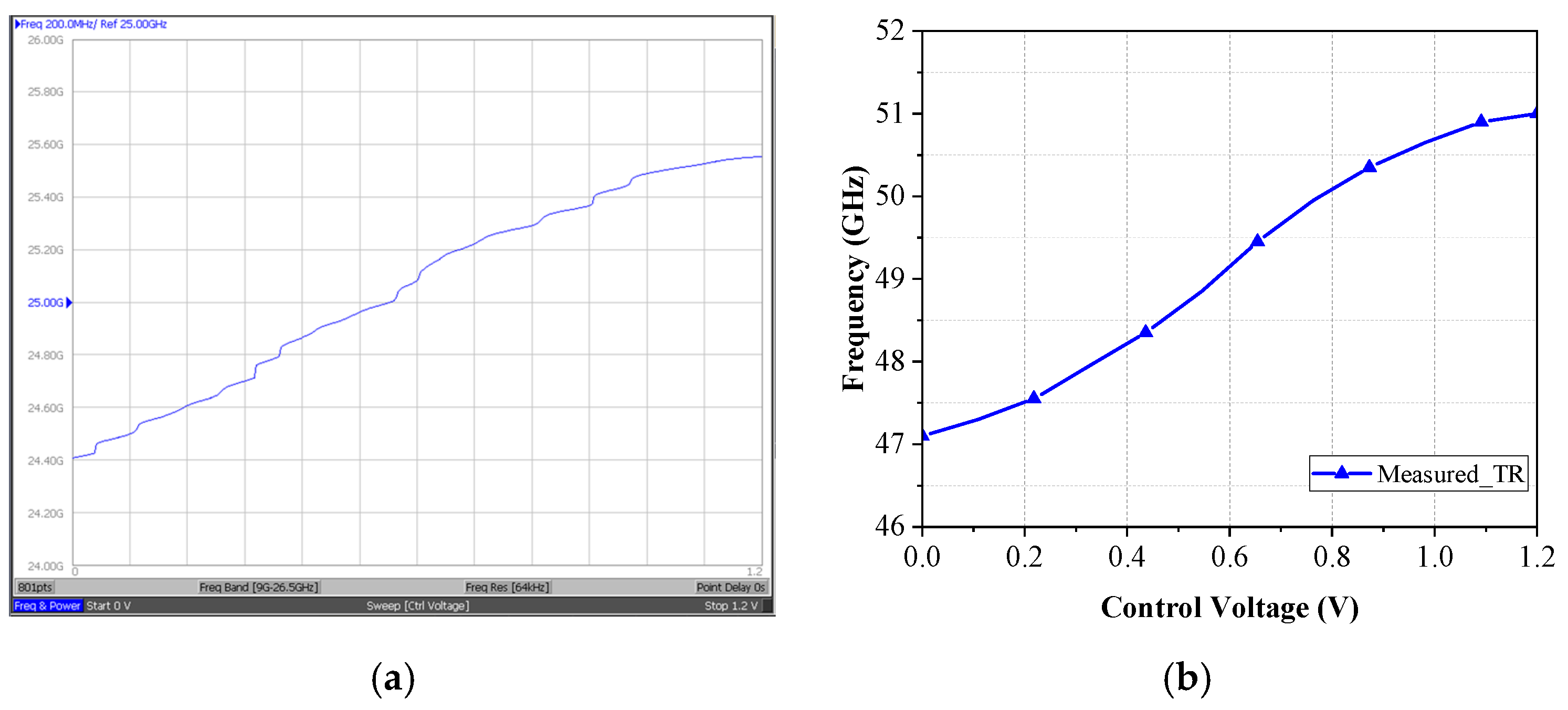

3. Implementation and Experimental Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Hegazi, E.; Sjoland, H.; Abidi, A.A. A filtering technique to lower LC oscillator phase noise. IEEE J. Solid-State Circuits 2001, 36, 1921–1930. [Google Scholar] [CrossRef]

- Yang, D.; Zhang, L.; Wang, H.; Zeng, D.; Zhou, C.; Yang, D. A 24GHz low phase noise feedback CMOS LC-VCO. In Proceedings of the 2011 IEEE International Conference of Electron Devices and Solid-State Circuits, Tianjin, China, 17–18 November 2011; pp. 1–2. [Google Scholar]

- Fu, Y.; Yao, H.; Dai, Y.; Wu, Y.; Huang, G. A 20GHz LC-VCO for Satellite Microwave Communication Application. In Proceedings of the 2020 IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications (IMWS-AMP), Suzhou, China, 29–31 July 2020; pp. 1–4. [Google Scholar]

- Lin, C.-H.; Yang, C.-Y. A 17-21GHz Current-Folding Frequency Tripler with >36 dBc Harmonic Rejection in 90nm CMOS. In Proceedings of the 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), Taipei, Taiwan, 6–9 November 2022; pp. 1–3. [Google Scholar]

- Barajas, B.; Molavi, R.; Mirabbasi, S. A Wideband 65-nm 60-GHz Push-Push LC VCO using a Nonlinear Varactor Array. In Proceedings of the 2024 IEEE 67th International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 11–14 August 2024; pp. 367–371. [Google Scholar]

- Wang, L.; Upadhyaya, P.; Sun, P.; Zhang, Y.; Heo, D.; Chen, Y.J.; Jeong, D.H. A 5.3GHz low-phase-noise LC VCO with harmonic filtering resistor. In Proceedings of the 2006 IEEE International Symposium on Circuits and Systems (ISCAS), Kos, Greece, 21–24 May 2006; p. 4. [Google Scholar]

- Katz, A.; Degani, O.; Socher, E. Design and optimization of a low-noise cross-coupled fundamental VCO in 90nm CMOS for 60GHz applications. In Proceedings of the 2011 IEEE 11th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, Glendale, AZ, USA, 17–19 January 2011; pp. 13–16. [Google Scholar]

- Luo, J.; He, J.; Wang, H.; Chang, S.; Huang, Q.; Xiong, Y.-Z. A 150-GHz push-push VCO in 0.13-μm SiGe BiCMOS. In Proceedings of the 2014 International Symposium on Integrated Circuits (ISIC), Singapore, 10–12 December 2014; pp. 308–311. [Google Scholar]

- Chiang, M.-J.; Wu, H.-S.; Tzuang, C.-K.C. Prorogation Characteristics of CMOS Synthetic Transmission Line and Slow-Wave Inductor on the Complementary Spiral-Shaped Electromagnetic Bandgap (EBG) Shielding Ground Plane. In Proceedings of the 2007 Asia-Pacific Microwave Conference, Bangkok, Thailand, 11–14 December 2007; pp. 1–4. [Google Scholar]

- Pawar, S.N.; Mane, P.B. Design and Implementation of KU Band LC-VCO using 90nm CMOS Process. In Proceedings of the 2020 International Conference on Smart Electronics and Communication (ICOSEC), Trichy, India, 10–12 September 2020; pp. 1234–1238. [Google Scholar]

- Li, D.; Zhang, L.; Wang, Y. A 60GHz quadrature LO synthesizer with 1.2° phase error and over 17% tuning range for IEEE 802.11ad applications. In Proceedings of the 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Guilin, China, 28–31 October 2014; pp. 1–3. [Google Scholar]

- Huang, L.; Yuan, S.; Zhang, R.; Li, W. A 15 GHz CMOS low phase noise VCO using coupled coplanar waveguide. In Proceedings of the 2011 3rd International Conference on Computer Research and Development, Shanghai, China, 11–13 March 2011; pp. 310–313. [Google Scholar]

- Wang, Z.; Jiang, S.; Jiang, H.; Chi, B. A K-Band Fractional-N Frequency Synthesizer with a Low Phase Noise LC VCO in 90nm CMOS. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

- Kwok, K.; Long, J.R.; Pekarik, J.J. A 23-to-29GHz Differentially Tuned Varactorless VCO in 0.13μm CMOS. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2007; Digest of Technical Papers. pp. 194–596. [Google Scholar]

- Chang, Y.-H. Low-Voltage Dual-B and CMOS Voltage-Controlled Oscillator for Ka-Band and V-Band Applications. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 1307–1310. [Google Scholar] [CrossRef]

- Yu, A.H.-T.; Tam, S.W.; Kim, Y.; Socher, E.; Hant, W.; Chang, M.C.; Itoh, T. A Dual-Band Millimeter-Wave CMOS Oscillator with Left-Handed Resonator. IEEE Trans. Microw. Theory Tech. 2010, 58, 1401–1409. [Google Scholar] [CrossRef]

- Chiu, H.-C.; Kao, C.-P. A Wide Tuning Range 69 GHz Push-Push VCO Using 0.18 μm CMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2010, 20, 97–99. [Google Scholar] [CrossRef]

| Ref. | [12] | [13] | [14] | This Work |

|---|---|---|---|---|

| Technology (nm) | 90 | 65 | 130 | 90 |

| Supply (V) | 1.5 | 1.2 | 1.2 | 1.2 |

| Frequency (GHz) | 14.62–15.5 | 21.4–22.4 | 23.2–29.4 | 23.51–25.09 |

| Power Consumption (mW) | 9.13 | 16 | 36.5 | 6.12 |

| POUT (dBm) | −4.12 | N/A | −11 | −0.65 |

| Tuning Range (%) | 5.8 | 11 | 26.5 | 6.5 |

| Phase Noise (dBc/1MHz) | −94.86 | −93.4 | −92.6 | −97.19 |

| FOM | −168 | −179.5 | −165.4 | −177.1 |

| Chip Core Area (mm2) | N/A | 0.64 | 0.12 | 0.47 |

| Ref. | [15] | [16] | [17] | This Work |

|---|---|---|---|---|

| Technology (nm) | 90 | 90 | 180 | 90 |

| Supply (V) | 0.6 | 1.2 | 1.8 | 1.2 |

| Frequency (GHz) | 28.26/56.52 | 21/55 | 69.3 | 24.9/49.8 |

| Power Consumption (mW) | 7.08 | 14 | 27.5 | 6.89 |

| POUT (dBm) | −13.74/−40.47 | −30.5/−21.17 | −31.46 | −2.15/−25.29 |

| Tuning Range (%) | 8.83 | N/A | 5.2 | 7.2 |

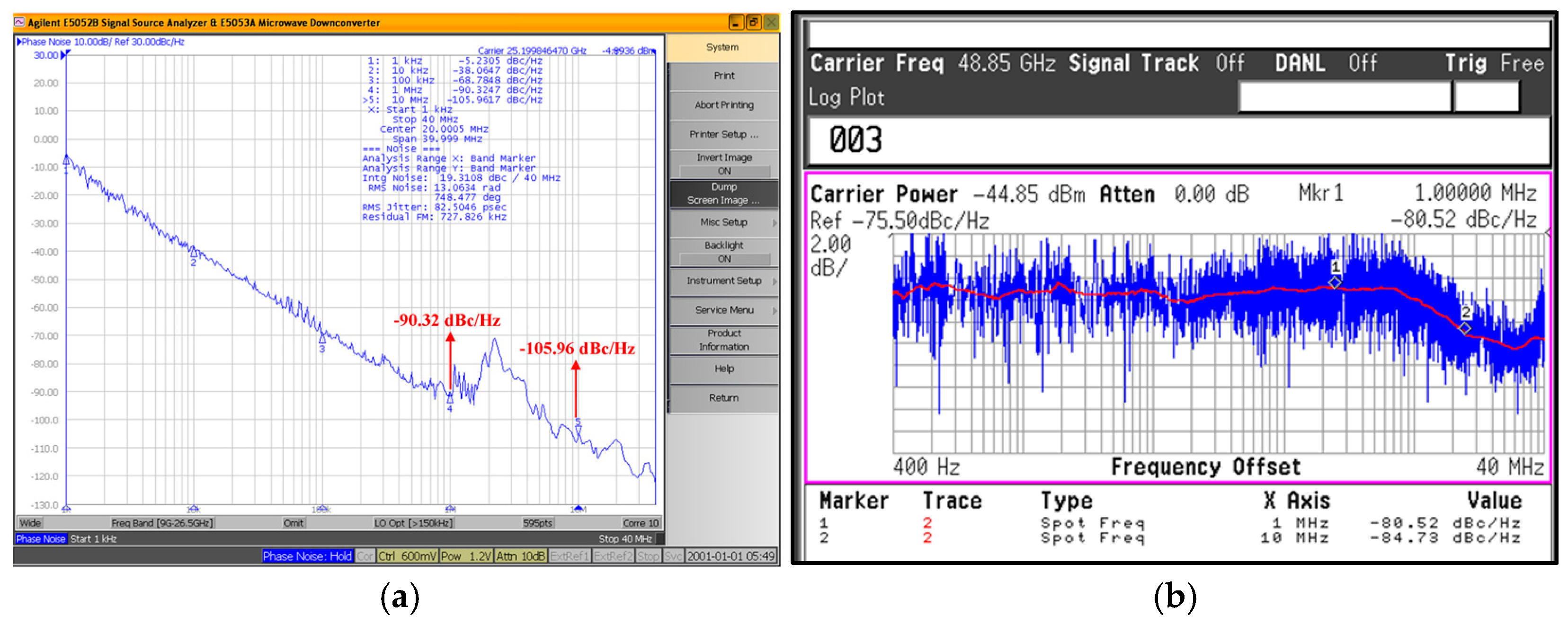

| Phase Noise (dBc/1MHz) | −95.62/−87.83 | −100.8/−86.7 | −75.23 | −90.32/−80.52 |

| FOM | −176.1/−174.3 | −175.8/−170 | −158.3 | −169.9/−166.2 |

| Chip Core Area (mm2) | 0.42 | 0.009 | 0.208 | 0.49 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ku, C.-C.; Wang, S. Design and Implementation of 24-GHz and 48-GHz VCOs Using Noise Filtering Technique in 90-nm CMOS. Micromachines 2025, 16, 682. https://doi.org/10.3390/mi16060682

Ku C-C, Wang S. Design and Implementation of 24-GHz and 48-GHz VCOs Using Noise Filtering Technique in 90-nm CMOS. Micromachines. 2025; 16(6):682. https://doi.org/10.3390/mi16060682

Chicago/Turabian StyleKu, Chen-Chih, and Sen Wang. 2025. "Design and Implementation of 24-GHz and 48-GHz VCOs Using Noise Filtering Technique in 90-nm CMOS" Micromachines 16, no. 6: 682. https://doi.org/10.3390/mi16060682

APA StyleKu, C.-C., & Wang, S. (2025). Design and Implementation of 24-GHz and 48-GHz VCOs Using Noise Filtering Technique in 90-nm CMOS. Micromachines, 16(6), 682. https://doi.org/10.3390/mi16060682